## **Freescale Semiconductor**Application Note

Document Number: AN5115

Rev. 0, 05/2015

# **MPC5777M Hardware Design Guide**

by: Andrew Turner, David McMenamin, and Curt Hillier

## 1 Introduction

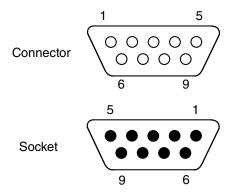

The MPC5777M is a multi-core 32-bit microcontroller initially intended for automotive powertrain applications. It contains two e200z7 and one e200z4 Power Architecture® cores running at up to 300 MHz.

This application note details the options of the MPC5777M power supplies and the correct external circuitry required for all of the power supplies, including digital, analog, and SRAM standby. It also discusses configuration options for clock, reset, and ADCs, as well as recommended debug and peripheral communication connections, and other major external hardware required for the device.

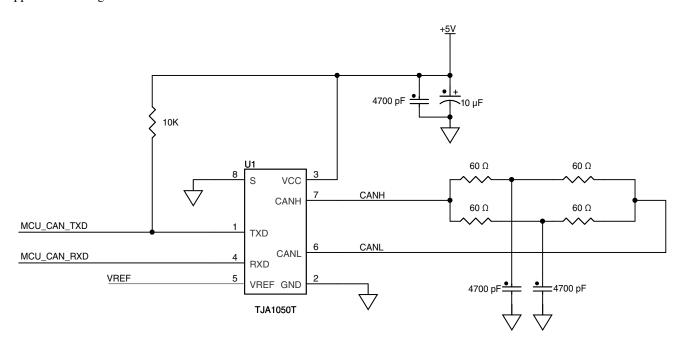

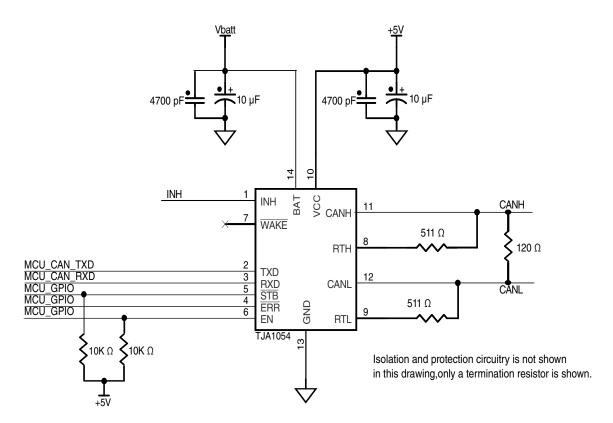

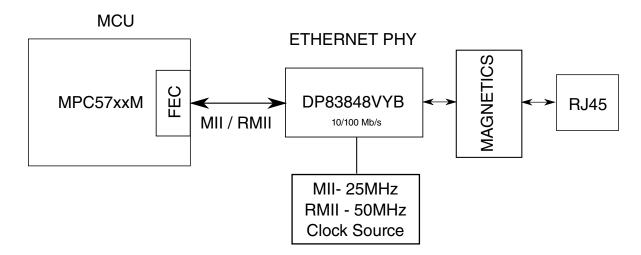

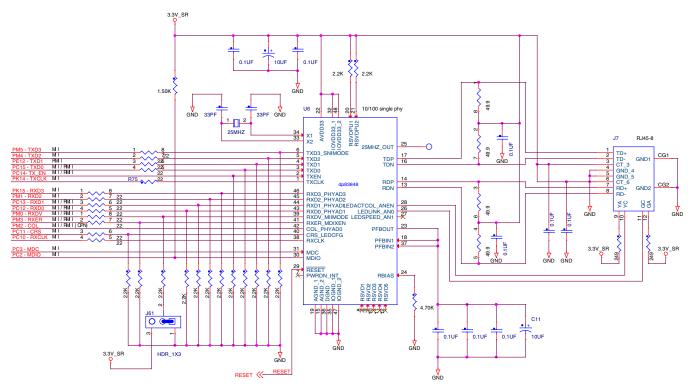

The MPC5777M requires multiple external power supply voltages to operate. The main power supplies required are 1.3 V for the internal logic and 5 V for the internal regulator and on-chip analog to digital converters. The 5 V supply can also be used to supply pin input and output voltages. The internal regulator generates the 3.3 V required to power the on-chip flash memory. Optionally, 3.3 V can be supplied for the External Bus Interface (EBI), FlexRay, and the JTAG interface input and output voltages. The SRAM has a separate supply input for keep-alive features, if they are required.

#### Contents

| 1 | Introduction                                                  | 1  |

|---|---------------------------------------------------------------|----|

| 2 | Overview of MPC5777M package options                          | 2  |

| 3 | Power supply                                                  | 2  |

| 4 | Clock Circuitry                                               | 16 |

| 5 | Device Reset Configuration                                    | 19 |

| 6 | Recommended debug connectors and connector pinout definitions | 19 |

| 7 | External Bus Interface (EBI)                                  | 24 |

| 8 | Example of Communication Peripheral Connections               | 27 |

## 2 Overview of MPC5777M package options

The MPC5777M is available in six different package options; three of these are intended for production and three are intended to provide additional features to support debug and calibration.

Table 1. MPC5777M package options

| Package    | Description                                                                                                                                  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 416 BGA PD | Production: Provides access to the primary features of the device, does not include EBI (External Bus Interface)                             |

| 416 BGA ED | Development: Footprint compatible with the 416 BGA ED package with additional Nexus High Speed Aurora Trace interface and calibration device |

| 512 BGA PD | Production: Superset of 416 BGA PD, with more I/O ports available and EBI                                                                    |

| 512 BGA ED | Development: Footprint compatible with the 512 BGA ED package with additional Nexus High Speed Aurora Trace interface and calibration device |

The decision of which package to use should be based on the number of input/output pins required for the application and the area available for the target system. The following table shows the size differences of the packages. See the device data sheet for complete package dimensions and ball placement. Drawings are also available on the Freescale web site; search for the case outline number shown in Table 2.

Table 2. Package sizes

| Package Type | Device Type            | Physical Size | Case Outline Number |

|--------------|------------------------|---------------|---------------------|

| 416TEPBGA    | Production             | 27 x 27 mm    | 98ARE10523D         |

| 416TEPBGA    | Emulation              | 27 x 27mm     | 98ASA00493D         |

| 512TEPBGA    | Production & Emulation | 25 x 25 mm    | 98ASA00262D         |

## 3 Power supply

MPC5777M microcontrollers include a robust power management infrastructure that enables applications to select among various user modes and to monitor internal voltages for high- and low-voltage conditions. The monitoring capability is also used to ensure supply voltages and internal voltages are within the required ranges before the microcontroller can exit reset.

The MPC5777M MCU supports three different input voltages:

- 1.3V (required) for the internal logic

- 5V (required) for the Power Management controller, I/O, Debug, ADCs and external communication interfaces.It is essential that 5v is applied to the VDD\_HV\_IO\_MAIN supply for the device to exit Reset.

- 3.3V (optional) for FlexRay, I/O, Debug and external communication interfaces

The 3.3 V required for the flash memory is generated by an on-chip regulator. This regulator requires an external decoupling capacitor on VDD\_HV\_FLA.

## 3.1 Power supply signals and pins

Table 3 lists all power domains with corresponding pin names.

Table 3. MCU supply pins

| Domain name               | Supply Voltage            | Description                                                  |

|---------------------------|---------------------------|--------------------------------------------------------------|

| VDD_HV_IO_JTAG            | 3.3V or 5V                | JTAG I/O and oscillator supply                               |

| VDD_HV_ADV                | 5V                        | High voltage supply for the ADC modules                      |

| VDD_HV_ADR_S              | 5V                        | Voltage reference of ADC SAR module                          |

| VDD_HV_ADR_D              | 5V                        | Voltage reference of ADC $\Sigma/\Delta$ module              |

| VDD_HV_PMC                | 5V                        | High voltage Power supply for internal power management unit |

| VDD_HV_IO_MAIN            | 5V                        | High voltage Power supply for the I/Os                       |

| VDD_HV_FLA <sup>1</sup>   | 3.3V - Internal Regulator | Decoupling supply pin for Flash voltage regulator            |

| VDD_HV_IO_FLEX            | 3.3V or 5V                | FlexRay & Ethernet 3.3V I/O Supply                           |

| VDD_HV_IO_FLEXE           | 3.3V or 5V                | FlexRay & Ethernet &EBI 3.3V I/O<br>Supply                   |

| VDD_HV_IO_EBI             | 3.3V or 5V                |                                                              |

| VDD_LV_STBY               | 1.3V                      | Buddy device core power supply                               |

| VDD_LV                    | 1.3V                      | Low voltage power supply for the core area                   |

| VDD_HV_IO_BD <sup>2</sup> | 3.3V or 5V                | High voltage Power supply for Buddy device I/O               |

- 1. No connection to external supply needed.

- 2. Only present on the 416ED and 512ED emulation devices

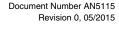

Some of the supplies can be powered with different supply voltages. In particular, the MCU allows flexibility in the supply of voltages that power selected input and output pins (VDD\_HV\_IO\_JTAG). These supplies are "high" supplies and can be connected to either a nominal 3.3 V or 5.0 V supply. See the data sheet for each specific device to learn what voltages can be connected to the power pins, but the generally used voltage is shown in Table 3 and in the figure below.

rower supply

Figure 1. Supply connections overview

The different package options mean that there are a different number of pins/balls available for the power supply, depending on the package. It also means that in some cases, some supplies might not be available. All supply pins/balls that are available on the package should be connected to a supply voltage.

Table 4 shows all power domains and the suggested decoupling and/or filter capacitors for their corresponding pins. These values are provided as a guideline and will vary depending on the application and capability of the power supplies used.

| Domain name     | Supply Voltage | Bulk                | Bypass             |

|-----------------|----------------|---------------------|--------------------|

| VDD_HV_IO_JTAG  | 3.3 V or 5 V   | 100 nF              | 1 nF               |

| VDD_HV_IO_BD    | 3.3 V or 5 V   | 100 nF              | 1 nF               |

| VDD_HV_ADV      | 3.3 V or 5 V   | 4.7 μF              | 0.1 μF             |

| VDD_HV_ADR_S    | 3.3 V or 5 V   | 100 nF              |                    |

| VDD_HV_ADR_D    | 3.3 V or 5 V   | 100 nF              |                    |

| VDD_HV_IO_MAIN  | 5 V            | 4.7 μF              | 10 nF <sup>1</sup> |

| VDD_HV_PMC      | 5 V            | 4.7 μF <sup>2</sup> | 0.1 μF             |

| VDD_HV_FLA      | 3.3 V          | 1.5 µF              |                    |

| VDD_HV_IO_EBI   | 3.3 V or 5 V   | 100 nF              |                    |

| VDD_HV_IO_FLEX  | 3.3 V or 5 V   | 100 nF              |                    |

| VDD_HV_IO_FLEXE | 3.3 V or 5 V   | 100 nF              |                    |

| VDD_LV_STBY     | 1.3 V          | 100 nF              |                    |

| VDD_LV          | 1.3 V          | 10 μF               | 47 nF              |

Table 4. Supply pin decoupling caps

- 1. External capacitors for the IO pins are dependent on the application.

- 2. VDD\_HV\_PMC pin only present on 416BGA package. On the 512BGA package VDD\_HV\_PMC is connected to VDD\_HV\_IO\_MAIN. No additional capcitance is required for the 512BGA

## 3.2 Input and output pins - power supply segmentation

The input and out pins are powered from three domains: VDD\_HV\_IO\_MAIN, VDD\_HV\_IO\_FLEX, and VDD\_HV\_IO\_JTAG. Each I/O pin is associated with one of these three domains. The majority of I/O pins are powered by VDD\_HV\_IO\_MAIN. The VDD\_HV\_IO\_FLEX and VDD\_HV\_IO\_JTAG domains are primarily intended to allow the FlexRay and JTAG interfaces to be operated at a voltage level different from the VDD\_HV\_IO\_MAIN domain. However, they can also be used to provided a limited amount of I/O pins at an alternative voltage level to the main domain.

The voltage level supplied on the I/O domains determins the output voltage level and input transition levels for the I/O pins associated with that domain. The pins that are powered from VDD\_HV\_IO\_JTAG and VDD\_HV\_IO\_FLEX are shown in Table 5. All other I/O pins are supplied from VDD HV IO MAIN.

| I/O power domain     | I/O pins                                       |

|----------------------|------------------------------------------------|

| VDD_HV_IO_FLEX       | PC[10:15] PE[12] PK[14:15] PM[0:8] PM[11]      |

| VDD_HV_IO_FLEXE      | PS[0:15] PT[0:15] PY[4]                        |

| VDD_HV_IO_EBI        | PV[1:15] PW[0:15]                              |

| VDD_HV_IO_EBI_CLKOUT | PV[0]                                          |

| VDD_HV_IO_JTAG       | PA[5:9] PA[14] PI[15] PD[6:7] PF[13] PI[14:15] |

Table 5. I/O pin power domain association

## 3.3 Decoupling capacitors layout priorities

When trade offs must be made in the layout, it is important to ensure that the highest priority decoupling capacitors are placed as closely as possible to the MCU. The list below orders the supplies from highest to lowest priority in terms of decoupling capacitor placement.

- 1. VDD\_HV\_ADR\_S & VDD\_HV\_ADR\_D

- 2. VDD HV ADV

- 3. VDD HV IO JTAG

- 4. VDD LV

- 5. VDD HV IO BD

- 6. VDD\_HV\_PMC

- 7. VDD HV FLA

- 8. VDD\_HV\_IO\_MAIN

- 9. VDD HV EBI

- 10. VDD HV IO FLEX

- 11. VDD HV IO FLEXE

- 12. VDD\_LV\_STBY

Highest priority is given to the analog-to-digital converters reference and power supply decoupling: VDD\_HV\_ADR\_S, VDD\_HV\_ADR\_D, and VDD\_HV\_ADV. Clean supplies are vital to ensure that the highest accuracy is achieved with the ADCs. Next, the supply for the oscillator is prioritized as this helps to ensure reliable and stable operation from the external oscillator.

Medium priority is given to VDD\_LV, VDD\_HV\_IO\_BD, VDD\_HV\_PMC, and VDD\_HV\_FLA. VDD\_LV is the main supply for the on-chip digital logic and this is prioritized as it affects the largest amount of logic on the device. VDD\_HV\_IO\_BD powers the high speed Nexus Aurora pins and noise on this domain would affect the quality of the output. VDD\_HV\_PMC powers the flash regulator and VDD\_HV\_FLA is the output of this this regulator. A good supply to the flash memory ensures reliable flash programming and erasing.

#### rower supply

VDD\_HV\_IO\_MAIN, VDD\_HV\_IO\_EBI, VDD\_IO\_FLEX, VDD\_IO\_FLEXE, and VDD\_LV\_STBY are given lower priority. Although it is still important that these supplies have a clean power signal, the hardware they power is less affected by noise.

## 3.4 Supply monitoring

The MPC5777M monitors the voltage supply internally. The function of the power-on reset (POR) and low-voltage detect (LVD) circuits is to hold the device in reset. The device is held in reset regardless of how slow the supply voltage rise is, until the point at which the POR and LVDs are released.

The POR and LVD circuits function correctly even if the input voltage is non monotonic.

For detailed information on the low-voltage detect (LVD) and high-voltage detect (HVD) circuits please refer to the device reference manual.

#### 3.4.1 Behavior of LVD / HVD

The internal LVD circuits monitor when the voltage on the corresponding supply is below defined values and either assert a reset or an interrupt. The LVDs also support hysteresis for the falling and rising trip points.

Although there is an option to disable the LVDs and HVDs following reset, they are capable of being used in a 'monitor' only mode and also capable of generating a safe/interrupt event. The LVDs/HVDs can also be configured after device initialization preventing reset to happen when supply crosses the LVD threshold, providing a higher voltage range. An application then verifies that the device remains in the functional range.

#### NOTE

LVD096 and LVD270 (low range LVDs) cannot be disabled. These modules are used during power-up phase and must ensure that an absolute lowest threshold of operation is never crossed. This is not a guarantee that the device will function down to this level. It is rather a guarantee that the device will recover if this level is crossed.

#### 3.4.2 Power-on reset

The power management controller (PMC) controls the power-on reset (PORST) for the MCU. When the critical power supplies are below minimum levels, the MCU is held in the POWER-UP phase of the reset state machine, until the power supplies have reached their specified levels. Power sequencing is not necessary. When the required voltage levels have been reached, the reset generation module (RGM) propagates the device through the next steps of the boot process.

The PMC has two internal power-on reset circuits:

- VPORUPLV monitors the voltage on the 1.3 V input supply. It is monitoring the VDD\_LV\_CORE pin. The VPORUPLV asserts a reset when the input supply is below defined values.

- VPORUPHV monitors the voltage on the 5.0 V input supply. It is monitoring the VDD\_HV\_PMC pin. The PORST trip point is high enough to make sure all the LVD circuits are functional.

See the Reset chapter in the reference manual for PORST/ESRO pin functionality.

## 3.4.3 Low-Voltage (LVD) and High-Voltage Detection (HVD)

The internal LVD circuits monitor when the voltage on the corresponding supply is below defined values and either assert a reset or an interrupt. The LVDs also support hysteresis in the falling and rising trip points.

- All LVDs and HVDs are capable of generating either a reset or an interrupt, with the following exceptions:

- It is not possible to disable the LVD270 and it always generates a reset when triggered (for example, LVD monitoring the high voltage supply input).

- It is not possible to disable the LVD096 and it always generates a reset when triggered (for example, LVD monitoring the internal core voltage). The LVD096 is integral to the POR management.

- All LVDs and HVDs configured for reset generation cause functional or destructive reset. MC\_RGM PHASE0 is not exited until all destructive reset conditions are cleared.

- The appropriate bits in the PMC registers are set by LVD and HVD events.

- LVD and HVD control is protected by the SoC-wide register protection scheme. Therefore, it is configurable as long as the scheme is followed.

- There are user option bits available to allow degrading of "configurable" LVDs/HVDs from destructive down to functional reset. This is a write once mechanism managed by SSCM during device initialization.

- When the LVD or the HVD is enabled for destructive reset generation, then when a trigger event is detected, the external PORST pin is driven low.

The table below lists the LVD and HVD monitors and their characteristics.

Table 6. Voltage monitor electrical characteristics

| Symbol                    |    | Parameter                                                    | Conditions                                                                |         | Value |                   | Unit |

|---------------------------|----|--------------------------------------------------------------|---------------------------------------------------------------------------|---------|-------|-------------------|------|

|                           |    |                                                              |                                                                           | Min Typ |       | Max               | 1    |

| V <sub>PORUP_LV</sub> , 1 | СС | [DST_MEDC18_0291][Covers:                                    | Rising voltage (power up)                                                 | 1111    | -     | 1235              | mV   |

|                           |    | ADD14.010]LV supply power on reset threshold[end]            | Falling voltage (power down) <sup>2</sup>                                 | 1015    | -     | 1125              |      |

|                           |    | reset tireshold[end]                                         | [DST_MEDC18_0074]<br>[Covers:<br>ADD14.073]Hysteresis on<br>power-up[end] | 50      | -     | -                 |      |

| V <sub>LVD096</sub>       | СС | LV internal <sup>3</sup> supply low voltage monitoring       | See note <sup>4</sup>                                                     | 1015    | -     | 1145              | mV   |

| V <sub>LVD108</sub>       | CC | Core LV internal <sup>3</sup> supply low voltage monitoring  | See note <sup>5</sup>                                                     | 1150    | -     | 1220              | mV   |

| V <sub>LVD112</sub>       | CC | LV external <sup>6</sup> supply low voltage monitoring       | See note <sup>3</sup>                                                     | 1175    | -     | 1235              | mV   |

| V <sub>HVD140</sub>       | СС | LV external <sup>7</sup> supply high voltage monitoring      | See note <sup>8</sup>                                                     | 1385    | -     | 1475              | mV   |

| V <sub>HVD145</sub>       | СС | LV external <sup>7</sup> supply high voltage reset threshold | -                                                                         | 1430    | -     | 1510              | mV   |

| VPORUP_HV <sup>1</sup>    | СС | HV supply power on reset threshold <sup>9</sup>              | Rising voltage (power up) on PMC/IO Main supply                           | 4040    | -     | 4480 <sup>7</sup> | mV   |

|                           |    |                                                              | Rising voltage (power up) on IO JTAG and Osc supply                       | 2730    | -     | 3030              |      |

|                           |    |                                                              | Rising voltage (power up) on ADC supply                                   | 2870    | -     | 3182              |      |

|                           |    |                                                              | Falling voltage (power down) <sup>10</sup>                                | 2850    | -     | 3162              |      |

|                           |    |                                                              | Hysteresis on power up <sup>11</sup>                                      | 878     | -     | 1630              | 7    |

| V <sub>POR240</sub>       | СС | HV supply power-on reset voltage                             | Rising voltage                                                            | 2420    | -     | 2780              | mV   |

|                           |    | monitoring                                                   | Falling voltage                                                           | 2400    | -     | 2760              | ]    |

| V <sub>LVD270</sub>       | СС | HV supply low voltage monitoring                             | Rising voltage                                                            | 2750    | -     | 3000              | mV   |

|                           |    |                                                              | Falling voltage                                                           | 2700    | -     | 2950              |      |

#### rower supply

#### Table 6. Voltage monitor electrical characteristics (continued)

| Symbol                 |    | Parameter                                        | Conditions      |      | Value |      |    |

|------------------------|----|--------------------------------------------------|-----------------|------|-------|------|----|

|                        |    |                                                  |                 | Min  | Тур   | Max  | 1  |

| V <sub>LVD295</sub>    | СС | Flash supply low voltage monitoring              | Rising voltage  | -    | -     | 3120 | mV |

|                        |    |                                                  | Falling voltage | 2920 | -     | 3100 | 1  |

| V <sub>HVD360</sub>    | СС | Flash supply high voltage                        | Rising voltage  | 3435 | -     | 3650 | mV |

|                        |    | monitoring                                       | Falling voltage | 3415 | -     | -    | 1  |

| V <sub>LVD360</sub>    | СС | HV supply low voltage monitoring                 | Rising voltage  | -    | -     | 4000 | mV |

|                        |    |                                                  | Falling voltage | 3600 | -     | 3880 | 1  |

| V <sub>LVD400</sub>    | СС | HV supply low voltage monitoring                 | Rising voltage  | 4110 | -     | 4410 | mV |

|                        |    |                                                  | Falling voltage | 3970 | -     | 4270 | 1  |

| V <sub>HVD600</sub>    | СС | HV supply high voltage monitoring                | Rising voltage  | 5560 | -     | 5960 | mV |

|                        |    |                                                  | Falling voltage | 5500 | -     | 5900 | 1  |

| t <sub>VDASSERT</sub>  | CC | Voltage detector threshold crossing assertion    | -               | 0.1  | -     | 2    | μs |

| t <sub>VDRELEASE</sub> | CC | Voltage detector threshold crossing de-assertion | -               | 5    | -     | 20   | μs |

- V<sub>PORUP\_LV</sub> and V<sub>PORUP\_HV</sub> threshold are untrimmed values before completion of the power-up sequence. All other LVD/HVD thresholds are provided after trimming.

- 2. Assume all of LVDs on LV supplies disabled.

- 3. LV internal supply levels are measured on device internal supply grid after internal voltage drop.

- 4. LVD is released after tVDRELEASE temporization when upper threshold is crossed, LVD is asserted tVDASSERT after detection when lower threshold is crossed.

- 5. This specification is driven by LVD108\_C. There are additional LVDs on PLL and Flash VDD\_LV supply nets which will assert at voltage below LVD108\_C.

- 6. LV external supply levels are measured on the die side of the package bond wire after package voltage drop. This is monitoring external regulator supply voltage and board voltage drop. This does not guarantee device is working down to minimum threshold. For minimum supply, refer to operating condition table.

- 7. The PMC supply also needs to be below 5472 mV (untrimmed HVD600 mV).

- 8. HVD is released after tVDRELEASE temporization when lower threshold is crossed, HVD is asserted tVDASSERT after detection when upper threshold is crossed. HVD140 does not cause reset.

- 9. This supply also needs to be below 5472 mV (untrimmed HVD600 min)

- 10. Untrimmed LVD300\_A will be asserted first on power down.

- 11. Hysteresis is implemented only between the VDD\_HV\_IO\_MAIN High voltage Supplies and the ADC high voltage supply. When these two supplies are shorted together, the hysteresis is as is shown in Figure 1. If the supplies are not shorted (VDD\_IO\_MAIN and ADC high voltage supply), then there will be no hysteresis on the high voltage supplies.

#### NOTE

LVD levels are measured on the die side of the package bond wire. For  $V_{DD\_LV}$  levels, a maximum of 30 mV IR drop is incurred from the pin to all sinks on the die. For other LVD, the IR drop is estimated by the multiplying the supply current by 0.5  $\Omega$ .

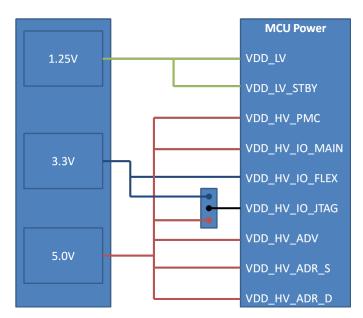

## 3.4.4 Analog module self-test and parameter monitoring

All of the internal Power Management system analog signals can be monitored by the main analog-to-digital converter (ADC): Successive-Approximation-Register ADC B (SARB). The power management reference module provides enough current to fill ADC capacitances without changing values. The minimum resistance for the switches is provided at regulator module.

Figure 2 shows the monitoring implementation. These signals are used for calibration, diagnostics during test or for the user to actively monitor the signal levels. There is a dedicated ADC channel for these monitoring purposes.

Figure 2. Analog module self-test

The table below lists all the internal test signals that can be monitored using ADC SARB.

Table 7. SARADC\_B analog test channel assignment

| SARADC_B input channel | Fast SAR | Fast SAR channel | Description                                                                 |

|------------------------|----------|------------------|-----------------------------------------------------------------------------|

| 96                     | _        | _                | VDD_HV_PMC                                                                  |

| 97                     | _        | _                | VDD_HV_ADV_S                                                                |

| 98                     | _        | _                | VDD_HV_JTAG_OSC                                                             |

| 99                     | _        | _                | VDD_HV_FLA                                                                  |

| 100                    | _        | _                | VDD_HV_IO_MAIN                                                              |

| 101                    | _        | _                | VDD_HV_IO_FLEX                                                              |

| 102                    | _        | _                | Reserved                                                                    |

| 103                    | _        | _                | VDD_HV_IO_FLEXE                                                             |

| 104                    | _        | _                | VDD_LV                                                                      |

| 105                    | _        | _                | VDD_HV_IO_EBI                                                               |

| 106                    | _        | _                | Unbuffered PMC Trim Bandgap Reference (used in PMC)                         |

| 107                    | _        | _                | 2nd bandgap (Trimmed), (ADC mode=60, ADC register=35 from power management) |

| 108                    | _        | _                | Buffered PMC Trim Bandgap Reference (used in Pad)                           |

| 109                    | _        | _                | VSS_HV_ADV (Ground Supply for ADC)                                          |

| 110                    | _        | _                | PMC generic input 0                                                         |

Table continues on the next page...

#### MPC5777M Hardware Design Guide, Rev. 0, 05/2015

rower supply

Table 7. SARADC\_B analog test channel assignment (continued)

| SARADC_B input channel | Fast SAR | Fast SAR channel | Description                                                                              |

|------------------------|----------|------------------|------------------------------------------------------------------------------------------|

| 111                    | _        | _                | 2nd bandgap (Crude), (ADC mode=59, ADC register=36 from power management)                |

| 112                    | _        | _                | HV regulator supply LVD falling edge 280_C                                               |

| 113                    | _        | _                | HV regulator supply HVD rising edge 600_C                                                |

| 114                    | _        | _                | HV flash supply LVD falling edge 280_F                                                   |

| 115                    | _        | _                | HV flash supply HVD rising edge 360_F                                                    |

| 116                    | _        | _                | LV core supply LVD falling edge 114_C                                                    |

| 117                    | _        | _                | LV core supply HVD falling edge 140_C                                                    |

| 118                    | _        | _                | LV flash supply LVD falling edge 114_F                                                   |

| 119                    | _        | _                | Reserved                                                                                 |

| 120                    | _        | _                | Temperature sensor                                                                       |

| 121                    | _        | _                | ADC bandgap reference                                                                    |

| 122                    | _        | _                | Reserved <sup>1</sup>                                                                    |

| 123                    | _        | _                | Reserved <sup>1</sup>                                                                    |

| 124                    | _        | _                | SAR BIAS 0 — VSS_HV_ADR_S through 20 K $\Omega$ source impedance                         |

| 125                    | _        | _                | SAR BIAS 1 — 1/3 (VDD_HV_ADR_S - VSS_HV_ADR_S) through 20 $\rm K\Omega$ source impedance |

| 126                    | _        | _                | SAR BIAS 2 — 2/3 (VDD_HV_ADR_S - VSS_HV_ADR_S) through 20 $\rm K\Omega$ source impedance |

| 127                    | _        | _                | SAR BIAS 3 — (VDD_HV_ADR_S - VSS_HV_ADR_S) through 20 K $\Omega$ source impedance        |

<sup>1.</sup> Channels 122 and 123 are reserved for factory use only.

Using the SARADCB PMC generic input channel 110 the following parameters can be measured.

Table 8. Parameter monitoring via ADC channel

| PMC ADC Mode Signal<br>Description | ADC Channel Select<br>Register | ADC Mode Description                           | Nominal value expected |

|------------------------------------|--------------------------------|------------------------------------------------|------------------------|

| Internal Voltage                   | 6b101000                       | Internal Voltage                               | 0.855 V                |

| POR for security                   | 6b000001                       | Power-On-Reset on LV core supply for security  | 1.0 V                  |

| POR for security                   | 6b011111                       | Power-On-Reset on LV flash supply for security | 1.0 V                  |

| LVD096_C                           | 6b011110                       | Power-On-Reset on LV core supply               | See VLVD096 in DS      |

| LVD096_F                           | 6b011101                       | Power-On-Reset on LV flash supply              | See VLVD096 in DS      |

| LVD108_B                           | 6b011100                       | LVD on Buddy device supply                     | 1.0 V                  |

| LVD112_C                           | 6b011011                       | LVD on Low voltage supply core (cold point)    | See LVD112 in DS       |

| LVD108_F                           | 6b011010                       | LVD on Flash Low voltage supply (hot point)    | See VLVD108 in DS      |

## Table 8. Parameter monitoring via ADC channel (continued)

| PMC ADC Mode Signal<br>Description | ADC Channel Select<br>Register | ADC Mode Description                                  | Nominal value expected                                                             |

|------------------------------------|--------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|

| LVD108_P                           | 6b011001                       | LVD on PLL Low voltage supply (hot point)             | See VLVD108 in DS                                                                  |

| LVD108_C                           | 6b011000                       | LVD on Low voltage internal supply (hot point)        | See VLVD108 in DS                                                                  |

| HVD140_C                           | 6b010111                       | LV Core supply high voltage detector (cold point)     | See VHVD140 in DS                                                                  |

| HVD145_F                           | 6b111001                       | Flash LV supply high voltage detector (cold point)    | See VHVD145 in DS                                                                  |

| HVD145_C                           | 6b111000                       | LV Core supply 2nd high voltage detector (cold point) | See VHVD145 in DS                                                                  |

| Internal POR on HV                 | 6b010101                       | HV PMC supply power-On-Reset detector                 | ~Supply*1.2/<br>POR240_Threshold<br>(falling)(See DS<br>VPOR240)                   |

| LVD270_C                           | 6b010100                       | HV PMC supply low voltage detector                    | LVD270_Threshold<br>(falling) (see VLVD270 in<br>DS                                |

| HVD600_C                           | 6b010011                       | HV PMC supply high voltage detector                   | ~Supply*1.2/<br>HVD600_Threshold<br>(rising) (See VHVD360 in<br>DS)                |

| LVD270_F                           | 6b010010                       | HV flash supply low voltage detector                  | HVD_Threshold (rising)" to<br>"LVD270_Threshold<br>(falling)(see VLVD270 in<br>DS  |

| LVD295_F                           | 6b010001                       | HV flash supply low voltage detector                  | HVD_Threshold (rising)" to<br>"LVD295_Threshold<br>(falling) (see VLVD295 in<br>DS |

| HVD360_F                           | 6b010000                       | HV flash supply high voltage detector                 | ~Supply*1.2/<br>HVD360_Threshold<br>(rising) (See VHVD360 in<br>DS)                |

| LVD295_A                           | 6b001111                       | HV ADC supply low voltage detector                    | LVD295_Threshold<br>(falling) (see VLVD295 in<br>DS                                |

| LVD400_A                           | 6b001110                       | HV ADC supply low voltage detector                    | HVD_Threshold (rising)" to LVD400_Threshold (falling)                              |

| HVD600_A                           | 6b001101                       | HV ADC supply high voltage detector                   | ~Supply*1.2/<br>HVD600_Threshold<br>(rising)                                       |

| LVD270_IM                          | 6b001100                       | HV IO main supply low voltage detector                | ~Supply*1.2/<br>LVD270_Threshold<br>(falling)                                      |

| LVD360_IM                          | 6b001011                       | HV IO main supply low voltage detector                | ~Supply*1.2/<br>LVD360_Threshold<br>(falling)                                      |

#### rower supply

## Table 8. Parameter monitoring via ADC channel (continued)

| PMC ADC Mode Signal<br>Description | ADC Channel Select<br>Register | ADC Mode Description                           | Nominal value expected                        |

|------------------------------------|--------------------------------|------------------------------------------------|-----------------------------------------------|

| LVD400_IM                          | 6b001010                       | HV IO main supply low voltage detector         | ~Supply*1.2/<br>LVD_Threshold (falling)       |

| Internal POR on flash HV           | 6b001001                       | HV flash supply power-On-Reset detector        | ~Supply*1.2/<br>LVD_Threshold (falling)       |

| LVD270_IF                          | 6b001000                       | FlexRay I/O supply low voltage detector        | ~Supply*1.2/<br>LVD270_Threshold<br>(falling) |

| LVD270_IJ                          | 6b000110                       | JTAG I/O supply low voltage detector           | ~Supply*1.2/<br>LVD270_Threshold<br>(falling) |

| LVD270_O                           | 6b000100                       | Oscillator supply low voltage detector         | ~Supply*1.2/<br>LVD270_Threshold<br>(falling) |

| LVD270_EBI                         | 6b000011                       | HV IE supply low voltage detector              | ~Supply*1.2/<br>LVD270_Threshold<br>(falling) |

| LVD270_IF2                         | 6b000010                       | Second FlexRay I/O supply low voltage detector | ~Supply*1.2/<br>LVD270_Threshold<br>(falling) |

| Normal Operation Mode              | 6b000000                       | ADC channel off                                | _                                             |

| _                                  | 6b111111                       | Reserved / ADC channel off                     | _                                             |

| VDDREG                             | 6b110111                       | Scaled VDDREG supply                           | PMC supply x 1/5                              |

| VDD ADC                            | 6b110110                       | Scaled ADC supply                              | ADC supply x 1/5                              |

| VDD Oscillator                     | 6b110101                       | Scaled Oscillator supply                       | Oscillator supply x 17/60                     |

| VDD Flash                          | 6b110100                       | Scaled Flash supply                            | Flash supply (x 17/60)                        |

| VDD main I/O                       | 6b110011                       | Scaled 5V main I/O supply                      | 5V main I/O supply (x 1/5)                    |

| VDD Flexray                        | 6b110010                       | Scaled Flexray supply                          | Flexray supply x 17/60                        |

| VDD Core                           | 6b110001                       | Core supply hot Sense                          | Core supply hot Point                         |

| VDD PLL                            | 6b110000                       | PLL supply Sense                               | PLL supply Sense                              |

| VDD EBI                            | 6b101111                       | Scaled EBI supply                              | EBI supply x 17/60                            |

| VDD Flexray2                       | 6b101110                       | Scaled 2nd Flexray supply                      | 2nd Flexray supply x<br>17/60                 |

| VDD LFAST PLL                      | 6b101101                       | LFAST PLL supply                               | LFAST PLL supply,1.28 V                       |

| VDD IJ                             | 6b101100                       | Scaled Jtag supply                             | Jtag supply X17/60                            |

| LV flash supply sense              | 6b101011                       | LV flash supply sense point                    | LV flash supply sense point                   |

| buddy device supply sense          | 6b101010                       | Buddy Device supply sense point                | Buddy Device supply sense point               |

| LV core supply sense               | 6b101001                       | LV core supply cold sense point                | LV core supply                                |

| internal voltage                   | 6b100000                       | _                                              | _                                             |

| Vref0p45                           | 6b010110                       | LVD/HVD self test voltage                      | 0.47 V                                        |

| Vref0p75                           | 6b100111                       | LVD selftest voltage                           | 0.74 V                                        |

| Vref1p0                            | 6b100110                       | LVD selftest voltage                           | 1.0 V                                         |

|                                    | •                              | -                                              | -                                             |

| Table 8. | <b>Parameter</b> | monitoring | via ADC | channel | (continued) | ) |

|----------|------------------|------------|---------|---------|-------------|---|

|----------|------------------|------------|---------|---------|-------------|---|

| PMC ADC Mode Signal<br>Description | ADC Channel Select<br>Register | ADC Mode Description                               | Nominal value expected |

|------------------------------------|--------------------------------|----------------------------------------------------|------------------------|

| Vref1p5                            | 6b100101                       | HVD selftest voltage                               | 1.6 V                  |

| VDDA22A                            | 6b111100                       | pre-regulator output                               | 2.5 V                  |

| REF_1P0A                           | 6b111011                       | 1.0 V                                              | 1.0 V                  |

| VBG_REF_1P22                       | 6b111110                       | 1.2 V crude band gap                               | 1.2 V                  |

| BG1P20_REF                         | 6b111010                       | bandgap trimmed reference voltage                  | 1.2 V                  |

| VREF_SOFT                          | 6b000111                       | reference to 3.3V flash supply regulator           | 1.2 V                  |

| Vbandgap buffered                  | 6b000101                       | 1.2 V                                              | 1.2 V                  |

| BIS_VBG_REF_1P 22                  | 6b100100                       | 2nd crude band gap                                 | 1.20 V                 |

| BIS_BG1P20_REF                     | 6b100011                       | 2nd bandgap trimmed reference for flash regulators | 1.2 V                  |

| Aux Reg REF                        | 6b100010                       | Reference for Aux regulator                        | _                      |

| REF for LFAST PLL REG              | 6b100001                       | Reference to LFAST PLL regulator                   | 1.28 V                 |

| _                                  | 6b111101                       | internal voltage                                   | Reserved               |

## 3.5 Power sequence

The following section describes the power sequence and the relation between the different supplies during power-up and power-down.

The device is considered to be in a power sequence (or POWERUP state) when the device is either not supplied or is partially supplied. An internal power-on signal is used to identify POWERUP state. This signal is released high on exit of the power sequence. The power-on signal is a combination of LVDs monitoring of supplies:

- VDD LV

- VDD\_HV\_PMC

- VDD\_HV\_IO

- VDD\_HV\_FLA

The actual threshold use for each LVD depends on the configuration of the device. This is configurable by hardware (flash option bits content) or by software (LVD event configuration through register interface). Once the power-on signal has been asserted, the device configuration is reset to default power-up configuration: during the initialization phase, the device defaults to a pre-determined state for each of the LVDs, HVDs, and the internal regulators. As the flash memory becomes available, the differential read process allows the trimmed data to be available for trimming the internal LVDs, HVDs, and regulators.

## 3.5.1 Power-up sequence

In this section, the assumption is made that all supplies are low when entering the power-up sequence. Brown-out and power down sequences are specified in the following sections.

At beginning of power-up, the internal power-on signal remains low due to the parasitic diodes. As soon as the minimum threshold is reached on VDD\_LV, the power-on signal is forced low. It remains low until the power-up LVDs reach their upper (not trimmed) threshold. During power-up, all functional pins are maintained in a known state as described in the table below.

#### rower supply

#### Table 9. Functional terminals state during power-up and reset

| TERMINAL          | POWERUP <sup>2</sup>      | RESET                       | DEFAULT                     | Comments                                                     |

|-------------------|---------------------------|-----------------------------|-----------------------------|--------------------------------------------------------------|

| TYPE <sup>1</sup> | pad state                 | pad state                   | pad state <sup>3</sup>      |                                                              |

| PORST             | Strong pull-down          | Weak pull-down              | Weak pull-down              | Power-on reset pad                                           |

| ESR0 <sup>5</sup> | Strong pull-down          | Strong pull-down            | Weak pull-up                | Functional reset pad.                                        |

| ESR1              | High impedance            | Weak pull-up                | Weak pull-up                | -                                                            |

| TESTMODE          | Weak pull-down            | Weak pull-down <sup>6</sup> | Weak pull-down <sup>6</sup> | -                                                            |

| GPIO              | Weak pull-up <sup>4</sup> | Weak pull-up                | Weak pull-up                | -                                                            |

| ANALOG            | High impedance            | High impedance              | High impedance              | -                                                            |

| ERROR0            | High impedance            | High impedance              | High impedance              | During functional reset, pad state can be overridden by FCCU |

| JCOMP             | High impedance            | Weak pull-down              | Weak pull-down              | -                                                            |

| TCK               | High impedance            | Weak pull-down              | Weak pull-down              | -                                                            |

| TMS               | High impedance            | Weak pull-up                | Weak pull-up                | -                                                            |

| TDI               | High impedance            | Weak pull-up                | Weak pull-up                | -                                                            |

| TDO               | High impedance            | Weak pull-up                | High impedance              | -                                                            |

- 1. Refer to pinout information for terminal type

- 2. POWERUP state is guaranteed from VDD\_HV\_IO>1.1 V and maintained until supply cross the power-on reset threshold: VPORUP\_LV for LV supply, VPORUP\_HV for high voltage supply.

- 3. Before software configuration

- 4. Pull-down and pull-up strength are provided in the MPC5777M Datasheet Pull-up/Pull-down are activated within 2 μs after internal reset has been asserted. Actual pad transition will depend on external capacitance.

- 5. Unlike ESR0, ESR1 is provided as normal GPIO and implements weak pull-up during power-up.

- 6. An internal pull-down is implemented on the TESTMODE pin to prevent the device from entering test mode if the package TESTMODE pin is not connected. It is recommended to connect the TESTMODE pin to V<sub>SS\_HV\_IO</sub> on the board for maximum robustness, but not required. The value of TESTMODE is latched at the negation of reset and has no affect afterward. The device will not exit functional reset with the TESTMODE pin asserted during power-up. The TESTMODE pin can be connected externally directly to ground without any other components.

#### The power-up sequence is as follows:

- 1. Digital reset is asserted, ensuring that all modules registers are reset to power-on value.

- 2. The POWERUP state can be exited when both VDD\_LV and VDD\_HV are above threshold. The VDD\_LV conditions to exit POWERUP is as follows:

- LVD096\_C, LVD096\_F upper threshold is crossed

- LVD112\_C upper threshold is crossed

- 3. After both LV, HV and temperature POWERUP exit conditions have been verified, the internal power-on signal is released to all analog modules.

- 4. The internal RC oscillator module starts initialization and provides a clock to the system after TRCSTARTUP. The PMC digital interface reset is released after two RC clock cycles and LVD400\_IM is masked. All other HV LVDs remain active.

- 5. The device proceeds with the reset sequence through RGM phase PHASE0, PHASE1[DEST], PHASE2[DEST] and PHASE3[DEST].

- 6. Voltage detector (LVD/HVD) modules are trimmed at the beginning of PHASE3[DEST]. Trimming of LVDs/HVDs is done by the SSCM at low voltage. After trimming is completed, SSCM waits for PMC acknowledge to proceed with the reset sequence.

- 7. The configurable LVD/HVD modules are optionally enabled at the beginning of PHASE3[DEST]. After trimming, the PMC interface monitors all the HVD/LVD outputs that have been enabled by the flash user option bits. When all enabled LVDs/HVDs are released and the analog temporization period has elapsed, LVDs/HVDs are unmasked.

- 8. When LVD108\_C and LVD360\_C are masked, the device relies on the PORST signal to detect a voltage failure during power-up. The device must wait for PORST to be released high before proceeding with power-up sequence. This may increase the amount of time necessary to complete the reset sequence.

- 9. After all LVDs/HVDs are unmasked the SSCM proceeds with the reset sequence, eventually running full speed accesses to the extended flash option bits required to complete device configuration.

- 10. The VDD\_HV conditions to exit POWERUP are as follows:

- LVD400 IM upper threshold is crossed

- LVD360\_IM upper threshold is crossed

- LVD300\_F upper threshold is crossed

- LVD270\_xx upper threshold is crossed

## 3.5.2 Power-down sequence

In case the threshold of the higher ranges, LVDs which are configured to generate a destructive reset is crossed, but neither LVD096 nor LVD270 threshold is crossed, device enters the PHASE0 phase. The power-down sequence is entered as soon as the threshold of one of the LVD096 or LVD270 is crossed. The device enters the POWERUP state. The device supplies may then proceed to drop down to ground either through device leakage or external pull-down.

## 3.5.3 Brown-out management

During brown-out, the MPC57xx devices re-enter the POWERUP phase as soon as the threshold of either LVD096 or LVD270 is crossed.

## 3.5.4 Low voltage during crank

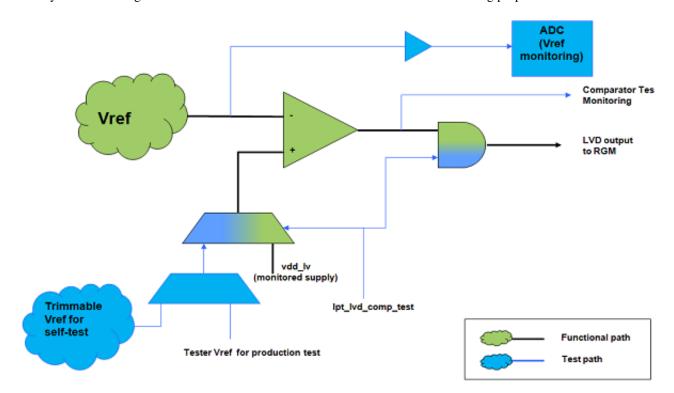

The device is able to continue operation to the minimum input voltage during cranking. In order to proceed with execution during cranking and prevent device reset, it is important to correctly configure the high voltage LVDs. Figure 3 represents a typical customer application crank profile:

#### **CIOCK Circuitry**

Note: This shows a typical customer crank voltage falling to 3.0 V. However, this is subject to change. See the data sheet for specifics.

Figure 3. Crank voltage application example

- Full parametric operation is a high voltage input between 4.5 V and 5.5 V

- Partial device operation is a voltage between 3.5 V and 4.0 V

## 4 Clock Circuitry

The MPC5777M devices can use either the on-chip oscillator with an external crystal or an external clock as the reference clock to the device. This reference is qualified in multiple manners before the PLL will begin lock operation. The "pre" FMPLL circuitry consists of an automatic level-controlled amplifier, a comparator, a loss of clock detector, and a predivider.

The most important aspects of an accurate clock source require that some care be taken in the layout and design of the circuitry around the crystal and FMPLL power supplies. Any noise in these circuits can affect the accuracy of the clock source to the FMPLL. The power supply for the PLLs is taken from VDD\_LV. The oscillator is powered from VDD\_HV\_JTAG\_OSC. Noise on these supplies can affect the accuracy and jitter performance of the oscillator and PLLs. In order to minimize any potential noise, it is recommended that the additional capacitors recommended in are fitted to the VDD\_LV and VDD\_HV\_JTAG\_OSC supplies.

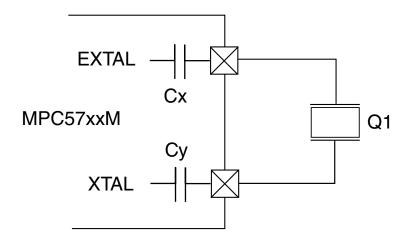

The MPC5777M features configurable internal load capacitors for 20–40 MHz external oscillators (Cx and Cy). This feature is intended to simplify the design and reduce the overall system cost by eliminating external components and reducing the PCB footprint. If an 8–16 MHz oscillator is used, then external load capacitors must be used.

If the external oscillator is to be started by hardware during reset then this requirement, the crystal frequency and the capacitance must be specified in the UTEST Miscellaneous DCF Client records field; see the MPC5777M reference manual for details. An example schematic for the external oscillator connection is shown in the figure below.

Figure 4. MPC5777M external oscillator connection

Since the layout of the module/board can affect the component values required, customers should have their board characterized by their crystal vendor to recommend values for Cx and Cy. The values shown in this document should be used as a starting point. These should be re-characterized for any change to the oscillator circuit layout, including routing changes of other circuitry near the crystal circuit.

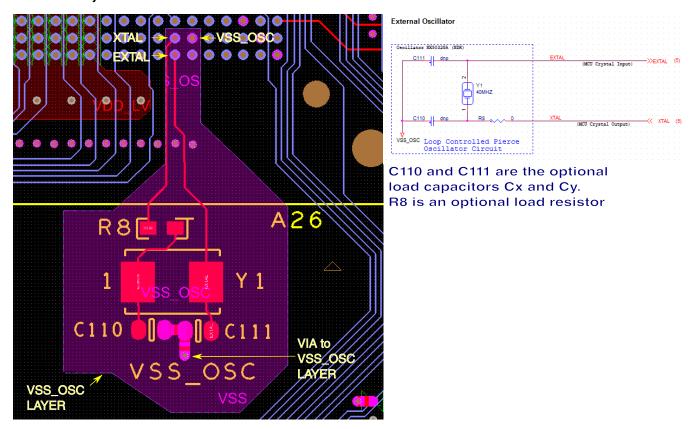

In order to minimize signal degradation and improve Electro Magnetic Compatability (EMC), following guidelines should be followed:

- The oscillator should be placed as close as possible to the MCU.

- The trace lengths of the EXTAL and XTAL crystal connections should be as short as possible.

- The lengths of the EXTAL and XTAL traces should be matched as closely as possible.

- The EXTAL and XTAL traces must be on the same layer.

- Do not allow other signals to cross the Crystal connections.

- Keep high current and high speed signals away from the crystal components.

- The VSS\_OSC connection should have its own individual isolated GND area. This can either be on a seperate layer, or as a seperate, segregated region of the GND Layer.

- The VSS\_OSC region should be connected to system ground at the the VSS\_OSC pin.

- Other than the connections shown in the above schematics, no other connections should be made to the crystal or EXTAL and XTAL device pins. Do not use XTAL to drive any other circuitry.

An example layout and accompanying schematic are shown in the figure below.

#### **CIOCK Circuitry**

Figure 5. Example crystal layout

The recommendations from the crystal manufacturer will include not only a series resistor value but also the load capacitance required for the crystal (the total crystal load capacitance is usually specified in the crystal data sheet). Keep in mind that the load capacitance is the sum of the following:

- Physical capacitors (Cx and Cy)

- Capacitance of the MCU

- Capacitive loading of the board (CPCB)

- Pin capacitance (CMCU\_PIN) of the MCU EXTAL and XTAL balls (BGA balls are specified as 7 pF maximum)

The requirement for the crystal vendor to measure the customer board is due to the board capacitance effect on the crystal load capacitors.

Generally, the method to calculate the capacitors values to use for Cx and Cy is given by the following:

$$CA = CB = 2 \times CL$$

$$CA = Cx + Cs xtal + CPCB$$

$$CB = Cy + Cs_xtal + CPCB$$

CL should come from the crystal specifications (requirements). CPCB should also include any socket capacitance if a socket is used. Cs\_xtal is the total on chip stray capacitance on the XTAL/EXTAL pins and is listed in the device data sheet as 8 pF.

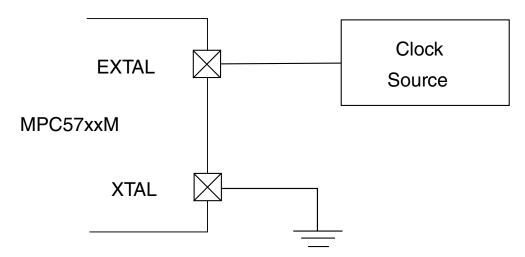

## 4.1 External clock connections

If an external clock is being used as clock reference to the MCU, then the XTAL pin should be connected to ground and the clock should be provided to EXTAL as shown in the figure below.

Figure 6. MPC5777M external clock connection

## 5 Device Reset Configuration

The MPC57xxM MCUs require only very basic external reset circuitry. External circuitry for device configuration is not required. The devices are configured during reset based on data in flash memory.

## 5.1 External reset signals

The MPC57xxM devices feature two external reset signals:

- Power-on reset (PORST)

- External signal reset (ESR0)

Both external reset signals are bidirectional and active-low. ESR0 indicates if the the device is active (high signal) or in reset. It is thus weak pullup after the reset sequence has completed. If not used, it can be left floating. A falling edge on this pin will trigger a functional reset to the Reset Generation Module. Forcing this pin low will keep the device in the last phase of the reset sequence (Phase3[Functional]).

After reset, PORST is configured as weak pulldown for safety reasons. In case PORST is disconnected the device will remain in reset. PORST is released when the device leaves the power-up state of the RGM. PORST has to be forced high externally so the device will leave the reset state. The internal weak pulldown of PORST is max 100  $\mu$ A. It is recommended to use an external 4.7 k $\Omega$  pullup resistor to ensure remaining safely above the threshold.

## 6 Recommended debug connectors and connector pinout definitions

The MPC57xxM family implements the newly added (in the IEEE-ISTO 5001<sup>TM</sup>-2011 version of the standard) high speed serial Nexus trace Auxiliary Port that uses the Xilinx<sup>TM</sup> Aurora physical interface. The Aurora interface allows the Nexus protocol information to be transmitted serially at a high date rate over one or more Aurora lanes. The Aurora protocol handles the encoding of the data and stripes the information across the number of lanes available on the device.

#### necommended debug connectors and connector pinout definitions

In addition to the high speed Nexus serial trace port, a new option is added in the MPC57xxM family devices to support a high speed calibration interface for run control and memory access: a High Speed Calibration interface based on JTAG and LFAST. The High Speed Calibration LFAST interface signals are alternate functions on the JTAG pins of the device. The device will start up in JTAG mode and the tool can request that the JTAG interface transitions to the High Speed Calibration LFAST interface.

This section gives recommendations for connections and pinouts of the available debug interfaces. For additional information on the MPC57xxM debug connector options and signal descriptions, see application note AN4225, "MPC57xxM C55 Family Debug Overview" available in freescale.com

Table 10 shows the recommended connectors for different applications for the MPC57xxM Family.

| Connector style                     | Target system part number | Connector type                                                                                                                                   |

|-------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-pin BERG JTAG only               | 3M 2514-6002UB            | JTAG-only configuration <sup>1</sup>                                                                                                             |

| 10-pin calibration connector        | Samtec TFM-105            | See separate High Speed Calibration<br>LFAST interface custom connector<br>documentation.                                                        |

| 17-position (2 x 17, 34-pin) Samtec | Samtec ASP-137973-01      | Serial Nexus configuration (supports up to 8 simplex lanes, less lanes are available if duplex support or High Speed Calibration LFAST interface |

Table 10. Recommended connectors

1. The existing MPC5500 and MPC5600 JTAG connector will be used on future MPC57xx devices.

#### **NOTE**

Whichever connector is chosen, "keep-out" areas may be required by some tools. Consult the preferred tool vendor to determine any area that must remain clear around the debug connector. Some tool vendors may include an extension cable to minimize "keep-out" areas, but use of an extension will degrade the signal. In many cases, this degradation will be insignificant, but it depends on many factors including clock frequency and target board layout.

## 6.1 MPC57xx JTAG connector

Table 11 shows the pinout of the recommended JTAG connector to support the MPC57xxM devices. This is an alternate JTAG only connector. It is not ideal for signal placement for ribbon cable used to support the High Speed Calibration LFAST interface.

The recommended connector for the target system is Tyco part number 2514-6002UB.

#### NOTE

This pinout is similar to the previous Freescale MPC5500/MPC5600 family of devices. The differences are noted below. The MPC5500/MPC5600 family did not have a calibration option.

Table 11. Recommended JTAG connector pinout

| Description | Pin | Pin | Description |

|-------------|-----|-----|-------------|

| TDI         | 1   | 2   | GND         |

| TDO         | 3   | 4   | GND         |

| TCK         | 5   | 6   | GND         |

Recommended debug connectors and connector pinout definitions

Table 11. Recommended JTAG connector pinout (continued)

| Description       | Pin | Pin | Description        |

|-------------------|-----|-----|--------------------|

| EVTI0             | 7   | 8   | PORST <sup>1</sup> |

| ESR0 <sup>2</sup> | 9   | 10  | TMS                |

| VREF              | 11  | 12  | GND                |

| EVTO0             | 13  | 14  | JCOMP              |

- 1. This pin was a no connect on the MPC55xx and MPC56xx devices.

- 2. Early versions of this document put the PORST signal on this pin. PORST and ESRO have been swapped to make it more backward compatible.

## 6.2 MPC5777M high-speed Nexus serial trace connector

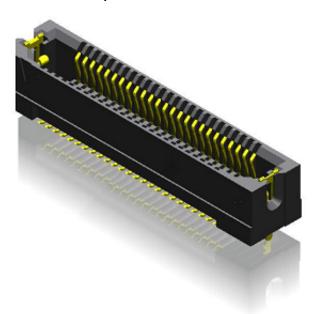

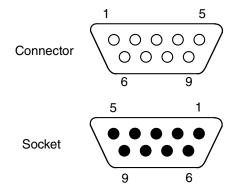

For high speed Nexus Aurora trace applications, the Samtec<sup>TM</sup> ERF8 Series connector is recommended in the IEEE-ISTO 5001<sup>TM</sup>-2011 standard. For the MPC57xx family, the 17 position (34 pins) connector is recommended. The part number of the Samtec connectors are shown in Table 12.

Table 12. Recommended high-speed serial trace connector part numbers

| Connector | Part number (Samtec) | Style                                    | Description                      |

|-----------|----------------------|------------------------------------------|----------------------------------|

| HS34      | ASP-137973-01        | Samtec ERF8 Series, 17 position by 2 row | Vertical mount for MCU module    |

| HS34      | TBD                  | Samtec ERF8 Series, 17 position by 2 row | Right Angle mount for MCU module |

The Samtec ERF8 series of connectors is intended for high speed applications requiring a minimum footprint size with a reliable, latching connection. The recommended connector has two rows of seventeen contacts each with a spacing of 0.8 mm. The connector provides isolation between the high-speed trace signals and the low-speed JTAG and control signals. It also provides ample ground connections to ensure signal integrity. If at all possible, the connector should be placed onto the target system with the even numbered pins nearest the edge of the printed circuit board.

Figure 7 is courtesy of Samtec U.S.A (http://www.samtec.com/search/NEXUS.aspx).

#### necommended debug connectors and connector pinout definitions

Figure 7. Recommended Nexus connector

The table below shows the recommended pinout for the Samtec connector.

Table 13. MPC5777M high-speed serial trace connector

| Function            | Pin No | Pin No | Function         |

|---------------------|--------|--------|------------------|

| TX0+                | 1      | 2      | VREF             |

| TX0-                | 3      | 4      | TCK/TCKC/DRCLK   |

| VSS                 | 5      | 6      | TMS/TMSC/TxDataP |

| TX1+                | 7      | 8      | TDI/TxDataN      |

| TX1-                | 9      | 10     | TDO/RxDataP      |

| VSS                 | 11     | 12     | JCOMP/RxDataN    |

| TX2+                | 13     | 14     | EVTI1            |

| TX2-                | 15     | 16     | EVTI0            |

| VSS                 | 17     | 18     | EVTO0            |

| TX3+                | 19     | 20     | PORST            |

| TX3-                | 21     | 22     | ESR0             |

| VSS                 | 23     | 24     | VSS              |

| (TX4+)              | 25     | 26     | CLK+             |

| (TX4-) <sup>1</sup> | 27     | 28     | CLK-             |

| VSS                 | 29     | 30     | VSS              |

| (TX5+) <sup>1</sup> | 31     | 32     | EVTO1            |

| (TX5-) <sup>1</sup> | 33     | 34     | N/C              |

| VSS                 | GND    | GND    | VSS              |

#### 1. Reserved for TXn signals, not currently used.

It is recommended that the "even" side of the connector be mounted closer to the edge of the printed circuit board to facilitate a direct connection to the tool.

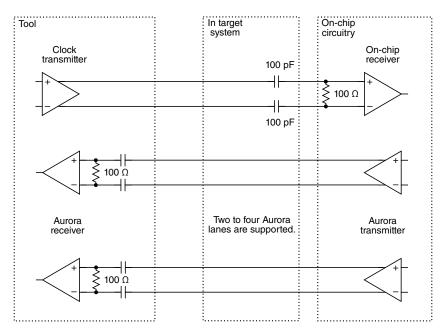

## 6.3 Nexus Aurora target system requirements

The Nexus Aurora interface requires termination and AC coupling of the signals between the target system and the tool. The termination resistor for the Aurora clock is located inside the MCU. An external termination resistor is required. The transmit termination resistor must be implemented in the target system; however, it may be implemented internal to the FPGA of the tool.

Figure 8. Nexus Aurora termination and coupling circuits

## 6.4 Minimum external circuitry

Next to the connector, additional circuitry is required for the Nexus/JTAG debug circuitry. The MPC57xx devices include internal pull devices that ensure the pins remain in a safe state; however, if there is additional circuitry connected to the Nexus/JTAG pins, or long traces that could be affected by other signals (due to crosstalk from high-current or high-speed signals), a minimum number of external pull resistors can be added to ensure proper operation under all conditions.

| Nexus/JTAG signal | Resistor/capacitor direction and value | Description                                                                                                           |

|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| JCOMP             | 10 kΩ pulldown                         | Holds debug port in reset and prevents any debug commands from interfering with the normal operation of the MCU       |

| PORST             | 4.7 kΩ pullup                          | The PORST input should be driven from an open collector output; therefore, it requires a pull-up resistor for the MCU |

| ESR0              | 4.7 kΩ pullup                          | The ESRO input should be driven from an open collector output; therefore, it requires a pull-up resistor for the MCU  |

Table 14. Optional external pullups/downs

#### External Bus Interface (EBI)

Table 14. Optional external pullups/downs (continued)

| Nexus/JTAG signal | Resistor/capacitor direction and value | Description                                                                                                                                                                                                                                                       |

|-------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nexus CLKP & CLKN | 100 nF on the signal lines             | The LVDS Nexus clock signals require a capacitor for high speed functionality                                                                                                                                                                                     |

| EVTI              | 10 kΩ pullup                           | A pullup resistor prevents debug mode from being forced after reset if debug mode is enabled (JCOMP = high). It also prevents breakpoints from being forced if debug mode is enabled.  NOTE: In almost all situations, a resistor is not required on this signal. |

In addition to the pullup and pulldown resistors, some systems may want to use buffers between the JTAG connector inputs (JCOMP, TDI, TDO, TMS, EVTI, EVTO, PORST, and ESR0) and the MCU. This will prevent over-voltage conditions from causing damage to the MCU signals. Normal systems should not require this circuitry, but it is helpful in systems that can be exposed to improper connections that provide voltages that are outside the operating conditions of the MCU. A common circuit to use is the Texas Instruments<sup>TM</sup> SN74CBTLV38615. This device is a bus switch that implements a bidirectional interface between two terminals with less than 5  $\Omega$  of resistance. It should be powered by the same supply that powers the debug port. The device enable should be connected to ground for the interface to be enabled whenever the debug port on the MCU is powered. This circuit provides a high impedance to the tool when the debug port is powered off.

## 7 External Bus Interface (EBI)

The External Bus Interface (EBI) handles the transfer of information between the internal busses and the memories or peripherals in the external address space. The EBI includes a memory controller that generates interface signals to support a variety of external memories. This includes Single Data Rate (SDR) synchronus burst mode flash and SRAM, and asynchronous/legacy memories FLASH and SRAM. It supports 3 regions (via chip selects), each with its own programmed attributes.

The EBI has the following features. For detailed information please see the MPC5777M reference manual.

- 32-Bit address bus with transfer size indication.

- 32-Bit Data bus (16-bit Data Bus Mode also supported)

- Memory controller with support for various memory types:

- · synchronous burst SDR flash and SRAM

- · asynchronous/legacy flash and SRAM

- Burst support (wrapped only)

- Port size configuration per chip select (16 or 32 bits)

- Support for Dynamic Calibration with up to 3 chip-selects

- Four Write/Byte Enable (WE[0:3]/BE [0:3]) signals

- Slower-speed clock modes

- Stop and Module Disable Modes for power savings

- Optional automatic CLKOUT gating to save power and reduce EMI

- Misaligned access support

- Compatible with MPC5xx

- Compatible with MPC5xx external bus (with some limitations)

The EBI signal properties are shown in Table 14. The assosciated pad configuration settings for MPC5777M are shown in the table below.

## Table 15. Signal properties

| Name                       | I/O Type | Function               | Pull <sup>1</sup> |

|----------------------------|----------|------------------------|-------------------|

| ADDR[8:31]                 | I/O      | Address bus            | -                 |

| ADDR[8:11]_WE[3:0]/BE[3:0] |          |                        |                   |

| BDIP                       | Output   | Burst Data in Progress | Up                |

| CLKOUT <sup>2</sup>        | Output   | Clockout               | -                 |

| <u>CS</u> [0:2]            | Output   | Chip Selects           | -                 |

| DATA[0:31]                 | I/O      | Data bus <sup>3</sup>  | -                 |

| OE                         | Output   | Output Enable          | Up                |

| RD_WR                      | I/O      | Read_Write             | Up                |

| TS                         | I/O      | Transfer Start         | Up                |

- 1. This column shows which signals require a weak pullup or pulldown. The EBI block does not contain these pullup/pulldown devices within the block. They are assumed to be in another module of the MCU (for example; pads module).

- 2. The CLKOUT signal is driven by the System Clock Block outside the EBI.

- 3. In Address/Data multiplexing modes, Data will also show the address during the address phase.

## Table 16. EBI pads configuration

| Pin    | MSCR | Function | Description                  | BGA416 | BGA512 |

|--------|------|----------|------------------------------|--------|--------|

| PV[0]  | 289  | CLKOUT   | EBI Clock Output             | AA26   | AG30   |

| PV[1]  | 290  | /OE      | EBI Output Enable Signal     | AA24   | AF30   |

| PV[2]  | 291  | RD_WR    | EBI Read_Write Enable Output | AA23   | AF29   |

| PV[3]  | 292  | /CS2     | EBI Chip Select 2 Output     | Y24    | AE30   |

| PV[4]  | 293  | /CS1     | EBI Chip Select 1 Output     | Y25    | AE29   |

| PV[5]  | 294  | /CS0     | EBI Chip Select 0 Output     | Y26    | AD30   |

| PV[7]  | 296  | /TS      | EBI Transfer Start Output    | W24    | AD29   |

| PS[0]  | 257  | D30      | EBI Data[30] Signal          | AD18   | AJ12   |

| PS[1]  | 258  | D29      | EBI Data[29] Signal          | AE18   | AK12   |

| PS[2]  | 259  | D28      | EBI Data[28] Signal          | AF18   | AJ13   |

| PS[3]  | 260  | D26      | EBI Data[26] Signal          | AD19   | AK13   |

| PS[4]  | 261  | D24      | EBI Data[24] Signal          | AE19   | AJ14   |

| PS[5]  | 262  | D23      | EBI Data[23] Signal          | AF19   | AK14   |

| PS[6]  | 263  | D20      | EBI Data[20] Signal          | AD20   | AJ15   |

| PS[7]  | 264  | D16      | EBI Data[16] Signal          | AE20   | AK15   |

| PS[8]  | 265  | D31      | EBI Data[31] Signal (LSB)    | AF20   | AJ16   |

| PS[9]  | 266  | D27      | EBI Data[27] Signal          | AD21   | AK16   |

| PS[10] | 267  | D21      | EBI Data[21] Signal          | AE21   | AJ17   |

| PS[11] | 268  | D25      | EBI Data[25] Signal          | AF21   | AK17   |

| PS[12] | 269  | D19      | EBI Data[19] Signal          | AD22   | AJ18   |

| PS[13] | 270  | D22      | EBI Data[22] Signal          | AE22   | AK18   |

| PS[14] | 271  | D18      | EBI Data[18] Signal          | AD23   | AJ19   |

| PS[15] | 272  | D17      | EBI Data[17] Signal          | AE23   | AK19   |

#### External Bus Interface (EBI)