# AN5317

# Loading Code on Cortex-M from U-Boot/Linux for the i.MX Asymmetric Multi-Processing Application Processors

Rev. 2 — 18 November 2021 Application Note

### 1 Introduction

There is a growing number of embedded use cases that require concurrent execution of isolated and secure software environments. Multiple software execution environments are useful for:

- · Off-loading tasks and improving real-time performance

- · Increasing system integrity and security

- · Optimizing power consumption

The i.MX 8M, i.MX 8, i.MX 8X, i.MX 7D/S/UL, and i.MX 6SoloX SoC families offer Asymmetric Multi-Processing (AMP) solutions with both Arm® Cortex®-A processors and Cortex-M4 microcontroller on a single SoC. The cores can be partitioned into two respective processing domains that can be programmed to run a different OS to cater for the real-time latency and application processing requirements.

In some applications, it is very useful to have the Arm Cortex-A processors reload code into the Cortex-M4 microcontroller. This application note shows

how to reload code on Cortex-M from the Linux shell/U-Boot using the Arm Cortex-A processor. The same method can be used for any other OS or bare metal implementation.

This application note shows how to load code into Cortex-M from the software running on Cortex-A cores.

The following table lists some NXP SoCs that can be used in the AMP configuration and the software support for Cortex-M loading from a side in U-Boot and Linux starting with NXP Linux BSP versions  $\geq L5.10.35_2.0.0$ .

Table 1. Examples of NXP SoCs that can be used in AMP configuration

| SoC name    | U-Boot - Cortex-M load support | RemoteProc support |

|-------------|--------------------------------|--------------------|

| i.MX 8QM    | √                              | √                  |

| i.MX 8QXP   | √                              | √                  |

| i.MX 8MP    | √                              | √                  |

| i.MX 8MQ    | √                              | √                  |

| i.MX 8MM    | √                              | √                  |

| i.MX 8MN    | √                              | √                  |

| i.MX 7D/S   | √                              | √                  |

| i.MX 6SoloX | √                              | √                  |

### **Contents**

| 1  | Introduction                       | • |

|----|------------------------------------|---|

| 2  | Overview of i.MX 8QM/QXP           |   |

|    | implementations                    |   |

| 3  | Overview of i.MX 8M family         |   |

|    | implementations                    | 2 |

| 4  | Overview of i.MX 7Dual/7Solo and   |   |

|    | i.MX 6SoloX implementations        | 2 |

| 5  | Reloading code on i.MX 8QM/QXP     |   |

|    |                                    | 3 |

| 6  | Reloading code on i.MX 8M family   |   |

|    |                                    | ٠ |

| 7  | Reloading code on i.MX 7Dual/7Sole | C |

|    |                                    | ٤ |

| 8  | Reloading code on i.MX 6SoloX      | ί |

| 9  | Linux Remote Processor (RPROC)     |   |

|    | framework                          |   |

| 10 | References14                       | 4 |

| 11 | Povision history 1                 | , |

# 2 Overview of i.MX 8QM/QXP implementations

The i.MX 8QM application processor provides a powerful fully coherent core complex based on a dual (2x) Cortex-A72 cluster for use cases requiring high computing performances, a quad (4x) Cortex-A53 cluster running most of the use cases at a lower power consumption and two clusters, each with one Cortex-M4 for real-time performance.

The i.MX 8QXP application processor provides a quad Arm Cortex-A35 cluster providing full 64-bit ARMv8-A support while maintaining seamless backward compatibility with 32-bit ARMv7-A software and a single Arm Cortex-M4.

The current U-Boot source code for both i.MX 8QM and i.MX 8QXP application processors provides a bootaux and a loadm4image <coreid> command that helps with loading the code to the Cortex-M4 core and bringing it up. For example, loading the sensor\_demo.bin file to location 0x80280000 and booting the Cortex-M4\_0 core with the image loaded can be done by running the following command: "run m4boot\_0" which implementation is "run loadm4image\_0; dcache flush; bootaux \${loadaddr} 0", where loadm4image\_0 is "fatload mmc \${mmcdev}:\${mmcpart} \${loadaddr} \${m4\_0\_image}" with loadaddr=0x80280000 and m4\_0\_image= sensor\_demo.bin.

This U-Boot feature is useful to bring the Cortex-M4 core up as soon as possible after the boot up or power-on reset, with the existing implementation every time a user wants to modify the application. U-Boot must be reconfigured. i.MX 8QM/iMX 8QXP introduces the System Controller Firmware (SCFW) for interaction with hardware. Controlling the Cortex-M4 from Linux is easier, enabling users to start, stop, and reload it. This implementation does not allow users to reload another application while a task is already running on the Cortex-M4 core. This application note describes the interaction with Cortex-M4 cores from the Linux shell via SCFW API.

# 3 Overview of i.MX 8M family implementations

The i.MX 8MQ/i.MX 8MM application processors offer a quad Arm Cortex-A53 cluster providing full 64-bit ARMv8-A support and also a single Arm Cortex-M4 processor.

The i.MX 8MP/i.MX 8MN application processors provide a guad Arm Cortex-A53 cluster and a single Arm Cortex-M7 processor.

The current U-Boot source code for both i.MX 8MM and i.MX 8MN application processors provides bootaux and fatload commands that help users with loading the code into the Cortex-M4/Cortex-M7 core and bringing it up. For example, "fatload mmc 0:1 0x7e0000 sensor\_demo.bin" loads the sensor\_demo.bin file to location 0x7e0000 and "bootaux 0x7e00000" boots the Cortex-M4/Cortex-M7 core with the image loaded at *0x007e\_0000*.

# 4 Overview of i.MX 7Dual/7Solo and i.MX 6SoloX implementations

There are many similarities between the i.MX 7Dual/7Solo and i.MX 6SoloX application processors in terms of where the TCM\_U and TCM\_L (Tightly Coupled Memory - Upper/Lower) memories are located. However, the boot vector and the specific register to issue the platform reset and reset the Cortex-M4 are different on the two application processors. The bit locations inside the registers for both i.MX 7Dual/7Solo and i.MX 6SoloX application processors are also different.

The i.MX 7Dual/7Solo application processor provides a multicore solution of Arm Cortex-A7 cores (dual or single) and a single Arm Cortex-M4 core.

The i.MX 6SoloX application processor provides a single Arm Cortex-A9 and a single Arm Cortex-M4. The Arm Cortex-A7 on i.MX 7Dual/7Solo and the Arm Cortex-A9 on i.MX 6SoloX are both capable of booting using different interfaces and they are also responsible for bringing up the different interfaces of the chip. It is the responsibility of Cortex-A7 on i.MX 7Dual/7Solo application processors and Cortex-A9 on i.MX 6SoloX application processors to enable the Cortex-M4 core.

The current U-Boot source code for both i.MX 7Dual/7Solo and i.MX 6SoloX application processors provides bootaux and fatload commands that help users with loading the code to the Cortex-M4 core and bringing it up. For example, "fatload mmc 0:1 0x7f8000 sensor\_demo.bin" loads the sensor\_demo.bin file to location 0x7f8000 and "bootaux 0x7f80000" boots the Cortex-M4 core with the image loaded at 0x007f\_8000.

Although this feature is useful to bring the Cortex-M4 core up as soon as possible after the boot up or power-on reset (with the existing implementation every time a user wants to modify the application), the U-Boot must be reconfigured. This implementation does not allow users to reload another application while a task is already running on the Cortex-M4 core. This application note describes the registers that are required to be programmed to reload the application from the Linux shell.

For this application note, we assume that the Cortex-M4 core is compiled to execute from the TCM L and TCM U on the chip memories. We also assume that the Cortex-M4 clock is enabled. Users using U-Boot can enable the clock with the bootaux command by loading a primary image which, on the Cortex-M4 side, tells the Linux kernel not to disable the Cortex-M4 clock when the Linux kernel takes over. If you do not run the U-Boot and want to enable the clock of the Cortex-M4, see the respective clock chapters in the i.MX 7Dual Applications Processor Reference Manual (document IMX7DRM) and the i.MX 6SoloX Applications Processor Reference Manual (document IMX6SXRM).

## 5 Reloading code on i.MX 8QM/QXP

### 5.1 On-chip memory view from each Arm core on i.MX 8QM/8QXP

The memory view of different peripherals is different between the Cortex-A and Cortex-M4 sides. Table 2 shows only the memory areas relevant for this application note. For more details, see the Memory Map chapter in the i.MX 8QM/QXP Applications Processor Reference Manual.

i.MX 8QM has two Cortex-M4 cores, each with their own cluster. i.MX 8QXP has one Cortex-M4 core. The Cortex-M4 0 from both platforms has the memory map even for the TCM memory.

Table 2. Start and end addresses of different memories from Cortex-M4 side on i.MX

| Peripheral | Start address Cortex-M4_0 | End address<br>Cortex-M4_0 | Start address Cortex-M4_1 | End address<br>Cortex-M4_1 | Size   |

|------------|---------------------------|----------------------------|---------------------------|----------------------------|--------|

| TCM_L      | 0x34FE_0000               | 0x34FF_FFFF                | 0x38FE_0000               | 0x38FF_FFFF                | 128 KB |

| TCM_H      | 0x3500_0000               | 0x3501_FFFF                | 0x3900_0000               | 0x3901_FFFF                | 128 KB |

### 5.2 Detailed procedure

To reload the code on the Cortex-M4 core using the Cortex-A processor on i.MX 8QM/QXP, follow the steps below if M4 resources belong to the Cortex-A partition:

- 1. Open an IPC channel to communicate with the SCFW that runs on the SCU using the sc\_ipc\_open (sc\_ipc\_t \_ ipc, sc\_ipc\_id\_t id) function.

- 2. Issue a software platform stop for the Cortex-M4 core using the sc\_pm\_cpu\_start (sc\_ipc\_t ipc, sc\_rsrc\_t resource, bool enable, sc\_faddr\_t address) function.

- 3. Issue a software platform power off for the Cortex-M4 core using the sc\_pm\_set\_resource\_power\_mode (sc\_ipc\_t ipc, sc\_rsrc\_t resource, sc\_pm\_power\_mode\_t mode) function. Power on the Cortex-M4 core using the above function. This step ensures that the TCM\_L memory is reset.

- 4. Load the code for the Cortex-M4 processor into the TCM\_L memory. For this application, we assume that the Cortex-M4 code is linked to the TCM\_L memory. Program the FreeRTOS binary file to the TCM\_L address.

- 5. When the image is loaded, start the Cortex-M4 core using the sc\_pm\_cpu\_start (sc\_ipc\_t ipc, sc\_rsrc\_t resource, bool enable, sc\_faddr\_t address) function.

# 6 Reloading code on i.MX 8M family

### 6.1 On-chip memory view from each Arm core on i.MX 8M SoC

The memory view of different peripherals is different between the Cortex-A53 and Cortex-M4/M7 sides. Table 3 and Table 4 show only the memory areas relevant for this application note. For more details, see the Memory Map chapter in the i.MX 8MM/8MN Applications Processor Reference Manual.

| NOTE                                                                                                       |

|------------------------------------------------------------------------------------------------------------|

| The TCM memory can be accessed from the A cores using the Cortex M platform-specific areas from the system |

| memory map. The TCM memory is mapped in the same address ranges as those that Cortex-M cores see as their  |

| TCM memory.                                                                                                |

|                                                                                                            |

Table 3. Start and end addresses of different memories from Cortex-M4 side on i.MX8MQ and i.MX8MM

| Peripheral | Start address Cortex-A53 | End address<br>Cortex-A53 | Start address Cortex-M4 | End address<br>Cortex-M4 | Size   |

|------------|--------------------------|---------------------------|-------------------------|--------------------------|--------|

| TCM_L      | 0x007E_0000              | 0x007F_FFFF               | 0x1FFE_0000             | 0x1FFF_FFFF              | 128 KB |

| TCM_H      | 0x0080_0000              | 0x0081_FFFF               | 0x2000_0000             | 0x2001_FFFF              | 128 KB |

Table 4. Start and end addresses of different memories from Cortex-M7 side on i.MX8MN and i.MX8MP

| Peripheral | Start address Cortex-A53 | End address<br>Cortex-A53 | Start address Cortex-M7 | End address<br>Cortex-M7 | Size   |

|------------|--------------------------|---------------------------|-------------------------|--------------------------|--------|

| ITCM       | 0x007E_0000              | 0x007F_FFFF               | 0x0000_0000             | 0x0001_FFFF              | 128 KB |

| DTCM       | 0x0080_0000              | 0x0081_FFFF               | 0x2000_0000             | 0x2001_FFFF              | 128 KB |

### 6.2 Detailed procedure

To reload the code on the Cortex-M4 core using the Cortex-A53 processor on i.MX 8MM, follow the steps below:

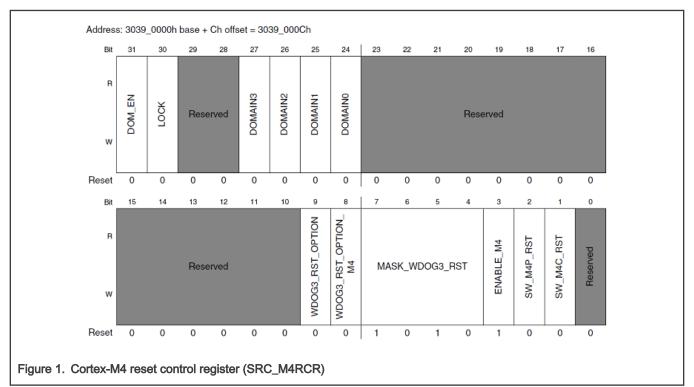

- 1. Issue a software platform reset by setting up SW\_M4P\_RST (Bit 2) in the SRC\_M4RCR (SRC\_M4RCR[2]) register. Issuing a platform reset resets the Cortex-M4 cores and their associated memories. The address of the SRC M4RCR register is 0x3039\_000C for the i.MX 8MM SoC.

- 2. Load the code for the Cortex-M4 processor into the TCM L memory. For this application, we assume that the Cortex-M4 code is compiled to execute from the TCM\_L memory. In Table 3, the TCM\_L address for the Cortex-A53 side is 0x007E\_0000. Program the FreeRTOS binary file to that address.

- 3. When the file is loaded, the next step is to set ENABLE\_M4 (Bit 3) in the SRC\_M4RCR (SRC\_M4RCR[3]) register. Because bootaux already booted a primary image, this bit should be 1. Performing a platform reset using SW\_M4P\_RST (Bit 2) in the SRC\_M4RCR (SRC\_M4RCR[2]) register does not clear this bit. The last step is to set the SW\_M4C\_RST (Bit 1) in the SRC\_M4RCR (SRC\_M4RCR[1]) register, which boots the new code in the Cortex-M4 processor.

To reload the code on the Cortex-M7 core using the Cortex-A53 processor on i.MX 8MN, follow the steps below:

- Issue a software core reset by setting up SW\_M7C\_RST (Bit 1) in the SRC\_M7RCR (SRC\_M7RCR[2]) register. Issuing a core reset resets the Cortex-M7 core and the associated memories. The address of the SRC\_M7RCR register is 0x3039 000C for the i.MX 8MN SoC.

- 2. Load the code for the Cortex-M7 processor into the ITCM memory. For this application, we assume that the Cortex-M7 code is compiled to execute from the ITCM memory. In Table 4, the ITCM address for the Cortex-A53 side is 0x007E\_0000. Program the binary file generated by FreeRTOS to that address.

- 3. When the file is loaded, the next step is to set the ENABLE\_M7 (Bit 3) in the SRC\_M7RCR (SRC\_M7RCR[3]) register. Because bootaux already booted a primary image, this bit should be 1. Performing a core reset using SW\_M7C\_RST

(Bit 1) in the **SRC\_M7RCR** (SRC\_M7RCR[1]) register does not clear this bit. The last step is to set the **SW\_M7C\_RST** (Bit 1) in the **SRC\_M7RCR** (SRC\_M7RCR[1]) register, which boots the new code in the Cortex-M4 processor.

# 7 Reloading code on i.MX 7Dual/7Solo

### 7.1 On-chip memory view from each Arm core on i.MX 7Dual/7Solo

The memory view of different peripherals is different between the Cortex-A7 and Cortex-M4 sides. Table 5 shows only the memory areas relevant for this application note. For more details, see the Memory Map chapter in the *i.MX 7Dual Applications Processor Reference Manual* (document IMX7DRM).

Table 5. Start and end addresses of different memories for Cortex-A7 and Cortex-M4 sides

| Peripheral | Start address<br>Cortex-A7 | End address<br>Cortex-A7 | Start address Cortex-M4 side | End address<br>Cortex-M4 side | Size  |

|------------|----------------------------|--------------------------|------------------------------|-------------------------------|-------|

| OCRAM_S    | 0x0018_0000                | 0x0018_7FFF              | 0x2018_0000                  | 0x2018_7FFF                   | 32 KB |

| TCM_L      | 0x007F_8000                | 0x007F_7FFF              | 0x1FFF_8000                  | 0x1FFF_FFFF                   | 32 KB |

| TCM_H      | 0x0080_0000                | 0x0080_7FFF              | 0x2000_0000                  | 0x2000_7FFF                   | 32 KB |

### 7.2 Detailed procedure

To reload the code on the Cortex-M4 core using the Cortex-A7 processor on i.MX 7Dual/7Solo, follow the steps below:

- Issue a software platform reset by setting up SW\_M4P\_RST (Bit 2) in the SRC\_M4RCR (SRC\_M4RCR[2]) register. Issuing a platform reset resets the Cortex-M4 cores and associated memories. The address of the SRC\_M4RCR register is 0x3039\_000C for i.MX 7Dual/7Solo SoC.

- 2. Load the code for the Cortex-M4 processor into the TCM\_L memory. For this application, we assume that the Cortex-M4 code is compiled to execute from the TCM\_L memory. In Table 5, the TCM\_L address from the Cortex-A7 side is 0x007F\_8000. Program the FreeRTOS binary file to that address.

- 3. When the file is loaded, set up the Stack and PC pointer in the OCRAM\_S memory. After reset, the processor uses the OCRAM\_S start address (0x0018\_0000) as the first instruction. For this implementation, the stack value is the first four bytes found in the binary file generated for the Cortex-M4 processor using FreeRTOS source. The PC value is also 4 bytes long and located at an offset of 0x4 in the binary file. This PC value is written to the OCRAM\_S base address plus 4 which is (0x0018\_0004) for this platform. Table 6 further clarifies the Stack and PC addresses.

Table 6. Boot vectors' location for Cortex-M4 core

| Boot vectors    | OCRAM_S location for boot vectors | Location of boot vectors in binary file |

|-----------------|-----------------------------------|-----------------------------------------|

| Stack pointer   | 0x0018_0000                       | First 4 bytes                           |

| Program counter | 0x0018_0004                       | 4 bytes after first 4 bytes             |

4. When the start-up address in the OCRAM\_S is adjusted according to the binary file, the file is loaded into the memory. The next step is to set the **ENABLE\_M4** (Bit 3) in the **SRC\_M4RCR** (SRC\_M4RCR[3]) register. Because *bootaux* already booted a primary image, this bit should be 1. Performing a platform reset using **SW\_M4P\_RST** (Bit 2) in the

Application Note 5 / 15

**SRC\_M4RCR** (SRC\_M4RCR[2]) register does not clear this bit. The last step is to set the **SW\_M4C\_RST** (Bit 1) in the **SRC\_M4RCR** (SRC\_M4RCR[1]) register, which boots the new code on the Cortex-M4 processor.

5. Repeat steps 1-3 to reload a new image. More details about the SRC\_M4RCR register are shown in Figure 1.

### 7.3 Steps for reloading code on i.MX 7Dual/7Solo

The steps required to reload code on i.MX 7Dual/7Solo are as follows:

- 1. Issue a platform reset by setting the SRC\_M4RCR[2] bit in the SRC\_MRCR register.

- 2. Wait for SRC\_M4RCR[2] to be cleared.

- 3. Set the stack pointer to the first 4 bytes of the binary file.

- 4. Set the PC pointer to the next 4 bytes after the first 4 bytes of the binary file.

- 5. Load the binary file starting at address 0x007F\_8000.

- 6. Reset the Cortex-M4 microcontroller by setting the SRC\_M4RCR[1] bit in the SRC\_M4RCR register.

# 8 Reloading code on i.MX 6SoloX

### 8.1 On-chip memory view from each Arm core on the i.MX 6SoloX

The memory view of different peripherals is different between the Cortex-A9 and Cortex-M4 sides. Table 7 shows only the memory areas relevant for this application note. For more details, see the Memory Map chapter in the *i.MX* 6SoloX Applications Processor Reference Manual (document IMX6SXRM).

| Table 7  | Start and end add    | resses of different | t memories from | Cortex-A9 and  | Cortex-M4 side  |

|----------|----------------------|---------------------|-----------------|----------------|-----------------|

| lable 1. | Otalit allu bilu auu | resses or unicient  |                 | CUITEY-V3 alla | COLICY-INE SIDE |

| Peripheral | Start address<br>Cortex-A9 | End address<br>Cortex-A9 | Start address<br>Cortex-M4 side | End address<br>Cortex-M4 side | Size  |

|------------|----------------------------|--------------------------|---------------------------------|-------------------------------|-------|

| TCM_L      | 0x007F_8000                | 0x007F_7FFF              | 0x1FFF_8000                     | 0x1FFF_FFFF                   | 32 KB |

| TCM_U      | 0x0080_0000                | 0x0080_7FFF              | 0x2000_0000                     | 0x2000_7FFF                   | 32 KB |

NOTE

The boot vector for the Cortex-M4 core is located at the start of the TCM\_L, whose address is 0x007F\_8000 from the Cortex-A9 core. This is a location different from that on the i.MX 7Dual/7Solo.

### 8.2 Detailed procedure

To reload the code on the Cortex-M4 core using the Cortex-A9 processor on i.MX 6SoloX, follow the steps listed below:

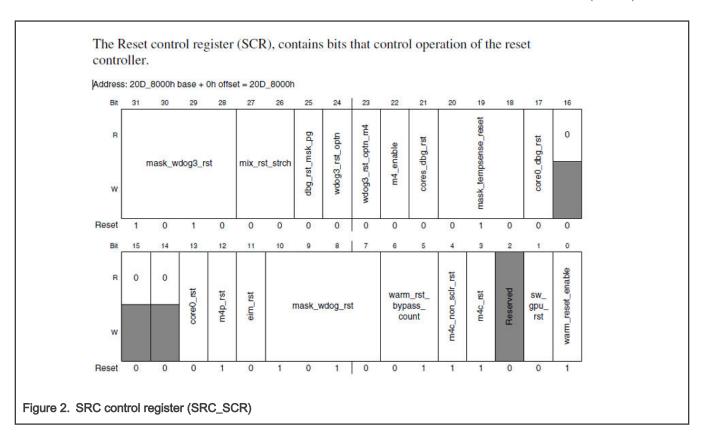

- Issue a software platform reset by setting up M4P\_RST (Bit 12) in the SRC\_SCR (SRC\_M4RCR[12]) register. Issuing

a platform reset resets the Cortex-M4 cores and associated memories. The address of the SRC\_SCR register is

0x020D\_8000 for i.MX 6SoloX.

- Load the code for the Cortex-M4 processor into the TCM\_L memory. For this application, we assume that the M4

code is compiled to execute from the TCM\_L memory. Program the binary file generated by FreeRTOS to the TCM\_L

address from the Cortex-A9 side, which is 0x007F\_8000, as listed in Table 7.

- 3. When the file is loaded, set up the stack and PC pointers in the TCM\_L memory. After a reset, the processor uses the TCM\_L start address (0x007F\_8000) as the first instruction. For this implementation, the stack value is the first 4 bytes found in the binary file generated for the Cortex-M4 processor using the FreeRTOS source. The PC value is also 4 bytes long and located at an offset of 0x4 in the binary file. This PC value is written to the TCM\_L base address plus four, which is (0x007F\_8004). Table 8 shows the stack and PC addresses.

Table 8. Boot vectors location for Cortex-M4 core

| Boot vectors    | TCM_L location for boot vectors | Location of boot vectors in binary file |

|-----------------|---------------------------------|-----------------------------------------|

| Stack pointer   | 0x007F_8000                     | First 4bytes                            |

| Program counter | 0x007F_8004                     | 4 bytes after first 4 bytes             |

- 4. When the startup address in the TCM\_L is modified according to the binary file and loaded into the memory, ensure that the ENABLE\_M4 (Bit 22) in the SRC\_SCR (SRC\_SCR[22]) register is set to 1. Because the *bootaux* already booted a primary image, this bit should be 1. Performing a platform reset using M4P\_RST (Bit 12) in the SRC\_SCR (SRC\_SCR[12]) register does not clear this bit. The last step is to set the M4C\_RST (Bit 3) in the SRC\_SCR (SRC\_SCR[3]) register, which boots the new code on the Cortex-M4 processor.

- 5. Repeat steps 1-3 to reload a new image. More details about the SRC\_SCR register are in Figure 2.

Application Note 7 / 15

### 8.3 Steps for reloading code on i.MX 6SoloX

The steps required to reload code on i.MX 6SoloX are as follows:

- 1. Issue a platform reset by setting the SRC\_SCR[12] bit in the SRC\_SCR register.

- 2. Wait for the SRC\_SCR[12] bit to be cleared by the hardware.

- 3. Set the stack pointer to the first 4 bytes of the binary file.

- 4. Set the PC pointer to the next 4 bytes after the first 4 bytes of the binary file.

- Load the binary file starting at address 0x007F\_8000.

- 6. Reset the Cortex-M4 by setting the SRC\_SCR[3] bit in the SRC\_SCR register.

# 9 Linux Remote Processor (RPROC) framework

The majority of modern SoCs are heterogenous platforms presenting Asymmetric Multiprocessing (AMP) configuration with different types of processors, which allows to run various instances of operating system (like Linux) in parallel with a real-time OS.

For example, i.MX 8MP presents a cluster of quad Cortex-A53 cores and a cluster with a Cortex-M7 core. The quad Cortex-A53 cluster usually runs Linux in SMP configuration and the Cortex-M7 core may run an RTOS.

The Remote Processor (RPROC) framework is a Linux community effort to introduce the possibility to control (power on, load firmware, power off) the remote processors abstracting the hardware differences in the same time on AMP SoCs. It offers monitoring and debug services for the remote coprocessor.

Later versions of the Linux kernel (≥ 5.x) implement the RPROC framework in the "remote proc" section of the Linux kernel repository drivers/remoteproc. The Linux kernel community implemented the framework abstractization between the user interaction (other Linux kernel modules, SysFs, Userspace) and the hardware to provide a uniform API which can be used in a similar way for all platforms that support Linux RPROC.

For the interaction with hardware, each SoC support must implement *rproc\_ops* callbacks. The following code snippet shows the operations from *rproc\_ops*.

```

/**

* struct rproc_ops - platform-specific device handlers

\star @start: power on the device and boot it

* @stop: power off the device

* @kick: kick a virtqueue (virtqueue id given as a parameter)

* @da to va: optional platform hook to perform address translations

* @parse fw: parse firmware to extract information (e.g. resource table)

* @handle rsc: optional platform hook to handle vendor resources. Should return

^{\star} RSC HANDLED if resource was handled, RSC IGNORED if not handled and a

* negative value on error

* @load rsc table: load resource table from firmware image

* @find loaded rsc table: find the loaded resource table

* @load: load firmware to memory, where the remote processor

* expects to find it

* @sanity_check: sanity check the fw image

* @get boot addr: get boot address to entry point specified in firmware

*/

struct rproc_ops

{

int (*start)(struct rproc *rproc);

int (*stop)(struct rproc *rproc);

void (*kick) (struct rproc *rproc, int vqid);

void * (*da to va)(struct rproc *rproc, u64 da, int len);

int (*parse fw) (struct rproc *rproc, const struct firmware *fw);

int (*handle rsc) (struct rproc *rproc, u32 rsc type, void *rsc,

int offset, int avail);

struct resource table *(*find loaded rsc table)(

struct rproc *rproc, const struct firmware *fw);

int (*load) (struct rproc *rproc, const struct firmware *fw);

int (*sanity check) (struct rproc *rproc, const struct firmware *fw);

u32 (*get_boot_addr)(struct rproc *rproc, const struct firmware *fw);

void * (*memcpy) (struct rproc *rproc, void *dest,

const void *src, size t count, int flags); };

```

RPROC Linux Documentation describes each API and their main functionality, which can be a useful resource when you start implementing the SoC support from scratch.

### 9.1 i.MX Linux RPROC support

NXP Linux BSP provides support for i.MX Linux RPROC on the following platforms: i.MX 8MP, i.MX 8MQ, i.MX 8MM, i.MX 8MM, i.MX 8MM, i.MX 8QM, i.MX 8QXP, i.MX 7D, i.MX 7UL, and i.MX 6SX. The implementation is realized in imx\_rproc.c. The supported platforms can be also identified in the code by checking compatible strings from the *imx\_rproc\_of\_match* structure.

RPROC implements the callback from *rproc\_ops*, following the recommendations listed in previous chapters. For example, the i.MX 8/i.MX 8X RPROC uses the SCFW API to start/stop the M4. The i.MX 8M RPROC programs the SRC registers directly or via ATF to start/stop the M4/M7.

The "imx\_rproc" sets the memory map for each supported platform inside to know what memory areas are allowed for the Cortex-M to contain code and date. Those limits are checked at runtime when the ELF is parsed and its sections are copied into the targeted memories.

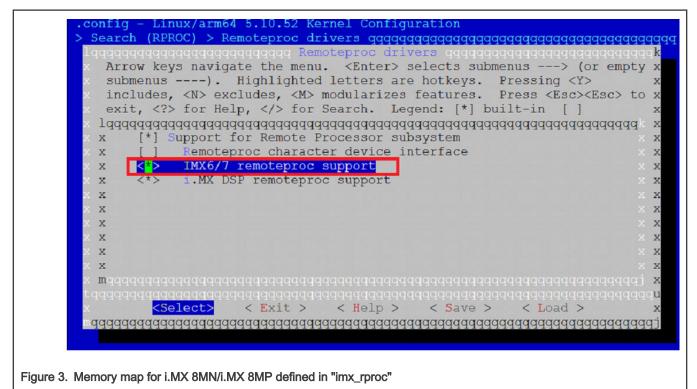

Figure 3 shows how the memory map for i.MX 8MN/i.MX 8MP is defined in "imx\_rproc":

```

static const struct imx_rproc_att imx_rproc_att_imx8mn[] = {

/* dev addr , sys addr , size , flags */

/* ITCM */

{ 0x00000000, 0x007E0000, 0x00020000, ATT_OWN },

```

```

/* OCRAM S */

{ 0x00180000, 0x00180000, 0x00009000, 0 },

/* OCRAM */

{ 0x00900000, 0x00900000, 0x00020000, 0 },

/* OCRAM */

{ 0x00920000, 0x00920000, 0x00020000, 0 },

/* OCRAM */

{ 0x00940000, 0x00940000, 0x00050000, 0 },

/* QSPI Code - alias */

{ 0x08000000, 0x08000000, 0x08000000, 0 },

/* DDR (Code) - alias */

{ 0x10000000, 0x40000000, 0x0FFE0000, 0 },

/* DTCM */

{ 0x20000000, 0x00800000, 0x00020000, ATT OWN },

/* OCRAM S - alias */

{ 0x20180000, 0x00180000, 0x00008000, ATT OWN },

/* OCRAM */

{ 0x20200000, 0x00900000, 0x00020000, ATT OWN },

/* OCRAM */

{ 0x20220000, 0x00920000, 0x00020000, ATT OWN },

/* OCRAM */

{ 0x20240000, 0x00940000, 0x00040000, ATT OWN },

/* DDR (Data) */

{ 0x40000000, 0x40000000, 0x80000000, 0 },

};

```

Firstly, activate the RPROC framework in the kernel configuration, if it is not enabled by default.

Secondly, the RPROC framework is enabled in the device tree using a dedicated DTS node. This required node is usually provided in "imx-\*-rpmsg.dts" by default in NXP Linux BSP. For example, i.MX 8MP uses the following DTS node, which specifies what mailboxes are needed to communicate between Linux and the M7 SDK app:

The **memory-region** attribute must contain the memory sections that are used by the firmware ELF to allow reloading from SysFS. For example, for i.MX 8MP, the following sections can be added:

· Memory regions definitions from the reserved-memory node:

```

m4_reserved: m4@0x80000000 {

no-map;

reg = <0 0x80000000 0 0x1000000>;

};

m7_ddr_alias: m4@0x10000000 {

no-map;

reg = <0 0x10000000 0 0x1000000>;

};

m7_itcm: m4@0x7E0000 {

no-map;

reg = <0 0x7E0000 0 0x20000>;

};

m7_dtcm: m4@0x800000 {

no-map;

reg = <0 0x800000 0 0x20000>;

};

```

RPROC DTS node referring to used memory nodes:

### 9.1.1 How to use RPROC on i.MX platforms

This subsection shows the usage of RPROC on i.MX platforms using the i.MX 8MP platform as a reference.

There are the following 3 possibilities to load and start the remote processor firmware:

- The firmware can be started via the SysFS interface.

- The firmware can be started automatically by the "remoteproc" driver at the probing stage.

- · Boot the firmware early using U-Boot and control the firmware using the SysFS interface.

#### NOTE

For i.MX 8M platforms, the root clock for M7/M4 must be kept always enabled by Linux to load the firmware code and start Cortex M7/M4. By default, NXP Linux BSP keeps the root clock enabled for the M core when it is started from U-Boot. Otherwise, if you need to firstly start the M core from the Linux booting phase, the clock driver (drivers/clk/imx/clk-composite-8m.c) must be updated to always skip the gate registration to keep the root clock always enabled for the M core.

### 9.1.1.1 Starting firmware using SYSFS interface

1. RPROC exports the RPROC functionalities to UserSpace using SysFS.

```

$ ls /sys/class/remoteproc/remoteproc0/

consumers device

name recovery subsystem uevent

coredump firmware power state

suppliers

```

### NOTE

If /sys/class/remoteproc/remoteproc\*/is empty, the RPROC framework is not enabled in the device tree. The previous section describes how to enable RPROC.

2. If the ELF is not stored in /lib/firmware, set the new path.

```

# echo -n <firmware path> > /sys/module/firmware class/parameters/path

$ echo -n /run/media/mmcblk1p1/ > /sys/module/firmware class/parameters/path

```

3. If the filename of the firmware ELF is different from the default one, set it to the new one.

```

# echo -n <firmware name.elf> > /sys/class/remoteproc/remoteproc<N>/firmware

$ echo -n imx8mp m7 TCM hello world.elf > /sys/class/remoteproc/remoteproc0/firmware

```

4. Check the state of the remote processor before starting it with a new firmware. If it is online, it should be stopped.

```

# cat /sys/class/remoteproc/remoteproc<N>/state

$ cat /sys/class/remoteproc/remoteproc0/state

offline

```

5. Start the remote processor with the new firmware.

```

# echo start > /sys/class/remoteproc/remoteproc<N>/state

$ echo start > /sys/class/remoteproc/remoteproc0/state

$ cat /sys/class/remoteproc/remoteproc0/state

running

```

6. Stop the remote processor.

```

# echo stop > /sys/class/remoteproc/remoteproc<N>/state

$ echo stop > /sys/class/remoteproc/remoteproc0/state

$ cat /sys/class/remoteproc/remoteproc0/state

offline

```

### 9.1.1.2 Starting firmware automatically by remote PROC driver during Linux Kernel boot time

Starting the firmware automatically by a remote PROC and not from U-Boot or Linux console is possible if fsl,rproc-auto-boot property is set to 1 and fsl,rproc-fw-name is set to the firmware ELF name located in /lib/firmware.

```

imx8mp-cm7 {

compatible = "fsl,imx8mn-cm7";

rsc-da = <0x550000000>;

clocks = <&clk IMX8MP CLK M7 DIV>;

mbox-names = "tx", "rx", "rxdb";

mboxes = <&mu 0 1

&mu 1 1

&mu 3 1>;

memory-region = <&vdev0vring0>, <&vdev0vring1>,

<&vdevbuffer>, <&m4 reserved>, <&m7 ddr alias>,

<&m7 itcm>, <&m7 dtcm>;

fsl,rproc-auto-boot = <1>;

fsl,rproc-fw-name="imx8mp_m7_TCM_sai_low_power_audio.elf";

status = "okay";

};

```

### 9.1.1.3 Booting firmware early using U-Boot and controlling firmware using SysFS interface

i.MX U-Boot can start Cortex-M from the U-Boot console level using the bootaux command. Depending on the used i.MX 8M, i.MX 8, or i.MX 8X platforms, some of them have already defined Cortex-M booting commands.

For example, to define an M7 boot command from TCM on i.MX 8MP, use the following commands in U-Boot:

```

@ M7 Bin Filename - stored on 1st partition

=> setenv m7image 'helloworld.bin'

# M7 Load command

=> setenv load m7image 'fatload mmc 1:1 0x48000000 ${m7image}; cp.b 0x48000000 0x7e0000 0x20000;'

# M7 Start Command

=> setenv m7boot 'run load m7image; bootaux 0x7e0000'

# Start M7

=> run m7boot

```

After Cortex-M is started from U-Boot, Linux can be started until the console appears. To shut down and reload Cortex-M, perform the following steps:

1. Stop the remote processor before deploying new firmware.

```

# echo stop > /sys/class/remoteproc/remoteproc<N>/state

$ echo stop > /sys/class/remoteproc/remoteproc0/state

```

2. If ELF is not stored in /lib/firmware, set a new path.

```

# echo -n <firmware path> > /sys/module/firmware class/parameters/path

$ echo -n "/run/media/mmcblk1p1/" > /sys/module/firmware class/parameters/path

```

If the filename of the firmware ELF is different from the default one, set it to a new one.

```

# echo -n <firmware name.elf> > /sys/class/remoteproc/remoteproc<N>/firmware

$ echo -n imx8mp m7 TCM hello world.elf > /sys/class/remoteproc/remoteproc0/firmware

```

4. Start the remote processor with the new firmware.

```

# echo start > /sys/class/remoteproc/remoteproc<N>/state

$ echo start > /sys/class/remoteproc/remoteproc0/state

```

### 10 References

- 1. i.MX 8MP Applications Processor Reference Manual

- 2. i.MX 8MQ Applications Processor Reference Manual (document IMX8MDQLQRM)

- 3. i.MX 8MM Applications Processor Reference Manual (document IMX8MMRM)

- 4. i.MX 8MN Applications Processor Reference Manual (document IMX8MNRM)

- 5. i.MX 8QM Applications Processor Reference Manual (document IMX8QMRM)

- 6. i.MX 8QXP Applications Processor Reference Manual (documentIMX8DQXPRM)

- 7. i.MX 7Dual Applications Processor Reference Manual (document IMX7DRM)

- 8. i.MX 6SoloX Applications Processor Reference Manual (document IMX6SXRM)

- 9. Linux Remote Processor Framework documentation

# 11 Revision history

Table 9. Revision history

| Revision number | Date             | Substantive changes                                            |

|-----------------|------------------|----------------------------------------------------------------|

| 0               | 08/2016          | Initial release                                                |

| 1               | 08/2019          | Introduced i.MX 8M support                                     |

| 2               | 18 November 2021 | Introduced RPROC and updated the look and feel of the document |

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

**Limited warranty and liability**— Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX,EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. M, M Mobileye and other Mobileye trademarks or logos appearing herein are trademarks of Mobileye Vision Technologies Ltd. in the United States, the EU and/or other jurisdictions.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 18 November 2021

Document identifier: AN5317