NXP Semiconductors Application Note Document Number: AN12225 Rev. 0, 07/2018

# How to Reduce SoC Power when Running M4 with A53 on i.MX8M

#### 1. Introduction

On i.MX8M EVK board, when user measures current with AMP applications, he may find that the VDD\_SOC current is much higher than expected. This document discusses about the root cause of the issue and the solution.

### 2. Chip overview

This section provides main features of i.MX 8M chips.

#### 2.1. i.MX8M chip overview

The i.MX 8M family is a set of NXP products focused on delivering the latest and greatest video and audio experience combining state-of-the-art media-specific features with highperformance processing while optimized for lowest power consumption. The i.MX 8M Quad Media Applications Processor is the first product of the growing i.MX 8M family targeting the consumer market.

- Built in TSMC 28HPC to achieve both high performance and low power consumption.

- Relies on a powerful fully coherent core based on a quad Cortex®-A53 cluster with graphics processing handled by the GC7000Lite GPU from Vivante supporting the latest graphic APIs.

- Advanced security modules for secure boot, cipher acceleration and DRM support.

#### Contents

| 1. | Introduction                             | 1 |

|----|------------------------------------------|---|

| 2. | Chip overview                            | 1 |

|    | 2.1. i.MX8M chip overview                |   |

| 3. | High VDD_SOC current issue               | 2 |

| 4. | Root cause of high VDD_SOC current issue | 2 |

| 5. | Solution                                 |   |

|    | 5.1. Preliminary knowledge on clock      | 4 |

|    | 5.2. Code change                         |   |

| 6. | Power Consumption Test                   | 6 |

|    | Conclusion                               |   |

| 8. | Revision history                         |   |

| 9. | Reference                                | 7 |

|    |                                          |   |

© 2018 NXP B.V.

- General purpose Cortex-M4 processor for low power processing.

- A wide range of audio interfaces including I2S, AC97, TDM and S/PDIF.

- Large set of peripherals that are commonly used in consumer/industrial markets including USB 3.0, PCIe and Ethernet.

### 3. High VDD\_SOC current issue

Here we will compare SOC current when only kernel is loaded on A53 and when both A53 kernel and M4 image are loaded.

• SOC current when only kernel is loaded on A53

| i.MX8MQ GA EVK dtb, no display, eth down, SDCard boot, idle |       |         |

|-------------------------------------------------------------|-------|---------|

|                                                             | ARM   | SOC     |

| Voltage(V)                                                  | 0.896 | 0.877   |

| Playback Current (mA)                                       | 65    | 205     |

| Power (mW)                                                  | 58.24 | 179.785 |

• SOC current when both A53 kernel and M4 image are loaded.

| i.MX8MQ GA EVK dtb, no display, eth down, SDCard boot, idle. Use SDK hello_world M4 image. |       |       |

|--------------------------------------------------------------------------------------------|-------|-------|

|                                                                                            | ARM   | SOC   |

| Voltage(V)                                                                                 | 0.896 | 0.877 |

| Playback Current (mA)                                                                      | 65    | 500   |

| Power (mW)                                                                                 | 58.24 | 438.5 |

Comparing the SOC current, we should see that **when M4 image is loaded, SOC current increases from 205 mA to 500 mA**, which is definitely abnormal.

### 4. Root cause of high VDD\_SOC current issue

Normally, in kernel initialization, it disables all peripheral's clock gate.

But in a AMP applications environment, when kernel detects that M4 core is running, it will not disable all peripheral's clock gates, that is, all peripherals are enabled. So it will consume much more current.

In drivers/clk/imx/clk.h, function imx\_clk\_gate3 is used to enable/disable peripherals' clock gates.

#### Root cause of high VDD\_SOC current issue

```

static inline struct clk *imx clk gate3(const char *name, const char *parent,

void __iomem *reg, u8 shift)

{

/*

* per design team's suggestion, clk root is NOT consuming

* much power, and clk root enable/disable does NOT have domain

* control, so they suggest to leave clk root always on when

* M4 is enabled.

*/

if (imx_src_is_m4_enabled())

return clk register fixed factor (NULL, name, parent,

CLK SET RATE PARENT, 1, 1);

else

return clk register gate (NULL, name, parent,

CLK SET RATE PARENT | CLK OPS PARENT ENABLE,

reg, shift, 0, &imx ccm lock);

```

Macro imx src is m4 enabled() is used to check if M4 is running.

So, when M4 is detected running, the peripheral's clock will be kept enabled.

In drivers/clk/imx/clk-imx8mq.c, function, when searching with imx\_clk\_gate3, you can find that a lot of peripheral's clock root gates are controlled by imx\_clk\_gate3.

```

clks[IMX8MQ_CLK_DRAM_ALT_CG] = imx_clk_gate3("dram_alt_cg", "dram_alt_src", base + 0xa000,

28);

clks[IMX8MQ_CLK_DRAM_APB_CG] = imx_clk_gate3("dram_apb_cg", "dram_apb_src", base + 0xa080,

28);

clks[IMX8MQ_CLK_VPU_G1_CG] = imx_clk_gate3("vpu_g1_cg", "vpu_g1_src", base + 0xa100, 28);

...

clks[IMX8MQ_CLK_PCIE2_PHY_CG] = imx_clk_gate3("pcie2_phy_cg", "pcie2_phy_src", base +

0xc080, 28);

clks[IMX8MQ_CLK_PCIE2_AUX_CG] = imx_clk_gate3("pcie2_aux_cg", "pcie2_aux_src", base +

0xc100, 28);

clks[IMX8MQ_CLK_ECSPI3_CG] = imx_clk_gate3("ecspi3_cg", "ecspi3_src", base + 0xc180, 28);

```

## 5. Solution

#### 5.1. Preliminary knowledge on clock

There're some preliminary knowledges that we should point out.

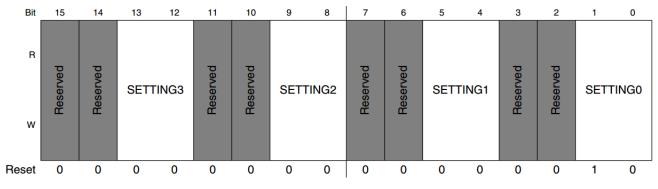

• On iMX8M, we should be aware of that **almost all peripheral modules have clock gates and those gates can be separately controlled by 4 power domains**. See peripheral modules' clock gate registers below:

Figure 1. Clock gate registers for peripheral modules

| SETTING0 | Clock gate control setting for domain 0.                                                                                                                                                         |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | This field can only be written by domain 0.                                                                                                                                                      |  |

|          | <ul> <li>00 Domain clocks not needed</li> <li>01 Domain clocks needed when in RUN</li> <li>10 Domain clocks needed when in RUN and WAIT</li> <li>11 Domain clocks needed all the time</li> </ul> |  |

Figure 2. Clock gate control setting

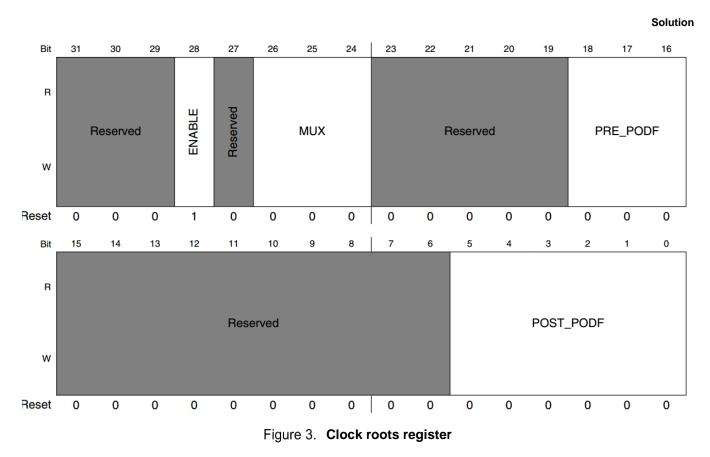

But clock roots don't have this power domain control. See clock roots register below:

So kernel will be responsible for overall control of clock roots.

• As kernel will control all clock roots and kernel don't know what root clocks that M4 image needed (that's why kernel enables all clock roots), we need to know what clock roots M4 image needed.

#### 5.2. Code change

Now that we know why kernel enable all clock gates when M4 core is running and we need to know what clock roots M4 image needed, we can do the change on code now.

• Disable M4 core detection in clock gate function

In drivers/clk/imx/clk.h, change imx\_clk\_gate3 as following:

#### Conclusion

• Add M4 needed clocks

In drivers/clk/imx/clk-imx8mq.c, add clks\_init\_on\_m4 as following:

```

static int const clks_init_on_m4[] __initconst = {

IMX8MQ_CLK_M4_CG,

IMX8MQ_CLK_SAI1_CG, IMX8MQ_CLK_SAI2_CG,

IMX8MQ_CLK_UART2_CG,

```

};

The clks\_init\_on\_m4 here is just an example. In real user applications, user should know what M4 root clocks are needed.

• Add clock init code in function imx8mq\_clocks\_init. We can add it right after initialization of A53 needed clock roots.

#### 6. Power Consumption Test

After code change, we can now recompile kernel and boot board again. New power data is listed below:

| i.MX8MQ GA EVK dtb, no display, eth down, SDCard boot, idle. Use SDK hello_world M4 image. |       |       |

|--------------------------------------------------------------------------------------------|-------|-------|

|                                                                                            | ARM   | SOC   |

| Voltage(V)                                                                                 | 0.896 | 0.877 |

| Playback Current (mA)                                                                      | 65    | 250   |

| Power (mW)                                                                                 | 58.24 | 438.5 |

The SOC current drops nearly 250mA.

### 7. Conclusion

This document mainly describes a power issue on i.MX8MQ platform and how to fix this issue. As there're no mechanism to communicate clock roots on i.MX8M, the solution should be applied according to different M4 user cases.

Users who are designing AMP applications on i.MX8M can make use of this document to optimize power on their code.

# 8. Revision history

| Revision number | Date   | Substantive changes |

|-----------------|--------|---------------------|

| 0               | 7/2018 | Initial release     |

#### 9. Reference

1. i.MX8MQ Reference Mannual

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C 5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, AMBA, Arm Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. Arm7, Arm9, Arm11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, Mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2018 NXP B.V.

Document Number: AN12225 Rev. 0 07/2018

# arm