# AN12573 i.MX 7ULP Power Consumption Measurement

Rev. 1 — 18 February 2022

Application Note

# 1 Introduction

This application note helps the user design power management systems. This report provides power consumption measurements for several use cases and provides information on minimizing power consumption on the i.MX 7ULP.

Because the data presented in this application note is based on empirical measurements taken on a small sample size, the presented results are not guaranteed.

#### Contents

| 1          | Introduction1                          |

|------------|----------------------------------------|

| 2          | Acronyms and abbreviations2            |

| 3          | Overview of i.MX 7ULP power            |

|            | domains4                               |

| 4          | Internal power measurement of the      |

|            | i.MX 7ULP processor6                   |

| 4.1        | DGO "Always ON" domain power           |

|            | supplies6                              |

| 4.2        | Real-Time Domain (RTD) power           |

|            | supplies6                              |

| 4.3        | Application Domain (AD) power          |

|            | supplies7                              |

| 4.4        | VBAT domain power supplies7            |

| 4.5        | Analog and other supplies8             |

| 4.6        | Voltage levels and DVFS usage in       |

|            | measurement process                    |

| 4.7        | Temperature8                           |

| 4.8        | Hardware and software used8            |

| 5          | Use cases and measurement results      |

|            |                                        |

| 5.1        | Real-time domain low-power             |

| 5.2        | modes9<br>Application domain low-power |

| 5.Z        | modes                                  |

| 5.3        | VBAT domain low-power mode. 11         |

| 5.3<br>5.4 | Low-power mode power                   |

| 5.4        | measurements                           |

| 5.5        | Real-time domain (M4) active           |

| 5.5        | power measurements                     |

| 5.6        | Application domain (A7) active         |

| 0.0        | power measurements                     |

| 6          | Minimizing power consumption 30        |

| 7          | Low-power design considerations for    |

| •          | i.MX 7ULP                              |

| 7.1        | Designing power supply rails for       |

|            | power consumption                      |

| 7.2        | Controlling i.MX 7ULP power            |

|            | supplies in the lowest power           |

|            | modes                                  |

| 7.3        | On-chip LDO regulator modes37          |

| 8          | Revision history38                     |

# 2 Acronyms and abbreviations

Table 1 defines the acronyms and abbreviations used in this document.

#### Table 1. Acronyms and definitions

| Term   | Definition                                         |

|--------|----------------------------------------------------|

| A7     | Arm <sup>®</sup> Cortex <sup>®</sup> -A7 processor |

| AD     | Application Domain                                 |

| ADC    | Analog-to-Digital Converter                        |

| АНВ    | Arm AMBA High-performance Bus                      |

| APLL   | Auxiliary Phase-Locked Loop clock generator        |

| Arm    | Advanced RISC machines processor architecture      |

| AWIC   | i.MX 7ULP Asynchronous Wakeup Interrupt Controller |

| AXI    | Arm Advanced eXtensible Interface                  |

| BSP    | Board Support Package                              |

| СМР    | i.MX 7ULP Analog Comparator module                 |

| DAC    | Digital-to-Analog Converter                        |

| DDR    | Dual data rate DRAM                                |

| DGO    | Designator for the Always On power domain          |

| DMA    | i.MX 7ULP Direct Memory Access Controller          |

| DRAM   | Dynamic Random-Access Memory                       |

| DVFS   | Dynamic Voltage and Frequency Scaling              |

| EVK    | Evaluation Kit                                     |

| FBB    | Forward Body Bias                                  |

| FIRC   | FAST Internal Reference Clock                      |

| GND    | Ground                                             |

| GPIO   | General-purpose input/output                       |

| GPU    | Graphics Processing Unit                           |

| GPU2D  | 2-Dimensional Graphics Processing Unit             |

| GPU3D  | 3-Dimensional Graphics Processing Unit             |

| High-Z | High impedance                                     |

| HSRUN  | i.MX 7ULP High Speed Run mode                      |

| I/Os   | Inputs / Outputs                                   |

| IOMUX  | Chip-level I/O multiplexing                        |

| IOMUXC | i.MX 7ULP Input/Output Multiplexing Controller     |

| Table 1. | Acronyms an | d definitions | (continued) |

|----------|-------------|---------------|-------------|

|----------|-------------|---------------|-------------|

| Term     | Definition                                        |

|----------|---------------------------------------------------|

| IPG      | i.MX 7ULP Internal Peripheral clocks and controls |

| LDO      | Low drop-out regulator                            |

| LLS      | i.MX 7ULP Low Leakage Stop mode                   |

| LPDDR2   | Low-power DDR2 SDRAM                              |

| LPDDR3   | Low-power DDR3 SDRAM                              |

| LPTMR    | i.MX 7ULP Low Power Timer                         |

| LVD      | Low-Voltage Detector                              |

| M4       | Arm Cortex-M4 processor                           |

| MIPI DSI | MIPI display serial interface controller          |

| MMDC     | Multi-mode DDR controller                         |

| MU       | i.MX 7ULP Messaging Unit                          |

| OTP      | One-time programmable                             |

| РСВ      | Printed Circuit Board                             |

| PLL      | Phase-Locked Loop clock generator                 |

| PMC      | Power Management Controller                       |

| PMIC     | Power management integrated circuit               |

| PSTOP    | i.MX 7ULP Low Power Partial Stop mode             |

| РТА      | Signals associated with Port A                    |

| РТВ      | Signals associated with Port B                    |

| PTC      | Signals associated with Port C                    |

| PTD      | Signals associated with Port D                    |

| PTE      | Signals associated with Port E                    |

| PTF      | Signals associated with Port F                    |

| QSPI     | i.MX 7ULP Quad Serial Peripheral Interface module |

| RAM      | Random access memory                              |

| RBB      | Reverse Body Bias                                 |

| ROM      | Read-only memory                                  |

| RTC      | Real-Time Clock                                   |

| RTD      | Real-Time Domain                                  |

| RUN      | i.MX 7ULP Normal Speed Run mode                   |

| SDK      | Software Development Kit                          |

| SIM      | i.MX 7ULP System Integration Module               |

| Term     | Definition                                                |

|----------|-----------------------------------------------------------|

| SIRC     | Slow Internal Reference Clock                             |

| SNVS     | Secure Non-Volatile Storage                               |

| SoC      | System on Chip                                            |

| SPLL     | System Phase-Locked Loop clock generator                  |

| SRAM     | On-Chip Static Random Access Memory                       |

| SRTC     | i.MX 7ULP Secure Real-Time Clock                          |

| STOP     | i.MX 7ULP Low Power Stop mode                             |

| ТСМ      | Cortex-M4 Tightly-Coupled Memory                          |

| UART     | Universal asynchronous receiver/transmitter               |

| USB      | Universal serial bus                                      |

| USB 2.0  | USB version 2.0 peripheral                                |

| USB HSIC | Universal serial bus high-speed inter-chip physical layer |

| USB OTG  | USB on-the-go                                             |

| uSDHC    | Ultra-secured digital host controller                     |

| VLLS     | i.MX 7ULP Very Low Leakage Stop mode                      |

| VLPR     | i.MX 7ULP Very Low Power Run mode                         |

| VLPS     | i.MX 7ULP Very Low Power Stop mode                        |

| WFI      | Wait-for-interrupt                                        |

Table 1. Acronyms and definitions (continued)

# 3 Overview of i.MX 7ULP power domains

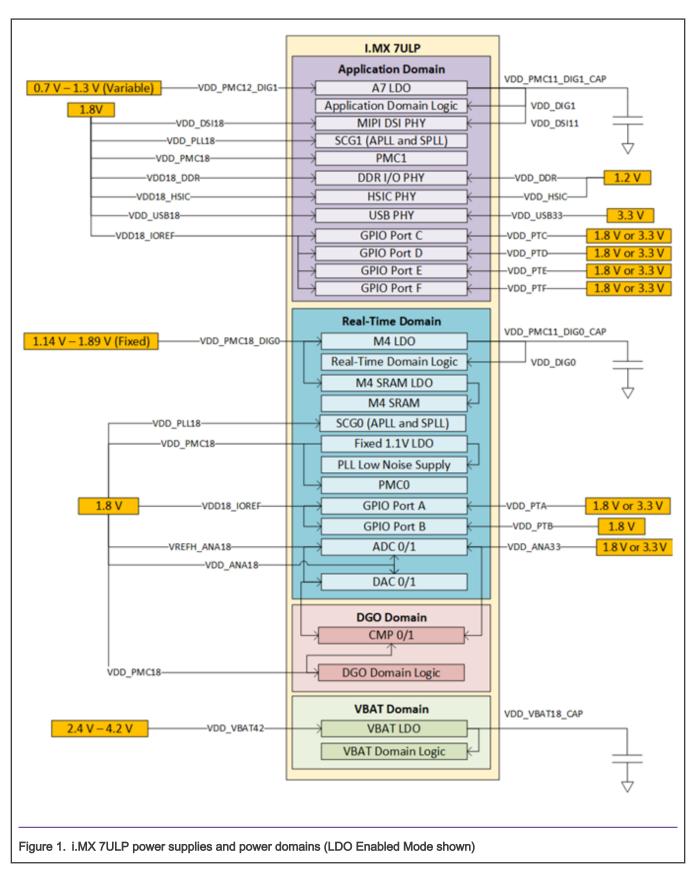

The i.MX 7ULP has several power domains each containing multiple power supplies.

The i.MX 7ULP power architecture is organized in four main power domains:

- The **Real-Time Domain (RTD)** contains the Arm Cortex-M4 platform, multiple peripherals, system-level components and two GPIO ports (Ports A and B).

- The Application Domain (AD) contains the Arm Cortex-A7 platform, a 3D Graphics Processing Unit (3DGPU), a 2D Graphics Processing Unit (2DGPU), the LPDDR2/LPDDR3 interface (MMDC), the MIPI DSI display interface, multiple peripherals, and four GPIO ports (Ports C, D, E and F).

- The **DGO "Always-On" Domain** contains reset and system mode control logic, the Low-Leakage Wakeup Unit (LLWU), analog comparators and low-power timers.

- The VBAT Domain contains the Real-Time Clock (RTC) and Secure Non-Volatile Storage (SNVS) components.

In general, these domains are independent of each other. Multiple power modes are available in the Real-Time Domain and the Application Domain to optimize power consumption to the demands of the application at a given time. These modes optimize power consumption by reducing clock frequencies, reducing voltages, gating clocks and gating power supplies.

Figure 1 shows the connections of the power supplies and the distribution of the internal power domains.

The external supplies shown in Figure 1 do not imply that separate power supplies are required for each orange block shown.

- All the i.MX 7ULP 1.2 V supplies can be provided from a single source.

- All the i.MX 7ULP 1.8 V supplies can be provided from a single source.

- All the i.MX 7ULP 3.3 V supplies can be provided from a single source.

#### NOTE

For the recommended operating conditions of each supply rail and for a detailed description of the groups of pins powered by each I/O voltage supply, see i.MX 7ULP Applications Processor - Consumer Products data sheet (document IMX7ULPCEC).

For more details regarding the i.MX 7ULP power architecture, see i.MX 7ULP Applications Processor Reference Manual (document IMX7ULPRM).

## 4 Internal power measurement of the i.MX 7ULP processor

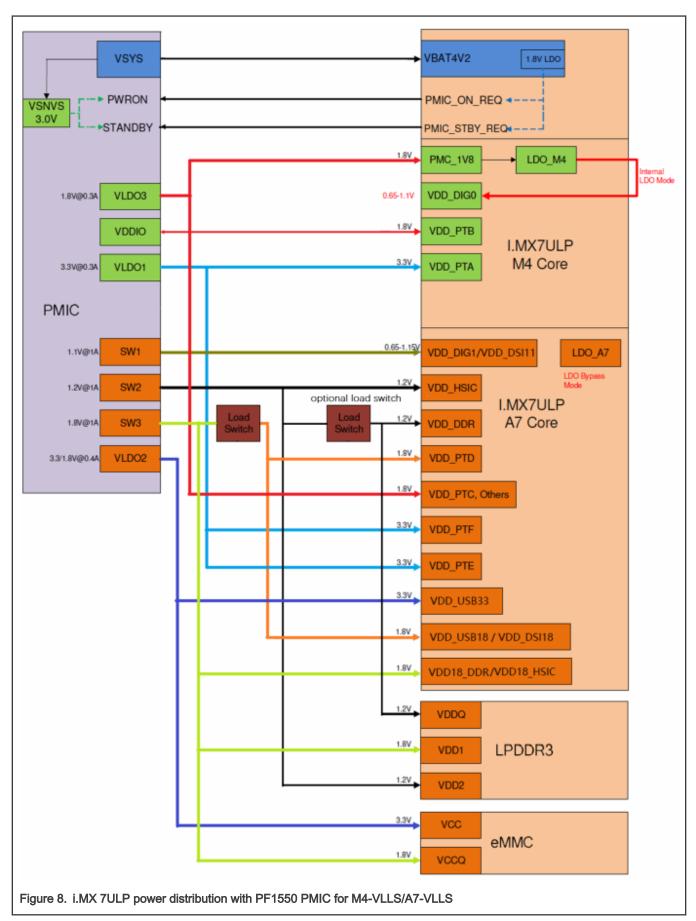

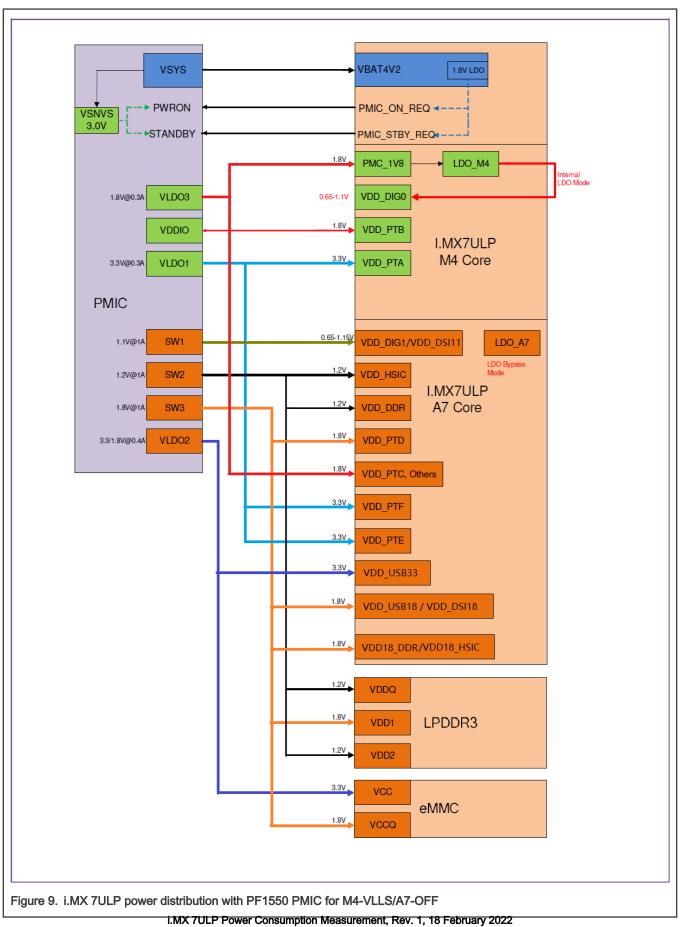

Several use cases (described in Use cases and measurement results) have been run on the i.MX 7ULP PWRSOM EVK (MCIMX7ULP-PWRSOM EVK). Some measurements have been obtained from other hardware as indicated.

The low-power mode measurements in this document apply to multiple power supplies.

The RUN mode and High-Speed RUN (HSRUN) mode measurements in this document primarily contains measurements from the dominant power supply in each active domain:

- For the Real-Time Domain, the dominant supply is VDD\_PMC18\_DIG0. This supply provides power to the internal LDO and the downstream low-voltage logic (including the M4, on-chip memory and peripherals). The internal LDO in this domain controls the voltage to the logic under software control.

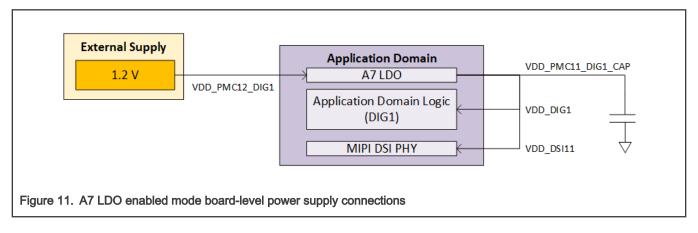

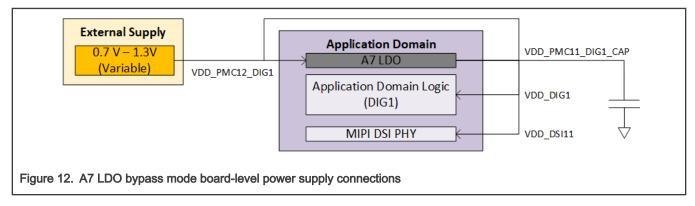

- For the Application Domain, the dominant supply depends on the internal LDO configurations:

- In LDO Enabled mode, a constant voltage is applied to VDD\_PMC12\_DIG1 and the internal LDO provides a lower voltage to the logic under software control. For more details on A7 LDO Enabled Mode, see A7 LDO enabled mode.

- In LDO Bypass mode, the internal LDO is disabled and VDD\_PMC12\_DIG1, VDD\_PMC11\_DIG1\_CAP, VDD\_DIG1, and VDD\_DSI11 are all connected externally. An external variable voltage is provided usually by an external Power Management IC (PMIC). This combined group of supplies is the dominant power consumer. The MCIMX7ULP-EVK is designed to operate in A7 LDO Bypass mode. All power measurements in this document were taken in A7 LDO Bypass mode, see A7 LDO bypass mode.

### 4.1 DGO "Always ON" domain power supplies

The following power supplies are used by the DGO domain:

- VDD\_PMC18 supplies the following circuits:

- CMP0/1

- PMC0/1

- Slow Internal Reference Clock (SIRC) generation [16 MHz]

- FAST Internal Reference Clock (SIRC) generation [48 MHz]

- Multiple other chip-level functions

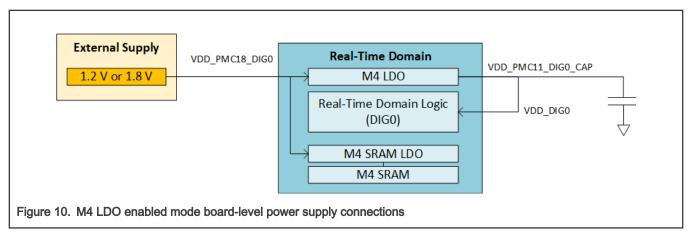

### 4.2 Real-Time Domain (RTD) power supplies

#### RTD uses the following power supplies:

• VDD\_PMC18\_DIG0 supplies the following circuits:

- M4 LDO, which provides power to the RTD low-voltage logic. The LDO output VDD\_PMC11\_DIG0\_CAP is connected to an external filter capacitor and it routed back into VDD\_DIG0 to supply the internal logic. For decoupling and bulk capacitor requirements, see *i.MX 7ULP Hardware Development Guide* (document IMX7ULPHDG).

- M4 SRAM LDO, which provides a fixed voltage to the on-chip RAM.

- VDD\_PMC18 supplies the following circuits:

- A portion of the M4 LDO.

- An internal fixed-voltage LDO which outputs a low-noise 1.1 V power source for the PLLs. VDD\_PMC18 also supplies the DGO Always-ON domain logic and the Power Management Controller 0 (PMC).

- VDD PTA supplies the I/Os on Port A (signals named PTAn).

- VDD PTB supplies the I/Os on Port B (signals named PTBn).

- Power consumption of VDD\_PTA and VDD\_PTB are completely application-dependent and as such, measurements for these supplies are not included in this document. For an equation to estimate GPIO segment power based on the activity of the individual I/O signals, see the **Maximum Supply Currents** table in *i.MX 7ULP Applications Processor Consumer Products data sheet* (document IMX7ULPCEC).

## 4.3 Application Domain (AD) power supplies

The Application Domain uses the following power supplies:

- VDD\_PMC12\_DIG1/VDD\_PMC11\_DIG1\_CAP/VDD\_DIG1 supplies the A7 LDO and the application domain logic. The LDO output, VDD\_PMC11\_DIG1\_CAP, is connected to an external filter capacitor and is routed back into VDD\_DIG1 to supply the internal logic. For decoupling and bulk capacitor requirements, see i.MX 7ULP Hardware Development Guide (document IMX7ULPHDG). The board-level configuration of these supplies is dependent on the choice of A7 LDO Enabled mode or A7 LDO Bypass mode. For details, see On-chip LDO regulator modes.

- VDD\_PMC18 supplies the following circuits:

- A portion of the A7 LDO

- PMC1

- VDD\_DSI18 and VDD\_DSI11 supply the MIPI DSI display interface. VDD\_DSI11 must be connected to VDD\_DIG1 at the board level.

- VDD18\_DDR and VDD\_DDR supply the LPDDR2/LPDDR3 PHY. VDD\_DDR is the 1.2 V supply for the LPDDR2/LPDDR3 interface I/Os.

- VDD18 HSIC and VDD HSIC supply the HSIC PHY. VDD HSIC is the 1.2 V supply for the USB HSIC interface I/Os.

- VDD USB33 and VDD USB18 supply the USB PHY

- VDD\_PTC supplies the I/Os on Port C (signals named PTCn)

- VDD PTD supplies the I/Os on Port D (signals named PTDn)

- VDD PTE supplies the I/Os on Port E (signals named PTEn)

- VDD\_PTF supplies the I/Os on Port F (signals named PTF*n*).

- For an equation to estimate GPIO segment power based on the activity of the individual I/O signals, see the Maximum Supply Currents table in *i.MX 7ULP Applications Processor - Consumer Products data sheet* (document IMX7ULPCEC).

## 4.4 VBAT domain power supplies

VDD\_VBAT42 supplies the VBAT Domain. In most applications, this supply will be provided by a battery. An internal LDO regulates the output to the 1.8 V used by the internal logic on the VBAT Domain. VDD\_VBAT18\_CAP is connected to an external capacitor. For decoupling and bulk capacitor requirements, see i.MX 7ULP Hardware Development Guide (document IMX7ULPHDG).

## 4.5 Analog and other supplies

The following supplies are used for analog and chip-level functions:

- VDD\_ANA33 is a 1.8 V or 3.3 V supply for analog functions.

- VDD\_ANA18 is a 1.8 V supply for analog functions.

- VDD PLL18 is a 1.8 V supply for the analog portions of the PLLs.

- VREFH ANA18 is the voltage reference for the high end of the ADC range.

- VDD18 IOREF is a 1.8 V reference supply used by the I/Os.

### 4.6 Voltage levels and DVFS usage in measurement process

The voltage levels of all the supplies are set to the typical voltage levels as defined in i.MX 7ULP Hardware Development Guide (document IMX7ULPHDG) unless otherwise specified.

VDD\_DIG0 and VDD\_DIG1 may be changed to implement Dynamic Voltage and Frequency Scaling (DVFS) during the run time of the use cases to minimize power consumption in each power mode. For the voltage specifications for each of the power modes, see the **Recommended operating conditions** table in i.MX 7ULP Hardware Development Guide (document IMX7ULPHDG).

## 4.7 Temperature

The power measurements in this document were measured at room temperature (approximately 25 °C) unless otherwise specified.

#### 4.8 Hardware and software used

#### Hardware

i.MX7ULP EVK POWERSOM board with B2 silicon - This PWRSOM board is a special designed board with power measurement capability. It is nearly an exact copy of the existing i.MX7ULP EVK SOM but with built-in power measurement capabilities. On this board, A7 LDO Bypass and M4 LDO Enable modes are used as indicated in internal power measurement of the i.MX 7ULP processor.

Table 2 lists the differences between POWERSOM board and EVK SOM board.

| Table 2. Differen | ces between POW | ERSOM board and E | EVK SOM board |

|-------------------|-----------------|-------------------|---------------|

|-------------------|-----------------|-------------------|---------------|

| Net     | i.MX7ULP EVK POWERSOM | i.MX7ULP EVK SOM   |

|---------|-----------------------|--------------------|

| VDD_PTC | PMC_1V8               | VDD_1V8            |

| VDD_PTF | PMC_3V3               | VDD_3V3            |

| U16.EN  | Pull-up to PMC_3V3    | Pull-up to VDD_3V3 |

#### Monitored power rails

All iMX7ULP SoC power rails are monitored, listed below. The iMX7ULP power numbers reported in this document represents the total sum of measured power rails, representing the full iMX7ULP SoC power consumption. Duration of use-cases power measurements is 1 minute.

The iMX7ULP input power rails monitored are (see Figure 1):

- VDD\_PMC12\_DIG1

- VDD\_DIG1

- VDD\_PMC11\_DIG1\_CAP

- VDD PMC18 DIG0 (M4 LDO enabled)

- VDD PMC18

- VDD PLL18

- VDD18\_DDR; VDD\_DDR

- VDD\_ANA18

- VREFH\_ANA18

- VDD\_ANA33

- VDD18\_HSIC; VDD\_HSIC

- VDD\_DSI18; VDD\_DSI11

- VDD\_USB18; VDD\_USB33

- VDD18\_IOREF

- VDD\_PTA; VDD\_PTB; VDD\_PTC; VDD\_PTD; VDD\_PTE; VDD\_PTF

- VDD\_VBAT42

#### Software used for the power measurements

- Real-Time Domain Software: Based on SDK 2.11.0. The running application is indicated in each case sections.

- Application Domain Software: Based on Linux L5.10.72\_2.2.0 with additional patches.

## 5 Use cases and measurement results

For the purpose of this document, active power modes are those in which the chip components are active (powered and have clock running). Low power modes are those in which some circuitry may be clock-gated, power-gated or both. These modes provide much lower power consumption in exchange for more limited capability.

Low-power modes between the Real-Time Domain (M4 side) and the Application Domain (A7 side) are generally independent and can be entered/exited separately. There are some chip-level limitations for combinations of power modes between the Real-Time Domain and the Application Domain. For details on the low-power mode definitions and the allowed combinations, see the **Power Modes** section and the **Allowed power modes between multicore** section in i.MX 7ULP Applications Processor Reference Manual (document IMX7ULPRM).

### 5.1 Real-time domain low-power modes

Table 3 summarizes the low-power modes for the Real-Time Domain.

| M4 Power mode         | Description                                                                              |

|-----------------------|------------------------------------------------------------------------------------------|

| STOP/VLPS             | • i.MX 7ULP is static state with all registers retained with maintaining LVD protection. |

| (Very Low Power Stop) | <ul> <li>Peripherals optionally operational in STOP mode4.</li> </ul>                    |

|                       | RBB only allowed in VLPS mode.                                                           |

|                       | FIRC enabled in VLPS mode via scg0_FIRCCSR register.                                     |

|                       | LVDs could be turned off in VLPS mode.                                                   |

| LLS                   | Static mode with no active transition.                                                   |

| M4 Power mode           | Description                                                                                                                                          |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Low Leakage Stop)      | CM4 in WFI mode with core clock gated.                                                                                                               |

|                         | RBB allowed.                                                                                                                                         |

| VLLS                    | <ul> <li>M4 core supply OFF with majority of the logic power gated.</li> </ul>                                                                       |

| (Very Low Leakage Stop) | <ul> <li>AWIC detects wake-up sources for M4 (via LLWU).</li> </ul>                                                                                  |

|                         | Selectable Memory retention (32/64/256 KB).                                                                                                          |

|                         | ADC, Comparators, LP Timers optionally functional.                                                                                                   |

|                         | RBB allowed (Optional).                                                                                                                              |

|                         | <ul> <li>DGO (aka Always ON) Logic Active. Only Peripherals in DGO domain (CMPx,<br/>LPTMRx) are functional.</li> </ul>                              |

|                         | NOTE                                                                                                                                                 |

|                         | The M4 can only enter VLLS when the A7 is in VLLS or OFF.                                                                                            |

|                         | For details on the low-power mode definitions and the allowed                                                                                        |

|                         | combinations, see the <b>Power Modes</b> section and the <b>Allowed power</b><br>modes between multicore section in i.MX 7ULP Applications Processor |

|                         | Reference Manual (document IMX7ULPRM).                                                                                                               |

#### Table 3. M4 low-power modes (continued)

## 5.2 Application domain low-power modes

Table 4 summarizes the low-power modes for the Application Domain.

| A7 Power mode         | Description                                                                     |

|-----------------------|---------------------------------------------------------------------------------|

| OFF                   | Application Domain supplies are unpowered.                                      |

|                       | LPDDR2/LPDDR3 supplies are unpowered.                                           |

| STOP/VLPS             | i.MX 7ULP is in static state with all registers retained with maintaining LVD   |

| (Very Low Power Stop) | protection.                                                                     |

|                       | RBB only allowed in VLPS mode.                                                  |

|                       | FIRCCSR[FIRCLPEN] in the SCG module keeps FIRC enabled in VLPS mode.            |

|                       | LVDs could be turned off in VLPS mode.                                          |

| LLS                   | A7 supply ON.                                                                   |

| (Low Leakage Stop)    | RBB is allowed.                                                                 |

|                       | LVD protection.                                                                 |

|                       | I/O supplies ON.                                                                |

|                       | • A7 processor is in a wait-for-interrupt (WFI) state. The core clock is gated. |

|                       | Bus and DMA clocks are gated.                                                   |

|                       | Table continues on the next page                                                |

| A7 Power mode                   | Description                                                                                                                                                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                 | <ul> <li>All peripheral clocks are gated.</li> <li>SRAM contents are retained.</li> <li>External LPDDR2/LPDDR3 can be in self-refresh.</li> </ul>              |

| VLLS<br>(Very Low Leakage Stop) | <ul> <li>A7 domain fully power gated.</li> <li>Wake-up only via MU_A (CM4 domain) or reset.</li> <li>External LPDDR2/LPDDR3 can be in self-refresh.</li> </ul> |

#### Table 4. A7 low-power modes (continued)

## 5.3 VBAT domain low-power mode

VBAT mode is a low-power mode on the i.MX 7ULP in which only the VBAT Domain is powered. VBAT mode is a chip-level state with the following conditions:

- All power supplies except VDD\_VBAT42 are off externally.

- VDD VBAT42 is on and within the voltage range specified in the i.MX 7ULP datasheet.

- The Secure Real-Time Clock (SRTC) is maintained and running.

- Tamper logic is retained.

VBAT mode represents the state where the application would be off and a battery would retain the SRTC and tamper logic.

### 5.4 Low-power mode power measurements

Table 5 shows the power measurements for low-power modes, by running the power\_mode\_switch demo in AN12573SW.

Table 5. Low-power mode power measurements

| Test description <sup>1</sup>                  | Test procedure | Total 7ULP SoC power (mW) |

|------------------------------------------------|----------------|---------------------------|

| VBAT Mode                                      |                | 0.007                     |

| A7 is powered OFF externally.                  |                |                           |

| M4 is powered OFF externally.                  |                |                           |

| VBAT domain maintained and operational.        |                |                           |

| VDD_VBAT42 = 3.0 V                             |                |                           |

| Measured on Production Tester                  |                |                           |

| A7-OFF / M4-VLLS                               |                | 0.054                     |

| A7 is powered OFF externally (VDD_DIG1 = 0 V). | u-boot used:   |                           |

| LPDDR3 powered OFF externally.                 | Default u-boot |                           |

| M4 in VLLS mode (VDD_DIG0 = 0 V).              |                |                           |

| TCM banks in retention mode (256 KB).          |                |                           |

| VBAT domain maintained and operational.        | DTB used:      |                           |

|                                                |                |                           |

| Table 5. Low-power mode power measurements (contin |

|----------------------------------------------------|

|----------------------------------------------------|

| Test description <sup>1</sup>                                                                   | Test procedure                                                        | Total 7ULP SoC power (mW) |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| SoC can wake from GPIO or timer (based on 32 kHz clock).                                        | imx7ulp-evkb-ptest.dtb                                                |                           |

| All GPIOs (except the wakeup GPIO) disabled:                                                    |                                                                       |                           |

| <ul> <li>IOMUXC0_SW_MUX_CTL_PAD_n =<br/>0x00000000</li> </ul>                                   | M4 Image:                                                             |                           |

| <ul> <li>IOMUXC1_SW_MUX_CTL_PAD_n =<br/>0x00000000</li> </ul>                                   | Default imx7ulp_m4_demo.img                                           |                           |

| VDD_PTD = 0 V<br><b>NOTE</b>                                                                    | Kernel Image:                                                         |                           |

| This test case cannot<br>be measured on the<br>EVK as designed. For                             | zImage (with MLK-21499 patch)                                         |                           |

| details on the EVK<br>modifications required<br>for this test, see EVK<br>modifications for A7- | Procedure:                                                            |                           |

| OFF/M4-VLLS test.                                                                               | Power on the board                                                    |                           |

|                                                                                                 | On U-boot console:                                                    |                           |

|                                                                                                 | <ul> <li>— Disable TEE with setenv tee<br/>no<sup>2</sup>.</li> </ul> |                           |

|                                                                                                 | On Linux console                                                      |                           |

|                                                                                                 | — Put A7 into VLLS echo mem<br>> /sys/power/state.                    |                           |

|                                                                                                 | On M4 console                                                         |                           |

|                                                                                                 | — Press <b>U</b> to shut down A7.                                     |                           |

|                                                                                                 | <ul> <li>— Select power options 0, 2, 3, 4 in Z menu.</li> </ul>      |                           |

|                                                                                                 | — Press I, S to enter VLLS.                                           |                           |

|                                                                                                 | — Wait 50 seconds.                                                    |                           |

|                                                                                                 | <ul> <li>Press Z and F to collect data for<br/>one minute.</li> </ul> |                           |

|                                                                                                 | Calculate the average power consumption.                              |                           |

| A7-VLLS / M4-VLLS                                                                               |                                                                       | 0.123                     |

| A7 in VLLS mode (VDD_DIG1 = 0 V).                                                               | u-boot used:                                                          |                           |

| LPDDR3 in self-refresh mode.                                                                    |                                                                       |                           |

| M4 in VLLS mode (VDD_DIG0 = 0 V).                                                               | Default u-boot                                                        |                           |

| TCM banks in retention mode (256 KB).                                                           |                                                                       |                           |

| Only VBAT domain maintained and operational.                                                    | DTB used:                                                             |                           |

| Test description <sup>1</sup>                                                                            | Test procedure                                                        | Total 7ULP SoC power (mW) |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------------------|

| SoC can wake from GPIO or timer (based on 32 kHz clock).<br>All GPIOs (except the wakeup GPIO) disabled: | imx7ulp-evkb-ptest.dtb                                                |                           |

| <ul> <li>IOMUXC0_SW_MUX_CTL_PAD_n =<br/>0x00000000</li> </ul>                                            | <br>M4 Image:                                                         |                           |

| <ul> <li>IOMUXC1_SW_MUX_CTL_PAD_n =<br/>0x00000000</li> <li>VDD_PTD = 0 V</li> </ul>                     | <br>Default imx7ulp_m4_demo.img                                       |                           |

| Measured on MCIMX7ULP-EVK                                                                                | Kernel Image:                                                         |                           |

|                                                                                                          | zImage (with MLK-21499 patch)                                         |                           |

|                                                                                                          | Procedure:                                                            |                           |

|                                                                                                          | Power on the board                                                    |                           |

|                                                                                                          | On U-boot console:                                                    |                           |

|                                                                                                          | <ul> <li>Disable TEE with setenv tee<br/>no<sup>2</sup>.</li> </ul>   |                           |

|                                                                                                          | On Linux console                                                      |                           |

|                                                                                                          | — Put A7 into VLLS echo mem<br>> /sys/power/state.                    |                           |

|                                                                                                          | On M4 console                                                         |                           |

|                                                                                                          | <ul> <li>— Select power options 2, 3, 4 in Z menu.</li> </ul>         |                           |

|                                                                                                          | — Press I, S to enter VLLS.                                           |                           |

|                                                                                                          | <ul> <li>Press Z and F to collect data for<br/>one minute.</li> </ul> |                           |

|                                                                                                          | Calculate the average power consumption.                              |                           |

#### Table 5. Low-power mode power measurements (continued)

1. Apply 0001-MLK-21499-arm-imx-put-pads-into-OFF-state-before-ent.patch to kernel.

2. With patched zImage, kernel may not be able to load modules. It results in failure when entering suspend mode. So we disabled TEE. To avoid the failure, build in CAAM module to kernel or copy CAAM modules built with patched kernel to rootfs. Don't forget to use lsmod command to check whether CAAM modules are loaded.

### 5.4.1 EVK modifications for A7-OFF/M4-VLLS test

According to i.MX 7ULP Applications Processor - Consumer Products data sheet (document IMX7ULPCEC), VDD\_DIG1 must remain powered if the following supplies are powered: VDD\_USB18, VDD\_USB33, VDD\_DS118 and VDD\_DS111. If the USB and DSI supplies are not used/powered, VDD\_DIG1 can be turned off at the board level.

On the EVK, the i.MX 7ULP VDD\_USB33 supply is connected to the EVK VDD\_3V3 rail, so to achieve lowest power consumption VDD DIG1 and VDD 3V3 would need to be turned off.

VDD\_3V3 is derived from EVK supply PMC\_3V3 via a low enabled load switch. PTA25 is configured to output HIGH to disable the load switch. Driving PTA25 low turns off VDD\_3V3. Power measurements on the i.MX 7ULP after the design of the EVK indicated that lower leakage power is achieved by leaving VDD\_PTA/B/C/E/F powered instead of turning them off. VDD\_PTD may be powered off.

To achieve lower power consumption, STANDBY\_REQ was used instead of PTA25 to control the load switch. The EVK was modified to connect STANDBY\_REQ to PTA25, and PTA25 was configured as an input. STANDBY\_REQ was chosen because it doesn't belong to a GPIO group; it is controlled by the SIM.

All other GPIOs were disabled by configuring IOMUXC0\_SW\_MUX\_CTL\_PAD\_n to 0x00000000 and IOMUXC1\_SW\_MUX\_CTL\_PAD\_n to 0x00000000.

## 5.5 Real-time domain (M4) active power measurements

Table 6 shows power measurements active power measurements for the Real-Time Domain by running Coremark on the M4 core. For instructions on how to build required Coremark MCU SDK demo images, see How to build out coremark\_tcm.img and coremark\_flash.img.

| Test description <sup>1</sup>                                                                                                                                       | Test conditions                                                                                                               | Test procedure                                                          | M4 code<br>location | Total 7ULP<br>SoC Power<br>(mW) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------|---------------------------------|

| M4 Active                                                                                                                                                           | AD:                                                                                                                           |                                                                         | ТСМ                 | 22.03                           |

| <ul> <li>- Normal Performance<br/>(96 Mhz)</li> <li>A7 in VLLS mode</li> <li>M4 in RUN mode (96<br/>MHz from SPLL)</li> <li>Running Coremark<sup>2</sup></li> </ul> | VDD_DIG1 = 0V;<br>All clocks OFF<br>RTD:<br>VDD_DIG0 = 0.9 V<br>SPLL=480 MHz<br>• Core Clock: 96 MHz<br>• Platform Clock: 96  | u-boot used:<br>Default u-boot<br>DTB used:<br>                         | QSPI                | 26.08                           |

|                                                                                                                                                                     | <ul> <li>MHz</li> <li>Bus Clock: 48 MHz</li> <li>Slow Clock: 16 MHz</li> <li>APLL OFF</li> <li>Module clock state1</li> </ul> | M4 Image:<br>                                                           |                     |                                 |

|                                                                                                                                                                     |                                                                                                                               | <br>Kernel Image:<br><br>zImage (with MLK-21499 patch)<br><br>Procedure |                     |                                 |

Table 6. Real-Time Domain (M4) active power measurements

| Test description <sup>1</sup>                              | Test conditions                                | Test procedure                                                      | M4 code<br>location | Total 7ULP<br>SoC Power<br>(mW) |

|------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------|---------------------|---------------------------------|

|                                                            |                                                | Power on the board                                                  |                     |                                 |

|                                                            |                                                | On U-boot console:                                                  |                     |                                 |

|                                                            |                                                | <ul> <li>Disable TEE with setenv<br/>tee no<sup>3</sup>.</li> </ul> |                     |                                 |

|                                                            |                                                | On Linux console                                                    |                     |                                 |

|                                                            |                                                | — Put A7 into VLLS<br>echo mem > /sys/<br>power/state.              |                     |                                 |

|                                                            |                                                | On M4 console                                                       |                     |                                 |

|                                                            |                                                | <ul> <li>Press a to enter RUN mode.</li> </ul>                      |                     |                                 |

|                                                            |                                                | — Press c to run Coremark.                                          |                     |                                 |

| M4 Active                                                  | AD:                                            |                                                                     | тсм                 | 9.05                            |

| Low Performance     Clock Config 1                         | VDD_DIG1 = 0V; All<br>clocks OFF               | u-boot used:                                                        | QSPI                | 11.04                           |

| A7 in VLLS mode                                            | RTD:                                           | Default u-boot                                                      |                     |                                 |

| <ul> <li>M4 in VLPR mode (48<br/>MHz from FIRC)</li> </ul> | VDD_DIG0 = 0.85 V;<br>RBB enabled              |                                                                     |                     |                                 |

| Running coremark                                           | FIRC =48 MHz                                   | DTB used:                                                           |                     |                                 |

| -                                                          | Core Clock: 48 MHz                             |                                                                     |                     |                                 |

|                                                            | <ul> <li>Platform Clock: 48<br/>MHz</li> </ul> | imx7ulp-evkb-ptest.dtb                                              |                     |                                 |

|                                                            | Bus Clock: 48 MHz     Slow Clock: 24 MHz       | M4 Image:                                                           |                     |                                 |

|                                                            | SPLL and APLL OFF                              | coremark_tcm.img (for TCM)                                          |                     |                                 |

|                                                            | Module clock state1                            | coremark_flash.img (for XIP in SPI Flash)                           |                     |                                 |

|                                                            |                                                | Kernel Image:                                                       |                     |                                 |

|                                                            |                                                | zImage (with MLK-21499 patch)                                       |                     |                                 |

|                                                            |                                                | Procedure                                                           |                     |                                 |

#### Table 6. Real-Time Domain (M4) active power measurements (continued)

| Test description <sup>1</sup>                              | Test conditions                                                    | Test procedure                                                         | M4 code<br>location | Total 7ULP<br>SoC Power<br>(mW) |

|------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|---------------------------------|

|                                                            |                                                                    | Power on the board                                                     |                     |                                 |

|                                                            |                                                                    | On U-boot console:                                                     |                     |                                 |

|                                                            |                                                                    | - Disable TEE with setenv tee no <sup>3</sup> .                        |                     |                                 |

|                                                            |                                                                    | On Linux console                                                       |                     |                                 |

|                                                            |                                                                    | — Put A7 into VLLS<br>echo mem > /sys/<br>power/state.                 |                     |                                 |

|                                                            |                                                                    | On M4 console                                                          |                     |                                 |

|                                                            |                                                                    | <ul> <li>Press d to use FIRC for<br/>VLPR (Clock Config 1).</li> </ul> |                     |                                 |

|                                                            |                                                                    | <ul> <li>Press b to enter VLPR<br/>mode.</li> </ul>                    |                     |                                 |

|                                                            |                                                                    | - Press c to run Coremark.                                             |                     |                                 |

| //4 Active                                                 | AD:                                                                |                                                                        | тсм                 | 7.74                            |

| Low Performance                                            | VDD_DIG1 = 0V; All                                                 | u-boot used:                                                           | QSPI                | 9.73                            |

| Clock Config 2                                             | clocks OFF                                                         |                                                                        |                     |                                 |

| A7 in VLLS mode                                            | RTD:                                                               | Default u-boot                                                         |                     |                                 |

| <ul> <li>M4 in VLPR mode (48<br/>MHz from FIRC)</li> </ul> | VDD_DIG0 = 0.85V;<br>RBB enabled                                   |                                                                        |                     |                                 |

| Running coremark                                           | FIRC =48Mhz                                                        | DTB used:                                                              |                     |                                 |

|                                                            | <ul> <li>Core Clock: 48 MHz</li> <li>Platform Clock: 48</li> </ul> | imx7ulp-evkb-ptest.dtb                                                 |                     |                                 |

|                                                            | MHz                                                                |                                                                        |                     |                                 |

|                                                            | Bus Clock: 24 MHz                                                  | M4 Image:                                                              |                     |                                 |

|                                                            | Slow Clock: 8 MHz                                                  |                                                                        |                     |                                 |

|                                                            | SPLL and APLL OFF                                                  | coremark_tcm.img (for TCM)                                             |                     |                                 |

|                                                            | Module clock state1                                                | coremark_flash.img (for XIP in SPI Flash)                              |                     |                                 |

|                                                            |                                                                    | Kernel Image:                                                          |                     |                                 |

|                                                            |                                                                    | zImage (with MLK-21499 patch)                                          |                     |                                 |

#### Table 6. Real-Time Domain (M4) active power measurements (continued)

| Test description <sup>1</sup>                              | Test conditions                                | Test procedure                                                         | M4 code<br>location | Total 7ULP<br>SoC Power<br>(mW) |

|------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------|---------------------|---------------------------------|

|                                                            |                                                | Procedure                                                              |                     |                                 |

|                                                            |                                                | Power on the board                                                     |                     |                                 |

|                                                            |                                                | On U-boot console:                                                     |                     |                                 |

|                                                            |                                                | - Disable TEE with setenv tee no <sup>3</sup> .                        |                     |                                 |

|                                                            |                                                | On Linux console                                                       |                     |                                 |

|                                                            |                                                | — Put A7 into VLLS<br>echo mem > /sys/<br>power/state.                 |                     |                                 |

|                                                            |                                                | On M4 console                                                          |                     |                                 |

|                                                            |                                                | <ul> <li>Press e to use FIRC for<br/>VLPR (Clock Config 2).</li> </ul> |                     |                                 |

|                                                            |                                                | <ul> <li>Press b to enter VLPR<br/>mode.</li> </ul>                    |                     |                                 |

|                                                            |                                                | — Press c to run coremark.                                             |                     |                                 |

| M4 Active                                                  | AD:                                            |                                                                        | тсм                 | 4.58                            |

| Very Low Performance                                       | VDD_DIG1 = 0V; All                             | u-boot used:                                                           | QSPI                | 5.54                            |

| Clock Config 2                                             | clocks OFF                                     |                                                                        |                     |                                 |

| • A7 in VLLS mode                                          | RTD:                                           | Default u-boot                                                         |                     |                                 |

| <ul> <li>M4 in VLPR mode (16<br/>MHz from SIRC)</li> </ul> | VDD_DIG0 = 0.85 V;<br>RBB enabled              |                                                                        |                     |                                 |

| Running coremark                                           | SIRC =16 MHz                                   | DTB used:                                                              |                     |                                 |

|                                                            | Core Clock: 16 MHz                             |                                                                        |                     |                                 |

|                                                            | <ul> <li>Platform Clock: 16<br/>MHz</li> </ul> | imx7ulp-evkb-ptest.dtb                                                 |                     |                                 |

|                                                            | Bus Clock: 16 MHz                              | M4 Image:                                                              |                     |                                 |

|                                                            | Slow Clock: 8 MHz                              |                                                                        |                     |                                 |

|                                                            | SPLL and APLL OFF                              | coremark_tcm.img (for TCM)                                             |                     |                                 |

|                                                            | Module clock state1                            | coremark_flash.img (for XIP in<br>SPI Flash)                           |                     |                                 |

|                                                            |                                                | Kernel Image:                                                          |                     |                                 |

#### Table 6. Real-Time Domain (M4) active power measurements (continued)

| Test description <sup>1</sup> | Test conditions | Test procedure                                         | M4 code<br>location | Total 7ULP<br>SoC Power<br>(mW) |

|-------------------------------|-----------------|--------------------------------------------------------|---------------------|---------------------------------|

|                               |                 | zImage (with MLK-21499 patch)                          |                     |                                 |

|                               |                 | Procedure                                              |                     |                                 |

|                               |                 | Power on the board                                     |                     |                                 |

|                               |                 | On U-boot console:                                     |                     |                                 |

|                               |                 | - Disable TEE with setenv tee no <sup>3</sup> .        |                     |                                 |

|                               |                 | On Linux console                                       |                     |                                 |

|                               |                 | — Put A7 into VLLS<br>echo mem > /sys/<br>power/state. |                     |                                 |

|                               |                 | On M4 console                                          |                     |                                 |

|                               |                 | <ul> <li>Press f to use SIRC for<br/>VLPR.</li> </ul>  |                     |                                 |

|                               |                 | <ul> <li>Press b to enter VLPR<br/>mode.</li> </ul>    |                     |                                 |

|                               |                 | - Press c to run coremark.                             |                     |                                 |

| Table 6. Real-Time Domain (M4) active power measurements (continued) |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

- 1. Linux Kernel: Apply 0001-MLK-21499-arm-imx-put-pads-into-OFF-state-before-ent.patch and rebuild kernel Image.

- 2. Coremark MCU SDK demo images: see How to build out coremark\_tcm.img and coremark\_flash.img

- 3. The reason we disabled TEE here is that with patched zImage, kernel may not be able to load modules. It results in failure when entering suspend mode. To avoid this, user can build in CAAM module into kernel or copy CAAM modules built with patched kernel to rootfs. Don't forget to use Ismod command to check whether CAAM modules are loaded.

RTD Modules clock state:

- Clock active in VLPR and RUN: RPIO2P0, MUA, LPUART0, PCTLA, QSPI (only when M4 running from QSPI else disabled).

- All other RTD module clocks are disabled.

#### 5.5.1 How to build out coremark\_tcm.img and coremark\_flash.img

The coremark tcm.img and coremark flash.img are used to measure power in M4 active power measurements.

To build out these two images, perform the following steps.

1. Get Coremark project from AN12573SW and put the coremark project into *boards/evkmcimx7ulp/demo\_apps/*in SDK 2.11.

Figure 2 shows the directory tree in *boards/evkmcimx7ulp/demo\_apps*.

| bubble                 | 2021/12/15 16:44 | File folder |  |

|------------------------|------------------|-------------|--|

| coremark               | 2021/12/24 17:12 | File folder |  |

| ecompass               | 2021/12/15 16:44 | File folder |  |

| hello_world            | 2021/12/15 16:44 | File folder |  |

| h lpi2c_vlps           | 2021/12/15 16:44 | File folder |  |

| pmc_temperature_sensor | 2021/12/15 16:44 | File folder |  |

| power_mode_switch      | 2021/12/15 16:44 | File folder |  |

| shell_mem              | 2021/12/15 16:44 | File folder |  |

| wireless_uart_bridge   | 2021/12/15 16:44 | File folder |  |

|                        |                  |             |  |

|                        |                  |             |  |

| ure 2. Directory tree  |                  |             |  |

- 2. Download latest Coremark source code from https://github.com/eembc/coremark with tag v1.01 and copy all Coremark code to *boards/evkmcimx7ulp/demo\_apps/coremark/coremark*.

- 3. Apply SDK Coremark patch, 0001-Add-patch-for-coremark-code-for-VLPR.patch, to Coremark project.

```

$ patch -p1 < ./0001-Add-patch-for-coremark-code-for-VLPR.patch

patching file boards/evkmcimx7ulp/demo_apps/coremark/coremark/core_main.c

patching file boards/evkmcimx7ulp/demo_apps/coremark/coremark/core_portme.c

patching file boards/evkmcimx7ulp/demo_apps/coremark/coremark/core_portme.h

patching file boards/evkmcimx7ulp/demo_apps/coremark/coremark_cfg.h

```

Figure 3. Applying SDK Coremark patch

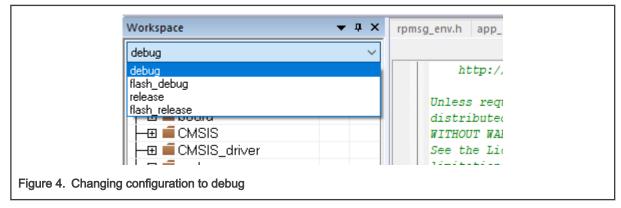

- 4. Open Coremark project, coremark.eww, in IAR.

- 5. Build out coremark.bin with debug configurations in IAR.

- a. Change the configuration to **debug**.

b. Click build to generate coremark.bin.

| > < >                    | ▋■ⅠΟ●〕ः…〕                                       |  |

|--------------------------|-------------------------------------------------|--|

| e_portme.c coremark.     | Make (F7)                                       |  |

| /LICENSE-2.0             | Make the active project (build files as needed) |  |

|                          |                                                 |  |

| Figure 5. Clicking Build |                                                 |  |

- 6. Build out coremark.bin with flash\_debug configurations in IAR.

- a. Change the configuration to flash debug.

| Workspace                                      | <b>▼</b> ₽ × | rpmsg |

|------------------------------------------------|--------------|-------|

| debug                                          | ~            |       |

| debug                                          |              |       |

| flash_debug<br>release<br>flash_release        |              |       |

|                                                |              |       |

| igure 6. Changing configuration to flash_debug |              |       |

b. Click build to generate coremark.bin.

| > < >   []               |                                                 |

|--------------------------|-------------------------------------------------|

| e_portme.c coremark.     | Make (F7)                                       |

| /LICENSE-2.0             | Make the active project (build files as needed) |

| ,                        |                                                 |

| Figure 7. Clicking Build |                                                 |

- 7. Use image tool to generate coremark\_tcm.img.

- a. Copy coremark.bin from <coremark\_project\_dir>/iar/debug/ to <SDK\_DIR>/tools/imgutil/evkmcimx7ulp/ and rename to sdk20-app.bin.

- b. Enter <SDK\_DIR>/tools/imgutil/evkmcimx7ulp.

- c. Use the command of ./mkimg.sh ram to generate sdk20-app.img and rename to coremark\_tcm.img.

- 8. To generate coremark\_flash.img, use the image tool.

- a. Copy coremark.bin from <coremark\_project\_dir>/iar/flash\_debug/to <SDK\_DIR>/tools/imgutil/evkmcimx7ulp/ and rename to sdk20-app.bin.

- b. Enter <SDK\_DIR>/tools/imgutil/evkmcimx7ulp.

- c. Use the command of ./mkimg.sh flash to generate sdk20-app.img and rename to coremark flash.img.

## 5.6 Application domain (A7) active power measurements

Table 7 shows the active power measurements for the Application Domain.

| Test description <sup>1</sup>                   | Test procedure                                   | Total 7ULP Soc power (mW) | Score              |

|-------------------------------------------------|--------------------------------------------------|---------------------------|--------------------|

| A7 Active                                       |                                                  | 159.41                    | - copy bandwidth:  |

| Low Performance                                 |                                                  |                           | 1504 MB/s          |

| Execution from external                         | u-boot used:                                     |                           | - scale bandwidth: |

| LPDDR3                                          |                                                  |                           | 655 MB/s           |

| No graphics/display                             | Default u-boot                                   |                           | - add bandwidth:   |

| • A7 in RUN mode (500<br>MHz; VDD_DIG1 = 1.1 V) |                                                  |                           | 595 MB/s           |

| Running STREAM core                             |                                                  |                           | - triad bandwidth: |

| benchmark                                       | DTB used:                                        |                           | 655 MB/s           |

| M4 in VLPS mode                                 |                                                  |                           |                    |

| No GPU or display     activity                  |                                                  |                           |                    |

| DVFS disabled                                   | imx7ulp-evkb.dtb                                 |                           |                    |

| LPDDR3 at 352.8 MHz                             |                                                  |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | M4 Image:                                        |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | Default                                          |                           |                    |

|                                                 | imx7ulp_m4_demo.img                              |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | Kernel Image:                                    |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | Default zImage                                   |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | Command line in u-boot:                          |                           |                    |

|                                                 | Command line in u-bool.                          |                           |                    |

|                                                 |                                                  |                           |                    |

|                                                 | Disable DVFS by adding                           |                           |                    |

|                                                 | " <i>cpufreq.off=1</i> " to bootargs             |                           |                    |

|                                                 | in u-boot                                        |                           |                    |

|                                                 | <i>=&gt; setenv mmcargs<br/>"setenv bootargs</i> |                           |                    |

|                                                 | console=ttyLP0,115200                            |                           |                    |

|                                                 | root=\${mmcroot}<br>cpufreq.off=1" => saveenv    |                           |                    |

|                                                 | , , , , , , , , , , , , , , , , , , , ,          |                           |                    |

Table 7. Application Domain (A7) active power measurements on default release

| Test description <sup>1</sup>                                      | Test procedure                                                                                                                                          | Total 7ULP Soc power (mW) | Score              |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------|

|                                                                    | Command line in M4 console:<br><br>Press F> to set the M4 in<br>VLPS mode<br>Press S> to wake up with<br>VOL+ button<br><br>Command line in kernel:<br> |                           |                    |

|                                                                    | root@imx7ulpevk:~# stream                                                                                                                               |                           |                    |

| A7 Active                                                          |                                                                                                                                                         | 224.64                    | glmark2 Score: 122 |

| High Performance                                                   | u-boot used:                                                                                                                                            |                           |                    |

| <ul> <li>Execution from external<br/>LPDDR3</li> </ul>             |                                                                                                                                                         |                           |                    |

| With 2D graphics/display                                           |                                                                                                                                                         |                           |                    |