# AN12788

## Emulating LIN Master/Slave with the FlexIO on i.MX RT Series MCU

Rev. 0 — March, 2020 Application Note

## 1 Introduction

This application note describes how to use FlexIO module to emulate LIN (Local Interconnect Network) bus based on i.MX RT series platform.

LIN is a widely used serial network protocol between components in vehicles. While the RT series MCU does not directly support LIN peripheral, the LPUART module of i.MX RT series can emulate the LIN bus. The FlexIO module can be a good workaround when LPUART is occupied.

FlexIO is an on-chip peripheral available on NXP i.MX RT series. It is a highly configurable module which is capable of emulating a wide range of communication protocols, such as UART, I2C, SPI, I2S, and so on. Users can also use FlexIO to emulate LIN bus.

This application creates a simple software demo based on the i.MX RT series platform for users to use FlexIO module emulating LIN Master&Slave with related configurations.

| 1 Introduction                  | 1      |

|---------------------------------|--------|

| 2 LIN overview                  | 1      |

| 3 Emulating LIN by using FlexIO | 2<br>4 |

| 4 Run the example               |        |

| 5 References                    | 12     |

| 6 Pevision history              | 13     |

**Contents**

## 2 LIN overview

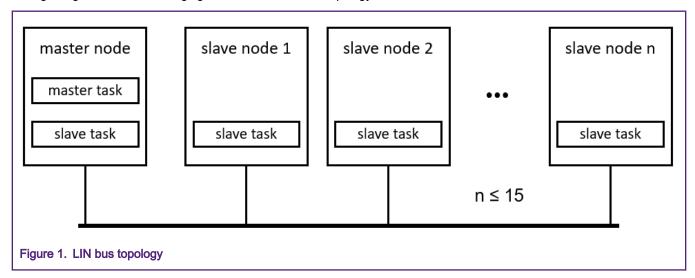

LIN is a low-cost serial communication protocol based on UART/SCI. LIN bus adopts the communication mode of one master and multiple slaves, and the transmission rate of LIN can reach up to 20 kbit/s. A LIN communication network can connect up to 16 nodes, 1 host node, and 1 to 15 slave nodes. The topology of LIN bus is linear which means all node devices are connected through single line. The following figure shows the LIN bus topology.

The host node contains the host task and the slave task, while the slave node contains only the slave task. The master task decides when and which frame shall be transferred on the bus. The slave tasks provide the data transported by each frame.

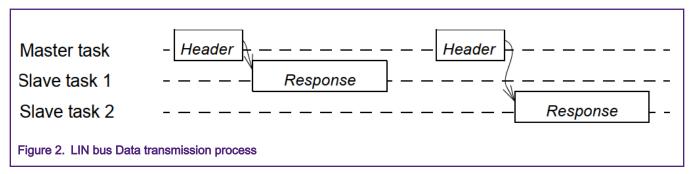

A frame of LIN consists of a header (provided by the master task) and a response (provided by a slave task). The host task sends the frame header, and the slave task determines whether to send or receive the response according to the frame header information. The following figure shows the data transmission process on the bus.

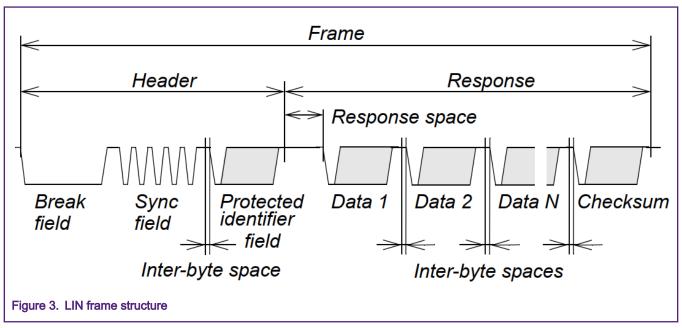

The header consists of a break field and sync field followed by a frame identifier. The frame identifier uniquely defines the purpose of the frame. The response consists of a data field and a checksum field. The following figure shows the structure of a complete data frame.

The break field is used to signal the beginning of a new frame and it shall be at least 13 nominal bit times of dominant value. The format of the rest of the data from the synchronous field to the checksum field is the same as that of the standard asynchronous serial port. For each byte of data, there is 1 low-level start bit(dominant bit), 1 high-level stop bit(recessive bit), and no checksum bit. A signal of LIN bus is transmitted with the LSB first and the MSB last. The sync field is a byte field with the data value 0x55.

## 3 Emulating LIN by using FlexIO

This chapter mainly introduces how to emulate LIN by using FlexIO module. LIN bus is a kind of low-cost serial communication system. So, the configuration of FlexIO used in emulating LIN is similar to that used in emulating UART.

## 3.1 LIN transmitter configuration

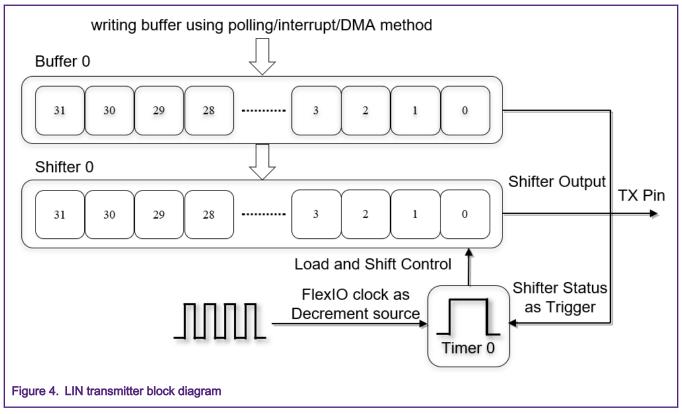

To emulate the LIN transmitter, users must use the following resources:

- One timer configured as 8-bit baud counter mode to control the data shift.

- · One shifter controlled by Timer to shift data from SHIFTBUF.

- · One pin connect to the Shifter to output data.

Application Note 2 / 14

Timer 0 is used to shift control the Shifter 0. The following figure shows the LIN transmitter block diagram.

Limited by the protocol, the baud rate of this application demo is set as 19200. The following table shows the configuration for Timer 0.

Table 1. Configurations for Timer 0

| Items            | Configurations                                                            |  |  |

|------------------|---------------------------------------------------------------------------|--|--|

| Trigger Select   | Shifter 0 status flag                                                     |  |  |

| Trigger Polarity | Active low                                                                |  |  |

| Trigger Source   | Internal trigger                                                          |  |  |

| Pin Config       | Output disable                                                            |  |  |

| Pin Select       | N/A                                                                       |  |  |

| Pin Polarity     | N/A                                                                       |  |  |

| Timer mode       | Dual 8-bit counters baud mode                                             |  |  |

| Timer Output     | Timer output is logic one when enabled and is not affected by timer reset |  |  |

| Timer Decrement  | Decrement counter on FlexIO clock, shift clock equals Timer output        |  |  |

| Timer Reset      | Timer never resets                                                        |  |  |

Table continues on the next page...

Application Note 3/14

Table 1. Configurations for Timer 0 (continued)

| Timer Disable   | Timer disabled on timer compare                                                          |  |  |

|-----------------|------------------------------------------------------------------------------------------|--|--|

| Timer Enable    | Timer enabled on trigger high                                                            |  |  |

| Timer Stop Bit  | Enabled on timer disable                                                                 |  |  |

| Timer Start Bit | Enable                                                                                   |  |  |

| Timer Compare   | ((bitCountPerChar <sup>1</sup> * 2 - 1) << 8)   (baudrate_divider <sup>2</sup> / 2 - 1)) |  |  |

- 1. bitCountPerChar is the number of bits of each data.

- 2. baudrate\_divider can be calculated from FlexIO clock divided by LIN baud rate.

In 8-bit Baud Counter Mode, the 16-bit counter is divided into two 8-bit counters. The lower 8-bits are used to configure the baud rate of the shift clock. The upper 8-bits are used to configure the number of shift clock edges in the transfer. When the lower 8-bits decrease to zero, the timer output is toggled and the lower 8-bits reload from the compare register. The upper 8-bits decrease when the lower 8-bits equal zero.

Table 2. Configurations for Shifter 0

| Items             | Configurations                        |  |  |

|-------------------|---------------------------------------|--|--|

| Timer Select      | Timer 0                               |  |  |

| Timer Polarity    | Shift on positive edge of shift clock |  |  |

| Pin Config        | Shifter pin output                    |  |  |

| Pin Select        | FlexIO_D21                            |  |  |

| Pin Polarity      | Active high                           |  |  |

| Shifter Mode      | Transmit mode                         |  |  |

| Input Source      | N/A                                   |  |  |

| Shifter Stop Bit  | Stop bit high                         |  |  |

| Shifter Start Bit | Start bit low                         |  |  |

The shifter status flag is set when SHIFTBUF data has been transferred to the Shifter (SHIFTBUF is empty), and the status flag is cleared when the SHIFTBUF register is written. The shifter status flag of Shifter 0 is configured to be the trigger of the Timer 0. So, as soon as the SHIFTBUT is written, the status flag is cleared and Timer 0 is enabled. The FlexIO\_D21 pin is configured as the data output pin. The Shifter 0 begins to shift out the data on the positive edge of the clock until the Timer 0 is disabled. Timer 0 is disabled when the timer counter counts down to 0.

## 3.2 LIN receiver configuration

To emulate the LIN receiver, use the following resources:

- One timer configured as 8-bit baud counter mode to control the data shift.

- · One shifter controlled by timer to input data into SHIFTBUF.

- One pin connect to the shifter to input data.

Application Note 4 / 14

5/14

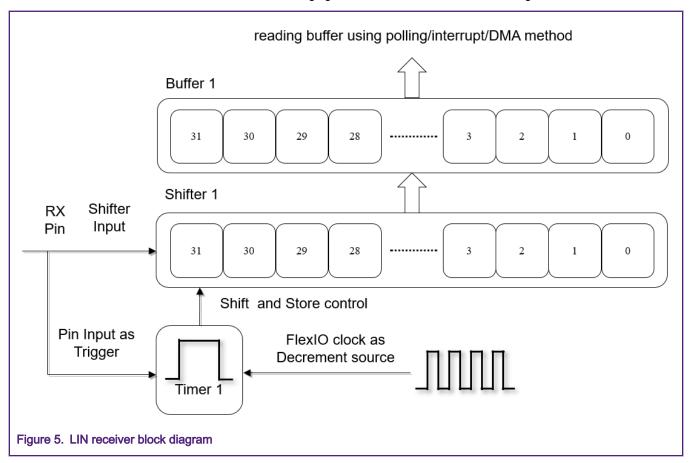

Timer 1 is used to shift control the Shifter 1. The following figure shows the LIN receiver block diagram.

Table 3. Configurations for Timer 1

| Items            | Configurations                                                     |  |  |

|------------------|--------------------------------------------------------------------|--|--|

| Trigger Select   | trigger from pin FlexIO_D26                                        |  |  |

| Trigger Polarity | active high                                                        |  |  |

| Trigger Source   | external trigger                                                   |  |  |

| Pin Config       | output disable                                                     |  |  |

| Pin Select       | N/A                                                                |  |  |

| Pin Polarity     | N/A                                                                |  |  |

| Timer mode       | dual 8-bit counters baud mode                                      |  |  |

| Timer Output     | Timer output is logic one when enabled and on timer reset          |  |  |

| Timer Decrement  | decrement counter on FlexIO clock, shift clock equals Timer output |  |  |

| Timer Reset      | Timer reset on Timer Pin rising edge                               |  |  |

Table continues on the next page...

Emulating LIN Master/Slave with the FlexIO on i.MX RT Series MCU, Rev. 0, March, 2020 **Application Note**

Table 3. Configurations for Timer 1 (continued)

| Timer Disable   | Timer disabled on Timer compare                                |  |  |

|-----------------|----------------------------------------------------------------|--|--|

| Timer Enable    | Fimer enabled on Pin rising edge                               |  |  |

| Timer Stop Bit  | enabled on timer disable                                       |  |  |

| Timer Start Bit | enable                                                         |  |  |

| Timer Compare   | ((bitCountPerChar * 2 - 1) << 8)   (baudrate_divider / 2 - 1)) |  |  |

The FlexIO\_D26 pin's rising edge is configured to enable the Timer 1. The Shifter 1 begins to shift in the data on the negative edge of the clock until the timer is disabled. The timer is disabled when the timer counter counts down to 0. Table 4 shows the configuration for Shifter 1.

Table 4. Configurations for Shifter 1

| Items             | Configurations                        |  |

|-------------------|---------------------------------------|--|

| Timer Select      | Timer 1                               |  |

| Timer Polarity    | Shift on negative edge of shift clock |  |

| Pin Config        | Output disable                        |  |

| Pin Select        | FlexIO_D26                            |  |

| Pin Polarity      | Active high                           |  |

| Shifter Mode      | Receive mode                          |  |

| Input Source      | Input from pin                        |  |

| Shifter Stop Bit  | Stop bit high                         |  |

| Shifter Start Bit | Start bit low                         |  |

### 3.3 LIN task model

The configurations of transmitter and receiver of emulating LIN bus are the same as emulating UART, but these configurations cannot meet the requirement of LIN host task generating break field. This section introduces how to implement LIN protocol data transmission and reception.

### 3.3.1 Header of frame

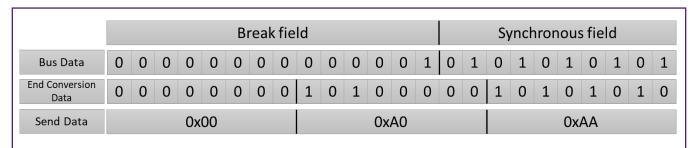

The length of break field is at least 13 bits dominant value (low level). However, the standard format data includes a recessive bit (high level), low level exceeding 9 bits cannot be transmitted under the normal configuration. So when master task needs to initiate a data transfer, the configuration of FlexIO needs to be changed to implement the break field. Since the break field and the synchronous field are fixed values, and the total number of bits of these two fields is 24 bits, we can disable the start and stop bits of the first three bytes. The following figure shows the structure of these two fields.

Application Note 6 / 14

Figure 6. Structure of break and synchronous field

When master node send the Header, users can change the setting of Timer 0 and Shifter 0:

- · Timer Stop Bit: Disable

- · Timer Start Bit: Disable

- · Shifter Stop Bit: Disable

- · Shifter Stop Bit: Disable

And set the send size as 3 bytes, send data as {0x00, 0xA0, 0xAA}.

A slave node shall use a break detection threshold of 11 dominant local slave bit times. Get rid of the first bit as the start bit. Change the upper 8 bits of the Timer 1, which configure the number of bits in each word, to a 10-bit per word.

• Timer Compare[15:8]: 0x13

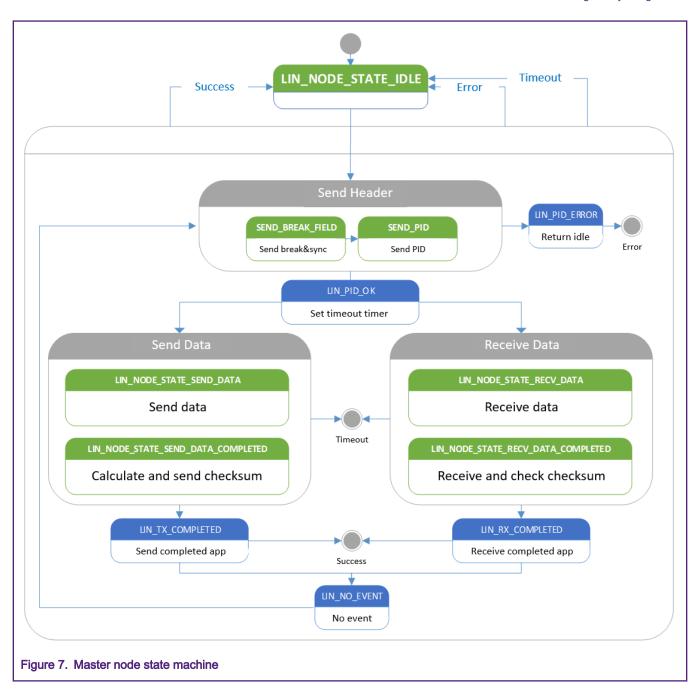

#### 3.3.2 Master node state machine

In this application, to simulate the send and response status, we set a state machine to manage the multiple running states. This state machine contains the application layer and the driver layer. This application sets two enumeration variables to represent the two layers. The following figure shows the state machine of LIN master node. Blue boxes represent application layer state, green boxes represent driver layer state.

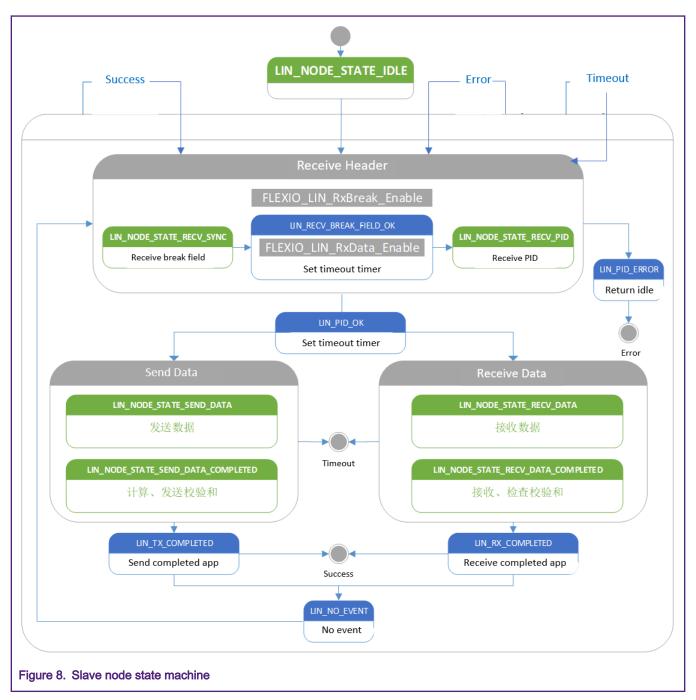

## 3.3.3 Slave node state machine

Same as the master node, the state machine of slave node also contains the application layer and the driver layer. The following figure shows the state machine of LIN slave node.

In this application, the slave node keeps monitoring the break field from the LIN bus. We use the FIEXIO\_LIN\_RxBreak\_Enable to change the setting for receiving break field and FIEXIO\_LIN\_RxData\_Enable to set configuration back to normal for receiving other fields.

## 4 Run the example

## 4.1 Development platform

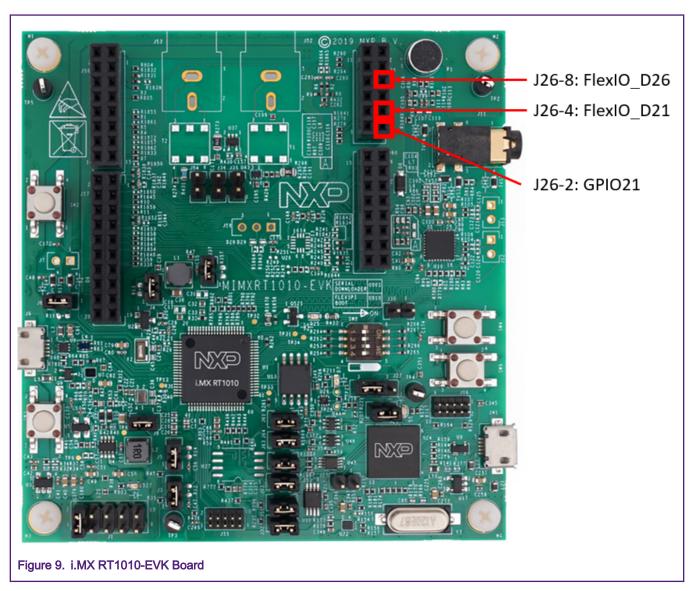

This document describes the example application based on the i.MX RT1010-EVK board shown in the following figure. Users can also easily enable this application on other i.MX RT series EVK board.

Emulating LIN Master/Slave with the FlexIO on i.MX RT Series MCU, Rev. 0, March, 2020

In this application, FlexIO using FlexIO\_D21 as the transmitting pin and FlexIO\_D26 as the receiving pin.

This demo uses two boards, one board as master and one board as slave. In order to comply with the physical layer standard of Lin bus, a LIN transceiver is needed. This demo uses two TJA1020 modules to implement the single-wire LIN. The transceiver uses GPIO21 to enable.

The connection between LIN nodes and transceivers is as follows:

Table 5. LIN nodes and transceiver connections

| Master Node     |          | Transceiver |          | Transceiver |          | Slave Node      |

|-----------------|----------|-------------|----------|-------------|----------|-----------------|

| J26-4(LIN_TX)   | <b>+</b> | RX LIN      | <b>+</b> | LIN TX      | <b>↔</b> | J26-8(LIN_RX)   |

| J26-8(LIN_RX)   | <b>*</b> | TX INH      |          | INH RX      | <b>*</b> | J26-4(LIN_TX)   |

| J26-2(Trans_EN) | <b>*</b> | SLP 12 V    |          | 12 V SLP    | <b>*</b> | J26-2(Trans_EN) |

| J60-14(GND)     | <b>*</b> | GND GND     | <b>↔</b> | GND GND     | <b>*</b> | J60-14(GND)     |

11 / 14

## 4.2 Run the demo

Users can download the software from www.nxp.com. Find the IAR project flexio\_LIN. This demo contains the master node and slave node codes which are separated by a macro. In flexio\_LIN\_driver.h file, set the macro FLEXIO\_LIN\_MODE as FLEXIO\_LIN\_SLAVE\_MODE and FLEXIO\_LIN\_MASTER\_NODE, and separately download to two boards, connect these boards and transceiver modules as above and run the two boards.

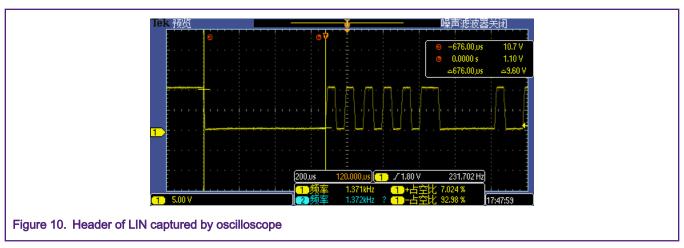

The following figure shows the waveform that an oscilloscope captures from the LIN bus.

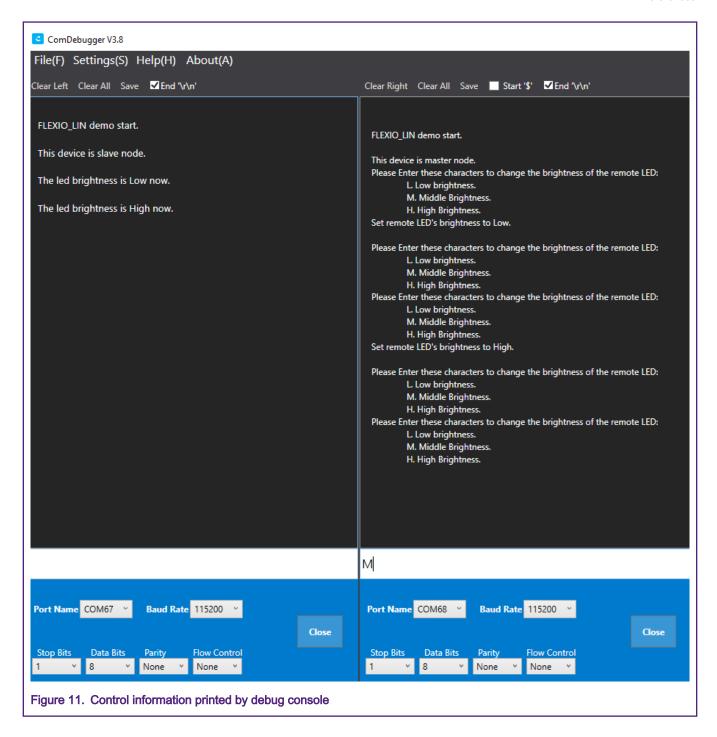

The following figure shows the information printed by debug port when the master node controls the slave node's LED brightness. Users can type in the characters 'L','M', or 'H' in the master node's debug console to change the remote slave node's LED brightness.

Emulating LIN Master/Slave with the FlexIO on i.MX RT Series MCU, Rev. 0, March, 2020

12 / 14

## 5 References

- 1. i.MX RT1010 Processor Reference Manual (document I.MXRT1010RM)

- 2. MCUXpresso SDK: Software Development Kit for NXP MCUs (https://mcuxpresso.nxp.com/en/welcome).

Application Note

# 6 Revision history

## Table 6. Revision history

| Revision number | Date    | Substantive changes |  |

|-----------------|---------|---------------------|--|

| 0               | 03/2020 | Initial release     |  |

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, UMEMS, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: March, 2020 Document identifier: AN12788