# AN13698 PCA9451A application note Rev. 2.0 — 26 May 2023

**Application note**

#### **Document Information**

| Information | Content                                                                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PCA9451A, I.MX 93x, PMIC                                                                                                                                                                                                             |

| Abstract    | This application note discusses the critical items needed in designing the PMIC PCA9451A in portable devices with an i.MX 93x application processor, and provides a guideline for component selection, placement, and trace routing. |

### PCA9451A application note

#### Revision history

| Rev   | Date     | Description                                        |

|-------|----------|----------------------------------------------------|

| v.2.0 | 20230526 | Updated Figure 1, Figure 2, Figure 3, and Figure 7 |

| v.1.0 | 20220830 | Initial version                                    |

### 1 Introduction

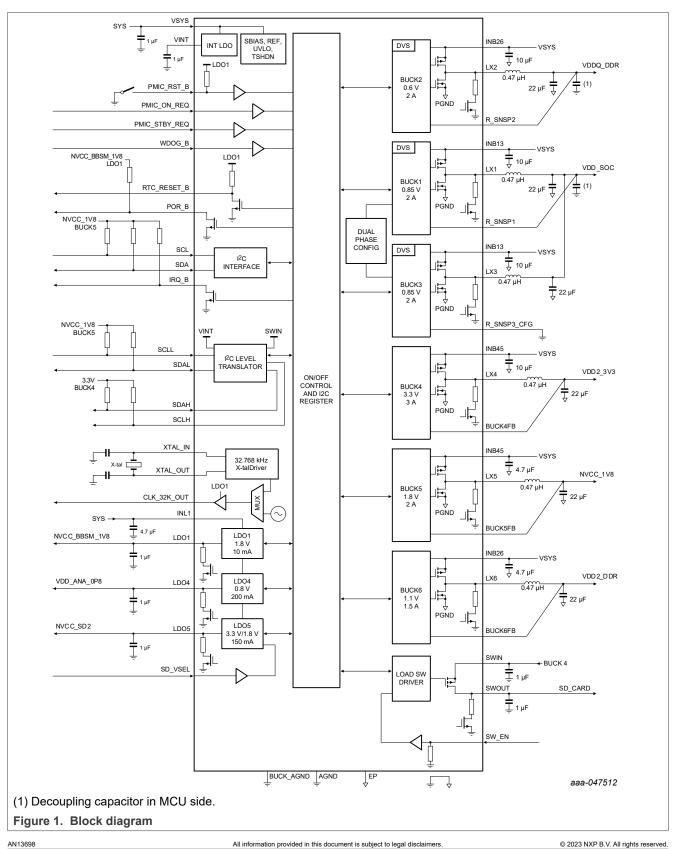

The PCA9451A is a single chip Power Management IC (PMIC) specifically designed to support i.MX 93x family processor in both 1 cell Li-Ion and Li-polymer battery portable application and 5 V adapter non-portable applications.

The device provides six high-efficiency step-down regulators, three LDOs, one 400 mA load switch, 2-channel level translator, and 32.768 kHz crystal oscillator driver. Three buck regulators support dynamic voltage scaling (DVS) feature along with programmable ramping up and down time; the buck regulators support remote sense to compensate IR drop to load. This device is characterized across -40 °C to 105 °C ambient temperature range.

Six step-down regulators are designed to provide power for i.MX 93x application processor and DRAM memory. One LDO (LDO1) feature very low quiescent current to provide power for Secure Non-Volatile Storage (SNVS) since this LDO is always ON when input voltage is valid.

PCA9451A integrates logic translator which is a 2-bit, dual supply translating transceiver with auto direction sensing. It enables bidirectional voltage level translation and can be used as an I<sup>2</sup>C level translator. A 400 mA load switch is to supply 3.3 V power supply to SD card, which has an internal discharge resistor.

The PCA9451A is offered in 56-pin HVQFN package, 7 mm x 7 mm, 0.4 mm pitch.

### 2 Features and benefits

- Six high-efficiency step-down regulators

- 4 A dual phase buck regulator with DVS feature and remote sense

- 2 A buck regulator with DVS feature and remote sense

- 3 A buck regulator

- 2 A buck regulator

- 1.5 A buck regulator

- Three linear regulators

- One 10 mA LDO

- One 150 mA LDO

- One 200 mA LDO

- 400 mA load switch with built-in active discharge resistor

- Two channel logic level translator

- 32.768 kHz crystal oscillator driver

- Power control IO

- Power ON/OFF control

- Standby/run mode control

- Fm+ 1 MHz I<sup>2</sup>C-bus interface

- ESD protection

- Human Body Model (HBM): ±2000 V

- Charged Device Model (CDM): ±500 V

- 7 mm x 7 mm, 56-pin HVQFN with 0.4 mm pitch

PCA9451A application note

### 3 Block diagram

# 4 Application design-in information

### 4.1 Reference schematic

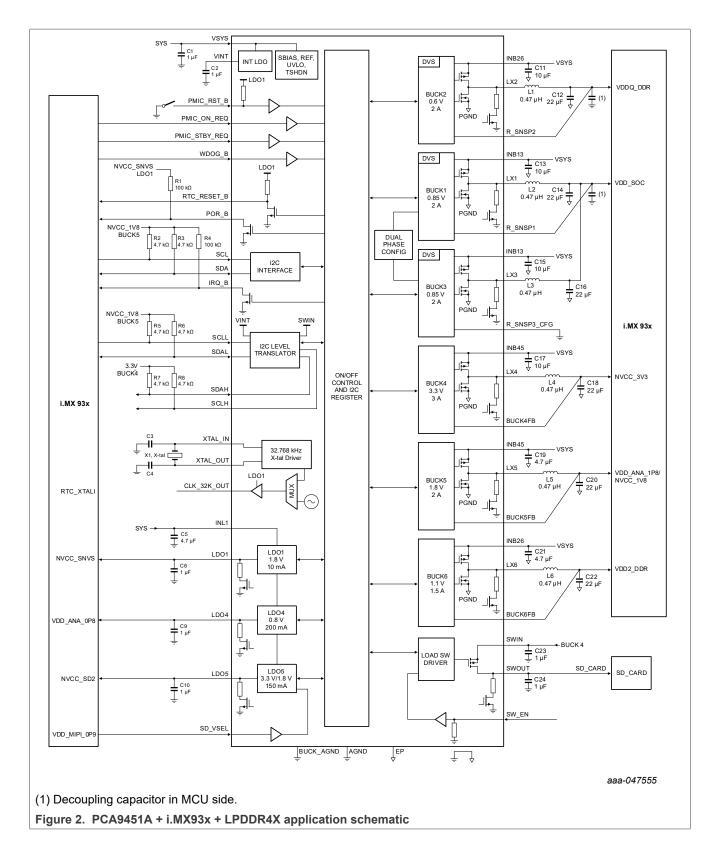

PCA9451A reference schematic with i.MX 93x + LPDDR4X is illustrated in Figure 2.

The schematic serves as a guide on how the output voltage rails on PCA9451A would be typically connected to the corresponding voltage domains on i.MX 93x, and external components such as the memories (DDR and or EMMC/SDHC). This configuration is not mandatory and the customer can make adjustments as long as the voltage and sequencing requirements for the processor are respected and are supported by PCA9451A.

Please refer to the corresponding i.Mx 93x EVK for detailed design information and schematic/layout source files.

### PCA9451A application note

### 4.2 Typical application

The PCA9451A device has only a few design requirements, as follows:.

- 1 µF bypass capacitor on VINT and VSYS, located as close as possible to those pins to ground

- If using INB and INL supplies, input capacitors must be present

- Output inductors and capacitors must be used on the outputs of the BUCK converters if used

- · Output capacitors must be used on the outputs of the LDOs

#### 4.2.1 Inductor selection for buck converters

Each of the converters in the PCA9451A typically use a 0.47  $\mu$ H output inductor which has to be rated for its DC resistance and saturation current. The DC resistance of the inductance influences directly the efficiency of the converter. Therefore, an inductor with lowest DC resistance must be selected for highest efficiency.

<u>Equation 1</u> calculates the maximum inductor current under static load conditions. The saturation current of the inductor must be rated higher than the maximum inductor current as calculated with <u>Equation 2</u>. This is needed because during heavy load transient the inductor current rises above the calculated value.

| $\Delta I_L = Vout \times \frac{1 - \frac{Vout}{Vinmax}}{L \times f}$ | (1) |

|-----------------------------------------------------------------------|-----|

| $I_{Lmax} = I_{out.max} \times \frac{\Delta I_L}{2}$                  | (2) |

Where

f = switching frequency (2 MHz )

L = Inductance

$\Delta I_L$  = Peak to peak inductor ripple current

I<sub>L.max</sub> = Maximum inductor current

A conservative approach is to select the inductor current rating just for the maximum switch current of the PCA9451A

Table 1 shows possible inductors list.

| Table | 1 | Tested | inductor | list |

|-------|---|--------|----------|------|

| Table |   | resteu | maucior  | IIJL |

| Buck             | Vendor  | Part number           | Inductance<br>[uH] | Size [mm] | DCR [mΩ] | Isat [A] | Irat [A] |

|------------------|---------|-----------------------|--------------------|-----------|----------|----------|----------|

| BUCK1,<br>BUCK2, | Sunlord | WPN252012<br>HR47MT   | 0.47               | 2520      | 29       | 5.6      | 4.0      |

| BUCK3,<br>BUCK4  | Murata  | 1239AS-H-<br>R47M     | 0.47               | 2520      | 39       | 3.8      | 3.7      |

|                  | Cyntec  | HMLB25201<br>B-R47MSR | 0.47               | 2520      | 26       | 4.55     | 4.0      |

| BUCK5,<br>BUCK6  | Sunlord | WPN201610<br>UR47MT   | 0.47               | 2016      | 28       | 5.0      | 4.1      |

|                  | Murata  | 1286AS-H-<br>R47M     | 0.47               | 2016      | 52       | 3.4      | 3.2      |

|                  | Cyntec  | HTEP20120<br>H-R47MSR | 0.47               | 2012      | 29       | 4.3      | 3.7      |

© 2023 NXP B.V. All rights reserved.

#### **4.2.2** Output capacitor selection for buck converters

The fast response adaptive constant ON time control scheme of the buck converters implemented in the PCA9451A allows the use of small ceramic capacitors with a typical value of 22  $\mu$ F for each converter without having large output voltage under and overshoots during heavy load transients. Ceramic capacitors having low ESR values have the lowest output voltage ripple and are recommended. See <u>Table 2</u> for recommended capacitor.

#### Table 2. Recommended capacitor

| BUCK                           | Vendor | Part number         | Capacitance [µF] | Size [mm] | Voltage [V] |

|--------------------------------|--------|---------------------|------------------|-----------|-------------|

| BUCK1, BUCK2,<br>BUCK3, BUCK4, | TDK    | C1608X5R1A226M080AC | 22               | 0603      | 10          |

|                                | TDK    | C1608JB1A226M080AC  | 22               | 0603      | 10          |

| BUCK5, BUCK6                   | Murata | GRT21BC81A226ME     | 22               | 0805      | 10          |

If ceramic output capacitors are used, the capacitor RMS ripple current rating always meets the application requirements. Just for completeness, the RMS ripple current is calculated in <u>Equation 3</u>.

$$I_{RMS.COUT} = \text{Vout} \times \frac{1 - \frac{\text{Vout}}{\text{Vin}}}{L \times f} \times \frac{1}{2\sqrt{3}}$$

(3)

At nominal load current, the inductive converters operate in PWM mode. The overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\Delta \text{Vout} = \text{Vout} \times \frac{1 - \frac{Vout}{Vin}}{L \times f} \times \left(\frac{1}{8 \times Cout \times f} + ESR\right)$$

(4)

Where:

• The highest output voltage ripple occurs at the highest input voltage Vin.

At light load currents, the converters operate in PFM mode and the output voltage ripple is dependent on the output capacitor value. The internal comparator delay and the external capacitor set the output voltage ripple, which is less than 1 % of the nominal output voltage.

#### 4.2.3 Input capacitor selection for buck converters

Low ESR input capacitor is highly recommended for best input voltage filtering and minimizing the interference with other circuits caused by high input voltage spikes because of the nature of buck converter. Each DC-DC converter requires a 10  $\mu$ F ceramic input capacitor on its input pins. The input capacitor could be increased without any limit for better input voltage filtering. See <u>Table 3</u> for recommended capacitor.

| BUCK                                           | Vendor  | Part number        | Capacitance [µF] | Size [mm] | Voltage [V] |

|------------------------------------------------|---------|--------------------|------------------|-----------|-------------|

| BUCK1, BUCK2,<br>BUCK3, BUCK4,<br>BUCK5, BUCK6 | Murata  | GRM188R60J106ME    | 10               | 1608      | 6.3         |

|                                                | Samsung | CL10A106MQ8NN      | 10               | 1608      | 6.3         |

|                                                | Murata  | GRM188Z71A106KA73D | 10               | 1608      | 10          |

Table 3. Recommended capacitor

### 4.2.4 VSYS, VINT, LDO1, LDO4, LDO5, SWIN and SWOUT capacitor selection

Internal power input, internal power supply output, LDOs, and load switch pins are all required to be bypassed by a low ESR 1  $\mu$ F ceramic capacitor. Table 4 shows the recommended capacitor.

| PIN                              | Vendor  | Part number        | Capacitance [µF] | Size [mm] | Voltage [V] |

|----------------------------------|---------|--------------------|------------------|-----------|-------------|

| VINT, VSYS, LDO1,<br>LDO4, LDO5, | Murata  | GRM188R60J106ME    | 1                | 1005      | 16          |

|                                  | Samsung | CL10A106MQ8NN      | 1                | 1005      | 16          |

| SWIN, SWOUT                      | Murata  | GRM155C71A105KE11D | 1                | 1005      | 10          |

Table 4. Recommended capacitor

# 5 Design guidelines

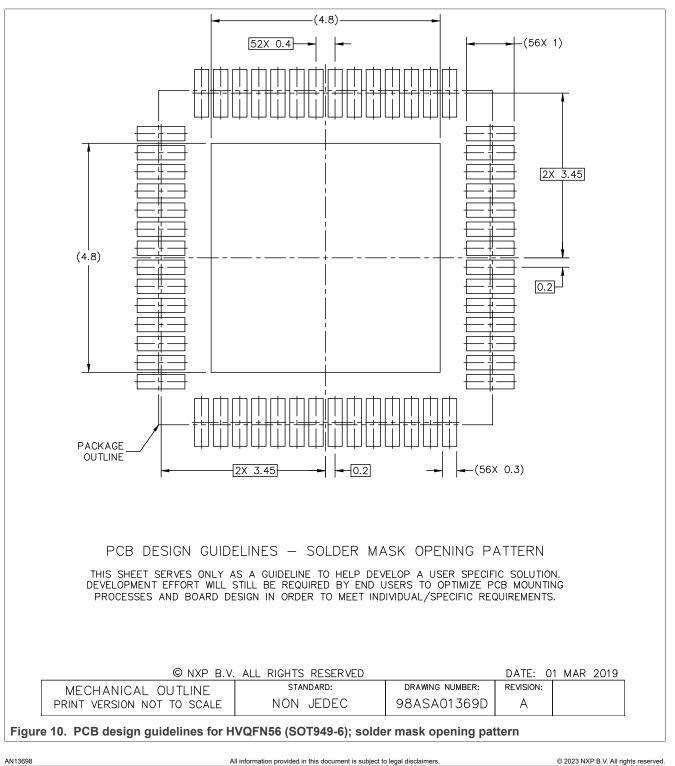

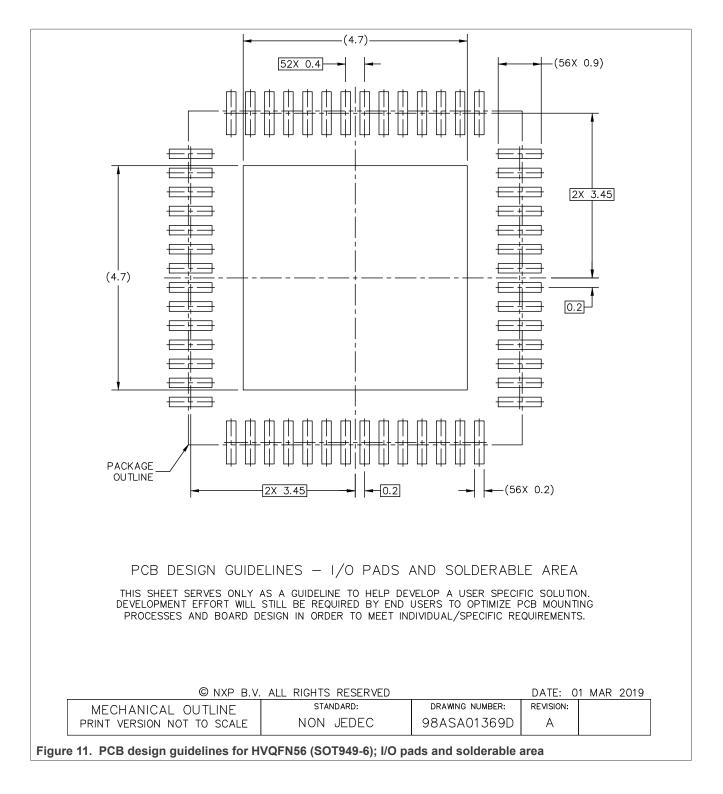

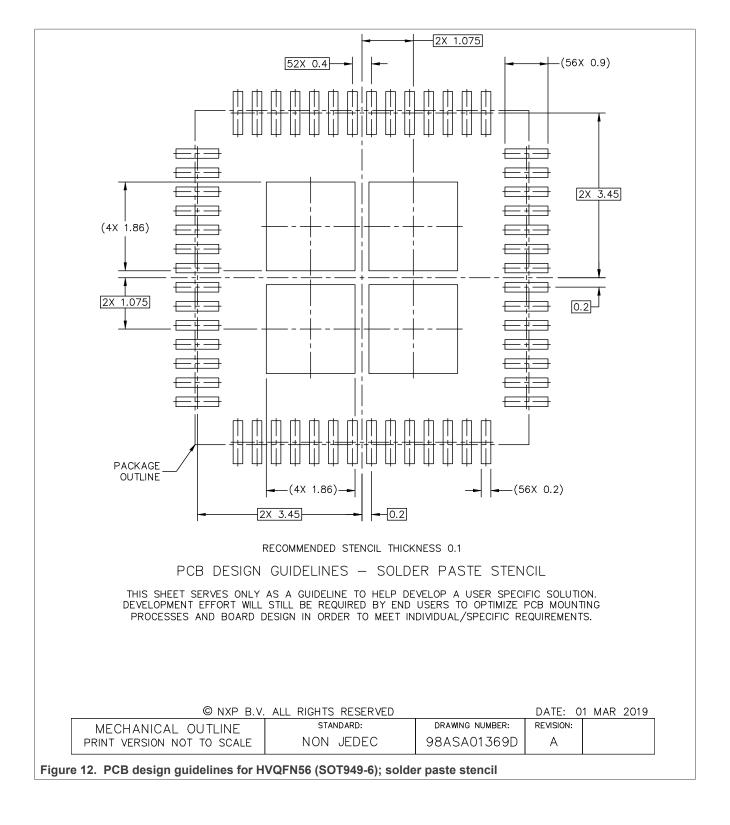

### 5.1 Package

The PCA9451A device is intended for use in commercial and industrial applications and is offered in a 56-pin HVQFN package, 7mm x 7mm, 0.4mm pitch. Refer to Application Note AN1902 (<u>https://www.nxp.com/docs/en/application-note/AN1902.pdf</u>) for guidelines on the handling and assembly of NXP QFN packages during PCB assembly, guidelines for PCB design and rework, and package performance information (such as Moisture Sensitivity Level (MSL) rating, board level reliability, mechanical, and thermal resistance data).

Package dimensions are provided in package drawings. To find the most current package outline drawing, refer to the package link: <u>SOT949-6 (nxp.com)</u>

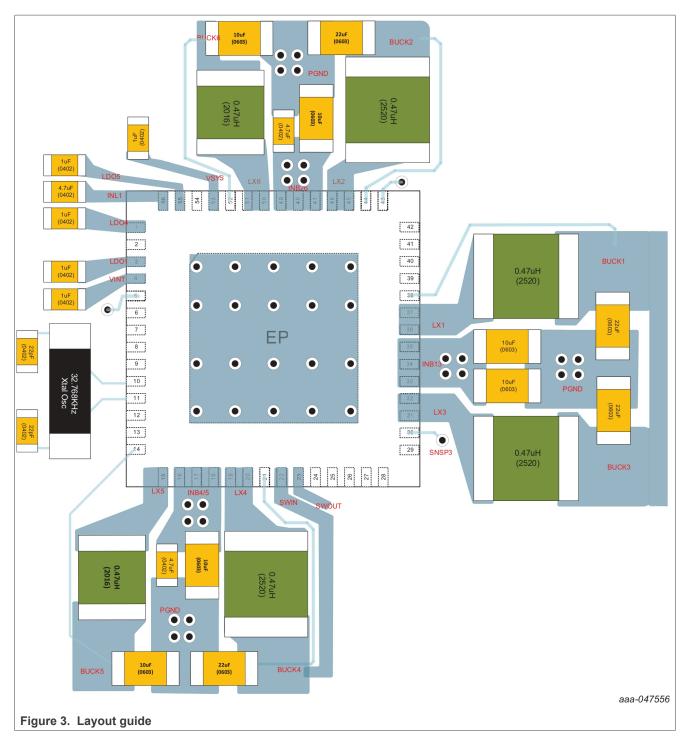

### 5.2 Placement

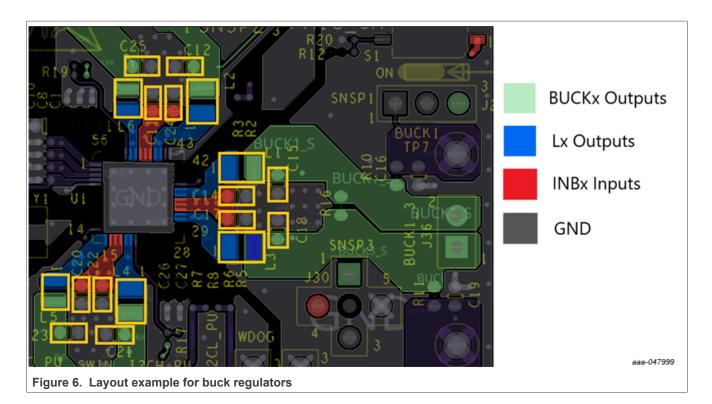

All components related to the power stage should be kept as close to the PMIC as possible, especially decoupling input and output capacitors.

Place these components in order of priority:

- · Input capacitor of the buck regulators

- LDO capacitors

- VSYS and VINT capacitors

- Buck regulator inductors

- Buck regulator output capacitors

Layout guide is shown in Figure 3.

### PCA9451A application note

### 5.3 Switching regulator schematic recommendations

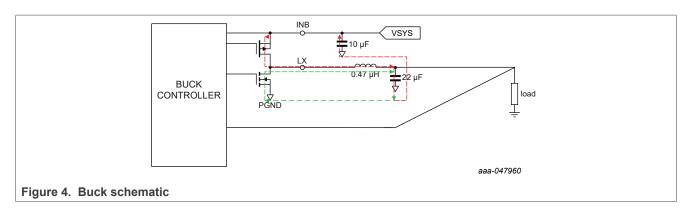

Figure 4 shows the critical path in buck converter which has high di/dt.

### PCA9451A application note

The biggest challenge in buck layout is EMI. To minimize the EMI requires the minimum loop area of two high di/dt paths as shown in Figure 4. The area in red is input power charging the inductor when high side FET is on; the area in green is inductor discharge energy to output capacitor (load) when low side FET is on.

### 5.4 Layout guidelines

### 5.4.1 General routing requirements

- 1. Some recommended things to keep in mind for manufacturability:

- Via in pads require a 4.5 mil minimum annular ring. Pad must be 9.0 mils larger than the hole

- Maximum copper thickness for lines less than 5.0 mils wide is 0.6 oz copper

- Minimum allowed spacing between line and hole pad is 3.5 mils

- · Minimum allowed spacing between line and line is 3.0 mils

- 2. Care must be taken with BUCKxFB pins traces. These signals are susceptible to noise and must be routed far away from power, clock, or high power signals, like the ones on the INBxx, and LXx pins. They could be also shielded.

- 3. Shield feedback traces of the regulators and keep them as short as possible (trace them on the bottom so the ground and power planes shield these traces).

- 4. Make sure all components related to a specific block are referenced to the corresponding ground.

- 5. Use the shortest path to route the trace including the return path (ground).

- 6. Make sure that the trace is capable of handling the maximum current in the application.

- 7. Keep enough vias to connect the ground pad to main ground; this not only reduces the parasitic inductance but also helps with heat dissipation.

### 5.4.2 Parallel routing requirements

- I<sup>2</sup>C signal routing

- 1. SCL is one of the fastest signals of the system, so it must be given special care.

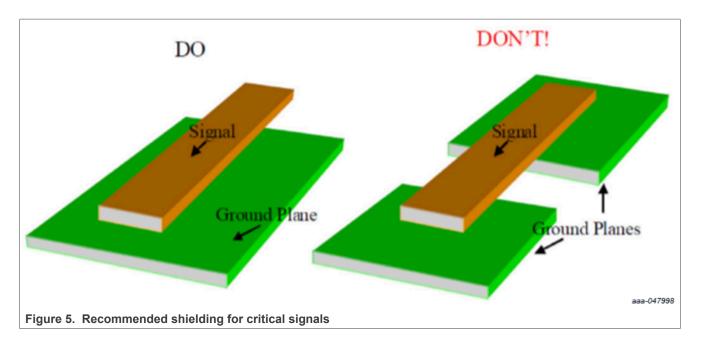

- To avoid contamination of these delicate signals by nearby high power or high frequency signals, it is a good practice to shield them with ground planes placed on adjacent layers. Make sure the ground plane is uniform throughout the whole signal trace length, as shown in <u>Figure 5</u>

- 3. These signals can be placed on an outer layer of the board to reduce their capacitance with respect to the ground plane.

- 4. Care must be taken with these signals not to contaminate analog signals, as they are high frequency signals. Another good practice is to trace them perpendicularly on different layers, so there is a minimum area of proximity between signals.

### PCA9451A application note

### 5.4.3 Switching regulator layout recommendations

- 1. Put the input/output capacitor and inductor as close to chip as possible to minimize the loop area. If using the high frequency bypass capacitor to filter the EMI, make sure this high frequency capacitor is close to the chip.

- 2. Make high-current ripple traces low-inductance (short, high W/L ratio).

- 3. Make high-current traces wide or copper islands.

- a. Maximum current on Lx pin to inductor is around 1.4 times maximum loading current by quick estimation.

PCA9451A application note

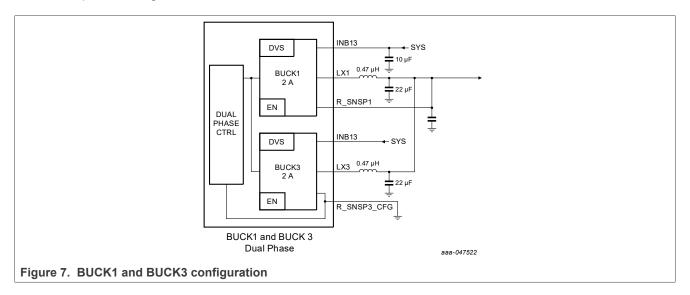

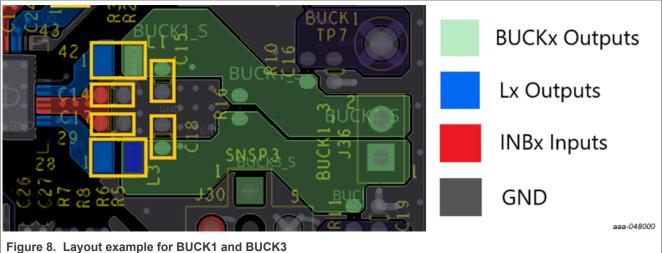

### 5.4.4 BUCK1/BUCK3 dual-phase buck

BUCK1 and BUCK3 are configured as dual phase buck. R\_SNSP3\_CFG pin should be connected to ground. This dual phase buck regulator is controlled through BUCK1 registers. All BUCK3 registers are not responsive under dual-phase configuration.

PCA9451A application note

#### 5.4.5 LDO

PCA9451A integrates three LDOs with different output current capability for different purposes. The output capacitor needs to be as close as possible to the chip. Make sure the trace is wide enough to carry the maximum current in the application.

#### Table 5. LDO summary

| LDO# | Default VOUT [V]         | VOUT range [V]        | Step size [mV] | Default<br>ON/OFF | Current rating [mA] |

|------|--------------------------|-----------------------|----------------|-------------------|---------------------|

| LDO1 | 1.8                      | 1.6 - 1.9 / 3.0 - 3.3 | 100            | ON                | 10                  |

| LDO4 | 0.8                      | 0.8 - 3.3             | 100            | ON                | 200                 |

| LDO5 | 3.3 / 1.8 <sup>[1]</sup> | 1.8 – 3.3             | 100            | ON                | 150                 |

[1] Voltage selection through SD\_VSEL pin

#### 5.4.6 Ground

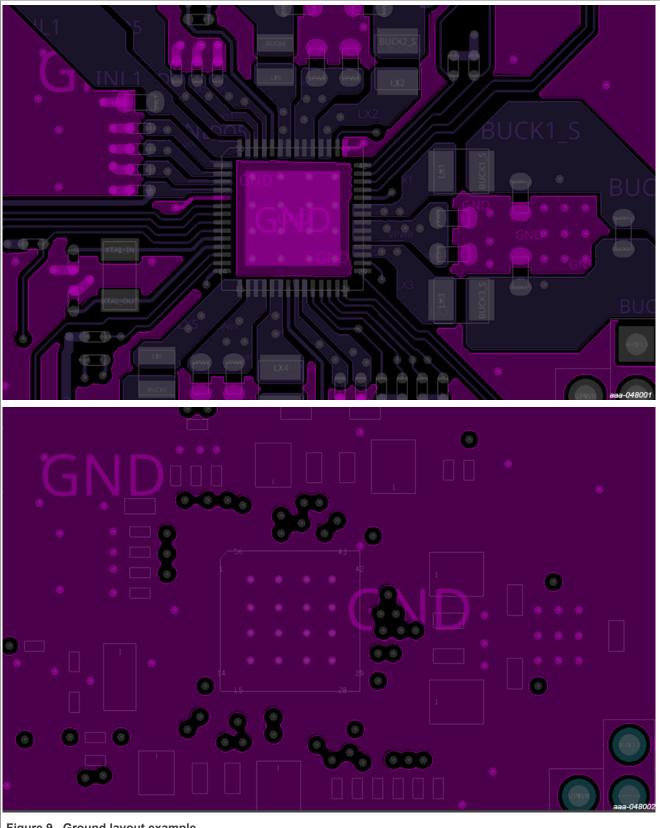

The exposed pad (EP) is the power ground of all bucks which is relatively noisy. AGND is the analog ground. Do not connect AGND to EP on the top layer. Connect AGND to main ground by via. Avoid separating the main ground under PCA9451A which may increase the return path. Make sure there are enough vias to connect EP to system main ground.

PCA9451A application note

Figure 9. Ground layout example

### 6 Thermal analysis

### 6.1 Rating data

Junction to Ambient Thermal Resistance Nomenclature: the JEDEC specification reserves the symbol R0JA or 0JA (Theta-JA) strictly for junction-to-ambient thermal resistance on a 1s test board in natural convection environment. R0JMA or 0JMA (ThetaJMA) is used for both junction-to-ambient on a 2s2p test board in natural convection and for junction-to-ambient with forced convection on both 1s and 2s2p test boards. It is anticipated that the generic name, Theta-JA, continues to be commonly used. The JEDEC standards can be consulted at <a href="http://www.jedec.org/">http://www.jedec.org/</a>.

### 6.2 Estimation of junction temperature

An estimation of the chip junction temperature TJ can be obtained from Equation 5:

| $TJ = TA + (R\Theta JA \times PD)$ | (5) |

|------------------------------------|-----|

|------------------------------------|-----|

Where:

- TA = Ambient temperature for the package in °C

- RθJA = Junction to ambient thermal resistance in °C/W

- PD = Power dissipation in the package in W

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board R0JA and the value obtained on a four layer board R0JMA. Actual application PCBs show a performance close to the simulated four layer board value although this may be somewhat degraded in case of significant power dissipated by other components placed close to the device.

## 7 PCB design guidelines

### 7.1 Package dimensions

Package dimensions are provided in package drawings. The latest package outline drawing can be found at the package link: <u>SOT949-6 (nxp.com)</u>

17 / 22

PCA9451A application note

### PCA9451A application note

AN13698 Application note

#### PCA9451A application note

# 8 Legal information

### 8.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 8.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

### 8.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

PCA9451A application note

### **Tables**

| Tab. 1. | Tested inductor list  | 7 |

|---------|-----------------------|---|

| Tab. 2. | Recommended capacitor | 8 |

| Tab. 3. | Recommended capacitor | 8 |

# Figures

| Fig. 1. | Block diagram4                               |

|---------|----------------------------------------------|

| Fig. 2. | PCA9451A + i.MX93x + LPDDR4X                 |

|         | application schematic6                       |

| Fig. 3. | Layout guide10                               |

| Fig. 4. | Buck schematic11                             |

| Fig. 5. | Recommended shielding for critical signals12 |

| Fig. 6. | Layout example for buck regulators           |

| Fig. 7. | BUCK1 and BUCK3 configuration13              |

| Tab. 4. | Recommended capacitor | 9  |

|---------|-----------------------|----|

| Tab. 5. | LDO summary           | 14 |

| Fig. 8.  | Layout example for BUCK1 and BUCK3 14       |

|----------|---------------------------------------------|

| Fig. 9.  | Ground layout example15                     |

| Fig. 10. | PCB design guidelines for HVQFN56           |

|          | (SOT949-6); solder mask opening pattern 17  |

| Fig. 11. | PCB design guidelines for HVQFN56           |

|          | (SOT949-6); I/O pads and solderable area 18 |

| Fig. 12. | PCB design guidelines for HVQFN56           |

|          | (SOT949-6); solder paste stencil19          |

### Contents

| 1     | Introduction                           | . 3 |

|-------|----------------------------------------|-----|

| 2     | Features and benefits                  | 3   |

| 3     | Block diagram                          | . 4 |

| 4     | Application design-in information      | 5   |

| 4.1   | Reference schematic                    | 5   |

| 4.2   | Typical application                    | . 7 |

| 4.2.1 | Inductor selection for buck converters | 7   |

| 4.2.2 | Output capacitor selection for buck    |     |

|       | converters                             | . 8 |

| 4.2.3 | Input capacitor selection for buck     |     |

|       | converters                             | . 8 |

| 4.2.4 | VSYS, VINT, LDO1, LDO4, LDO5, SWIN     |     |

|       | and SWOUT capacitor selection          |     |

| 5     | Design guidelines                      | . 9 |

| 5.1   | Package                                | 9   |

| 5.2   | Placement                              | 9   |

| 5.3   | Switching regulator schematic          |     |

|       | recommendations                        |     |

| 5.4   | Layout guidelines                      |     |

| 5.4.1 | General routing requirements           |     |

| 5.4.2 | Parallel routing requirements          | 11  |

| 5.4.3 | Switching regulator layout             |     |

|       | recommendations                        |     |

| 5.4.4 | BUCK1/BUCK3 dual-phase buck            |     |

| 5.4.5 | LDO                                    | 14  |

| 5.4.6 | Ground                                 |     |

| 6     | Thermal analysis                       | 16  |

| 6.1   | Rating data                            |     |

| 6.2   | Estimation of junction temperature     |     |

| 7     | PCB design guidelines                  | 17  |

| 7.1   | Package dimensions                     | 17  |

| 8     | Legal information                      | 20  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 26 May 2023 Document identifier: AN13698