# **Freescale Semiconductor**

**Application Note**

Document Number: AN2661 Rev. 1, 01/2007

# Software Migration from the IBM (AMCC) 440GP to the MPC8540

Paul Wilson hv NCSD Applications Freescale Semiconductor, Inc. Austin. TX

As embedded systems become more complex, software complexity is the deciding factor when a new system is designed and built. The cost of porting code can sometimes offset the benefits that come with the additional features of a new processor platform. Fortunately, software migration can be easy, especially when staying within a processor core architecture.

This document details device driver and lower-level software migration from the IBM 440GP Embedded PowerPC<sup>TM</sup> processor by Applied Micro Circuits Corporation (AMCC) to the Freescale PowerQUICC<sup>™</sup> III product family. Both processors are PowerPC based, so software migration has few caveats, leaving architects with decisions based more on hardware functionality and processor feature sets.

### Feature Comparison 1

The IBM 440GP embedded PowerPC processor includes a PowerPC core (based on a 32-bit implementation of the Book E architecture) as well as the following integrated peripherals:

- DDR SDRAM memory controller

- Fast Ethernet controllers

### © Freescale Semiconductor, Inc., 2004, 2007. All rights reserved.

#### Contents

| 1  | Feature Comparison1         |

|----|-----------------------------|

| 2  | Software Migration Overview |

| 3  | DDR SDRAM 3                 |

| 4  | Interrupt Controller        |

| 5  | General-Purpose Timers13    |

| 6  | DMA Transfers 14            |

| 7  | Buffer Descriptors 19       |

| 8  | Ethernet                    |

| 9  | UART                        |

| 10 | I2C                         |

| 11 | PCI-X                       |

| 12 | Conclusions                 |

| 13 | Document Revision History   |

#### Feature Comparison

- 32-/64-bit PCI-X bus

- UART

- I<sup>2</sup>C

- DMA capability

- Peripheral bus

The Freescale PowerQUICC III architecture is based on the latest embedded PowerPC architecture Book E definition and uses a new high performance e500 core with 256-Kbytes of Level 2 cache. PowerQUICC III also offers two integrated 10/100/1000 three-speed Ethernet controllers (TSEC), a DDR SDRAM memory controller, a 64-bit PCI-X/PCI controller, and a RapidIO interconnect.

The MPC8540 and MPC8560 are examples of PowerQUICC integrated communication processors:

- MPC8540 integrated host processor Ethernet only options (two 10/100/1000 Mbps interfaces and one 10/100 Mbps interface) with dual UART interfaces to provide the highest level of performance and integration at lower system cost.

- MPC8560 integrated communication processor. This device differs from the MPC8540 in that it

includes a dedicated RISC communications controller (referred to as the CPM) for handling

communication protocols. The MPC8560 CPM supports three fast serial communications channels

(FCCs) for 155 Mbps ATM, 10/100 Mps Ethernet, and HDLC up to DS3 rates. Support for

256 full-duplex, time-division-multiplexed (TDM) channels using 2 multi-channel controllers

(MCCs) is provided. In addition, the MPC8560 CPM supports four serial communications

controllers (SCCs), one serial peripheral interface (SPI), and one I<sup>2</sup>C interface.

This application note discusses software migration from the IBM 440GP embedded PowerPC processor to the Freescale MPC8540 PowerQUICC III processor. Table 1 compares these devices, highlighting features common to both processors. The features of the IBM 440GP are a subset of the features on the MPC8540, enabling an easy hardware migration to the PowerQUICC III family. Also, the features common to both processors are similar from a software point of view, enabling reasonably easy migration from the IBM 440GP to the MPC8540 from both a hardware and software prospective.

| Feature                             | IBM 440GP                                 | MPC8540                                                       |

|-------------------------------------|-------------------------------------------|---------------------------------------------------------------|

| Core frequency                      | 400 to 500 MHz                            | 667 to 833 MHz                                                |

| Core architecture                   | 32-bit Book E PowerPC                     | 32-bit Book E PowerPC                                         |

| L1 cache (I/D)                      | 32-/32-Kbytes                             | 32-/32-Kbytes                                                 |

| SRAM/L2 cache                       | 8-Kbytes SRAM/No L2                       | 256-Kbytes L2 or<br>256-Kbytes SRAM or<br>128-/128-Kbytes mix |

| DDR controller                      | 32-/64-bit, DDR<br>266 MHz up to 2 Gbytes | 32-/64-bit, DDR<br>333 MHz up to 4 Gbytes                     |

| User programmable memory controller | No                                        | 3                                                             |

| Interrupt controller                | 13 external/45 internal                   | 12 external/22 internal                                       |

| DMA channels                        | 4                                         | 4                                                             |

Table 1. Feature Comparison of IBM 440GP versus MPC8540

Software Migration Overview

| Feature            | IBM 440GP                           | MPC8540                             |

|--------------------|-------------------------------------|-------------------------------------|

| RapidIO            | No                                  | 8-bit parallel RapidIO              |

| PCI-X (32-/64-bit) | PCI v2.2 33/66 MHz<br>PCI-X 133 MHz | PCI v2.2 33/66 MHz<br>PCI-X 133 MHz |

| Ethernet           | 10/100 (×2)                         | 10/100 and<br>10/100/1 Gbit (×2)    |

| UART               | 2                                   | 2                                   |

| l <sup>2</sup> C   | 2                                   | 1                                   |

| Technology         | 0.25 μm                             | 0.13 μm                             |

| Power              | <4 W @ 400 MHz                      | ~7 W @ 833 MHz                      |

Table 1. Feature Comparison of IBM 440GP versus MPC8540 (continued)

# 2 Software Migration Overview

High-level software such as a real-time operating system (RTOS) and any high-level applications running on top of the RTOS (for example, a web server) should not be affected by processor selection. An RTOS typically uses a board support package (BSP) to communicate with the underlying hardware, and this BSP is subject to change with new hardware. Changes to a BSP are outside of the scope of this document because these changes are not only RTOS dependent, but hardware dependent.

During a migration to a new hardware platform, device drivers are the most affected software element. A device driver communicates with anything external to the processor through mechanisms internal to the processor. This includes, but is not limited to: interrupt handling, Ethernet physical layer devices (PHYs) through an internal MAC, memory devices through the DDR-SDRAM memory controller, RS-232 transceivers through the UART interface, and the internal I<sup>2</sup>C controller. In porting code from the IBM 440GP to the MPC8540, differences in features common to both processors are discussed:

- DDR SDRAM controller

- Interrupt controller

- General purpose timers

- DMA transfers

- Ethernet

- UART

- I<sup>2</sup>C

- PCI-X

The byte ordering for IBM 440GP and MPC8540 is big-endian, enabling an easy software migration.

# 3 DDR SDRAM

The similarities between the integrated DDR-SDRAM controllers of the MPC8540 and the IBM 440GP are as follows:

#### DDR SDRAM

- The IBM 440GP has a programmable DDR SDRAM controller that supports x8 DDR SDRAMs and can provide a 32- or 64-bit interface to SDRAM memory with optional error checking and correction (ECC). The controller supports page mode operation with bank interleaving always active and can maintain up to eight open pages. The controller supports up to four 512-Mbytes logical banks in limited configurations, providing memory up to 2 Gbytes. Global memory timings, address and bank sizes, and memory addressing modes are programmable. System power can be reduced by placing the DDR SDRAM controller in sleep and/or self-refresh mode.

- PowerQUICC III has a fully programmable DDR SDRAM controller which supports JEDEC complaint DDR-I SDRAM standard x8 or x16 memories up to 166 MHz (333-MHz data rate) with optional ECC. PowerQUICC III supports page mode operation to retain the currently active SDRAM page for pipelined burst accesses for up to 16 simultaneously open pages (4 for each memory bank). Fourteen multiplexed address signals and 2 logical bank signals provide support for device densities of 64 Mbits to 1 Gbits. Four chip select signals are provided to support up to 4 physical banks of memory each from 64 Mbytes to 1 Gbytes in size or up to 2 DIMM modules. As these 4 banks provide a theoretical maximum of 4-Gbytes of DDR main memory, the 4 Gbytes could span the entire 32-bit address space. However, since space must be reserved for boot ROM, configuration registers and other important addressable locations, the maximum DDR memory is limited to 3.5 Gbytes.

However, there are differences in the way the DDR-SDRAM controllers of the MPC8540 and the IBM 440GP are configured, as explained in the following sections.

## 3.1 IBM 440GP DDR-SDRAM Controller

The IBM 440GP uses 23 indirectly accessed registers to configure the SDRAM controller. These registers are accessed through the SDRAM0\_CFGADDR and SDRAM0\_CFGDATA registers. At system reset of the processor, software must configure and then enable the DDR SDRAM controller. The registers to configure the IBM 440GP DDR SDRAM controller are shown in the following tables. Table 2 shows the SDRAM0\_CFG0 register, which enables specific features of the DDR SDRAM controller.

| Bits <sup>1</sup> | Name | Description                           |

|-------------------|------|---------------------------------------|

| 0                 | DCEN | DDR SDRAM controller enabled/disabled |

| 2–3               | MCHK | ECC enabled/disabled                  |

| 4                 | RDEN | Registered DIMM enabled/disabled      |

| 5                 | PMU  | Page management unit enabled/disabled |

| 6                 | DMWD | DDR SDRAM width 32- or 64-bit         |

| 8–9               | UIOS | Unused I/O state                      |

| 10                | PDP  | Page deallocation policy              |

Undocumented bits are reserved.

1

Table 3 shows the SDRAM0\_CFG1 register, which enables the DDR SDRAM controller power management and self-refresh features.

### Table 3. IBM 440GP SDRAM0\_CFG1

| Bits <sup>1</sup> | Name | Description                       |

|-------------------|------|-----------------------------------|

| 0                 | SRE  | Self-refresh entry                |

| 1                 | PMEN | Power management enabled/disabled |

<sup>1</sup> Undocumented bits are reserved.

Table 4 shows the SDRAM0\_DEVOPT register, which allows configuration of the defined DDR SDRAM device-specific options.

| Bits <sup>1</sup> | Name | Description                           |

|-------------------|------|---------------------------------------|

| 0                 | DLL  | DDR SDRAM device DLL enabled/disabled |

| 1                 | DS   | DDR SDRAM device I/O drive strength   |

### Table 4. IBM 440GP SDRAM0\_DEVOPT

<sup>1</sup> Undocumented bits are reserved.

The IBM 440GP DDR SRAM controller supports four logical banks. Table 5 shows the SDRAM0\_BnCR registers to configure and enable memory in each logical bank.

### Table 5. IBM 440GP SDRAM0\_BnCR

| Bits <sup>1</sup> | Name | Description                                |

|-------------------|------|--------------------------------------------|

| 0–8               | SDBA | Base address                               |

| 12–14             | SDSZ | DDR-SDRAM size                             |

| 16–18             | SDAM | DDR SDRAM address mode/memory organization |

| 31                | SDBE | Memory bank enabled                        |

<sup>1</sup> Undocumented bits are reserved.

Table 6 shows the SDRAM0\_TR0 register, which is used to configure DDR-SDRAM device-specific timing parameters.

### Table 6. IBM 440GP SDRAM0\_TR0

| Bits <sup>1</sup> | Name | Description                                                         |

|-------------------|------|---------------------------------------------------------------------|

| 0                 | SDWR | DDR SDRAM write recovery                                            |

| 1                 | SDWD | DDR SDRAM write-to-write delay                                      |

| 7–8               | SDCL | DDR SDRAM CAS latency                                               |

| 12–13             | SDPA | DDR SDRAM CBR precharge command to next activate<br>command minimum |

| 14–15             | SDCP | DDR SDRAM read/write precharge command to command                   |

| 16–17             | SDLD | DDR SDRAM command to leadoff                                        |

| Bits <sup>1</sup> | Name | Description                                    |

|-------------------|------|------------------------------------------------|

| 27–29             | SDRA | DDR SDRAM CBR refresh command to next activate |

| 30–31             | SDRD | DDR SDRAM RAS to CAS delay                     |

Table 6. IBM 440GP SDRAM0\_TR0 (continued)

<sup>1</sup> Undocumented bits are reserved.

The SDRAM0\_TR1 register is used to control various aspects of the DDR SDRAM read data path.

#### 3.2 MPC8540 DDR-SDRAM Controller

The MPC8540 DDR-SDRAM controller registers are directly accessed by the CPU and are shown in the following tables. Table 7 shows the chip select memory bound registers (CSn BNDS), which define the address range for memory banks controlled by that chip select.

| Table 7 | MPC8540 | CSn_BNDS |

|---------|---------|----------|

|---------|---------|----------|

| Bits <sup>1</sup> | Name        | Description                               |

|-------------------|-------------|-------------------------------------------|

| 0–7               | SAn         | Starting address for chip select (bank) n |

| 16–23             | EA <i>n</i> | End address for chip select (bank) n      |

| 1                 |             |                                           |

<sup>1</sup> Undocumented bits are reserved.

Table 8 shows the chip select configuration registers (CSn\_CONFIG), which define the memory organization (number of row/columns).

| Bits <sup>1</sup>              | Name             | Description                                          |  |

|--------------------------------|------------------|------------------------------------------------------|--|

| 0                              | CS_ <i>n</i> _EN | Chip select <i>n</i> enable                          |  |

| 8                              | AP_ <i>n</i> _EN | Chip select <i>n</i> auto precharge enable           |  |

| 21–23                          | ROW              | No. of row bits for SDRAM on chip select n           |  |

| 29–31                          | COL              | No. of column bits for SDRAM on chip select <i>n</i> |  |

| Undocumented bits are reserved |                  |                                                      |  |

Table 8. MPC8540 CSn\_CONFIG

Undocumented bits are reserved.

Table 9 shows the DDR SDRAM timing configuration register (TIMING\_CFG1), which defines timing intervals between various SDRAM control commands.

Table 9. MPC8540 TIMING CFG1

| Bits <sup>1</sup> | Name     | Description                                           |

|-------------------|----------|-------------------------------------------------------|

| 1–3               | PRETOACT | Precharge to activate interval (t <sub>rp</sub> )     |

| 5–7               | ACTTOPRE | Activate to precharge interval (t <sub>ras</sub> )    |

| 9–11              | ACTTORW  | Activate to read/write interval for SDRAM $(t_{rcd})$ |

| 13–15             | CASLAT   | CAS latency from read command                         |

| Bits <sup>1</sup> | Name     | Description                                                     |

|-------------------|----------|-----------------------------------------------------------------|

| 16–19             | REFREC   | Refresh recovery time (t <sub>rfc</sub> )                       |

| 22–23             | WRREC    | Last data to precharge interval $(t_{wr})$                      |

| 25–27             | ACTTOACT | Activate to activate interval (t <sub>rrd</sub> )               |

| 30–31             | WRTORD   | Last write data pair to read command issue internal $(t_{wtr})$ |

### Table 9. MPC8540 TIMING\_CFG1 (continued)

<sup>1</sup> Undocumented bits are reserved.

Table 10 shows the DDR SDRAM configuration register (DDR\_SDRAM\_CFG), which enables/disables features of the memory controller including: self-refresh, ECC, and dynamic power management.

| Table 10 | . MPC8540 DDR | _SDRAM_CFG |

|----------|---------------|------------|

|----------|---------------|------------|

| Bits <sup>1</sup> | Name       | Description                               |  |

|-------------------|------------|-------------------------------------------|--|

| 0                 | MEM_EN     | DDR SDRAM controller enabled/disabled     |  |

| 1                 | SREN       | Self-refresh enable                       |  |

| 2                 | ECC_EN     | ECC enable                                |  |

| 3                 | RDEN       | Registered DIMM enabled/disabled          |  |

| 6–7               | SDRAM_TYPE | Type of SDRAM device used                 |  |

| 10                | DYN_PWR    | Dynamic power management enabled/disabled |  |

|                   |            |                                           |  |

<sup>1</sup> Undocumented bits are reserved.

Table 11 shows the DDR SDRAM mode configuration (DDR\_SDRAM\_Mode), which defines the mode registers of the SDRAM device.

Table 11. MPC8540 DDR\_SDRAM\_MODE

| Bits  | Name    | Description         |

|-------|---------|---------------------|

| 0–15  | ESDMODE | Extended SDRAM mode |

| 16–31 | SDMODE  | SDRAM mode          |

Table 12 shows the DDR SDRAM interval configuration (DDR\_SDRAM\_INTERVAL), which configures the precharge and refresh intervals.

| Bits <sup>1</sup> | Name    | Description        |

|-------------------|---------|--------------------|

| 6–7               | REFINT  | Refresh interval   |

| 18–31             | BSTOPRE | Precharge interval |

<sup>1</sup> Undocumented bits are reserved.

Interrupt Controller

# 3.3 Porting DDR SDRAM to the MPC8540

There are similarities between the DDR SDRAM controller in the IBM 440GP and MPC8540, although the exact register formats are different. The MPC8540 DDR-SDRAM controller registers are directly accessed by the CPU, but the IBM 440GP DDR SDRAM controller registers are indirectly accessed by the CPU. Key features of the DDR SDRAM controller and how registers from the IBM 440GP map to the MPC8540 are shown in Table 13.

| Feature                                           | IBM 440GP Register <sup>1</sup> | MPC8540 Register           |

|---------------------------------------------------|---------------------------------|----------------------------|

| Refresh enable/timer                              | SDRAM0_CFG1[SRE]                | DDR_SDRAM_CFG[SREN]        |

|                                                   |                                 | DDR_SDRAM_INTERVAL[REFINT] |

| CAS latency (t <sub>aa</sub> )                    | SDRAM0_TR0[SDCL]                | TIMING_CFG_1[CASLAT]       |

| Precharge to activate timing (t <sub>rp</sub> )   | SDRAM0_TR0[SDPA]                | TIMING_CFG_1[PRETOACT]     |

| Activate to precharge (t <sub>ras</sub> )         | SDRAM0_TR0[SDCP]                | TIMING_CFG_1[ACTTOPRE]     |

| Refresh recovery timing (t <sub>rfc</sub> )       | SDRAM0_TR0[SDRA]                | TIMING_CFG_1[REFREC]       |

| Activate to read/write timing (t <sub>rcd</sub> ) | SDRAM0_TR0[SDCP]                | TIMING_CFG_1[ACTTORW]      |

| Write recovery (t <sub>wr</sub> )                 | SDRAM0_TR0[SDWR]                | TIMING_CFG_1[WRREC]        |

| Power management enable                           | SDRAM0_CFG1[PMEN]               | DDR_SDRAM_CFG[DYN_PWR]     |

| DDR SDRAM DLL disabled                            | SDRAM0_DEVOPT[DLL]              | LCRR[DBYP]                 |

| DDR SDRAM base address                            | SDRAM0_BnCR[SDBA]               | CSn_BNDs[SA <i>n</i> ]     |

| DDR SDRAM size                                    | SDRAM0_BnCR[SDSZ]               | CSn_BNDs[SAn] and [EAn]    |

| Memory organization                               | SDRAM0_BnCR[SDBA]               | CSn_CONFIG[ROW_BIT_CS_n]   |

|                                                   |                                 | CSn_CONFIG[COL_BIT_CS_n]   |

| Memory bank enabled                               | SDRAM0_BnCR[SDBE]               | CSn_CONFIG[CS_n_EN]        |

<sup>1</sup> n = 0 to 3.

The IBM 440GP uses predefined modes (SDRAM0\_BnCR[SDRAM]) for each logical bank, which defines the supported DDR-SDRAM configuration. In combination with the size (SDRAM0\_BnCR[SDSZ]) of the memory, this mode initializes the DDR-SDRAM memory controller address muliplexing and A10 (precharge pin) settings.

The MPC8540 uses the  $CSn_CONFIG$  registers for each logical bank to define the DDR-SDRAM configuration in terms of number of row and columns. These settings combined with the size ( $CSn_BNDs$ ) of the memory initialize the DDR-SDRAM memory controller address muliplexing and A10 (precharge pin) settings.

# 4 Interrupt Controller

Although there are many similarities between the interrupt controllers of the IBM 440GP and the MPC8540, they are configured somewhat differently, as explained in this section.

## 4.1 IBM 440GP Interrupt Controller

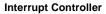

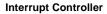

The IBM 440GP contains two universal interrupt controllers (UIC0 and UIC1) that provide all necessary control, status, and communication between 45 internal interrupts, 13 external interrupts, and the processor core. The UICs are cascaded as shown in Figure 1.

UIC0 collects interrupts from internal and external sources, including the critical and non-critical interrupt outputs of the secondary interrupt controller, UIC1. Table 14 shows the registers used to configure the IBM 440GP universal interrupt controller.

| Offset | Name     | Description                         |

|--------|----------|-------------------------------------|

| 0x0C0  | UIC0_SR  | UIC status register 0               |

| 0x0D0  | UIC1_SR  | UIC status register 1               |

| 0x0C2  | UIC0_ER  | UIC enable register 0               |

| 0x0D2  | UIC1_ER  | UIC enable register 1               |

| 0x0C3  | UIC0_CR  | UIC critical register 0             |

| 0x0D3  | UIC1_CR  | UIC critical register 1             |

| 0x0C4  | UIC0_PR  | UIC polarity register 0             |

| 0x0D4  | UIC1_PR  | UIC polarity register 1             |

| 0x0C5  | UIC0_TR  | UIC trigger register 0              |

| 0x0D5  | UIC1_TR  | UIC trigger register 1              |

| 0x0C6  | UIC0_MSR | UIC masked status register 0        |

| 0x0D6  | UIC1_MSR | UIC masked status register 1        |

| 0x0C7  | UIC0_VCR | UIC vector configuration register 0 |

| 0x0D7  | UIC1_VCR | UIC vector configuration register 1 |

| 0x0C8  | UIC0_VR  | UIC vector register 0               |

| 0x0D8  | UIC1_VR  | UIC vector register 1               |

### Table 14. IBM 440GP Interrupt Controller Registers

### Interrupt Controller

The UIC status registers (UIC0\_SR and UIC1\_SR) capture and hold internal and external interrupts until software resets them by writing to the interrupt (bit) location in these registers. The fields of the UIC enable registers (UIC0\_E and UIC1\_ER) match the UIC status registers and enable or disable interrupt reporting in the UIC status registers. Similarly, the fields of the UIC critical registers (UIC0\_CR and UIC1\_CR) determine whether an interrupt captured in the UIC status registers generates a non-critical or critical interrupt.

The fields of the UIC priority registers (UIC0\_PR and UIC1\_PR) determine whether an interrupt captured in the UIC status registers has a positive or negative priority. The fields of the UIC trigger registers (UIC0\_TR and UIC1\_TR) determine whether an interrupt captured in the UIC status registers are edge-sensitive or level-sensitive.

The UIC masked status registers (UIC0\_MSR and UIC1\_MSR) are read-only registers which contain the result of the masking of the UIC status registers (UIC0\_SR and UIC1\_SR) and the UIC enable registers (UIC0\_E and UIC1\_ER). This allows software to check which enabled interrupts are active.

The UIC vector configuration registers (UIC0\_VCR and UIC1\_VCR) are write-only registers which enable software control of interrupt vector generation for critical interrupts only. These registers contain an address, used as an interrupt vector base address (VBA), and a field specifying the interrupt ordering priority (PRO). The VBA field contains either the base address for an interrupt handler vector table or the base address for the interrupt handler associated with each interrupt. The actual interrupt vector (the address of the interrupt handler that services the interrupt) is generated in the UIC vector registers (UIC0\_VR and UIC1\_VR) using VBA. The PRO field controls whether the interrupt associated with  $UICn_SR[0]$  or  $UICn_SR[31]$  has the highest priority. If  $UICn_VCR[PRO] = 0$ , the interrupt associated with  $UICn_SR[0]$  has the highest priority; if  $UICn_VCR[PRO] = 1$ , the interrupt associated with  $UICn_CR$  as a interrupt has the second highest priority. Priority decreases across the  $UICn_SR$  to the end opposite the highest priority field.

### 4.2 MPC8540 Interrupt Controller

The MPC8540 programmable interrupt controller (PIC) is compliant with the OpenPIC architecture and supports 12 external and 22 internal interrupt sources, 4 inter-processor interrupts, 4 global timers, and 4 message registers. The PIC can be reset through the global configuration register (GCR). In addition, this register can be used to program the PIC to operate in one of two modes:

- Pass through mode. One external active high interrupt request on  $\overline{IRQ0}$  is directly passed to the e500 core. All other external requests are ignored and all internal interrupts are passed to the  $\overline{IRQ_OUT}$  signal.

- Mixed mode. External and internal interrupts are delivered according to the programmed options (IRQ\_OUT or e500 in the interrupt destination registers).

Each interrupt source (except for inter-processor interrupts) has an interrupt destination register, which determines the destination of that interrupt:

- For external sources—EIDR0–EIDR11

- For internal sources—IIDR0–IIDR31

- For messaging sources—MIDR0–MIDR3

• For timer sources—GTDR0–GTDR3

There are three interrupt destinations on a per interrupt basis:

- Core\_int (e500 interrupt)

- Core\_cint (e500 critical interrupt)

- **IRQ\_OUT** (external pin)

Each interrupt source has an interrupt vector/priority register to configure its priority (there are 16 programmable interrupt priority levels per interrupt), vector, masking, and polarity/sensing (for external interrupt sources only).

- For external sources—EIVPR0–EIVPR11

- For internal sources—IIVPR0–IIVPR31

- For messaging sources—MIVPR0–MIVPR3

- For timer sources—GTVPR0–GTVPR3

- For inter-processor sources—IPIVR0–IPIVR3

There are two critical interrupt summary registers (CISR0 and CISR1), which determine if an active interrupt is directed to the processor critical interrupt signal, Core\_cint.

Software uses one processor current task priority register (CTPR) to set the current task priority executed by the core. The current priority of an interrupt should be higher than the value in the CTPR for it to be serviced. In response to an interrupt, software should read the processor interrupts acknowledge register (IACK) to obtain the vector of the interrupt being serviced. Reading IACK also has the following side effects:

- Associated field in the interrupt pending register is cleared for edge-sensitive interrupts.

- In-service register (ISR) is updated.

- Interrupt signal (int or cint) to the processor is negated.

Writing to the end of interrupt (EOI) register signals the end of processing for the highest-priority interrupt currently in service by the processor. The write to the EOI updates the ISR by retiring the highest-priority interrupt.

For nested interrupts, if the processor is servicing an interrupt, it can only be interrupted if the PIC receives an interrupt request from a source with higher priority than the one being serviced. This is true even if software, as part of its interrupt service routine, writes a new and lower value into the CTPR. Thus, although several interrupts may be in-service simultaneously, the code currently executing always handles the highest-priority interrupts that are in service. When the processor performs an EOI cycle, this highest-priority interrupt is taken out-of-service. The next EOI cycle takes the next-highest priority interrupt out-of-service, and so on. An interrupt with lower priority than those currently in-service is not started until all higher priority interrupts complete even if its priority is greater than the CTPR value.

In addition, on the MPC8560 device, there is a separate CPM interrupt controller to manage, prioritize, and route interrupts from CPM serial peripheral and parallel IO ports to the PIC.

Interrupt Controller

## 4.3 **Porting Interrupts to the MPC8540**

There are similarities between the interrupt controller in the IBM 440GP and the MPC8540, although the exact register formats are different. Table 15 lists key features of the interrupt controller and how registers from the IBM 440GP map to the MPC8540.

| Feature                     | IBM 440GP Register                   | MPC8540 Register                                                                                                                                          |

|-----------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enabling/masking interrupts | UIC0_ER-UIC1_ER<br>UIC0_MSR-UIC1_MSR | Mask field of the following<br>registers:<br>• EIVPR0–EIVPR11<br>• IIVPR0–IIVPR31<br>• IVPR0–MIVPR3<br>• GTVPR0–GTVPR3<br>• IPIVR0–IPIVR3                 |

| Interrupt status            | UIC0_SR-UIC1_SR                      | Activity field of the following<br>registers:<br>• EIVPR0–EIVPR11<br>• IIVPR0–IIVPR31<br>• IVPR0–MIVPR3<br>• GTVPR0–GTVPR3<br>• IPIVR0–IPIVR3             |

| Critical interrupts         | UIC0_CR-UIC1_CR                      | CISR0 and CISR1                                                                                                                                           |

| Interrupt polarity          | UIC0_PR-UIC1_PR                      | Polarity field of the following<br>registers:<br>• EIVPR0–EIVPR11<br>• IIVPR0–IIVPR31<br>• IVPR0–MIVPR3<br>• GTVPR0–GTVPR3<br>• IPIVR0–IPIVR3             |

| Edge or level sensitive     | UIC0_TR-UIC1_TR                      | Sense field of the following<br>registers for external interrupt<br>sources only:<br>• EIVPR0–EIVPR11                                                     |

| Vector/prioritization       | UIC0_VR-UIC1_VR<br>UIC0_VCR-UIC1_VCR | Priority and vector fields of the<br>following registers:<br>• EIVPR0–EIVPR11<br>• IIVPR0–IIVPR31<br>• IVPR0–MIVPR3<br>• GTVPR0–GTVPR3<br>• IPIVR0–IPIVR3 |

Table 15. Mapping Features of the IBM 440GP Interrupt Controller to PowerQUICC III

The IBM 440GP defines separate registers for different features of the interrupt controller. The MPC8540 defines registers for each interrupt source, which determines polarity, vector/prioritization, sensing, interrupt status, and if the interrupt source is enabled. The IBM 440GP, for critical interrupts, only has fixed priority levels defined by the priority field in the UIC vector configuration registers. The MPC8540 has a more flexible interrupt controller that defines an interrupt vector/priority register for each interrupt source. This controller can be used to configure up to 16 levels of priority.

# 5 General-Purpose Timers

Timer facilities (including time base, decrementer, fixed internal timer (FIT), and watchdog) between the IBM 440GP and MPC8540 CPU Book E implementation are identical and are not discussed in this section. However, the configuration of the general-purpose timers differs.

## 5.1 IBM 440GP General Purpose Timers

The IBM 440GP supports a general-purpose timer (GPT) with five maskable compare registers and a 32-bit time base counter. Each compare register has a corresponding GPT interrupt to the universal interrupt controller (UIC). GPT interrupts can be generated for a specific count by a match between the contents of a compare register and the time base counter. GPT interrupts can also be generated on a specific interval by masking individual bits of a compare register.

## 5.2 MPC8540 General Purpose Timers

The MPC8540 supports four global general purpose timers that are programmed in the programmable interrupt controller. There are appropriate clock prescalers and synchronizers to provide a time base for the four internal timers of the PIC unit. The timers can be individually programmed to generate a processor interrupt when they count down to zero and can be used to generate regular periodic interrupts. Each timer has four configuration and control registers:

- Global timer current count register (GTCCR*n*)

- Global timer base count register (GTBCR*n*)

- Global timer vector-priority register (GTVPRn)

- Global timer destination register (GTDR*n*)

The timer frequency for all four timers is determined by the timer frequency reporting register (TFRR), timer interrupts are all edge-triggered interrupts. If a timer period expires while a previous interrupt from the same source is pending or in-service, the subsequent interrupt is lost. Using the timer control register (TCR), you can create timers larger than the 31-bit global timers. Two 16-bit timers can be internally cascaded to form a 32-bit counter. Timer 1 can be internally cascaded to timer 2, and timer 3 can be internally cascaded to timer 4. The timer global configuration registers (TGCRs) are used to put the timers into cascaded mode. You can change the timer frequency by setting the appropriate fields of the TCR.

# 5.3 Porting General-Purpose Timers to the MPC8540

There are similarities in the general-purpose timers of the IBM 440GP and the MPC8540, although the exact register formats are different. Table 16 illustrates how general-purpose timer registers from the IBM 440GP map to the MPC8540.

| Feature           | IBM 440GP Register | MPC8540 Register |

|-------------------|--------------------|------------------|

| Number of timers  | 5                  | 4                |

| Time base counter | GP0_TBC            | GTBCR0–3         |

### Table 16. Mapping Features of the IBM 440GP to the MPC8540

| Feature                             | IBM 440GP Register              | MPC8540 Register  |

|-------------------------------------|---------------------------------|-------------------|

| Compare timers                      | GP0_COMP0-4<br>GP0_MASK0-4      | GTCCR0-3          |

| Interrupt enable/status information | GPT0_ISS, GPT0_ISC, and GPT0_IE | GTVPR0–3          |

| Polarity (for external I/O trigger) | DMA0_POL                        | Not programmable. |

| Status information                  | DMA0_SR                         | DGSR              |

Table 16. Mapping Features of the IBM 440GP to the MPC8540 (continued)

# 6 DMA Transfers

This section discusses how the DMA controller transfers data on the IBM 440GP and the MPC8540.

### 6.1 IBM 440GP DMA Controller

The IBM 440GP DMA controller provides four DMA channels, each with its own control, count and control, source address, destination address, and scatter/gather address registers (see Table 17).

| Offset | Mnemonic  | Register                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x100  | DMA0_CR0  | DMA channel control register 0             | DMA0_CR0–DMA0_CR3 configure and enable<br>their respective DMA channels. Configuration<br>settings include transfer modes, width, and channel<br>priority. Before a DMA channel can transfer data, the<br>channel control, count and control, source address,<br>and destination address registers must be<br>programmed.                                                                                                                                             |

| 0x101  | DMA0_CTC0 | DMA count and control register 0           | DMA0_CT0–DMA0_CT3 contain the number of transfers remaining in the DMA transaction for their respective channels when EOT <i>n</i> [TC <i>n</i> ] is programmed as a terminal count output, along with additional channel control information. In addition, these registers contain fields used to enable interrupts for terminal count, end of transfer, and error conditions. Other fields enable parity checking during the peripheral portion of peripheral type. |

| 0x102  | DMA0_SAH0 | DMA source address high register 0         | DMA0_SAH <i>n</i> and DMA0_SAL <i>n</i> contain the source                                                                                                                                                                                                                                                                                                                                                                                                            |

| 0x103  | DMA0_SAL0 | DMA source address low register 0          | address for memory-to-memory and<br>memory-to-peripheral transfers. DMA destination<br>address registers (DMA0_DAH0–DMA0_DAH3 and<br>DMA0_DAL0–DMA0_DAL3) contain the destination<br>address for memory-to-memory and<br>peripheral-to-memory transfers.                                                                                                                                                                                                              |

| 0x104  | DMA0_DAH0 | DMA description address high<br>register 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x105  | DMA0_DAL0 | DMA description address low register 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Table 17. IBM 440GP DMA Controller Registers

| Offset      | Mnemonic  | Register                                   | Description                                                                                                                                                                                                                                                                   |

|-------------|-----------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x106       | DMA0_SGH0 | DMA scatter/gather address high register 0 | Contain the memory address of the next scatter/gather descriptor table. Prior to starting a                                                                                                                                                                                   |

| 0x107       | DMA0_SGL0 | DMA scatter/gather address low register 0  | scatter/gather transfer, software must write the address of the channel's descriptor table to DMA0_SGH <i>n</i> and DMA0_SGL <i>n</i> . Once the scatter/gather transfer starts, DMA0_SGH <i>n</i> and DMA0_SGL <i>n</i> are automatically updated from the descriptor table. |

| 0x108-0x11F | _         | As above for DMA channels 1–3              |                                                                                                                                                                                                                                                                               |

| 0x120       | DMA0_SR   | DMA status register                        | Provides status information for each of the DMA<br>channels. The sleep mode register (DMA0_SLP)<br>enables the DMA controller to enter sleep<br>(low-power) mode after a programmed number of<br>idle cycles.                                                                 |

| 0x123       | DMA0_SGC  | DMA scatter/gather command register        | Sets up a DMA channel for scatter/gather transfers (DMA0_SGC[SSG $n$ ] = 1). Determines whether start scatter/gather transfers are enabled for DMA channels 0 to 3.                                                                                                           |

| 0x125       | DMA0_SLP  | DMA sleep mode register                    |                                                                                                                                                                                                                                                                               |

| 0x125       | DMA0_POL  | DMA polarity configuration register        | Sets the polarity (active state) of the external DMAI/O signals: DMAReq <i>n</i> , DMAAck <i>n</i> , and EOT <i>n</i> [TC <i>n</i> ].                                                                                                                                         |

When you program these DMA registers, the DMA controller performs the requested data transfer between memory and peripherals or memory-to-memory without the need for host intervention. For external peripheral transfers, three external signals are supported for each channel, as follows:

- DMAReqn—DMA request used to request data transfer

- DMAAckn—DMA acknowledge used to instruct peripheral to start DMA transfer

- EOT*n*[TC*n*]—End of transfer or terminal count signal used to stop channel.

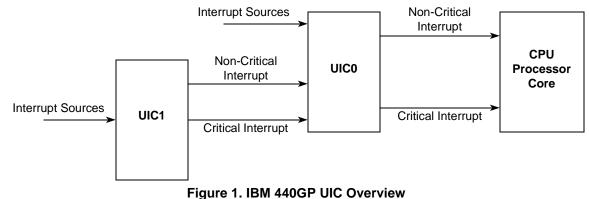

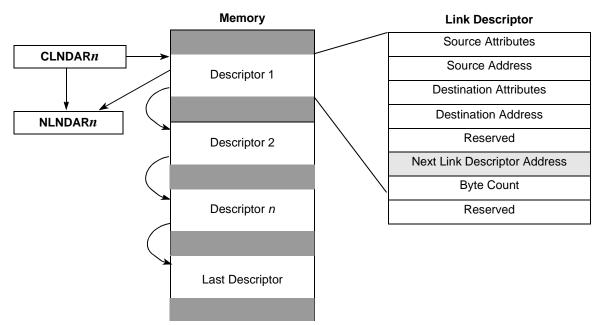

With a normal DMA transfer, it is necessary to program a channel's control, count and control, source, and destination registers for each transfer. The scatter/gather capability of the DMA controller provides a more efficient solution for applications that require multiple transactions on a single DMA channel. Instead of individually programming a channel's registers, software creates a set (linked list) of descriptor tables in system memory. To configure a channel for a scatter/gather transfer, the DMA scatter/gather descriptor address registers (DMA0\_SGH*n* and DMA0\_SGL*n*) for the channel are set to the address of the first descriptor table, which must be quadword (16-byte) aligned. The format of these descriptor tables is shown in Figure 2.

|                    | Byte 1                                                        | BYT | ΓE 2             | Byte 3            | Byte 4 |

|--------------------|---------------------------------------------------------------|-----|------------------|-------------------|--------|

| Word 1             | DMA Channel Control Word (DMA_CRn)                            |     |                  |                   |        |

| Word 2             | Configuration Bits <sup>1</sup>                               |     | Count (DMA_CTCn) |                   |        |

| Word 3             | 3 Source Address High (DMA_SAH <i>n</i> )                     |     |                  |                   |        |

| Word 4             | Source Address Low (DMA_SALn)                                 |     |                  |                   |        |

| Word 5             | Destination Address High (DMA_DAHn)                           |     |                  |                   |        |

| Word 6             | Destination Address Low (DMA_DALn)                            |     |                  |                   |        |

| Word 7             | Linked Next Scatter/Gather Descriptor Address High (DMA_SGHn) |     |                  | IA_SGH <i>n</i> ) |        |

| Word 8             | Linked Next Scatter/Gather Descriptor Address Low (DMA_SGLn)  |     |                  | A_SGL <i>n</i> )  |        |

| <sup>1</sup> The M | <sup>1</sup> The MSB of word 2 is the link (LK).              |     |                  |                   |        |

### Figure 2. Descriptor Table Format

To begin a scatter/gather transfer, software writes DMA0\_SGC register as follows:

- Enable mask—DMA0\_SGC[EM*n*] = 1

- Start scatter/gather bit DMA0\_SGC[SSGn] = 1

- Finally, indicate the bus location of the descriptor tables DMA0\_SGC[SGL*n*] = X.

The DMA controller then reads the descriptor table at address (DMA0\_SGH $n \parallel$  DMA0\_SGLn) and updates the DMA controller registers. On receiving the data from the scatter/gather descriptor table, the channel's terminal count status bit (DMA0\_SR[TCn]) and end of transfer status bit (DMA0\_SR[EOTn]) are automatically cleared.

After the channel registers are loaded from the descriptor table, DMA transfer functions as a normal non-scatter/gather operation. If the LK (link) bit was not set, the scatter/gather process stops when the current transfer completes. Otherwise, the DMA controller reads the descriptor table at address (DMA0\_SGH*n* || DMA0\_SGL*n*) and the process repeats.

### 6.2 MPC8540 DMA Controller

The MPC8540 supports four high-speed DMA channels for transferring blocks of data between the RapidIO controller, PCI, and the local bus address space, independent of the e500 core or external hosts. Data transfers can be triggered and controlled by software or triggered and controlled by an external device using handshake signals DMA\_DREQ, DMA\_DACK, and DMA\_DDONE. In addition, misaligned transfers and DMA sub-block transfers up to 256 bytes are supported on a per channel basis, to minimize the number of discrete memory transactions and to maximize performance over interfaces, such as RapidIO. A summary of the DMA controller registers is shown in Table 18.

| Name <sup>1</sup> | Description                                    |

|-------------------|------------------------------------------------|

| MR <i>n</i>       | DMA <i>n</i> mode register                     |

| SR <i>n</i>       | DMA n Status register                          |

| CLNDAR <i>n</i>   | DMA n current link descriptor address register |

| SATR <i>n</i>     | DMA <i>n</i> source attributes register        |

| SAR <i>n</i>      | DMA <i>n</i> source address register           |

Table 18. MPC8540 DMA Register Summary

| Name <sup>1</sup> | Description                                                          |

|-------------------|----------------------------------------------------------------------|

| DATR <i>n</i>     | DMA <i>n</i> destination attributes register                         |

| DAR <i>n</i>      | DMA <i>n</i> destination address register                            |

| BCR <i>n</i>      | DMA <i>n</i> byte count register                                     |

| NLNDAR <i>n</i>   | DMA n next link descriptor address register                          |

| CLSDARn           | DMA <i>n</i> current list alternate base descriptor address register |

| NLSDAR <i>n</i>   | DMA <i>n</i> next list alternate base descriptor address register    |

| SSR <i>n</i>      | DMA <i>n</i> source stride register                                  |

| DSR <i>n</i>      | DMA <i>n</i> destination stride register                             |

| DGSR              | DMA general status register                                          |

### Table 18. MPC8540 DMA Register Summary (continued)

n = 0 to 3 for all four DMA channels.

There are two main modes of operation, direct mode and chaining mode. In direct mode, software initializes all parameters of the transfer in the appropriate register as follows:

- Mode register (MR*n*), including MR*n*[CTM] = 1

- If stride mode is desired, set MR*n*[XFE]

- If external I/O starts the transfer, set  $MRn[EMS_EN] = 1$

- If software (single-register write) starts the transfer, set MRn[SRW] = 1

- Program other DMA options in MRn

- Program the stride registers (SSR*n* and DSR*n*), if enabled. Stride capability allows a DMA channel to transfer data from selected memory regions of a memory segment by skipping over certain regions of that segment.

- Program the number of bytes to transfer in the byte count register (BCR*n*), up to 64 Mbytes.

- Program DMA source attributes in the 32-bit source attributes register (SATR*n*).

- Program DMA source address in the 32-bit source address register (SAR*n*).

- Program DMA destination attributes in the 32-bit destination attributes register (DATR*n*).

- Program DMA destination address in the 32-bit destination address register (DAR*n*).

In chaining mode, software does not program source/destination parameters via registers. Instead, software provides the parameters of the transfer via link descriptor tables in memory (one chain).

- Program mode register (MR*n*)

- Current link descriptor address register (CLNDAR*n*) is used to point to the first descriptor.

- When DMA is started, the DMA reads parameters of the transfer including next descriptor address loaded in to the next link descriptor address register (NLNDAR*n*).

- When the current DMA segment is transferred, if NLNDAR*n*[EOLND] is set, the DMA is complete. If not set, the next link descriptor address from NLNDAR*n* is read in to the current link descriptor address register (CLNDAR*n*) and the process is repeated.

The link descriptor format for basic chaining mode is shown in Figure 3.

#### DMA Transfers

The extended chaining mode allows the user to setup a series buffer descriptors all referenced from a linked list. Through this linked list, the DMA controller can then walk through multiple BDs allowing complex DMA transactions to be performed.

Figure 3. MPC8540 Basic Chaining Mode—Link Descriptor Format

### 6.3 Porting DMA Transfers to the MPC8540

Similarities exist between the DMA controller in the IBM 440GP and MPC8540, although the exact register formats are different. Key features of the DMA controllers and how registers from the IBM 440GP map to MPC8540 are shown in Table 19.

| Feature                                     | IBM 440GP Register                                                                                             | MPC8540 Register                                                                                              |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Enabling DMA channels and mode of operation | DMA0_CRn                                                                                                       | MR <i>n</i>                                                                                                   |

| Transfer size                               | DMA0_CR <i>n</i> [PW] × DMA0_CT <i>n</i> [TC]                                                                  | BCRn                                                                                                          |

| Source address/attributes                   | DMA0_SAHn and DMA0_SALn                                                                                        | SAR <i>n</i> and SATR <i>n</i>                                                                                |

| Destination address/attributes              | DMA0_DAHn and DMA0_DALn                                                                                        | DAR <i>n</i> and DATR <i>n</i>                                                                                |

| DMA chaining                                | DMA0_SCH <i>n</i> , DMA0_SGL <i>n</i> , DMA_SCR <i>n</i> ,<br>and link descriptor tables in external<br>memory | MR <i>n</i> [CTM] = 0<br>CLNDAR <i>n</i> , NLNDAR <i>n</i> , and link descriptor<br>tables in external memory |

| Sleep mode                                  | DMA0_SLP                                                                                                       | Supported globally on PQ3 but not DMA specific                                                                |

| Polarity (for external I/O trigger)         | DMA0_POL                                                                                                       | Not programmable                                                                                              |

| Status information                          | DMA0_SR                                                                                                        | DGSR                                                                                                          |

Table 19. Mapping Features of the IBM 440GP DMA Controller to the MPC8540

The MPC8540 features are identical to those of the IBM 440GP for DMA transfers. In addition, the DMA controller on the MPC8540 is more flexible and offers support for extended chaining mode and DMA stride transfers.

# 7 Buffer Descriptors

Buffer descriptors (BDs) are the primary data structures used on the IBM 440GP and MPC8540 for passing data between higher level software and on-chip serial communication peripherals. Organization of BDs differs between the IBM 440GP and the MPC8540, but the basic structure is similar, easing migration to the MPC8540. For example, the differences in BDs for Ethernet operation on the IBM 440GP and MPC8540 will be examined.

# 7.1 IBM 440GP Buffer Descriptors

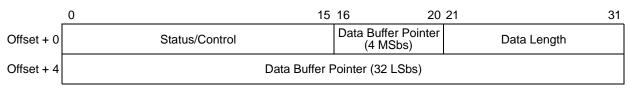

On the IBM 440GP, a hardware block referred to as the memory access layer (MAL) manages data transfers between two Ethernet controllers (EMACs). To communicate with software device drivers, MAL utilizes a buffer descriptor ring structure in external memory. A software device driver uses the buffer descriptor structure to inform MAL about buffer locations and packet or buffer status. The descriptors are pointers to the actual buffers organized as circular queues. Each EMAC is associated with two tables (transmit and receive) of up to 256 buffer descriptors per table. The format of the buffer descriptor (BD) shown in Figure 4, is the same for both transmit and receive.

### Figure 4. IBM 440GP Buffer Descriptor Format

The most significant half word in each buffer descriptor contains the status/control bits. The second half word determines the 4 MSbs of the data buffer pointer and the data length (in bytes) referenced in this buffer descriptor. The second word in the buffer descriptor contains the 32 LSbs of the data buffer pointer that points to the actual data buffer in memory. An example of the BD and data buffer structure in external memory is shown in Figure 5.

BD Tables (Memory)

MAL BD Table Pointer Register

Memory

Descriptor 0

Descriptor 1

Descriptor 1

•

MAL Channel 3 Table Pointer

Buffer Pointer

MAL Channel 3 Table Pointer

Data Buffer

NOTE: W = 1 means the wrap bit is set for this descriptor.

W = 1 Buffer Pointer

### Figure 5. IBM 440GP BDs and Data Buffers in External Memory

Table 20 shows the format of the status/control bits for transmit buffer descriptors. Bits 6–15 are used for EMAC specific control information during a write access and status information during a read access.

| Bit | Name  | Description                                                                         |

|-----|-------|-------------------------------------------------------------------------------------|

| 0   | R     | Ready—indicates Tx buffer is ready for transmission                                 |

| 1   | W     | Wrap—last buffer in the circular BD table                                           |

| 2   | СМ    | Continuous mode—indicates continuous transmission of buffer regardless of the R bit |

| 3   | L     | Indicates last buffer in frame                                                      |

| 4   | —     | Reserved                                                                            |

| 5   | I     | Specifies an Interrupt to be generated on processing of BD                          |

| 6   | FCS   | Generate FCS (control)                                                              |

|     |       | Indicates BAD FCS (status)                                                          |

| 7   | PAD   | Generate padding (control)                                                          |

|     | BPACK | Indicates BAD packet (status)                                                       |

| 8   | ISA   | Insert source address (control)                                                     |

|     | LOCS  | Loss of carrier sense (status)                                                      |

| 9   | RSA   | Replace source address (control)                                                    |

|     | ED    | Excessive deferral (status)                                                         |

### Table 20. IBM 440GP Status/Control Bits of TxBDs

| Bit | Name | Description                   |

|-----|------|-------------------------------|

| 10  | IVTg | Insert VLAN tag (control)     |

|     | EC   | Excessive collisions (status) |

| 11  | RVTg | Replace VLAN tag (control)    |

|     | LC   | Late collisions (status)      |

| 12  | MC   | Multiple collisions (status)  |

| 13  | SC   | Single collision (status)     |

| 14  | UR   | Underrun (status)             |

| 15  | SQE  | Signal quality error (status) |

### Table 20. IBM 440GP Status/Control Bits of TxBDs (continued)

Table 21 shows the format of the status/control bits for receive buffer descriptors. Bits 6–15 are used for EMAC-specific status information.

| Bit | Name | Description                                                                    |

|-----|------|--------------------------------------------------------------------------------|

| 0   | E    | Empty—indicates the receive data buffer is ready to receive data               |

| 1   | W    | Wrap—last buffer in the circular BD table                                      |

| 2   | СМ   | Continuous mode—indicates continuous reception of data regardless of the E bit |

| 3   | L    | Indicates last buffer in frame                                                 |

| 4   | F    | Indicates first buffer in frame                                                |

| 5   | I    | Specifies an interrupt to be generated on processing of BD                     |

| 6   | OR   | Indicates overrun error indication                                             |

| 7   | PP   | Pause packet indication                                                        |

| 8   | BP   | Bad packet—indicates early termination caused by packet error                  |

| 9   | RP   | Runt packet error indication                                                   |

| 10  | SE   | Short event error indication                                                   |

| 11  | AE   | Alignment error indication                                                     |

| 12  | BF   | Bad FCS error indication                                                       |

| 13  | PTL  | Packet too long error indication                                               |

| 14  | ORE  | Out of range error indication                                                  |

| 15  | IRE  | In range error indication                                                      |

### Table 21. IBM 440GP Status/Control Bits of RxBDs

### 7.2 MPC8540 Buffer Descriptors

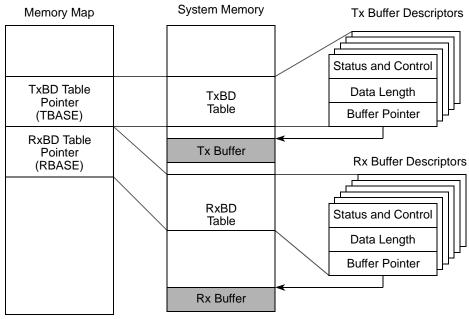

The three-speed ethernet controllers (TSECs) on the MPC8540 also use buffer descriptors and data buffers in the transmission and reception of Ethernet frames.

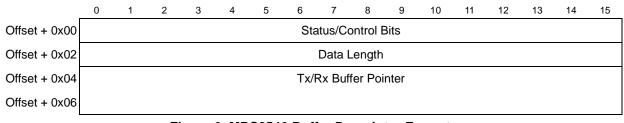

The format of the buffer descriptor (BD) shown in Figure 6 is the same for both transmit and receive:

### Figure 6. MPC8540 Buffer Descriptor Format

The first word contains the status/control bits and the buffer data length (in bytes) to be transmitted or received. The second word in the buffer descriptor contains the data buffer pointer that points to the actual data buffer in memory. An example of the BD and data buffer structure in external memory is shown in Figure 7.

Figure 7. Example of MPC8540 TSEC Memory Structures for BDs

Table 22 shows the format of the status/control bits for the MPC8540 TSEC transmit buffer descriptors.

Table 22. MPC8540 TSEC Status/Control Bits of Tx BDs

| Bit | Name | Description                                                |

|-----|------|------------------------------------------------------------|

| 0   | R    | Ready—indicates TX buffer is ready for transmission        |

| 1   | PAD  | Padding for short <64-byte Ethernet frames                 |

| 2   | W    | Wrap—last buffer in the circular BD table                  |

| 3   | I    | Specifies an interrupt to be generated on processing of BD |

| 4   | L    | Indicates last buffer in frame                             |

| 5   | тс   | Transmit CRC                                               |

| Bit   | Name | Description                             |

|-------|------|-----------------------------------------|

| 6     | DEF  | Defer                                   |

| 7     | _    | Reserved                                |

| 8     | HFE  | Hugh frame enable (control)             |

|       | LC   | Late collision indication               |

| 9     | RL   | Retry limit reached indication          |

| 10–13 | RC   | Retry count indicates number of retries |

| 14    | UN   | Underrun indication                     |

| 15    | _    | Reserved                                |

### Table 22. MPC8540 TSEC Status/Control Bits of Tx BDs (continued)

Table 23 shows the format of the status/control fields for the MPC8540 TSEC receive buffer descriptors.

| Bit | Name | Description                                                      |

|-----|------|------------------------------------------------------------------|

| 0   | E    | Empty—indicates the receive data buffer is ready to receive data |

| 1   | —    | Reserved                                                         |

| 2   | W    | Wrap—last buffer in the circular BD table                        |

| 3   | I    | Specifies an interrupt to be generated on processing of BD       |

| 4   | L    | Indicates last buffer in frame                                   |

| 5   | F    | Indicates first buffer in frame                                  |

| 6   | —    | Reserved                                                         |

| 7   | М    | Miss—frame accepted because of promiscuous but no match address  |

| 8   | BC   | Broadcast—frame had a broadcast address                          |

| 9   | MC   | Multicast—frame had a multicast address                          |

| 10  | LG   | Large-indicates frame bigger than maximum frame length received  |

| 11  | NO   | Non-octet-frame not divisible by 8 received                      |

| 12  | SH   | Short—indicates short frame received if enabled                  |

| 13  | CRC  | CRC—frame had a CRC error                                        |

| 14  | OV   | Overrun indication                                               |

| 15  | TR   | Truncation—indicates frame was truncated                         |

### Table 23. MPC8540 TSEC Status/Control Fields of RxBDs

### 7.3 Porting Buffer Descriptors to MPC8540

Since both the MPC8540 and the IBM 440GP rely on circular queues of buffer descriptors, porting software applications from the IBM 440GP to the MPC8540 should be relatively straightforward. Buffer descriptors themselves have a similar format, although the exact contents do differ.

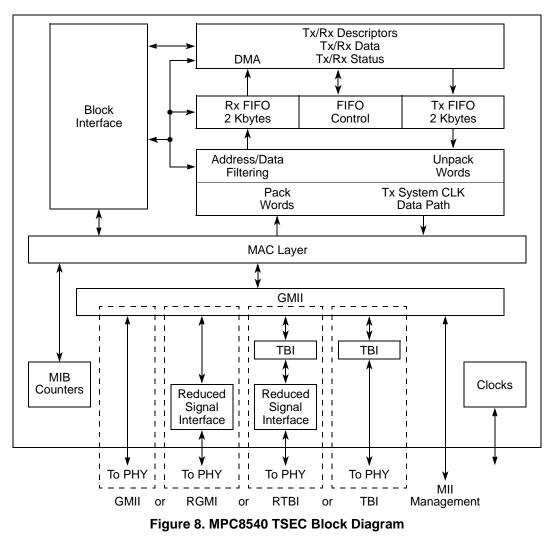

# 8 Ethernet

Table 24 compares the key Ethernet features of IBM 440GP and MPC8540. Many similarities exist between the Ethernet access controllers (EMACs) on the IBM 440GP and the three-speed ethernet controllers (TSECs) of the MPC8540. In the following sections we discuss only Ethernet features common to both processors and the configuration differences.

| Ethernet Feature                                              | IBM 440GP                                             | MPC8540                                             |

|---------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|

| Standards                                                     | IEEE 802.3, 802.3u, and 802.3x,                       | IEEE 802.3, 802.3u, 802.3x, 802.3z,<br>and 802.3ab  |

| Speeds                                                        | 10/100 Mbps                                           | 10/100/1000 Mbps                                    |

| Interfaces                                                    | MII, RMII, and SMII                                   | GMII, RGMII, MII, RMII, TBI, and RTBI               |

| Half-duplex support                                           | 10/100 Mbps                                           | 10/100 Mbps                                         |

| Full-duplex support                                           | 10/100 Mbps                                           | 10/100/1000 Mbps                                    |

| Automatic retransmission of packets on collision              | Yes                                                   | Yes                                                 |

| FCS (CRC) checking and generation                             | Yes                                                   | Yes                                                 |

| Programmable inter-packet gap                                 | Yes                                                   | Yes                                                 |

| Flow control (including pause packet checking and generation) | Yes                                                   | Yes                                                 |

| Address recognition                                           | Unicast, multicast, broadcast, and promiscuous mode   | Unicast, multicast, broadcast, and promiscuous mode |

| Jumbo frame support                                           | No                                                    | Programmable option                                 |

| Automatic source address insertion or replacement             | Programmable option                                   | No                                                  |

| VLAN support                                                  | VLAN ID tag insertion/replacement in transmit packets | None                                                |

| Wake on LAN (WOL) handling                                    | Yes                                                   | No                                                  |

### Table 24. Ethernet Comparison of IBM 440GP versus MPC8540

### 8.1 IBM 440GP Ethernet Controllers

The IBM 440GP supports two Ethernet access controllers (EMACs) for half-/full-duplex operation at 10/100 Mbps. Each EMAC uses a media independent interface (MII) controlled by a ZMII bridge to connect to standard Ethernet physical devices (PHYs). The ZMII bridge supports one MII interface, or two RMII/SMII interfaces selected by enabling bits 28–29 of the power-on configuration register 0 (CPC0\_STRP0). In addition, there are three registers which control and maintain status information on the ZMII bridge. A register summary for each EMAC is shown in Table 25.

| Table 25. IBM 440GP Ethernet MAC Register Su | ummary |

|----------------------------------------------|--------|

|----------------------------------------------|--------|

| Mnemonic               | Register | Description                                                                                |  |

|------------------------|----------|--------------------------------------------------------------------------------------------|--|

| EMACn_MR0 <sup>1</sup> | •        | Define the operating mode including: Tx/Rx enable, full-dup                                |  |

| EMACn_MR1              |          | operation, flow control, 10/100 Mbps operation, FIFO size, loopback mode, and VLAN enable. |  |

| Table 25. IBM 440GF | P Ethernet MAC | Register | Summary |

|---------------------|----------------|----------|---------|

|---------------------|----------------|----------|---------|

| Mnemonic                       | Register                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMACn_TR0                      | Transmit mode register 0                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EMACn_TR1                      | Transmit mode register 1                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EMAC <i>n_</i> RMR             | Receive mode register                        | Defines the EMAC mode during receive operation including:<br>address recognition modes, strip padding/FCS enable/disable,<br>propagate pause packets, and reception of oversized packets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| EMACn_ISR                      | Interrupt status register                    | The EMAC generates interrupt events using the contents of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

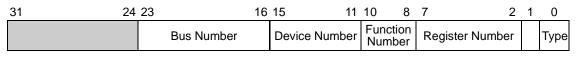

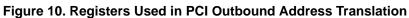

| EMAC <i>n</i> _ISER            | Interrupt status enable register             | interrupt status register (EMAC <i>n</i> _ISR) and the corresponding mask bits in the interrupt status enable register (EMAC <i>n</i> _ISER).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |