# Freescale Semiconductor

**Application Note**

Document Number: AN4180 Rev. 0, 08/2010

# System-80 Asynchronous Display on the i.MX31 WINCE 6.0 PDK

by Multimedia Applications Division Freescale Semiconductor, Inc. Austin, TX

This application note provides the necessary information, considerations, and procedure to add or adapt a System-80 Type 2 (sampling with the read and write signals) asynchronous panel to the WINCE600 Board Support Package (BSP) for the i.MX31 Platform Development Kit (PDK). This application note describes the smart panel information and the generalities of the Asynchronous Display Controller (ADC). In addition, this application note also describes the development process to adapt a new panel to the BSP, considering that the framework driver structure is already provided by the operating system. This application note assumes that the reader is familiar with the Microsoft<sup>®</sup> Platform Builder packages and the WINCE Embedded 6.0 Device Driver concepts.

# 1 Overview of i.MX31 Display

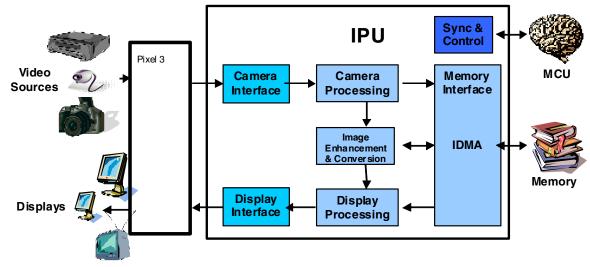

As a multimedia processor, the i.MX31 supports several types of displays. The display devices are handled by a special module called the Image Processing Unit (IPU). The IPU module also handles other graphic interfaces such as the Camera interface and 2D graphics acceleration. All the IPU submodules are connected by a private

#### Contents

| 1. | Overview of i.MX31 Display         | 1  |

|----|------------------------------------|----|

| 2. | LCD Generalities                   | 3  |

| 3. | Asynchronous Display Interfaces    | 5  |

| 4. | Display Configuration in WINCE 6.0 | 22 |

| 5. | Modifying the BSP                  | 31 |

| 6. | Revision History                   | 47 |

© 2010 Freescale Semiconductor, Inc. All rights reserved.

#### Overview of i.MX31 Display

Direct Memory Access (DMA) Interface that is used for the IPU to transfer data between the submodules and also between the IPU and external memory.

Figure 1 shows the functional block diagram of the IPU module.

Figure 1. IPU Functional Block Diagram

Selecting an appropriate Liquid Crystal Display (LCD) for a mobile device involves several conflicts with respect to the requirements. Some of these conflicts are described as follows:

- Large amount of data, implying high rate of data transfer and processing, requiring significant resources

- Flexibility to support a variety of use cases

- Small size, cost, and power consumption

Freescale provides reference designs for the i.MX family where the functionality of LCD is demonstrated. However, according to the requirements, developers find many reasons to replace the display in their products. Features such as screen size, resolution, weight, power consumption, and price are very important in a commercial multimedia product. Another important fact about LCD panels is that many displays become obsolete quickly. Therefore, it is hard to find the same LCD panel included in the reference design while creating a product.

This application note is intended only for Smart Displays that include panels, which uses the System-80 Type 2 (sampling with the read and write signals) as display interface. However, this application note also provides some information about dumb displays.

# 2 LCD Generalities

This section describes the generalities of the LCD devices.

# 2.1 LCD Basics

LCD is an electronic device, which consists of an array of pixels, which can be either color or monochrome unit. Every element in the array is created with a special material that allows the LCD to change the characteristics of the light that passes through them. These devices do not emit light and therefore, another element named backlight is shipped along with the panel to create a fully functional display device.

# 2.1.1 Resolution

In this application note, the term resolution is used to refer to the number of pixels contained in an LCD array. It has two dimensions—horizontal and vertical.

Table 1 lists the most common video resolution standards.

| Video Name | Description                          | Width | Height | Aspect Ratio |

|------------|--------------------------------------|-------|--------|--------------|

| CGA        | Color Graphics Adapter               | 320   | 200    | 8:5          |

| QVGA       | Quarter VGA                          | 320   | 240    | 4:3          |

| VGA        | Video Graphics Array                 | 640   | 480    | 4:3          |

| NTSC       | National Television System Committee | 720   | 480    | 3:2          |

| PAL        | Phase Alternating Line (TV)          | 768   | 576    | 4:3          |

#### Table 1. Video Resolution Standards

The maximum standard resolution that the i.MX31 supports is SVGA and hence, resolutions greater than SVGA are not included in Table 1.

All resolutions mentioned in Table 1 show a landscape orientation of LCD panels, which means that there are more pixels in the horizontal axis than in the vertical axis. However, there are also portrait LCD panels available in the market with the same standard resolution but the horizontal and vertical size are inverted. These portrait LCD panels have more vertical pixels when compared to the horizontal pixels.

Figure 2 shows the portrait and landscape orientation of an LCD panel.

Figure 2. Portrait and Landscape Orientation of an LCD Panel

It is important to select an appropriate orientation of the LCD panel because both the electronic and optical features are optimized for applications that use the native orientation of the panel. Besides the optical

#### LCD Generalities

characteristics, the dumb displays include an embedded LCD controller to draw the pixels from left to right and top to bottom. However, to show images or videos on the LCD panel using a non-native orientation, the display content is pre-processed. Therefore, the image is stored in a buffer in a way (order) the LCD controller expects the pixel information to be sent to it. This operation is called rotation and the i.MX31 includes hardware to perform this operation. It is recommended to select the LCD panel that mostly uses its native orientation to avoid additional image processing.

Figure 3 shows the portrait and landscape LCD panels displaying images in the non-native orientation.

Figure 3. Rotated Frame on Portrait and Landscape Orientation of an LCD Panel

The frames can be rotated in 90°, 180°, or 270°. Every frame has to be rotated before sending to the display.

## 2.1.2 Size

The size of an LCD panel is measured diagonally in inches, from top left corner to bottom right corner. Since the size directly impacts the pixel width, it is common to assume the size of a VGA ( $640 \times 480$ ) panel to be larger than a QVGA ( $320 \times 240$ ) panel because the number of pixels in VGA is four times greater when compared to QVGA. But, this is not true at all times. LCD manufacturing processes allow the size and resolution to be independent variables. It is difficult to determine the size of a panel from its resolution. Screens that are larger in size tend to consume more power than the smaller ones and also impact the size and weight of the final product. On the other hand, higher resolutions on smaller LCD panels can complicate the visibility for the final user. Based on the information available in the datasheet, it is difficult to determine if a particular LCD panel fits the application. Instead, it is recommended to view the LCD in other reference design or demo before making a final decision.

# 2.1.3 Color Spaces

A color space is a way to represent colors. There are two main color spaces—RGB (that is, RGB565, RGB888, and RGBA8888) and YUV (that is, YUV 4:4:4, YUV 4:2:2, and YUV 4:2:0). The i.MX31 supports both the color spaces, but the display panels can receive data only by using the RGB interface.

# 2.2 LCD Types

The LCD panels are categorized as synchronous and asynchronous panels and their descriptions are described in the following sections.

# 2.2.1 Synchronous Panel (Dumb Display)

Dumb displays or synchronous displays are panels which require the microprocessor to send all pixels in the image every frame. In these panels, screen refresh is performed by driving the complete frame data continuously. In general, smart displays are more expensive than dumb displays and due to this reason, synchronous panels are more commonly used in the final product.

# 2.2.2 Asynchronous Panel (Smart Display)

The advantage of smart displays is that the i.MX31 has to send only the display data when the image has changed, and most of the times it sends only the portion that has changed. Images can be sent at any time and the screen refresh is handled by the embedded Smart Liquid Crystal Display Controller. Another advantage of smart displays is that the i.MX31 can handle three asynchronous displays and synchronous interface simultaneously. If an application requires two LCD panels, one of them must be an asynchronous interfaces.

# 3 Asynchronous Display Interfaces

There are two types of asynchronous display interfaces—System-80 LCD interface and 68 K interface.

# 3.1 System-80 (Type 2) LCD Interface

The System-80 LCD interface is one of the widely used interfaces for smart displays. It is also known as 80-series system bus interface or Intel 80 interface. This interface is composed of four control lines—CS, RS, WR, and RD, and the data bus whose width can vary. The i.MX31 can handle the Type 1 (sampling with the chip select signal) and Type 2 (sampling with the read and write signals) interfaces, but this application note focuses only on the Type 2 interface, which is the most commonly used interface.

Table 2 shows the System-80 (Type 2) interface signals.

| Signal    | IPU Signal          | Description                                |

|-----------|---------------------|--------------------------------------------|

| CS0       | IPP_DO_DISPB_D0_CS  | Display 0 chip select                      |

| CS1       | IPP_DO_DISPB_D1_CS  | Display 1 chip select                      |

| CS2       | IPP_DO_DISPB_D2_CS  | Display 2 chip select                      |

| RS        | IPP_DO_DISPB_PAR_RS | Data/command select for parallel interface |

| WR        | IPP_DO_DISPB_WR     | Write strobe signal                        |

| RD        | IPP_DO_DISPB_RD     | Read strobe signal                         |

| DB [15:0] | DISPB_DATA [15:0]   | Data bus                                   |

Table 2. System-80 (Type 2) Interface Signals

The various signals that are available in the System-80 LCD interface are as follows:

• CS 0–2—Chip Select (CS) signal is used to communicate to the smart LCD panel that the commands and data used in the System-80 interface belongs to LCD. The i.MX31 can handle up to three asynchronous panels, and the method used to distinguish which LCD is addressed by the

**Asynchronous Display Interfaces**

microprocessor by using a CS per panel. Most of the times, the CS0 signal is active low and the tag used for this line is ncs.

- RS—Register Select (data/command) is a control signal for the System-80 interface of the asynchronous display (0–2). Using the RS signal, the processor communicates to the LCD panel if the information in the bus has to be interpreted either as a command or data. In general, command mode is used to set the register address before sending the register's value using the data mode.

- WR—When the Write strobe signal is active, the processor is indicating that either the command or data is on the data bus and it must be read by the LCD panel.

- RD—The Read strobe signal is used by the i.MX31 to request the LCD panel to place the command or data in the bus when the processor is ready to read the information and this information is related with the previous command.

- DI—The Display Interface (DI) is used to send/receive data and command to/from the LCD panel. Depending on the LCD interface, the bus width can vary from 7 to 18 bits.

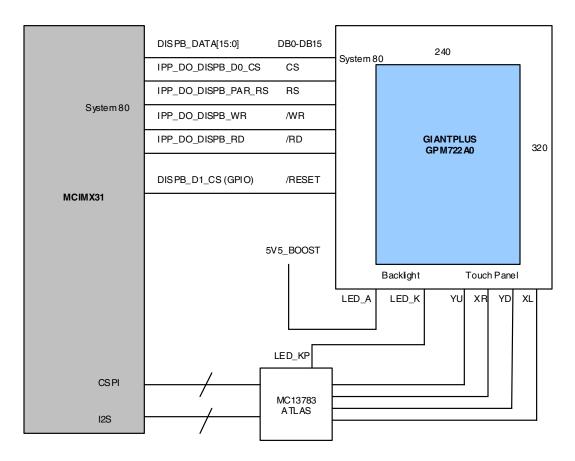

Figure 4 shows the LCD interface between the i.MX31 processor and the Giant plus GPM722A0 VGA panel.

#### Figure 4. LCD Interface Between the i.MX31 and GiantPlus GPM722A0 VGA Panel

Figure 4 shows how i.MX31 is interfaced with a smart LCD panel such as the GPM722A0 GiantPlus. The System-80 (Type 2) interface is used for LCD initialization (command mode) and also for sending the

display buffers (template data mode). Additionally, the LCD panel requires a reset signal, external backlight power booster circuit, and touch screen support. In PDK (only), the touch screen support feature is provided by PMIC ATLAS MC13783 by using the keypad LED circuit. Also, the PMIC settings are configured by the i.MX31 using an SPI interface.

# 3.2 68 K Interface

The 68 K interface is from Motorola and it is one of the widely used interfaces for smart displays. This interface is composed of four control lines—CS, RS, RW\_WR, and E\_RDB, and the data bus, whose width can vary. The difference between this interface and the System-80 interface is the inclusion of an Enable signal (E\_RDB), which is used to indicate when the data needs to be latched for read and write operations. Also, unlike System-80 interface, this interface combines the read or write selection in a single line (RW\_WR).

Table 3 shows the 68 K interface signals.

| Signal    | IPU Signal          | Description                                |

|-----------|---------------------|--------------------------------------------|

| CSO       | IPP_DO_DISPB_D0_CS  | Display 0 chip select                      |

| CS1       | IPP_DO_DISPB_D1_CS  | Display 1 chip select                      |

| CS2       | IPP_DO_DISPB_D2_CS  | Display 2 chip select                      |

| RS        | IPP_DO_DISPB_PAR_RS | Data/command select for parallel interface |

| RD_WR     | IPP_DO_DISPB_RD_WR  | Read/Write strobe signal                   |

| EN        | IPP_DO_DISPB_EN     | Enable                                     |

| DB [15:0] | DISPB_DATA [15:0]   | Data bus                                   |

Table 3. 68 K Interface Signals

The various signals that are available in the 68 K interface are as follows:

- CS 0–2—Chip Select (CS) signal is used to communicate to the smart LCD panel that the commands and data used in the 68 K interface belongs to LCD. The i.MX31 can handle up to three asynchronous panels, and the method used to distinguish which LCD is addressed by the microprocessor is by using one CS per panel. Most of the times, the CS signal is active low and the tag used for this line is ncs.

- RS—Register Select (data/command) is a control signal for the 68 K interface of the asynchronous display (0–2). Using the RS signal, the processor communicates to the LCD panel if the information in the bus has to be interpreted either as a command or data. In general, command mode is used to set the register address before sending the register's value using the data mode.

- RD\_WR—Read/Write control signal is used to distinguish whether the information on the data bus is being written to the LCD, or if the instruction is a reading request to the LCD.

- EN—Enable signal determines when the data in the bus is ready to perform both the read and write operations.

- DI—Depending on the LCD interface, the bus width can vary from 7 to 18 bits. This application note does not focus on the display interface. Therefore, there are no details available about this interface.

Asynchronous Display Interfaces

# 3.3 Asynchronous Serial Interfaces

Apart from the parallel interface, there are also serial interfaces that can be used to control the smart panels. The i.MX31 IPU can handle the following types of asynchronous serial interfaces:

- 3-wire (with bidirectional data line)

- 4-wire (with separate data input and output lines)

- 5-wire type 1 (with sampling RS by the serial clock)

- 5-wire type 2 (with sampling RS by the chip select signal)

As this application note do not focus on the above interfaces, there are no details available about all these interfaces.

# 3.4 System-80 (Type 2) Display Timing and Signals

This section focuses on the timing and signal waveforms and how to configure them in the LCD panel and the i.MX31 display interface. The first step in selecting an LCD module is to refer to its datasheet. The datasheet must contain the pin interface, system interface data format (that is, 16-bit or 18-bit interface, 1,2, or 3 transfer per pixel), initialization routine, and timing charts for the System-80 (Type 2) interface. Many times a shorter version of the datasheet is only available with no sufficient information. In this case, it is advisable to request for full documentation from the supplier. The document that is received contains a message (in every sheet) indicating that the document is only a preliminary version. Though there is not much difference between the preliminary and final versions, it is always better to have the final version.

# 3.4.1 Timing Charts

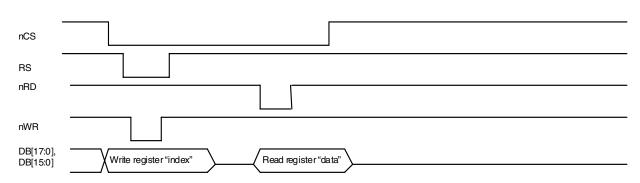

To understand the timing issues in a System-80 LCD interface, review the charts—CS, RS, RD, WR, and Data bus in the datasheet.

These charts can be used to verify the logical value of every signal while performing any operation. Most of the System-80 LCD datasheets contain diagrams to show how to read, write, and send commands to the LCD controller.

For example, if the LCD is using the System-80 (Type 2) interface with 18/16 bit data system interface, then the diagrams are similar to the following figures.

Figure 5 shows the write sequence of the System-80 (Type 2) 18/16 bit interface.

| nCS                   |                                              |

|-----------------------|----------------------------------------------|

| RS                    |                                              |

| nRD                   |                                              |

| nWR                   |                                              |

| DB[17:0],<br>DB[15:0] | Write register "index" Write register "data" |

#### Figure 5. Write Sequence of the System-80 (Type 2) 18/16 Bit Interface

In this figure, the CS, RD, and WR signals are active low. These signals become active only when the signal goes low. From Figure 5, it is verified to be a System-80 (Type 2) interface, because the data is latched by using the RD and WR signals. When RS is the only signal used in conjunction with WR signal and also when RS is low, the information on the data bus must be treated as a command (register). On the other hand, when RS has a high value and WR is active, the information on the data bus is related with some data, which is typically a straight RS polarity.

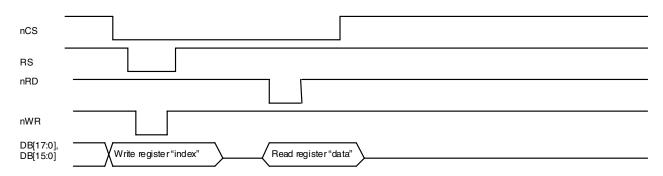

## 3.4.1.1 Read from Register

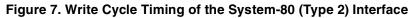

Figure 6 shows the read sequence of the System-80 (Type 2) 18/16 bit interface.

Figure 6 shows that the RD signal is used to indicate when the data is going to be read and this signal is used only after a command is issued.

It is observed that the data polarity is always straight for color LCDs and can be inverted for monochromatic LCDs.

# 3.4.2 Timing Concepts

Though the previous figures are helpful in understanding the logical flow of the interface, more details about the timing of each state (in ns) are required to configure the display interface.

Table 4 shows the timing concepts in the asynchronous System-80 (Type 2) LCD interface.

| Timing Concepts                              | Description                                                                                                                                                                                                                                 |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Write system cycle time (t <sub>CYCW</sub> ) | Width of the write signal strobe cycle that is used to mark the writing of each data or command to the LCD. It is the combination of the write low pulse width and the write high pulse width and the transition between these states.      |

| Read system cycle time $(t_{CYCR})$          | Width of the read signal strobe cycle that is used to mark the reading of each data or command from the LCD panel. It is the combination of the read low pulse width and the read high pulse width and the transition between these states. |

| Write low pulse width (t <sub>WL</sub> )     | Time for which the WR signal must be low for a valid write system cycle time.                                                                                                                                                               |

Table 4. Timing Concepts

| Write high pulse width (t <sub>WH</sub> )    | Time for which the WR signal must be high for a valid write system cycle time.                                                                                                                                                                  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read low pulse width (t <sub>RL</sub> )      | Time for which the RD signal must be low for a valid read system cycle time.                                                                                                                                                                    |

| Read high pulse width<br>(t <sub>RH</sub> )  | Time for which the RD signal must be high for a valid read system cycle time                                                                                                                                                                    |

| Setup time for write<br>(t <sub>DCSW</sub> ) | Time measured between the t <sub>CYCW</sub> initialization (RS) until the WR signal goes low.                                                                                                                                                   |

| Setup time for read<br>(t <sub>DCSR</sub> )  | Time measured between the t <sub>CYCR</sub> initialization (RS) until the RD signal goes low.                                                                                                                                                   |

| Write signal fall time<br>(t <sub>Wf</sub> ) | Maximum acceptable time that the WR signal must spend in the transition from high-level to low-level state. Most of the times, this value is ignored, and it is assumed that the i.MX LCD interface is able to switch the signal at high speed. |

| Write signal rise time<br>(t <sub>Wr</sub> ) | Maximum acceptable time that the WR signal must spend in the transition from low-level to high-level state. Most of the times, this value is ignored, and it is assumed that the i.MX LCD interface is able to switch the signal at high speed. |

| Read signal fall time<br>(t <sub>Rf</sub> )  | Maximum acceptable time that the RD signal must spend in the transition from high-level to low-level state. Most of the times, this value is ignored, and it is assumed that the i.MX LCD interface is able to switch the signal at high speed. |

| Read signal rise time<br>(t <sub>Rr</sub> )  | Maximum acceptable time that the RD signal must spend in the transition from low-level to high-level state. Most of the times, this value is ignored, and it is assumed that the i.MX LCD interface is able to switch the signal at high speed. |

| Hold time for write<br>(t <sub>DCHW</sub> )  | After the WR signal switches from low-level to high-level (write latch instruction), the address hold time is the time that the RS signal needs to maintain in its current value ( $0 = $ command and $1 = $ Data).                             |

| Hold time for read<br>(t <sub>DCHR</sub> )   | After the RD signal switches from low-level to high-level (write latch instruction), the address hold time is the time that the RS signal needs to maintain in its current value ( $0 = $ command and $1 = $ Data).                             |

| Write data set up time<br>(t <sub>DS</sub> ) | Time required to verify whether the data bus has the valid data before executing the write latch instruction.                                                                                                                                   |

| Write data hold time<br>(t <sub>DH</sub> )   | Time required to verify whether the i.MX31 has the valid data on the bus after executing the write latch instruction.                                                                                                                           |

| Read data delay time<br>(t <sub>RACC</sub> ) | Time taken by the LCD to place the valid data on the bus after it receives the read start instruction (RD transition from high-level to low-level).                                                                                             |

| Read data hold time<br>(t <sub>ROH</sub> )   | Time taken by the LCD to place the valid data on the bus after it receives the read latch instruction (RD transition from low-level to high-level).                                                                                             |

#### Table 4. Timing Concepts (continued)

Figure 7 shows the write cycle timing of the System-80 (Type 2) interface.

Figure 8 shows the read cycle timing of the System-80 (Type 2) interface.

Figure 8. Read Cycle Timing of the System-80 (Type 2) Interface

## 3.4.3 Custom LCD Timing

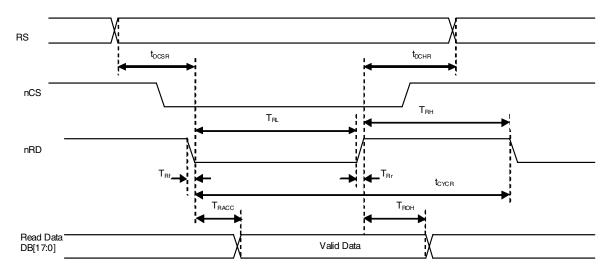

This section describes the reset signal and its artifacts.

## 3.4.3.1 Reset

Many LCD panels include an LCD controller, which needs an external system reset. If the LCD uses the reset signal, the timing regarding the pulse has to be found.

#### Asynchronous Display Interfaces

Figure 9 shows the example of a reset signal.

Figure 9. Reset Signal Example

Table 5 provides the artifacts of the reset signal.

Table 5. Artifacts of Reset Signal

| Parameter             | Symbol            | Minimum | Туре | Maximum | Unit |

|-----------------------|-------------------|---------|------|---------|------|

| Reset low-level width | T <sub>RES</sub>  | 1       | _    | _       | ms   |

| Reset rise time       | T <sub>rRES</sub> | —       |      | 10      | μs   |

The important fact that can be observed is the reset signal is active low. This means that the reset signal must be high while performing normal operations. The reset signal must be low for at least 15 ns to ensure a valid reset. The reset pin is controlled by the i.MX31 General Purpose Input/Output (GPIO). It is recommended not to use the RC circuit to generate the reset signal as it restricts the rising time of the signal to  $10 \,\mu s$ .

# 3.5 System Interface Data/Command Format

The data width is not the only characteristic of the data interface. Another important feature of the smart panel is the Interface Data Format.

To explain this, the following example needs to be reviewed:

Consider that an RGB565 LCD is available and a 16-bit data bus width is used. The first step is to send all the RGB data using one single transfer (16-bit data bus and one transfer per pixel) through the parallel data bus and this approach is an appropriate way to do it.

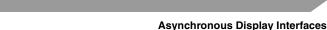

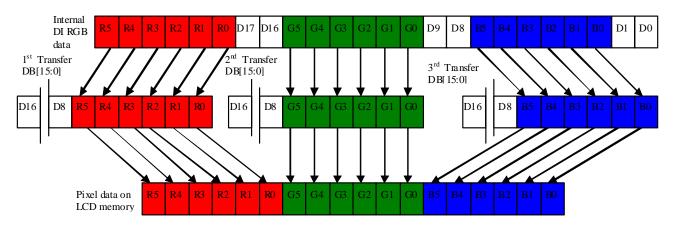

Figure 10 shows the data format of the RGB565 LCD system interface.

Figure 10. RGB565 16 Bit Data Bus, 1 Transfer Per Pixel System Interface Data Format

Now, suppose that this same LCD also supports RGB666 and an image is created based on this pixel depth. It is evident that all the RGB data cannot be sent through the 16-bit data bus by using only one transfer (i.MX31 data bus is 18-bit width maximum, but currently only 16 bits are used because LCD supports only 16-bit data transfer). For example, send all the red and green components in the first transfer and then send the remaining two blue bits in the following transfer. Then, in the next transfer start over with the next pixel.

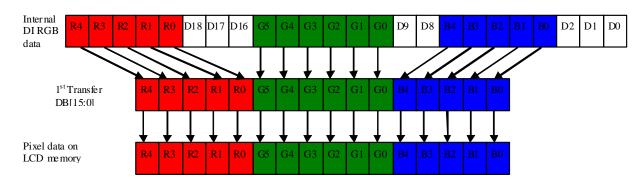

Figure 11 shows the data format of the RGB666 LCD system interface.

Figure 11. RGB666 16 Bit Data Bus, 2 Transfers Per Pixel System Interface Data Format

However, the LCD can request for a different system interface data format, where the dummy data has to be sent in the first transfer and not in the second. Also, R5 and R4 must be placed in the most significant bit (msb) of the data bus instead of the least significant bit (lsb).

**Asynchronous Display Interfaces**

Figure 12 shows the data format of the RGB666 LCD system interface.

Figure 12. RGB666 16 Bit Data Bus, 2 Transfers Per Pixel System Interface Data Format

Though Figure 11 and Figure 12 give the best performance regarding data transfers between the i.MX and LCD, there are also other means to send this data. For example, each color component can be sent in a single data transfer. First, send the six bits of the red component, then send the six green bits in the next transfer, and then in the third transfer, send the remaining five bits of the blue component. After this transfer, the process begins with the next pixel data.

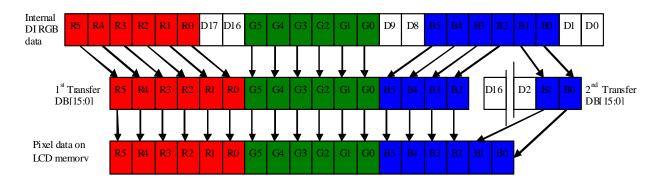

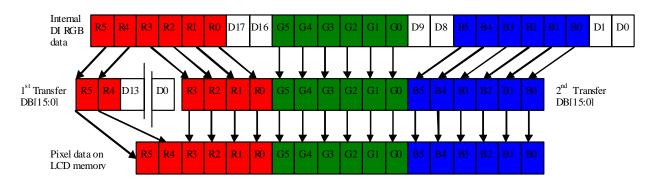

Figure 13 shows the data format of the RGB666 LCD system interface.

Figure 13. RGB666 16 Bit Data Bus, 3 Transfers Per Pixel System Interface Data Format

The same LCD supports more than one color depth (bits per pixel) and more than one system interface data format. The system interface is selected using a specific pin or register configuration. If the system interface is selected by a register, the question that arises is, how the data is sent before selecting the system interface. This is possible because command and pixel data transfer system interface are not always the same. The command interface can perform only one transfer per command, but the data transfer system interface can perform two or three transfers per pixel.

# 3.6 LCD Panels Supported by the i.MX31

The i.MX31 can handle up to four displays at the same time.

Table 6 lists the various types of displays that are handled by the display controllers.

| Display | Display Type | Interface                                         |

|---------|--------------|---------------------------------------------------|

| DISP0   | Asynchronous | Parallel interface only                           |

| DISP1   | Asynchronous | Serial and parallel interface                     |

| DISP2   | Asynchronous | Serial and parallel interface                     |

| DISP3   | Synchronous  | RGB interface (HSYNC, VSYNC, PIXCLK, upto RGB666) |

#### Table 6. Display Controllers and their Interfaces

# 3.6.1 Asynchronous Display Interface

The i.MX31 ADC can be configured to handle several types of devices and interfaces. The ADC is able to support up to three smart displays simultaneously with time multiplexed access. The DISP1 and DISP2 provide parallel and serial display interfaces while DISP0 provides only the parallel interface.

The interfaces supported by the ADC are as follows:

- System-80 interface

- Type 1 (sampling with the chip select signal) with or without byte enable signals

- Type 2 (sampling with the read and write signals) with or without byte enable signals

- System 68 K interface

- Type 1 (sampling with the chip select signal) with or without byte enable signals

- Type 2 (sampling with the read and write signals) with or without byte enable signals

- Serial interfaces

- 3-wire (with bidirectional data line)

- 4-wire (with separate data input and output lines)

- 5-wire type 1 (with sampling RS by the serial clock)

- 5-wire type 2 (with sampling RS by the chip select signal)

For more details, refer to the Image Processing Unit chapter of the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM).

For parallel interfaces, the data bus is time multiplexed with DISP3 (synchronous interface) and with the other parallel asynchronous interfaces. If there is a synchronous panel in the system, the asynchronous displays can be accessed only when the i.MX31 does not send any data to the dumb display (implies back and front porches). Based on this, it is observed that the bandwidth for parallel asynchronous LCDs are limited by the synchronous panel frame rate, back porch, and front porch (both horizontal and vertical). When the Synchronous Display Controller (SDC) or ADC communicates with one of the four displays through the parallel interface, the Micro Controller Unit (MCU) is allowed to access another display through the serial interface simultaneously.

The i.MX31 is able to support a wide variety of system data interfaces. In general, for System-80 type 2, the i.MX31 supports data bus, whose width varies from 8 to 18 lines (DISPB\_DATA [17:0]). The internal Display Interface (DI) format for data and command is a 24-bit word which is divided into three byte components (for a 16-bit word, eight zeros are added to the MSB from the ADC). Because of this, it is

#### Asynchronous Display Interfaces

always better to assume that the RGB888 is available internally and also assume that there are 24 bits available for commands, even when the bits can be masked to 8 or 16 bits. This word can be either as an output or input in one, two, or three of the display clock cycles. Due to this, the ADC is able to provide the outputs—RGB565, RGB666, and RGB888 color depths and few other variations of color, which fits in the 24 bits. Another important feature of i.MX31 is that it has a separate system transfer configuration for both commands and data.

It is important to mention the registers that are used to configure the system interface. For DISPO, the registers used for data mapping are:

- DI\_DISP0\_DB0\_MAP

- DI\_DISP0\_DB1\_MAP

- DI\_DISP0\_DB2\_MAP

- DI\_DISP\_ACC\_CC

For command mapping, the registers used are:

- DI\_DISP0\_CB0\_MAP

- DI\_DISP0\_CB1\_MAP

- DI\_DISP0\_CB2\_MAP

- DI\_DISP\_ACC\_CC

DISPX\_IF\_CLK\_CNT\_Y 0

For more details, refer to the Image Processing Unit chapter of the *MCIMX31 and MCIMX31L Multimedia* Applications Processors Reference Manual (MCIMX31RM).

The examples available in Figure 10 to Figure 13 can be reviewed using proper values to gain more clarity.

Table 7 shows the i.MX31 register values for a RGB565 transfer per pixel system interface.

|             | OFFS0 | OFFS1 | OFFS2 | М7 | M6 | M5 | M4 | M3 | M2 | M1 | MO |

|-------------|-------|-------|-------|----|----|----|----|----|----|----|----|

| Byte2 Red   | 15    | 0     | 0     | 3  | 3  | 3  | 0  | 0  | 0  | 0  | 0  |

| Byte1 Green | 10    | 0     | 0     | 3  | 3  | 0  | 0  | 0  | 0  | 0  | 0  |

| Byte0 Blue  | 4     | 0     | 0     | 3  | 3  | 3  | 0  | 0  | 0  | 0  | 0  |

Table 7. i.MX31 Register Values for 16 Bit Data Interface RGB565 1 Transfer Per Pixel

The OFFS1 and OFFS2 columns are set to 0 because the data is packed and sent in a single transfer and therefore, no data is sent in the second or third transfer. The OFFS0 determines how the color components are ordered in the first transfer (clock cycle). Here, the MSB of blue component is located in D4 (five bits), MSB of green component is located in D10 (6 bits) and MSB of red component is located in D15 (five bits). Since RGB565 is used, masking can reflect the color depth by specifying which is the MSB (not masked). The M5-M7 columns are always masked (3 implies masked) for red and blue components (five bits) and for the green component, only the M7 and M6 columns are masked (six bits). The M0-M4 columns in the red and blue components and the M0-M5 columns in the green component are filled with zeros because the data has to be enabled in the first clock cycle. The DISPX\_IF\_CLK\_CNT\_Y row is set

NP

to 0 (display clock cycles - 1) because only one transfer per pixel is used and therefore, only one clock cycle is required.

#### NOTE

X in DISPX\_IF\_CLK\_CNT\_Y can be 0, 1, or 2 depending on which display is selected, and Y can be C (command mapping) and D (data mapping).

Table 8 shows the i.MX31 register values for the RGB666 two transfer per pixel system interface.

Table 8. i.MX31 Register Values for 16 Bit Data Interface RGB666 2 Transfers Per Pixel

|                    | OFFS0 | OFFS1 | OFFS2 | M7 | M6 | M5 | M4 | M3 | M2 | M1 | МО |

|--------------------|-------|-------|-------|----|----|----|----|----|----|----|----|

| Byte2 Red          | 15    | 0     | 0     | 3  | 3  | 0  | 0  | 0  | 0  | 0  | 0  |

| Byte1 Green        | 9     | 0     | 0     | 3  | 3  | 0  | 0  | 0  | 0  | 0  | 0  |

| Byte0 Blue         | 3     | 5     | 0     | 3  | 3  | 0  | 0  | 0  | 0  | 1  | 1  |

| DISPX_IF_CLK_CNT_Y | 1     |       |       |    |    |    |    |    |    |    |    |

In this example, two transfers are required and so DISPX\_IF\_CLK\_CNT\_Y is set to one (number of clock cycles - 1). Using OFFS0, the first cycle is set up, where the red (six bits) and green (six bits) components are sent and hence, the red MSB is on D15 and the green MSB is on D9. Also, part of the blue component is sent in the first transfer (four MSB bits) and hence, the blue MSB is on D3. In the second transfer, only the remaining bits of the blue component is sent. Therefore, OFFS1 column contains only the blue offset, which is placed on D5, so that B0 and B1 are placed in the LSB. The M6 and M7 columns are masked for all colors (bytes), which imply that all color components are of six bits width. Using 0 or 1 in masks is used to specify whether the bits are in the first cycle (0 = first transfer) or second cycle (1 = second transfer).

Table 9 shows the i.MX31 register values for the RGB666 two transfer per pixel system interface.

|                    | OFFS0 | OFFS1 | OFFS2 | M7 | M6 | M5 | M4 | M3 | M2 | M1 | МО |

|--------------------|-------|-------|-------|----|----|----|----|----|----|----|----|

| Byte2 Red          | 15    | 17    | 0     | 3  | 3  | 0  | 0  | 1  | 1  | 1  | 1  |

| Byte1 Green        | 0     | 11    | 0     | 3  | 3  | 1  | 1  | 1  | 1  | 1  | 1  |

| Byte0 Blue         | 0     | 5     | 0     | 3  | 3  | 1  | 1  | 1  | 1  | 1  | 1  |

| DISPX_IF_CLK_CNT_Y | 1     |       |       |    |    |    |    |    |    |    |    |

Table 9. RGB666 16 Bit Data Bus, 2 Transfers Per Pixel System Interface Data Format

This example also requires two transfers and therefore, DISPX\_IF\_CLK\_CNT\_Y is set to one. Since RGB666 is used, M6 and M7 columns must be masked (3) to indicate the color depth. In the first transfer, only the two MSB of the red component are sent and so, red OFFS0 is 15. For the second transfer (OFFS1), the blue component starts at D5 and the green component at D11, but the remaining red information has an offset of 17 because the four least significant bits of the red component are sent using the lines, D12-D15. The masks determine that only R5 and R4 have to be sent in the first transfer and all the other bits are sent in the second cycle.

Asynchronous Display Interfaces

Table 10 shows the i.MX31 register values for the RGB666 three transfer per pixel system interface.

|                    | OFFS0 | OFFS1 | OFFS2 | M7 | M6 | M5 | M4 | М3 | M2 | M1 | МО |

|--------------------|-------|-------|-------|----|----|----|----|----|----|----|----|

| Byte2 Red          | 5     | 0     | 0     | 3  | 3  | 0  | 0  | 0  | 0  | 0  | 0  |

| Byte1 Green        | 0     | 5     | 0     | 3  | 3  | 1  | 1  | 1  | 1  | 1  | 1  |

| Byte0 Blue         | 0     | 0     | 5     | 3  | 3  | 2  | 2  | 2  | 2  | 2  | 2  |

| DISPX_IF_CLK_CNT_Y | 2     |       |       | •  | •  |    |    |    | •  |    |    |

Table 10. RGB666 16 Bit Data Bus, 3 Transfers Per Pixel System Interface Data Format

The DISPX\_IF\_CLK\_CNT\_Y row indicates that three transfer per pixel are required and masks determine that the RGB666 is used. Here, the red component is sent in the first transfer (0), green component in the second transfer (1), and blue component in the third transfer (2). The MSB's of all the components are placed on D5, and this is reflected in the offsets. (OFFS0 for red, OFFS1 for green, and OFSS2 for blue)

The same concept can be applied to the command interface by considering the byte0, byte1, and byte2 store command information instead of color information. For more details, refer to the Bus Mapping Unit section in the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM).

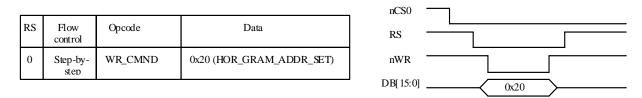

# 3.7 Command and Template Mode

For asynchronous panels, the two types of display accesses for registers and data are—the command and template mode. The command mode is used for initialization process and the template mode is used for the frame buffer update. Once the interfaces have been configured, both modes generate all the signals to write data or send commands to the smart panel.

# 3.7.1 Command Mode

The command mode is used for the initialization routine. In this mode, the asynchronous command interface is set up with the desired characteristics by using the DI\_DISP\_LLA\_CONF register:

- Display Interface (DISP0, DISP1, or DISP2)

- Data or command (RS polarity)

Write the command or data to be sent to the smart panel in the DI\_DISP\_LLA\_DATA register. With these two actions, the ADC sends the data or command from the DI\_DISP\_LLA\_DATA register to the LCD in one, two, or three transfers according to the system command configuration that is described in the DI\_DISP0\_CB0\_MAP, DI\_DISP0\_CB1\_MAP, DI\_DISP0\_CB2\_MAP, and DI\_DISP\_ACC\_CC registers (offsets and masks). If another command or data with the same configuration needs to be sent, write the command or data again on the DI\_DISP\_LLA\_DATA register.

The WINCE600 BSP provides a function where the low-level aspects such as DI\_DISP\_LLA\_CONF and DI\_DISP\_LLA\_DATA are encapsulated in the ADCWriteCommand() function. It is important to mention that the offsets and masks for the command system interface must be configured before using the ADCWriteCommand() function. See the following example:

Consider an interface where either the data (RS = 1) or command (RS = 0) is of 16-bit width. While using an interface, first send the register address (command) and then the register contents (data) in order to configure the register. Also, assume that the DISPO 16-bit width command is used with only one transfer per command.

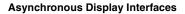

Figure 14 shows the 16 bit command one transfer per command system interface data format.

Figure 14. 16 Bit Command 1 Transfer Per Command System Interface Data Format

The following configuration shows that the DI\_DISP\_LLA\_DATA byte0 and byte1 are sent to the display during the first clock cycle. Byte2 is ignored because there is only one transfer per command (DISP0\_IF\_CLK\_CNT\_C=0). Configure the interface before writing data to DI\_DISP\_LLA\_DATA.

For more details, refer to the Memory Map and Register Definition section in the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM).

Table 11 shows the data format of the 16 bit command one transfer per command system interface.

|                    | OFFS0 | OFFS1 | OFFS2 | М7 | M6 | М5 | М4 | М3 | M2 | M1 | MO |

|--------------------|-------|-------|-------|----|----|----|----|----|----|----|----|

| Byte2              | 0     | 0     | 0     | 3  | 3  | 3  | 3  | 3  | 3  | 3  | 3  |

| Byte1              | 15    | 0     | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Byte0              | 7     | 0     | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| DISP0_IF_CLK_CNT_C | 0     |       |       |    |    |    |    |    |    |    |    |

Table 11. 16 Bit Command one Transfer Per Command System Interface (Refer Figure 14)

## 3.7.2 Template Mode

The template mode is used for sending pixels to the LCD. Once the LCD is initialized, the display data on the smart panel memory can be considered as an external memory where the i.MX31 display driver modifies either some part of the content or the complete frame buffer. In this way, the driver attempts to access only that memory and the ADC sets up all the signals in order to write those pixels in the smart panel memory.

A template is a micro program that is executed every time when a data burst has to be written to or read from a smart display. A typical structure of the template includes the following parts:

- Sending a pre-command sequence to the display.

- Sending an address to the display.

#### Asynchronous Display Interfaces

- Waiting for acknowledgement from the display or for the given number of display clocks and waiting is required only for the read access.

- Sending a data sequence to the display or receiving a data sequence from the display. This step is repeated when addressing is sequential (refer to the Sequential Addressing Access section of the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM).

- Sending a post-command sequence to the display.

- Depending on the access type (read or write) and access, the template structure can be varied. For the sequential access (refer to the Sequential Addressing Access section of the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM), both commands and addresses are not sent to the display. Therefore, templates are not used for the sequential access. Two templates—read and write exists for each of the three displays and the maximal template length is 32 commands.

There is no standard that specifies how this transfer is going to happen. For example, in the GiantPlus GPM722A0 if the frame buffer contents has to be modified, send the X (pixel offset) and Y (line) position of the pixel to the smart panel, by writing the addresses in the Graphics RAM (GRAM) horizontal (R20h) and GRAM vertical address (R21h) registers, and then write the pixel contents in the R22h register (write data to GRAM). After this operation, if the display interface writes again on the R22h register, the smart panel stores the RGB data in the next pixel location and so on.

Even when the addresses of X and Y are set every time a pixel is referenced, the i.MX31 is able to distinguish the continuous access and run only the address set up (R20h, R21h, and R22h). When a non-sequential access is referenced, the functionality needs to be configured in the i.MX31 IPU's ADC\_CONF register. This helps to reduce the transfer per pixel in the display interface. For more details, refer to the *MCIMX31 and MCIMX31L Multimedia Applications Processors Reference Manual* (MCIMX31RM).

# 3.7.2.1 Sending Pre-Command Sequence to the Display

There is no pre-command sequence for GiantPlus GPM722A0.

## 3.7.2.2 Sending an Address to the Display

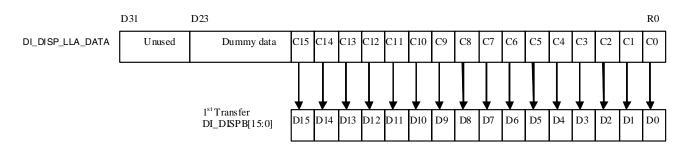

The addresses to the GRAM horizontal/vertical address Set (R20h, R21h) registers need to be sent and the template command for this is as follows:

1. Send the GRAM horizontal address set command to the register (R20h).

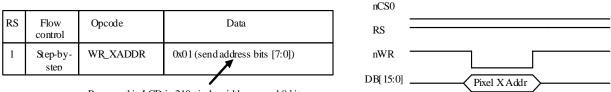

Figure 15 shows the GRAM horizontal address set command (R20h).

Figure 15. Horizontal Address Set Command

2. Send the contents of the GRAM horizontal address to the register.

Figure 16 shows the contents of the GRAM horizontal address.

Because this LCD is 240 pixels width we need 8 bits for X Addresses.

#### Figure 16. Contents of the GRAM Horizontal Address

3. Send the GRAM vertical address set command to the register (R21h).

Figure 17 shows the GRAM vertical address set command.

|    | -                |         |                         | nCS0      |  |

|----|------------------|---------|-------------------------|-----------|--|

| RS | Flow<br>control  | Opcode  | Data                    | RS        |  |

| 0  | Step-by-<br>step | WR_CMND | 0x21(VER_GRAM_ADDR_SET) | nWR       |  |

|    |                  | I       |                         | DB[ 15:0] |  |

#### Figure 17. Vertical Address Set Command

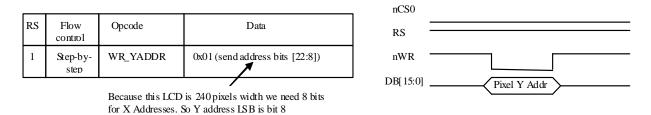

4. Send the contents of the GRAM vertical address to the register.

Figure 18 shows the contents of the GRAM vertical address.

#### Figure 18. Contents of the GRAM Vertical Address

5. Send the write data to the GRAM command (R22h).

Figure 19 shows sending of the write data to the GRAM command.

|    |                  |         |                       | nCS0     |      |

|----|------------------|---------|-----------------------|----------|------|

| RS | Flow<br>control  | Opcode  | Data                  | RS       |      |

| 0  | Step-by-<br>step | WR_CMND | 0x22(WR_DATA_TO_GRAM) | nWR      |      |

|    |                  |         | <b>L</b>              | DB[15:0] | 0x22 |

#### Figure 19. Send Write Data to the GRAM Command

**Display Configuration in WINCE 6.0**

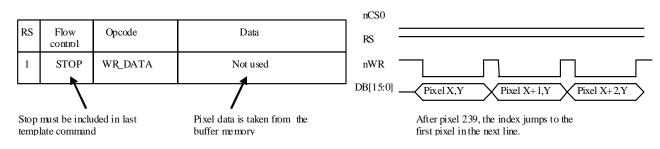

# 3.7.2.3 Sending a Data Sequence to the Display

Finally, send the pixel information to the panel.

Figure 20 shows sending of the pixel information to the panel.

Figure 20. Sending Pixel Information to the Panel

# 3.7.2.4 Sending a Post-Command Sequence to the Display

There is no post-command sequence for GiantPlus GPM722A0.

It is observed that nearly six transfers are required for loading the initial pixel data, but if the sequential access is used correctly, the total number of transfers can be reduced to one transfer per pixel.

# 4 Display Configuration in WINCE 6.0

LCD support is one of the most important features for any multimedia device. Display support enables the device to have a Graphical user interface (GUI) and the possibility to become an entertainment artifact.

The graphic context is composed of several layers where the i.MX31 display interface is the final part in the abstraction. All the ADC and display interface characteristics that are reviewed in previous sections describe only how the i.MX31 sends the frame buffer to the panel. However, it is important to know who is going to create the frames that need to be sent to the panel. If the screen is refreshed 60 times per second (60 Hz), every line and every single pixel has to be created to maintain the coherence of the graphic context.

The i.MX31 PDK BSP bases its display driver on the Display Driver Interface (DDI) defined by Microsoft<sup>®</sup> for all WINCE600 devices. Implementing a driver using this model ensures the compatibility of the hardware with the operating system. In other words, once WINCE is loaded and if the driver is created using the MS model, the operating system handles the graphic context, providing all frames.

# 4.1 WINCE600 Display Driver Development Concepts

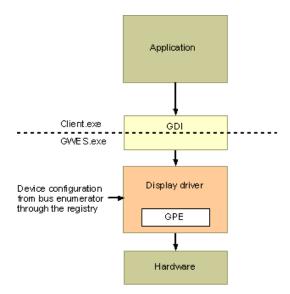

Display drivers are loaded and called directly by the graphics, windowing, and event subsystem, called Gwes.exe. Drivers are most commonly written using a layered architecture because of the number of hardware-independent operations.

The Graphics Primitive Engine (GPE) library handles the default drawing, acting as the display driver's Model Device Driver (MDD) upper layer.

The user develops the hardware-specific code that corresponds to the display drivers lower layer, called the Platform-Dependent Driver (PDD).

Table 12 shows the elements that constitute the Windows CE graphics pipeline.

| Element     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application | The application can be simple such as a Hello World application or complex such as a three-dimensional engineering application.<br>Whichever it is, the application calls GDI functions. Coredll.dll exposes these functions.                                                                                                                                                                                                                                                                                             |

| Coredll.dll | The major set of functions is exposed through a single DLL, called CoredlI.dll.<br>In most cases, this library does not perform the work. Instead, the library packages the parameters for the<br>function call and then triggers a Local Procedure Call (LPC) to another process.<br>The specific process depends on the function call. All drawing and windowing calls are sent to Gwes.exe.                                                                                                                            |

| Gwes.exe    | The Graphics, Windowing, and Events Subsystem (GWES) is responsible for all graphical output and all interactions with the user.<br>The drivers that reside in the GWES address space include display drivers, printer drivers, keyboard drivers, mouse drivers, and touch screen drivers.                                                                                                                                                                                                                                |

| Ddi.dll     | The default name for the display driver is Ddi.dll. As with most DLLs, Ddi.dll communicates through exported functions.<br>Ddi.dll exports only the DrvEnableDriver function, which returns a pointer to an array of 27 function pointers to the caller. When GWES requires a display driver, it calls one of the 27 functions.<br>Writing a device driver involves writing the code for the 27 functions.<br>Three of these functions are specific to printer drivers, which leaves 24 for the display driver developer. |

| Hardware    | The graphic pipeline ends at the hardware. The display driver communicates to the hardware using the mechanism required by the hardware.<br>This process typically involves a combination of memory-mapped video buffers and I/O registers.                                                                                                                                                                                                                                                                               |

#### Table 12. Elements of Windows CE Graphics Pipeline

Figure 21 shows the Windows CE graphics architecture.

Figure 21. Windows CE Graphics Architecture

**Display Configuration in WINCE 6.0**

More details can be found under Display Drivers (Developing a Device Driver > Windows CE Drivers > Display Drivers) topic of Platform Builder for Microsoft<sup>®</sup> Windows CE 5.0 help.

It is important to mention that developing a WINCE Display driver from scratch implies a considerable effort and knowledge, specially the WINCE architecture. Freescale provides the i.MX31 display driver for asynchronous displays in the WINCE600 BSP. The i.MX31 Windows CE 6.0 BSP display driver is based on the Microsoft<sup>®</sup> DirectDraw Graphics Primitive Engine (DDGPE) classes and supports the Microsoft<sup>®</sup> DirectDraw interface. This driver combines the functionality of a standard LCD display with DirectDraw support and the display driver interfaces with IPU. This driver supports more than one panel which can be selected by using the Windows Register. The support for a new asynchronous panel can be added using the procedure described in the following section.

# 4.2 Adding Support for a New LCD Panel

The following sections describes the procedure used to add the support for a new asynchronous panel.

# 4.2.1 Identify LCD Characteristics and Timing

To add the support for a new System-80 smart panel for the i.MX31 BSP, ensure that this panel is compatible with the i.MX31. The panel must have the following interface characteristics:

- Asynchronous display (smart display)

- System-80 Type 2 (sampling with the read and write signals) interface

- Resolution not greater than SVGA

Once a compatible LCD panel is selected, it is important to find the timing and system data interface characteristics of the display. Following tables are related to the GPM722A0 display.

Table 13 shows the artifacts of the GPM722A0 display.

| Parameter                         | Symbol | Value                                                                            |

|-----------------------------------|--------|----------------------------------------------------------------------------------|

| Display Interface                 | DI     | System-80 Type 2 (sampling with the read and write signals)                      |

| Burst Mode                        | BRSTM  | Parallel interface burst mode                                                    |

| Data Polarity                     | DEP    | Straight                                                                         |

| Chip Select Polarity              | CSPOL  | Active low                                                                       |

| Register Select (PAR_RS) Polarity | RSPOL  | Straight polarity                                                                |

| Write Signal Polarity             | WRPOL  | Active low                                                                       |

| Read Signal Polarity              | RDPOL  | Active low                                                                       |

| Color Depth (bits per pixel)      | BPP    | 16(RGB565)/18(RGB666) bits (configurable)                                        |

| System interface data format      | DFMT   | One or two transfer per pixel depending on color depth, one transfer per command |

| LCD width                         | HDISP  | 240 pixels                                                                       |

| LCD height                        | VDISP  | 320 lines                                                                        |

#### Table 13. Artifacts of the GPM722A0 Display

Table 14 also shows the artifacts of the GPM722A0 display.

| Parameter              | Symbol            | Minimum | Туре | Maximum | Unit |

|------------------------|-------------------|---------|------|---------|------|

| Write Cycle Time       | t <sub>CYCW</sub> | 100     | _    | —       | ns   |

| Read Cycle Time        | t <sub>CYCR</sub> | 300     | _    | —       | ns   |

| Write Low Pulse Width  | t <sub>WL</sub>   | 50      | _    | 500     | ns   |

| Write High Pulse Width | t <sub>WH</sub>   | 50      | _    | —       | ns   |

| Read Low Pulse Width   | T <sub>RL</sub>   | 150     | _    | —       | ns   |

| Read High Pulse Width  | T <sub>RH</sub>   | 150     | _    | —       | ns   |

| Setup Time for Write   | T <sub>DCSW</sub> | 10      | _    | —       | ns   |

| Setup Time for Read    | T <sub>DCSR</sub> | 5       | _    | —       | ns   |

| Write Signal Fall Time | T <sub>WF</sub>   | _       | _    | 25      | ns   |

| Write Signal Rise Time | T <sub>WR</sub>   | _       | _    | 25      | ns   |

| Read Signal Fall Time  | T <sub>RF</sub>   | _       | _    | 25      | ns   |

| Read Signal Rise Time  | T <sub>RF</sub>   | _       | _    | 25      | ns   |

| Hold Time for Write    | T <sub>DCHW</sub> | 15      | _    | —       | ns   |

| Hold Time for Read     | T <sub>DCHR</sub> | 5       | _    | —       | ns   |

| Write Data set up Time | T <sub>DS</sub>   | 10      | _    | —       | ns   |

| Write Data Hold Time   | T <sub>DH</sub>   | 15      | —    | —       | ns   |

| Read Data Delay Time   | T <sub>RACC</sub> | —       | —    | 100     | ns   |

| Read Data Hold Time    | T <sub>ROH</sub>  | 5       | _    | —       | ns   |

Table 14. Artifacts of the GPM722A0 Display

**Note:** Check if these values are same as the PANEL\_INFO structure.

More details on how to deduce these values from the LCD data sheet can be found in the Section 1, "Overview of i.MX31 Display," to Section 3, "Asynchronous Display Interfaces," of this application note.

# 4.2.2 i.MX31 WINCE600 PDK LCD Driver Initialization Flow

The following snippet represents the WINCE600 PDK LCD driver initialization flow:

```

NP

```

#### **Display Configuration in WINCE 6.0**

```

+ Configure ADC and DI: IPU_CONF, IPU_CHA_DB_MODE_SEL, IPU_CHA_CUR_BUF,

DI_DISPx_DB0_MAP, DI_HSP_CLK_PER, ADC_CONF

+ _init_dma()

+ CreateTemplate()

+ ReadTemplateMemory()

+ ADCSetSrcBuffer()

+ BSPEnableLCD(eIPU_ADC) - GiantPlusEnableLCD()

+ PmicVoltageRegulatorOn(VMMC1); VMMC1 = 2.8 V

+ PmicVoltageRegulatorOn(VGEN); VGEN = 2.8 V

+ BSPDisplayIOMUXEnable() - GiantPlusDisplayIOMUXEnable()

+ Configure LCD pins: LD0-17, LCS0, PAR_RS, WRITE, READ, etc)

+ BSPResetLCD(eIPU ADC) - GiantPlusResetLCD()

+ LCD_RESET_GPIO_PIN=0

+ Sleep(3000)

+ LCD_RESET_GPIO_PIN=1

+ ADCEnableModules()

+ Enable DI

+ Enable ADC

+ Startup Command Sequence

ADCWriteCommand() - GiantPlusWriteRegister(

+ EnableADC()

+ Enable DI

+ Enable ADC

+ DDIPU::AdvertisePowerInterface()

```

The LCD driver is initialized in the DDIPU\_SDC::DDIPU\_SDC() function. The video memory size is not taken from the registry, because this value is a constant (IMAGE\_WINCE\_IPU\_RAM\_SIZE) declared in the image\_cfg.hc file. Panel type, rotation parameters, pixel depth, and TV modes supported by the platform are extracted from the registry (platform.reg file). Based on the selected panel, the driver notifies the WINCE display properties such as width, height, bits per pixel, and so on. The GPEMode data is automatically set by using the PANEL\_INFO structure of the current panel. With this information, WINCE graphic context creates the frame buffers in the width, height, and format required by the LCD, which is to be displayed on the screen. The information regarding the GPEMode must also be modified to complete the support for the new LCD. The width and height must be provided in the natural orientation of the LCD.

The next step is the hardware initialization. Here, the IPU registers are configured to enable the ADC and DI for working with the selected panel. The LCD timing features are not stored in registers, but are located in the array PANEL\_INFO g\_ADCPanelArray[numPanel] placed in the

WINCE600\PLATFORM\iMX313DS\SRC\DRIVERS\IPU\ADC\adc.c file. So, to add the support for a new panel, this array must be updated by adding another PANEL\_INFO structure with the panel timing information. The IDMAC ADC channels are configured, and the IOMUX is also configured to enable the LCD pin interface (LD0-LD17, LCS0, PAR\_RS, WRITE, READ, and so on). Then using bspdisplay.cpp, the driver configures the specific LCD panel pins for initialization which includes reset and other enable pins that are required. At the end of the process, the power levels for LCD are enabled, the panel is reset and all initialization commands are sent to the LCD panel.

# 4.2.3 i.MX31 WINCE600 PDK LCD Display Interface Related Files

The files related to the i.MX31 WINCE600 PDK LCD display are contained in the following locations:

WINCE600\PLATFORM\iMX313DS\SRC\INC\adc.h WINCE600\PLATFORM\iMX313DS\SRC\DRIVERS\IPU\ADC\adc.c WINCE600\PLATFORM\iMX313DS\SRC\DRIVERS\IPU\DISPLAY\COMMON\ddipu.cpp

```

WINCE600\PLATFORM\iMX313DS\SRC\DRIVERS\IPU\DISPLAY\COMMON\ddipu_cursor.cpp

WINCE600\PLATFORM\COMMON\SRC\SOC\FREESCALE\MXARM11_FSL_V1\IPU\INC\ipu.h

WINCE600\PLATFORM\iMX313DS\SRC\DRIVERS\IPU\DISPLAY\DLL\bspdisplay.cpp

WINCE600\PLATFORM\iMX313DS\FILES\platform.reg

WINCE600\PLATFORM\COMMON\SRC\SOC\FREESCALE\PMIC\MC13783_FSL_V1\INC\pmic_regulator.h

WINCE600\PLATFORM\iMX313DS\SRC\INC\bsp_cfg.h

```

## 4.2.4 i.MX31 PDK LCD Structures

It is important to understand how and where the information related to the LCD panel settings (see Section 4.2, "Adding Support for a New LCD Panel,") are stored because the communication channel is used to inform the Asynchronous LCD driver about the settings for the new LCD display. PANEL\_INFO, which contains ADC\_IPU\_DI\_SIGNAL\_CFG and SDC\_IPU\_DI\_SIGNAL\_CFG is the structure that needs to be changed in order to add the support for a new panel. The g\_ADCPanelArray[] array in adc.c file is the global array that stores the PANEL\_INFO for all supported smart displays (Toshiba, Epson, and so on). To modify the driver, it is recommended to add a new entry at the end of the structure with the new PANEL\_INFO structure.

## 4.2.4.1 PANEL\_INFO

PANEL\_INFO is the main structure for the LCD timing and features. It also contains two structures related to the signal polarity. The ADC\_IPU\_DI\_SIGNAL\_CFG is used for asynchronous displays. Alternatively, the SDC\_IPU\_DI\_SIGNAL\_CFG describes the polarities and characteristics of the RGB interface.

```

struct PANEL_INFO_ST {

PUCHAR NAME;

IPU_PANEL_TYPE TYPE;

IPU_PIXEL_FORMAT PIXEL_FMT;

INT MODEID;

INT WIDTH;

INT HEIGHT;

INT FREQUENCY;

INT VSYNCWIDTH;

INT VSTARTWIDTH;

TNT VENDWIDTH;

INT HSYNCWIDTH;

INT HSTARTWIDTH;

INT HENDWIDTH;

INT RD_CYCLE_PER; // in ns

INT RD_UP_POS; // in ns

INT RD_DOWN_POS; // in ns

INT WR_CYCLE_PER; // in ns

INT WR_UP_POS; // in ns

INT WR_DOWN_POS; // in ns

INT PIX_CLK_FREQ; // in Hz

INT PIX_DATA_POS; // in ns

ADC_IPU_DI_SIGNAL_CFG ADC_SIG_POL;

SDC_IPU_DI_SIGNAL_CFG SDC_SIG_POL;

};

typedef struct PANEL_INFO_ST PANEL_INFO;

```

Table 15 provides the description of each element in the PANEL\_INFO structure.

| Data Type        | Variable Name | Description                          | Symbol            | Unit  |

|------------------|---------------|--------------------------------------|-------------------|-------|

| PUCHAR           | NAME          | Name of the panel                    | —                 | —     |

| IPU_PANEL_TYPE   | TYPE          | Index of the panel type <sup>1</sup> | —                 | —     |

| IPU_PIXEL_FORMAT | PIXEL_FMT     | Pixel format <sup>2</sup>            | BPP               | bit   |

| INT              | MODEID        | Mode ID <sup>3</sup>                 | _                 | ns    |

| INT              | WIDTH         | Active frame width                   | VDISP             | pixel |

| INT              | HEIGHT        | Active frame height                  | HDISP             | line  |

| INT              | FREQUENCY     | Refresh rate                         | FV                | Hz    |

| INT              | VSYNCWIDTH    | Not used by smart panels             | _                 | _     |

| INT              | VSTARTWIDTH   | Not used by smart panels             | _                 | _     |

| INT              | VENDWIDTH     | Not used by smart panels             | _                 | _     |

| INT              | HSYNCWIDTH    | Not used by smart panels             | _                 | _     |

| INT              | HSTARTWIDTH   | Not used by smart panels             | _                 | _     |

| INT              | HENDWIDTH     | Not used by smart panels             | _                 | _     |

| INT              | RD_CYCLE_PER  | Read cycle period                    | t <sub>CYCR</sub> | ns    |

| INT              | RD_UP_POS     | Read up position                     | T <sub>RH</sub>   | ns    |

| INT              | RD_DOWN_POS   | Read down position                   | T <sub>RL</sub>   | ns    |

| INT              | WR_CYCLE_PER  | Write cycle period                   | t <sub>CYCW</sub> | ns    |

| INT              | WR_UP_POS     | Write up position                    | t <sub>WH</sub>   | ns    |

| INT              | WR_DOWN_POS   | Write down position                  | t <sub>WL</sub>   | ns    |

| INT              | PIX_CLK_FREQ  | Pixel clock frequency [4]            | _                 | —     |

| INT              | PIX_DATA_POS  | Pixel data position [5]              | _                 | —     |

#### Table 15. PANEL\_INFO Structure Elements

<sup>1</sup> The enum on this data field is used by adc.c file to distinguish the proper timing settings between the supported displays (LCD, NTSC TV, and PAL TV) when the selected display is being loaded. The *ipu.h* header file contains IPU\_PANEL\_TYPE.

<sup>2</sup> There are three different RGB pixel formats, RGB565, RGB666, and RGB888. By selecting one of these formats, the ADC's interpretation of the frame buffer data can be specified.

<sup>3</sup> For LCD panels, use DISPLAY\_MODE\_DEVICE as MODEID. Two other supported modes are also available, but those values belong to the TV out functionality.

# 4.2.4.2 ADC\_IPU\_DI\_SIGNAL\_CFG

The following snippet represents the bit fields of the ADC display interface signal polarities:

```

// Bitfield of ADC Display Interface signal polarities

typedef struct {

UINT32 DISP_NUM :2;

UINT32 DISP_IF_MODE:2;

UINT32 DISP_PAR_BURST_MODE:2;

UINT32 DATA_POL :1; // true = inverted

```

}

| UINT32 CS_POL :1;      | 17      | true =  | active high             |

|------------------------|---------|---------|-------------------------|

| UINT32 PAR_RS_POL      | :1; //  | true =  | inverse                 |

| UINT32 WR_POL :1       | 1; //   | true =  | active high             |

| UINT32 RD_POL :1;      | //      | true =  | active high             |

| UINT32 VSYNC_POL :     | :1; //  | true =  | active high             |

| UINT32 SD_D_POL :1;    | ; //    | true =  | inverse                 |

| UINT32 SD_CLK_POL :    | :1; //  | true =  | inverse                 |

| UINT32 SER_RS_POL :    | :1; //  | true =  | inverse                 |

| UINT32 BCLK_POL :1;    | ; //    | true =  | inverted                |

| UINT32 Dummy :         | :16; // | Dummy v | variable for alignment. |

| ADC_IPU_DI_SIGNAL_CFG; |         |         |                         |

Table 16 provides the name and description of the ADC display interface bit fields.

#### Table 16. ADC Display Interface Bit Fields

| Offset | Bit-Field Name      | Description                                                   | Symbol |

|--------|---------------------|---------------------------------------------------------------|--------|

| 0      | DISP_NUM            | Display number <sup>1</sup>                                   | —      |

| 2      | DISP_IF_MODE        | Display interface mode <sup>2</sup>                           | —      |

| 4      | DISP_PAR_BURST_MODE | Bust mode for parallel interfaces <sup>3</sup>                | —      |

| 5      | DATA_POL            | Data polarity <sup>4</sup>                                    | DEP    |

| 6      | CS_POL              | Chip select polarity <sup>5</sup>                             | CSPOL  |

| 7      | PAR_RS_POL          | Parallel register strobe (REG/Data) polarity <sup>6</sup>     | RSPOL  |

| 8      | WR_POL              | Write signal polarity <sup>7</sup>                            | WRPOL  |

| 9      | RD_POL              | Read signal polarity <sup>8</sup>                             | RDPOL  |

| 10     | VSYNC_POL           | VSYNC polarity (not used in GPM722A0) <sup>9</sup>            | —      |

| 11     | SD_D_POL            | Data polarity for serial interface (not used in parallel)     | —      |

| 12     | SD_CLK_POL          | Clock polarity for serial interface (not used in parallel)    | —      |

| 13     | SER_RS_POL          | Register polarity for serial interface (not used in parallel) | —      |

| 14     | BCLK_POL            | Burst clock polarity [10]                                     | —      |

| 15     | Dummy               | Dummy data for memory alignment                               | —      |

<sup>1</sup> Display number refers to the i.MX31 display that is used for this interface. For parallel interfaces (System-80 Type 2), DISP0, DISP1, or DISP3 can be used. Since this option is available, DISP0 (IPU\_ADC\_DISPLAY\_0) can be selected.

<sup>2</sup> There are seven different types of interfaces supported by the i.MX31, but this application note uses only the IPU\_DI\_DISP\_IF\_CONF\_IF\_MODE\_SYSTEM80\_TYPE2 (0x01) interface, which is defined in the mxarm11\_ipu.h file.

<sup>3</sup> The burst access mode must be IPU\_DI\_DISP\_IF\_CONF\_PAR\_BURST\_MODE\_BURST\_CS for the GiantPlus GPM722A0.

- <sup>4</sup> Data polarity must be straight (IPU\_DI\_DISP\_SIG\_POL\_DATA\_POL\_STRAIGHT). If required, invert the signals in the data bus (used only for B/W displays).

- <sup>5</sup> When the CS signal goes low to indicate it is active, the polarity of the CS\_POL must be IPU\_DI\_DISP\_SIG\_POL\_CS\_POL\_ACTIVE\_LOW. Active low is the most common configuration for this signal. However, the CS\_POL can also be IPU\_DI\_DISP\_SIG\_POL\_CS\_POL\_ACTIVE\_HIGH at times.

- <sup>6</sup> Setting PAR\_RS\_POL to IPU\_DI\_DISP\_SIG\_POL\_PAR\_RS\_POL\_STRAIGHT implies low for commands and high for data in most common configuration. Additionally, IPU\_DI\_DISP\_SIG\_POL\_PAR\_RS\_POL\_INVERSE can be used if the interface requires a configuration, which is HIGH for commands and LOW for data.

- <sup>7</sup> Write signal polarity is IPU\_DI\_DISP\_SIG\_POL\_CS\_POL\_ACTIVE\_LOW, which implies that the signal is active when it goes low. If the LCD requires, the IPU\_DI\_DISP\_SIG\_POL\_CS\_POL\_ACTIVE\_HIGH can also be used.

# NP

#### **Display Configuration in WINCE 6.0**

- <sup>8</sup> Read signal polarity is IPU\_DI\_DISP\_SIG\_POL\_WR\_POL\_ACTIVE\_LOW, which implies that the signal is active when it goes low. Active Low is the most common configuration for this signal, similar to the Chip select and Write signal. The IPU\_DI\_DISP\_SIG\_POL\_WR\_POL\_ACTIVE\_HIGH configuration is also available for rest of the cases.

- <sup>9</sup> VSYNC\_POL refers to the polarity of VSYNC signal, which is used in some of the smart panels to synchronize the writings. But, in the case of GPM722A0, the module does not provide this signal and therefore, this polarity can be ignored in this driver. Additionally, if this signal is not available, the driver must be configured in order to ignore this synchronization. This is done by setting an environmental variable (BSP\_ADC\_ENABLE\_TEARING\_PREVENTION) in the bsp\_cfg.h header file to false.

## 4.2.4.3 SDC\_IPU\_DI\_SIGNAL\_CFG

The following snippet represents the bit fields of the SDC display interface signal polarities:

```

// Bitfield of SDC Display Interface signal polarities.

typedef struct {

UINT32 DATAMASK_EN:1;

UINT32 CLKIDLE_EN :1;

UINT32 CLKSEL_EN :1;

UINT32 VSYNC_POL

:1;

UINT32 ENABLE POL :1;

UINT32 DATA_POL :1;

// true = inverted

UINT32 CLK_POL

:1;

// true = rising edge

UINT32 HSYNC_POL :1;

// true = active high

UINT32 Dummy

:24;

// Dummy variable for alignment.

} SDC_IPU_DI_SIGNAL_CFG;

```

This structure is not used for asynchronous display panels and therefore, all these bitfields can be set to zero.

## 4.2.4.4 GPEMode

The following code snippet provides the GPEMode structure:

```

// STRUCT GPEMode

11

// This structure describes a display mode.

struct GPEMode

{

int

modeId;

int

width;

int

height;

int.

Bpp;

int

frequency;

EGPEFormat

format;

};

```

The GPEMode structure is used to communicate to the WINCE graphics engine, the size and format of the screen. Using this information, the OS creates the frame in an appropriate size (required by the i.MX31), which is to be processed and sent to the panel using the display interface.

Table 17 provides the description of each element in the GPEMode structure.

| Data Type | Variable Name | Description                      | Symbol | Unit  |

|-----------|---------------|----------------------------------|--------|-------|

| int       | modeld        | Display or TV modes <sup>1</sup> | —      | —     |

| int       | Width         | Active frame width               | VDISP  | pixel |

| int       | Height        | Active frame height              | HDISP  | line  |

| int       | Врр           | Bits per pixel <sup>2</sup>      | BPP    | bit   |

| int       | Frequency     | Screen refresh rate              | FV     | Hz    |

| int       | Format        | EGPEFormat enum <sup>3</sup>     | —      | —     |

#### Table 17. GPEMode Structure Elements

<sup>1</sup> Display mode can be either DISPLAY\_MODE\_DEVICE or DISPLAY\_MODE\_NTSC.

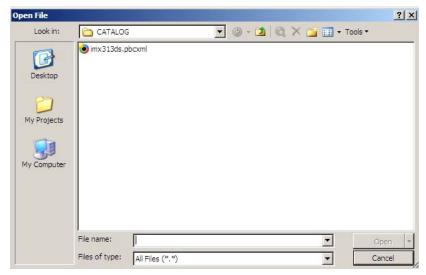

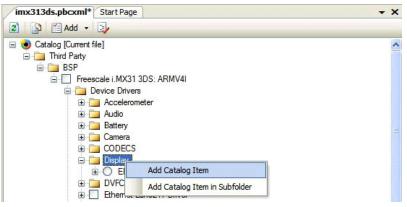

<sup>2</sup> The mode must be set to DISP\_BPP, whose value is 16.