# NXP Semiconductors

**Application Note**

Document Number: AN4770 Rev. 5.0, 12/2017

# Implementing the MC33903/4/5 CAN and LIN system basis chip

# 1 Introduction

This document provides in-depth guidance for module design and development implementing the MC33903/4/5 CAN-LIN System Basis Chip (SBC). This guidance will assist hardware and software engineers to develop safe, reliable, and robust automotive application modules. A detailed description of the SMARTMOS device operation features and their application usage is provided to ease the module's design and development. This specific application note covers the following topics:

- · Device Segmentation

- Supply Voltage

- Embedded Regulators

- Multiplexer

- Serial Peripheral Interface (SPI)

- Configurable I/Os

- SAFE, RST, and INT Safe modes

- CAN and LIN Physical Layers

- Hardware Design

- Crank Pulse Handling

- Extending Current Capability on Vaux

- Programming the SBC

- Debug Mode

- SBC Initialization

- Enhanced Diagnostics

- Advanced WatchdogLow Power Modes

- Secured SPI

- Normal Request, Reset, and Flash Modes

#### **Contents**

| 1 | Introduction        |

|---|---------------------|

| 2 | General information |

| 3 | Device features     |

| 4 | Hardware design     |

| 5 | Programming the SBC |

| 6 | References          |

| 7 | Revision history    |

# 2 General information

# 2.1 MC33903/4/5 at a glance

The MC33903/4/5 System Basis Chip (SBC) is NXP Semiconductors' latest generation of SBCs designed and developed for automotive body multiplexing applications requiring CAN and LIN communication. These products offer enhanced diagnostics for functional safety and optimized multiple low power modes for low module current consumption.

The MC33903/4/5 SBC features NXP's robust CAN and LIN physical layers, which have been approved by multiple automotive Original Equipment Manufacturers (OEMs). These devices also have multiple 5.0 V or 3.3 V embedded regulators, robust I/Os, high accuracy voltage monitoring, multiplexer, fail-safe output, and enhanced SPI communication.

# 2.2 SBC device family concept

## 2.2.1 Device variations

The MC33903/4/5 SBC device family is composed of fourteen different products, which combine one or more transceivers, Low Drop Out (LDO) voltage regulators, I/Os, voltage monitoring, MUX output, and other features as shown on **Table 1**, **Table 2**, and **Table 3**:

Table 1. 33905 device variations - (all devices rated at  $T_A$  = -40 °C TO 125 °C)

| NXP part number     | V <sub>DD</sub> output<br>voltage | LIN interface(s) | Wake-up input / LIN master termination                                                     | Package                 | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|---------------------|-----------------------------------|------------------|--------------------------------------------------------------------------------------------|-------------------------|------------------|--------------------|-----|

| 33905 (Dual LIN)    | 3.3 V<br>or<br>5.0 V              | 2                | 2 Wake-up + 2 LIN terms<br>or<br>3 Wake-up + 1 LIN terms<br>or<br>4 Wake-up + no LIN terms | SOIC 54 pin exposed pad | Yes              | Yes                | Yes |

| 33905S (Single LIN) |                                   | 1                | 3 Wake-up + 1 LIN terms<br>or<br>4 Wake-up + no LIN terms                                  |                         |                  |                    |     |

### Table 2. 33904 device variations - (all devices rated at $T_A$ = -40 °C TO 125 °C)

| NXP part number | V <sub>DD</sub> output<br>voltage | LIN interface(s) | Wake-up input / LIN master<br>termination | Package                 | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|-----------------|-----------------------------------|------------------|-------------------------------------------|-------------------------|------------------|--------------------|-----|

| 33904           | 3.3 V<br>or<br>5.0 V              | 0                | 4 Wake-up                                 | SOIC 32 pin exposed pad | Yes              | Yes                | Yes |

NXP Semiconductors 2

Table 3. 33903 device variations - (all devices rated at  $T_A$  = -40 °C TO 125 °C)

| NXP part number     | V <sub>DD</sub> output<br>voltage                  | LIN interface(s) | Wake-up input / LIN master termination                                                     | Package                    | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|---------------------|----------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|----------------------------|------------------|--------------------|-----|

| 33903               | 3.3 V <sup>(1)</sup><br>or<br>5.0 V <sup>(1)</sup> | 0                | 1 Wake-up                                                                                  | SOIC 32 pin<br>exposed pad | No               | No                 | No  |

| 33903D (Dual LIN)   | 3.3 V<br>or                                        | 2                | 1 Wake-up + 2 LIN terms<br>or<br>2 Wake-up + 1 LIN terms<br>or<br>3 Wake-up + no LIN terms |                            |                  | Yes                | Yes |

| 33903S (Single LIN) | 5.0 V                                              | 1                | 2 Wake-up + 1 LIN terms<br>or<br>3 Wake-up + no LIN terms                                  |                            |                  |                    | res |

| 33903P              |                                                    | 0                | 3 Wake-up                                                                                  |                            |                  |                    |     |

#### Notes

# 2.2.2 Pin compatibility

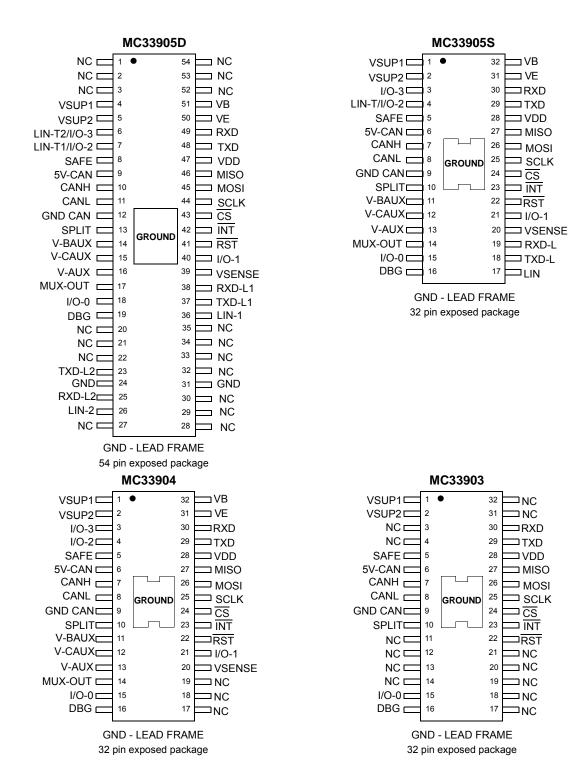

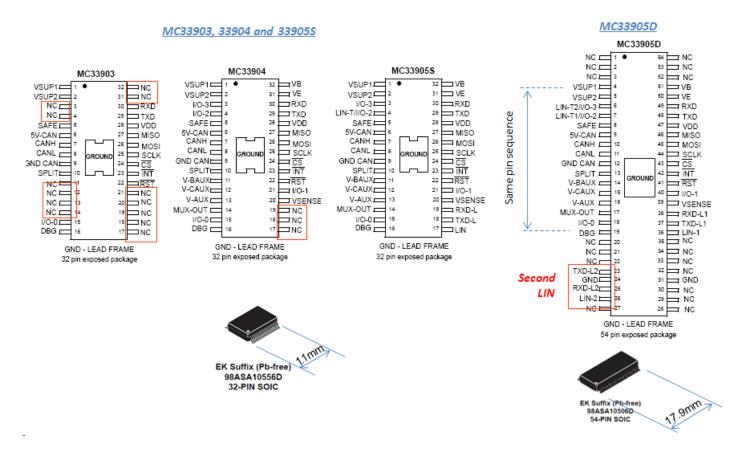

The feature set of ALL the SBCs described in this document is 100% compatible amongst all device part numbers. The SBC family is divided in two separate groups of devices that implement pin compatibility. The pin compatibility of each of the groups eases the transition of going from one part number to another and prevents having to re-layout a module in case of last minute module functionality requirement changes. One of the pin compatible groups is made up of the MC33905D, MC33905S, MC33904, and MC33903 as shown in Figure 1

<sup>1.</sup>  $V_{DD}$  does not allow usage of an external PNP on the 33903. Output current limited to 100 mA.

Figure 1. MC33905D, MC33905S, MC33904, and MC33903 pin connections

Something to note about this pin compatible group is that although the MC33905D is a 54 pin SOIC package, its footprint is still pin compatible to the rest of the 32 pin SOIC devices. Pin compatibility is accomplished by offsetting the placement of the smaller package by 3 pins down on the 54 pin footprint as shown in Figure 2

NXP Semiconductors 4

Figure 2. MC33905D, MC33905S, MC33904, and MC33903 pin compatibility

One other item to consider when laying out the Printed Circuit Board (PCB) is the implementation of the exposed pad to maximize power dissipation regardless of the package used. To accommodate the option of using both 54 and 32 lead packages, the exposed pad PCB flag must be enlarged as shown in Figure 3

Figure 3. MC33905D, MC33905S, MC33904, and MC33903 exposed pad design

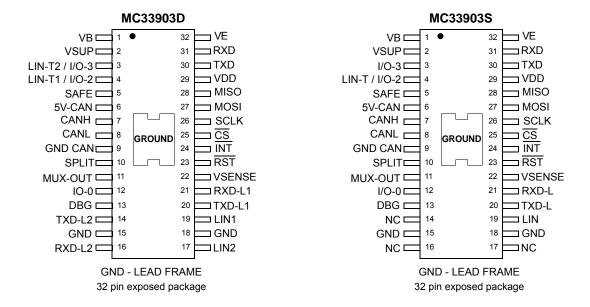

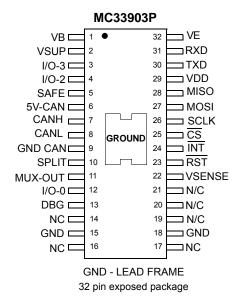

The other pin compatible group is made up of the MC33903D, MC33903S, and MC33903P as shown in Figure 4

Note: MC33903D, MC33903S, and MC33903P are footprint compatible.

Figure 4. MC33903D, MC33903S, and MC33903P pin compatibility

This group of pin compatible devices implements the same package so there is no need to accommodate the package placement or PCB exposed flag like the previously mentioned group.

## 2.3 Device identification

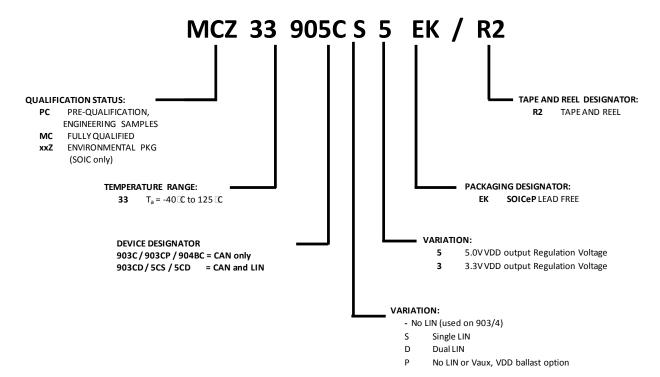

As previously described, there are numerous part numbers available to choose from and sometimes it may be difficult to keep track of which device has been mounted on a specific module. For this reason, the marking on a device is critical to understand. NXP has developed the SBC product numbering scheme shown in Figure 5.

Figure 5. Device marking information

In addition to the physical marking on the device's package, the device's part number can also be acquired by the microcontroller via SPI communication by reading the assigned SAFE-INT register address (see Table 4). The SPI word that has to be sent on MOSI is 0x2580 and the corresponding data will be read on MISO by the microcontroller. This becomes extremely useful when the user does not have visual access to the physical device or the marking on the package has faded off.

Table 4. Device identification via SPI command

### **SAFE-INT Register**

### **Device ID Coding**

| 00 | 1_0010<br>SAFE                                                                                                                                      | 1 | 1 | V <sub>DD</sub> (5.0 V<br>or 3.3 V) | device<br>p/n 1 | device<br>p/n 0 | id4 | id3 | id2 | id1 | id0 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------|---|---|-------------------------------------|-----------------|-----------------|-----|-----|-----|-----|-----|

|    | Hexa SPI commands to get device Identification: MOSI 0x 2580 example: MISO bit [7-0] = 1011 0100: MC33904, 5.0 V version, silicon Rev. C (Pass 3.3) |   |   |                                     |                 |                 |     |     |     |     |     |

| V <sub>DD</sub> (5.0 V or 3.3 V) | Description           | 0: mean 3.3 V V <sub>DD</sub> version<br>1: mean 5.0 V V <sub>D</sub> D version                                                                     |

|----------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Set / Reset condition | N/A                                                                                                                                                 |

| Device P/N1 and 0                | Description           | Describe the device part number: 00: MC33903 01: MC33904 10: MC33905S 11: MC333905D                                                                 |

|                                  | Set / Reset condition | N/A                                                                                                                                                 |

| Device id 4 to 0                 | Description           | Describe the silicon revision number 10010: silicon revision A (Pass 3.1) 10011: silicon revision B (Pass 3.2) 10100: silicon revision C (Pass 3.3) |

|                                  | Set / Reset condition | N/A                                                                                                                                                 |

Note: This device identification feature is not available on the MC33903D, MC33903S, and MC33903P.

# 3 Device features

## 3.1 MC33903/4/5 functional blocks

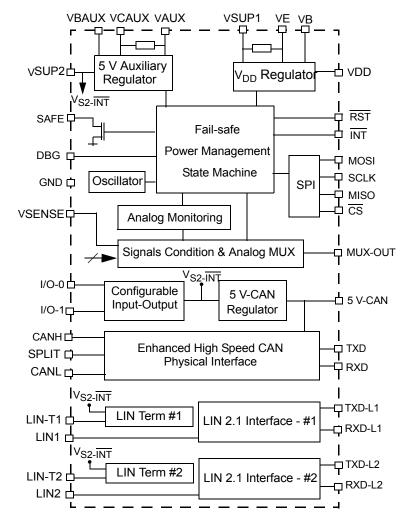

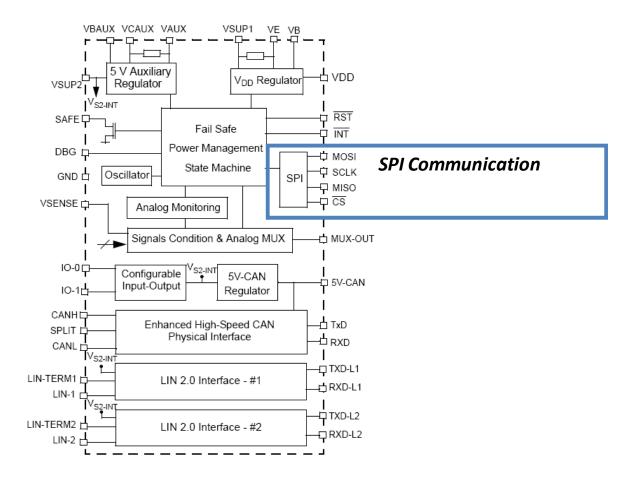

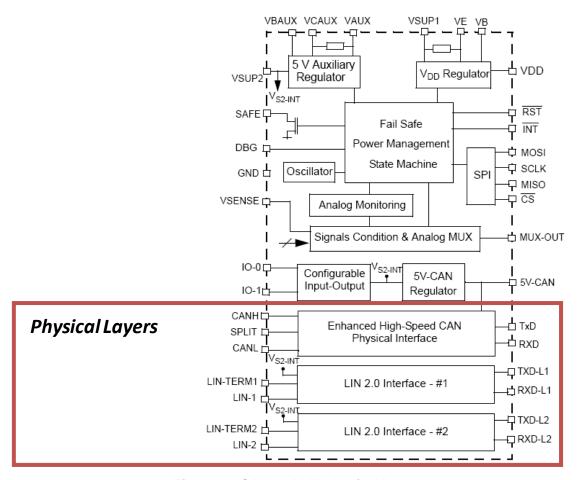

SBCs may sometimes be perceived as complex devices that are hard to implement due to their extensive feature set, but working with these is actually quite simple. To design and develop a reliable and robust automotive application that implements the MC33903/4/5, the module designer must first have a good understanding of the SBC's features and circuit blocks functionality. **Figure 6** shows the internal block diagram for the MC33905D, which is the SBC with the most features compared to the rest of the SBC devices that also combine the necessary features to meet the designer's needs.

Figure 6. 33905D internal block diagram

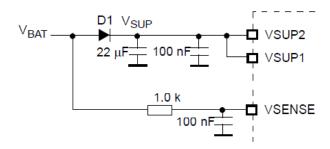

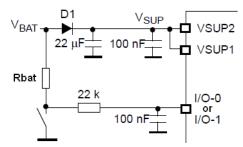

# 3.1.1 Voltage supplies - VSUP1, VSUP2

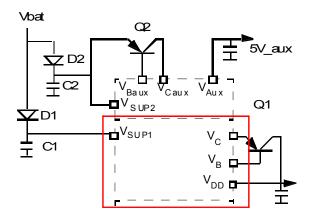

This family of SBCs has been developed to meet rigorous 12 V automotive system requirements and with this in mind, it has two separate supplies. The purpose of having dual voltage supply inputs for some of these SBCs is to give the module designer the flexibility to use specific external components on the battery lines depending on module requirements. As shown in Figure 7, VSUP1 is a dedicated supply that feeds the main VDD regulator, which has the function of powering up the module's microcontroller. VSUP2 supplies V<sub>AUX</sub>, 5V-CAN, LIN, and I/Os so in case of any faults on any of these, the VDD will not be affected due to its supply isolation.

Figure 7. V<sub>SUP1</sub> and V<sub>SUP2</sub> Voltage supplies

In addition to the internal isolation of the  $V_{SUP1}$  to supply the VDD regulator feature, the module's designer can also optimize the external capacitor and reverse battery protection diode used on  $V_{SUP1}$  to sustain environmental conditions such as battery crank pulse and chattering.

The MC33903D, MC33903S, and MC33903P only have a single supply input (VSUP), which supplies VDD, VAUX, 5V-CAN, LIN, and I/Os. For these devices, VSUP1 and VSUP2 nodes are internally connected by wire bonds to the VSUP pin.

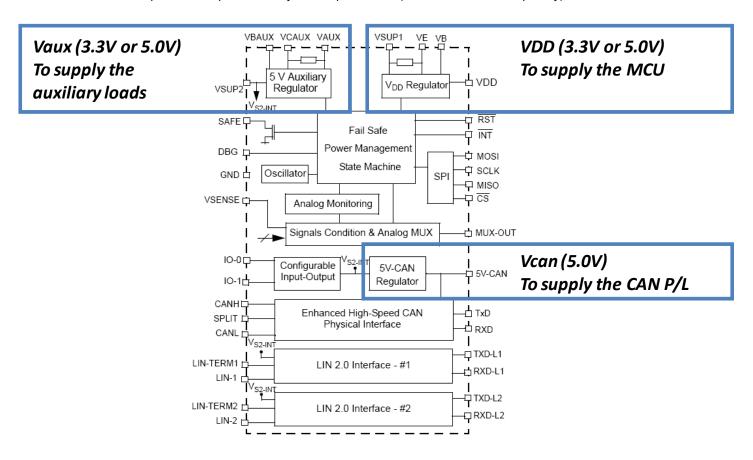

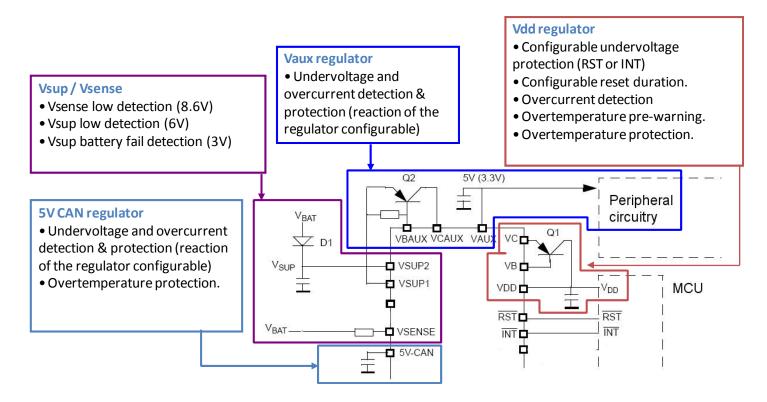

## 3.1.2 Voltage regulators - VDD, VAUX, 5V-CAN

There are two to three embedded voltage regulators included in the MC33903/4/5 SBC family. The VDD is the main regulator that supplies the microcontroller of the module. This regulator can be either 3.3 V or 5.0 V at +/-2% accuracy. The VDD voltage is dependent on part number. Refer to the data sheet for more details.

The Vaux regulator can also be 3.3 V or 5.0 V (at +/-5% accuracy), but in this case the voltage is configurable via SPI. Vaux is not implemented in all of the MC33903/4/5 SBC devices since some applications may not require this auxiliary regulator (see Table 1, Table 2, and Table 3).

The 5V-CAN regulator is a dedicated 5.0 V supply for the CAN physical layer. Ideally, this regulator should be used solely for the CAN interface, but some applications may not require this communication protocol. So for cases where there is no CAN transceiver implemented or during no CAN communication modes of the SBC, this regulator may also be used to supply another 5.0 V device. Good care must be taken to keep the device parametrically within specification (i.e. 5V-CAN current capability).

Figure 8. VDD, V<sub>AUX</sub>, and 5V-CAN embedded regulators

NXP Semiconductors 12

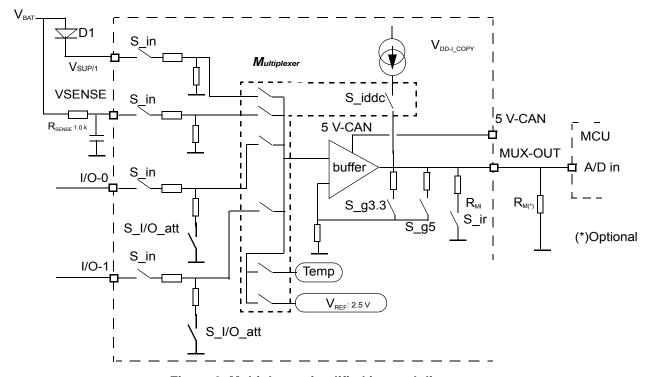

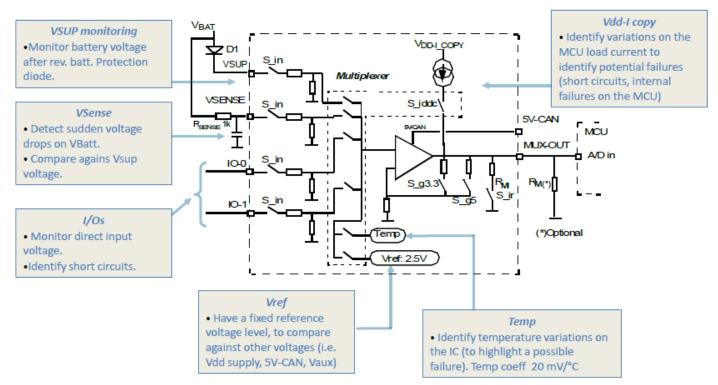

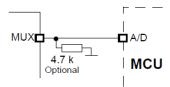

## 3.1.3 Multiplexer - MUXOUT

The MC33903/4/5 family of SBCs implements an analog multiplexed output for some of the SBCs. The MUX-OUT pin should be connected to the analog to digital converter of the microcontroller. This output voltage is limited to the voltage on VDD and allows for the microcontroller to monitor critical environment conditions of the module such as  $V_{SUP}$ ,  $V_{SENSE}$ , I/O-0, and I/O-1 voltages. Additionally, the SBC has an internal reference voltage of 2.5 V that can also be read on the MUX-OUT. The current sourced on VDD and the internal die temperature of the SBC can also be measured by the microcontroller by reading the MUX-OUT voltage.

Figure 9. Multiplexer simplified internal diagram

The 5V-CAN voltage can be within the limits before or after  $V_{DD}$  voltage is available, and  $V_{DD}$  undervoltage reset is released.

Therefore it is recommended to validate the availability of the 5V-CAN voltage after a start-up of the device or return from an undervoltage condition, and before the MUX register write operation. This can be done with means of the flag 5V-CAN\_UV in the Regulator Flag Register.

In addition to the dedicated 5V-CAN\_UV, the 5V-CAN regulator undervoltage condition is also indicated by the bit VREG-G bit of the Fixed Status bits. Fixed Status is the first byte of each MISO frame. It is a good practice to implement an appropriate exception handling in the software, in case one or more of the Fixed Status bits are set.

Another possibility for verification of the MUX register is to read the register value back after a write operation. If the 5V-CAN regulator is OFF, a read-back of the MUX register (command 0x0100) returns the value 0x00.

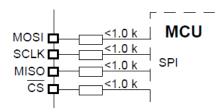

# 3.1.4 Serial peripheral interface (SPI) - MOSI, MISO, SCLK, CS

The 16 bit SPI communication in this family of SBCs has some unique features that can be implemented to improve the safety and robustness of the module's microcontroller and SBC interaction. There are 32 bit-addresses available for SPI communication and multiple types of watchdog operations can be implemented. Window watchdog is set by default and user can then select timeout or advanced watchdog thereafter.

Figure 10. SPI port - MOSI, MISO, SCLK, and CS

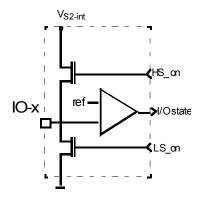

# 3.1.5 Configurable input/output - I/O-0, I/O-1, I/O-2, I/O-3

There are one to four configurable I/Os included in the MC33903/4/5 SBC family. These I/Os can be used to drive external transistors or small loads such as LED indicator lights. These I/Os can be configured as high-side or low-side outputs that switch to VSUP2 and GND correspondingly. Additionally, these can be configured as wake-up inputs, which can sustain automotive transients when connected to the battery line.

Figure 11. I/O simplified internal diagram

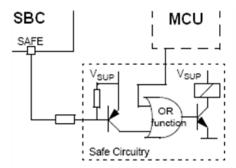

# 3.1.6 Safe modes - SAFE, RST, INT

In addition to the continuous monitoring of the watchdog to maintain supervision of the microcontroller-SBC interaction, the SBC also features continuous monitoring of the battery voltage and the embedded regulators of the device. In case of serious module conditions due to faults on the battery resulting on VDD undervoltage conditions, a reset will be generated by the SBC.

There are also mask-able interrupts configurable to trigger upon CAN and LIN faults, overvoltage and undervoltage conditions on Vaux, 5V-CAN,  $V_{SUP}$ , and  $V_{SENSE}$ , missed watchdog/s, thermal issues and overcurrent conditions. Additionally, the microcontroller can voluntarily request and INT assertion by sending a SPI command.

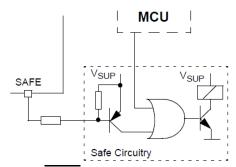

The MC33903/4/5 family of SBCs also has a SAFE active-low output that is triggered in the event of a microcontroller failure, which could be indicated by multiple resets, RST pin shorted to GND, low VDD, or missed watchdog/s. The intention for this output signal is to drive electrical safe circuitry isolated from both the microcontroller and the SBC to put the module in a known state.

Figure 12. SAFE output typical application schematic

# 3.1.7 Physical layers - CAN & LIN

The MC33903/4/5 family of SBCs combines CAN and LIN physical layers with various features such as number of I/Os, number of regulators, multiplexing capability, etc. All devices have one CAN physical layer and dependent on part number, these may integrate one, two or no LIN transceivers.

Figure 13. CAN and LIN physical layers

The CAN physical layer is fully compliant to ISO 11898-2 and ISO 11898-5 High Speed CAN protocol specifications. This allows for bus communication baud rates ranging from 40 kb/s up to 1.0 Mb/s via twisted pair.

The LIN physical layer is fully compliant to LIN 2.1 and SAE J2602-2 LIN protocol specifications, which allow single wire bus communication speeds of 20 Kb/s and 10.4 Kb/s correspondingly.

Both the CAN and LIN physical layers have been EMC/ESD certified by numerous worldwide OEMs. To accomplish this certification, the family of SBCs must be robust enough to conform to rigorous EMC/ESD tests that meet and exceed some of the OEM requirements.

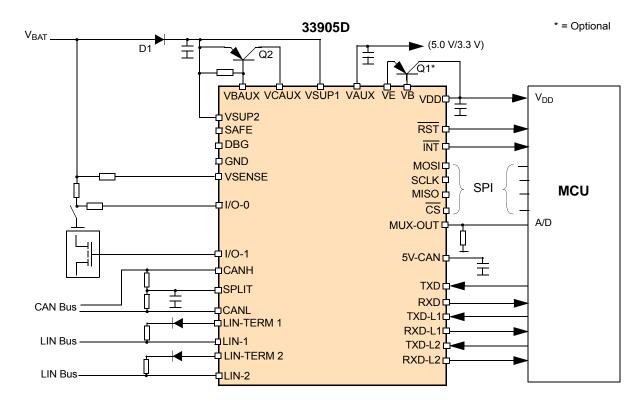

# 4 Hardware design

Once the module designer has a good understanding of the SBC's features and circuit blocks functionality, a robust and reliable automotive module can then be designed. The typical application schematic, which is included in the datasheet, is a good starting point for the design and development of an automotive module that implements the MC33903/4/5.

Figure 14. 33905D simplified application diagram

# 4.1 Supply environment

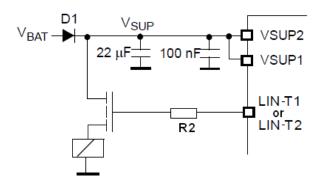

The automotive battery supply line is exposed to various high voltage transients, drops, and high/low frequency noise. To accommodate for this harsh supply environment, the MC33903/4/5 implements two separate supply lines for some of the SBCs and has a wide range of functionality depending on voltage of VSUP1 pin. Additionally, there is a VSENSE input that can optionally be connected directly to the battery through a 1.0 k $\Omega$  +/-1% resistor to monitor exact battery voltage via MUX-OUT. Figure 15 shows a typical way to connect the battery to all the supplies of the SBC. Note that the 22  $\mu$ F capacitor on the V<sub>SUP</sub> line is not required, but was implemented to test for CAN and LIN EMC per OEM's requirement of 10  $\mu$ F minimum on the V<sub>SUP1</sub> line.

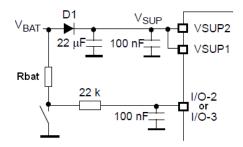

Figure 15. VSUP1 and VSUP2 typical application schematic

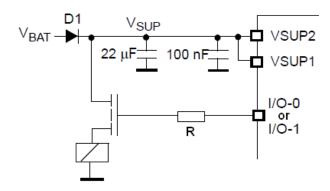

There are two options of connecting the SBC's voltage supply line to the car battery. One option is to short the VSUP1 and VSUP2 together and use the same protection and buffering external components (shown in Figure 16).

Figure 16. Single supply line typical application schematic

In this case, the same high voltage transients and drops will be seen on both VSUP1 and VSUP2. The module designer must also take into account that in addition to  $V_{AUX}$ , the  $V_{SUP2}$  line also supplies the 5V-CAN, LIN, and I/Os. Any perturbations on these circuit blocks affecting the  $V_{SUP2}$  supply line will also affect  $V_{SUP1}$  and perturb  $V_{DD}$  as a result.

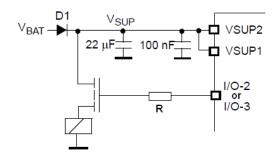

The other option of connecting the supply lines is by separating  $V_{SUP1}$  and  $V_{SUP2}$  using different protection and buffering components as shown in Figure 17.

Figure 17. Separate supply lines typical application schematic

Although this adds some cost to the module's bill of material (BOM), in return it may prevent serious module malfunctions during extreme low battery conditions. Separating the supply lines allows for the optimization of the buffering capacitor for handling automotive conditions such as cranking, battery chattering and others. Additionally, a conventional reverse battery protection diode can be replaced with a Schottky type to further decrease the voltage drop from battery to VSUP1. This will give VDD more headroom to stay above the minimum voltage threshold and keep the microcontroller fully functional.

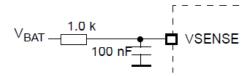

Optionally, VSENSE can be connected directly to the car's battery through a 1.0 k $\Omega$  +/-1% resistor to acquire exact battery voltage and deliver it to the microcontroller via MUX-OUT. The high accuracy of the resistor is required to keep the MUX-OUT reading at +/-1% accuracy. If battery voltage accuracy reading is not required, lower accuracy resistors can also be used (1.3 k $\Omega$  resistor on VSENSE will change the MUX-OUT ratio by about 1%; 10 k $\Omega$  will change ratio by about 7%). Note that although the MC33903/4/5 family of SBCs maximum nominal voltage is 28 V, the VSENSE reading out on MUX-OUT will only cover 5.5 V to 27 V.

Figure 18. VSENSE typical application schematic

# 4.1.1 Crank pulse and battery chattering

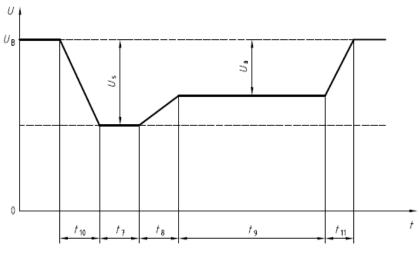

OEMs require that modules withstand various pulses on the supply line, some of which are part of the ISO 7637 specification. Pulse 4 of the ISO 7637 emulates the battery line voltage transitions during engine start (see Figure 19). The MC33903/4/5 is able to function properly during these voltage dips and even lower voltages than the worst case conditions incorporating enhanced diagnostics and keeping the module's microcontroller running.

| Parameter       | 12 V system                                   |

|-----------------|-----------------------------------------------|

| $U_{s}$         | - 6 ∨ to - 7 ∨                                |

| $U_{a}$         | – 2,5 V to – 6 V with $ U_a  \leqslant  U_S $ |

| t <sub>7</sub>  | 15 ms to 40 ms                                |

| t <sub>8</sub>  | ≼ 50 ms                                       |

| t <sub>9</sub>  | 0,5 s to 20 s                                 |

| t <sub>10</sub> | 5 ms                                          |

| t <sub>11</sub> | 5 ms to 100 ms                                |

Figure 19. Crank pulse parameters

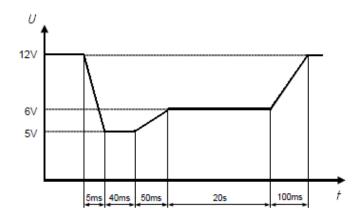

Taking the worst case conditions for pulse 4, as specified on the ISO 7637, results in the voltage waveform shown in Figure 20 for the battery line (represented by Vbat [in green] in Figure 21).

Figure 20. Worst case crank pulse

NXP Semiconductors 19

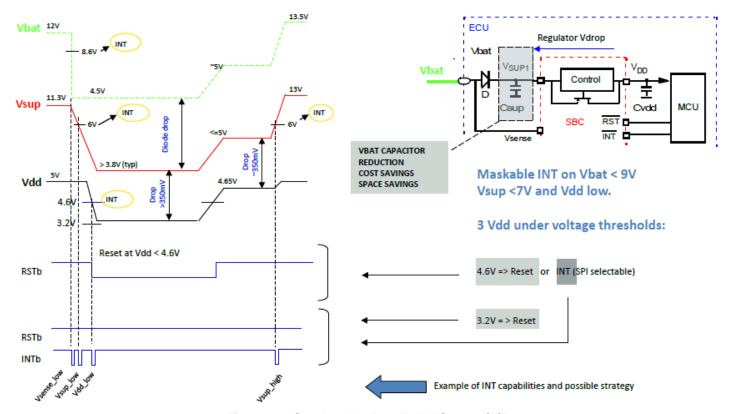

Figure 21 shows all the various transitions of the key voltages of the module during the crank pulse on battery voltage and how these are handled by the MC33903/4/5 (5.0 V  $V_{DD}$  devices). Note that a Schottky diode is not required to withstand these pulse conditions. As the battery voltage decreases, the SBC can immediately acknowledge this via the VSENSE input, which is directly connected to the battery through a 1.0 k $\Omega$  +/-1% resistor. A flag will be set when VSENSE voltage reaches ~8.6 V and can be configured to generate an interrupt or mask it for the microcontroller. Due to the capacitor on the VSUP line, its voltage will decrease at a slower rate and when it reaches ~6.0 V, a flag is set and the SBC can also optionally be configured to generate an interrupt or mask it for the microcontroller. As the  $V_{SUP}$  voltage continues to decrease, the  $V_{DD}$  voltage eventually tracks it with typically ~200 mV drop. VDD can be configured to generate a RST and/or INT (maskable) at 4.6 V or down to 3.2 V.

Figure 21. Crank pulse handled MC33903/4/5

As battery voltage starts to increase,  $V_{SUP}$  tracks it and  $V_{DD}$  tracks  $V_{SUP}$ . When  $V_{DD}$  reaches 4.6 V, RST is released and the microcontroller can function accordingly. When the  $V_{SUP}$  reaches ~6.0 V, an interrupt can be generated depending on SBC configuration.

All these capabilities of the MC33903/4/5 allow the engineer to implement highly intelligent modules with enhanced diagnostics. These modules are capable of sustaining aggressive conditions such as pulse 4 of the ISO 7637 as well as battery chattering without the need for higher cost capacitors and/or Schottky diodes. This doesn't only reduce cost, but also optimizes PCB real estate.

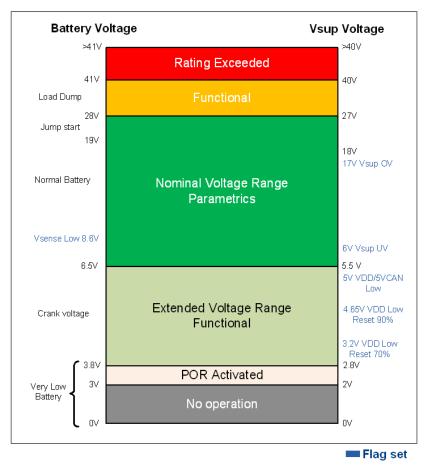

In addition to low battery conditions, the MC33903/4/5 will also withstand higher than nominal voltage conditions/pulses on the battery line such as 40 V Load Dump (pulse 5b of ISO 7637). Figure 22 shows all the voltage ranges the SBC can handle and what functionality can be expected during these voltage ranges. Shown in blue are the flags that will automatically be set for the microcontroller to acknowledge.

Figure 22. Supply voltage ratings

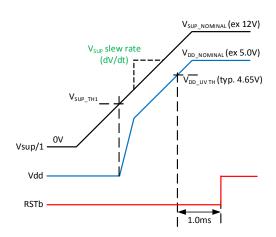

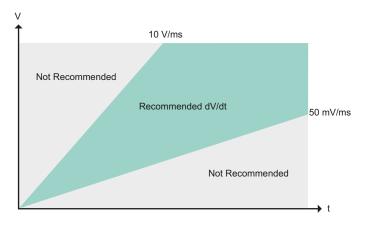

# 4.1.2 V<sub>SUP</sub> ramp up slew rate

Note: The following recommendation does not apply to the D version.

V<sub>DD</sub> regulator is connected to V<sub>SUP</sub>. V<sub>DD</sub> regulator start up could be influenced by V<sub>SUP</sub> ramp up slew rate at low temperatures.

Figure 23. V<sub>SUP</sub> dV/dt limit

Both behaviors described below could be observed on specific application where  $V_{SUP}$  is switched on and off with front relay and regularly generates this specific dV/dt. The behavior is not observed in typical applications where  $V_{SUP}$  is directly connected to the battery.

NXP Semiconductors 21

These behaviors depend on V<sub>SUP</sub> slope at start-up, V<sub>SUP</sub> voltage and temperature. Two different conditions have been identified:

- No V<sub>DD</sub> SSR (Slow Slew Rate on V<sub>SUP</sub>)

- No V<sub>DD</sub> FSR (Fast Slow Rate on V<sub>SUP</sub>)

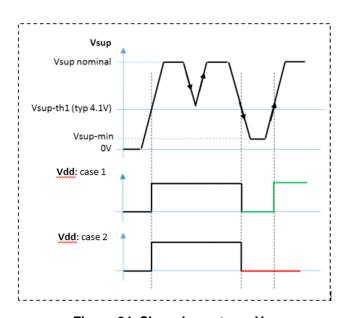

# 4.1.2.1 No V<sub>DD</sub> SSR

$V_{\mbox{\scriptsize DD}}$  case 2, as described in Figure 23, has been observed with following conditions:

- V<sub>SUP</sub>-min = 1.0 V

- V<sub>SUP</sub> nominal = 9.0 V

- Cold temperature conditions: from 5.0 °C to –40 °C

- V<sub>SUP</sub> slow slew rate: 10 mV/ms

Figure 24. Slow slew rate on V<sub>SUP</sub>

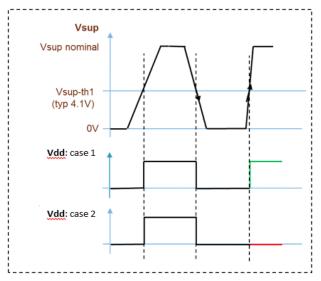

# 4.1.2.2 No V<sub>DD</sub> FSR

V<sub>DD</sub> case 2, as described in Figure 24, could be observed if all following conditions are met:

- V<sub>SUP</sub> slew rate is faster than 10 mV/μs

- Cold temperature from 0 °C to –40 °C

#### Risk assessment:

- 0 ppm is dV/dt slower than 10 mV/µs

- 0.33 ppm to 50.3 ppm with 90% confident Level, if dV/dt is faster than 10 mV/µs

- 0.66 ppm to 42.8 ppm with 60% confident level, if dV/dt is faster than 10 mV/μs

Figure 25. Fast slew rate on V<sub>SUP</sub>

The  $V_{SUP}$  ramp up slew rate and voltage level should be controlled as described below, especially in applications where  $V_{SUP}$  switches on and off regularly.

Figure 26.  $V_{DD}$  start up versus  $V_{SUP}/1$  ramp

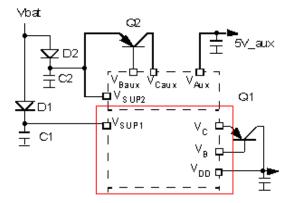

# 4.2 Regulators

The MC33903/4/5 offers three low dropout linear voltage regulators.  $V_{DD}$  is specifically supplied by VSUP1 separately from VAUX and 5V-CAN, which are supplied by VSUP2. Some buffering capacitors have to be implemented on the regulators depending on application. There is also the option to increase the current capability of the VDD regulator by implementing an external ballast transistor. The MC33903D, MC33903S, and MC33903P only have one supply input ( $V_{SUP}$ ), which supplies all three regulators. For these devices,  $V_{SUP1}$  and  $V_{SUP2}$  nodes are internally connected by wire bonds to the VSUP pin.

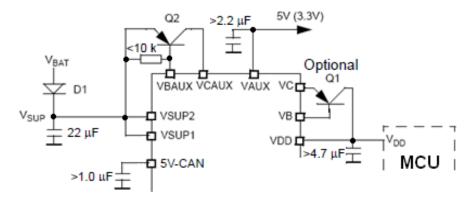

Figure 27. VDD, VAUX, and 5V-CAN typical application schematic

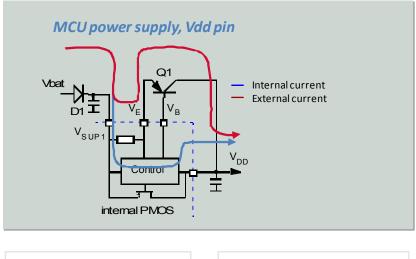

## 4.2.1 VDD

Supplying the microcontroller, VDD is the main regulator for the module. All MC33903/4/5 SBCs are available with 5.0 V or 3.3 V VDD (part number selectable). The current capability and voltage monitoring of this regulator is critical for the application. There are various safety features integrated into this regulator allowing for a highly robust and smart module design. VDD has overcurrent, overtemperature, and undervoltage detection. In case of overtemperature, the regulator will turn off automatically to protect itself from damage. The SBC is continuously monitoring the VDD voltage and will trigger an interrupt or reset during undervoltage conditions.

Figure 28. V<sub>DD</sub> typical application schematic options

VDD does not require any discrete components other than a minimum of  $4.7~\mu F$  capacitor. Optionally, VDD's 150 mA current capability can be increase by the implementation of an external PNP bi-polar junction transistor. When the transistor is not implemented, VC and VB pins must be left open. When the PNP transistor is implemented, 1/3 of the current will flow through the device and 2/3 will flow outside through the external ballast transistor. The recommended PNP bi-polar junction transistors are MJD42C and BCP52-16.

# Internal Regulator

- 5.0V / 3.3V Option

- Supply up to 150 mA

- LDO +/- 2%

## **Power Sharing**

- Optional

- Derivation of 2/3 Ivdd

- 2/3 Power dissipation

- Current Limitation

- Over Voltage protect

Figure 29. VDD power sharing capability

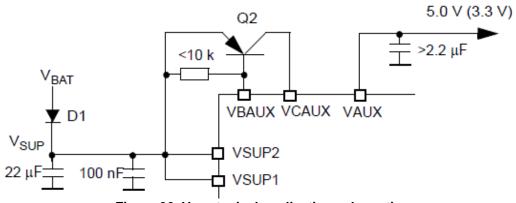

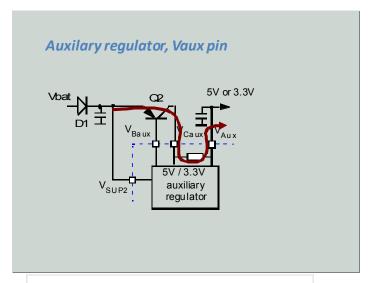

## 4.2.2 VAUX

The VAUX regulator can be used to supply other ICs such as switch detection interfaces, standalone CAN transceivers, RF modules, back up microcontroller, etc. This 5.0 V or 3.3 V +/-5% accuracy auxiliary regulator is available on all MC33904/5 SBCs, except the MC33903. The  $V_{AUX}$  output voltage level is selectable by the SPI during the SBC's initialization phase (default is 3.3 V). This regulator has overcurrent and undervoltage detection and automatic shutdown for protection. Additionally, the SBC can be configured to trigger an interrupt for the microcontroller in case of an overcurrent or undervoltage condition.

Figure 30. V<sub>AUX</sub> typical application schematic

This regulator requires an external PNP bi-polar junction transistor, a resistor, and a buffering capacitor, as shown in Figure 30. The transistor enables better power dissipation to enhance the current capability of  $V_{AUX}$  (MAX: 250 mA). This regulator is OFF by default and controlled by SPI after power-up. The recommended PNP bi-polar junction transistors are MJD42C and BCP52-16.

Control of External Ballast transistor

- 5.0 / 3.3 V Configurable

- Control of Regulation (LDO +/-5%)

- Power dissipation on external PNP

- Current Limitation

- Over Voltage protection

Figure 31. V<sub>AUX</sub> nominal application characteristics

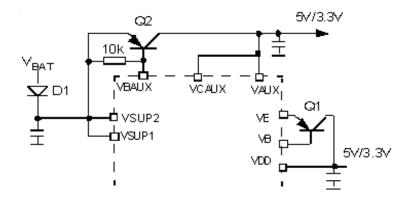

## 4.2.2.1 Extending current capability and routing outside of module

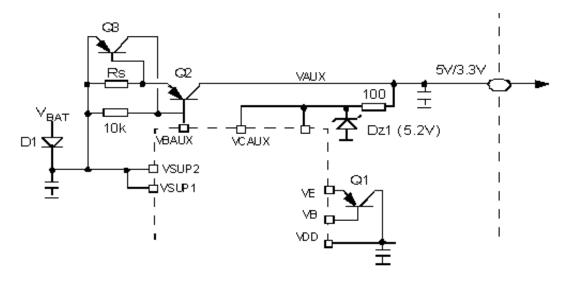

If more than 250 mA of current capability is required out of the  $V_{AUX}$  regulator, it is possible to extend the current capability by implementing a non-typical use case for the SBC (see Figure 32). Be warned that when using the SBC as described, the  $V_{AUX}$  internal current limitation is deactivated. In this case, the current will be limited by the VBAUX drive capability. Using the recommended transistors MJD42C or BCP52-16 will increase the  $V_{AUX}$  MAX current capability to 500 mA (considering a DC gain greater than 25).

Figure 32. V<sub>AUX</sub> increased current capability without current limit schematic

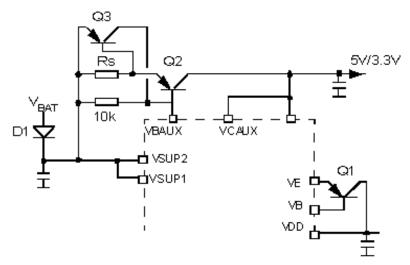

If current limit is required with higher MAX current capability, it is possible to accomplish this with a few additional components as shown in Figure 33. In this case, the external current limit will be  $V_{BE}$  of Q3 divided by Rs. The recommended PNP bi-polar junction transistors are MJD42C and BCP52-16.

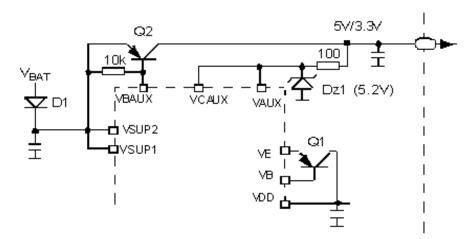

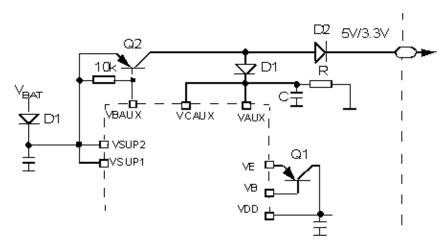

Figure 33. V<sub>AUX</sub> increased current capability with external current limit schematic

Some applications require that the  $V_{AUX}$  regulator be brought outside of the module. This option is also available for the MC33904/5 SBCs with some limitations by implementing a few additional components. Adding a 5.2 V zener diode and a 100  $\Omega$  resistor as shown in Figure 34, will allow  $V_{AUX}$  to survive shorts to +20 V. Be warned that by implementing this circuitry, the current limit function is disabled. The  $V_{AUX}$  voltage will also increase by about 40 mV compared to the internal typical use case voltage shown in Figure 30. The recommended PNP bipolar junction transistors are MJD42C and BCP52-16.

Figure 34. V<sub>AUX</sub> routed outside module with +20 V protection and without current limit

If current limit is required with higher MAX current capability and  $V_{AUX}$  needs to go outside the module, it is possible to accomplish this with a few additional components as shown in Figure 35. Adding a 5.2 V zener diode and a 100  $\Omega$  resistor will allow  $V_{AUX}$  to survive shorts to +20 V. In this case, the external current limit will be Vbe of Q3 divided by Rs so the SBC will also survive shorts to GND. The  $V_{AUX}$  voltage will increase by about 40 mV compared to the internal typical use case voltage shown in Figure 30. The recommended PNP bi-polar junction transistors are MJD42C and BCP52-16.

Figure 35. V<sub>AUX</sub> routed outside module with +20 V protection and external current limit

If it's required for the  $V_{AUX}$  to be brought outside the module and to handle positive transient voltages up to +40 V (Load Dump), this can be accomplished by adding a few additional components. Be warned that the  $V_{AUX}$  current limit will be disabled and the voltage drop will be higher due to the diode drop of D2 shown in Figure 36. Short to GND detection can be done via the  $V_{AUX}$  undervoltage detection. The recommended PNP bi-polar junction transistors are MJD42C and BCP52-16.

Figure 36. VAIIX routed outside module with +40 V protection and without current limit

## 4.2.3 5V-CAN

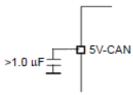

The 5V-CAN is a dedicated 5.0 V +/-5% accuracy regulator to supply the CAN interface of the MC33903/4/5 SBC family. This regulator has overcurrent, overtemperature, and undervoltage detection and automatic shutdown for protection. It requires a minimum of  $1.0 \mu F$  buffering capacitor and typically nothing else is connected to this regulator as shown in Figure 37. MUX-OUT and some blocks of the LIN interfaces are also powered by the 5V-CAN. In order to have a functional multiplexer and the LIN interfaces operational in transmit/receive mode, the 5V-CAN must be ON. This regulator is OFF by default and must be turned ON via the SPI. Note that when in debug mode, 5V-CAN is ON by default.

Figure 37. 5V-CAN typical application schematic

Although it is possible to supply other ICs with this regulator, it is not recommended mainly due to EMC performance degradation. In such cases, module designer must take good care to keep the SBC within specification. Some applications may not require CAN communication making the use of the 5V-CAN to supply other devices on the module more feasible. Optionally, this regulator may also supply other devices during non-CAN communication modes of the SBC.

# 4.3 Multiplexer

Some of the devices that are part of the MC33903/4/5 SBC family include an analog multiplexer to connect to the module's microcontroller A/D converter. Critical environment conditions such as:  $V_{SUP1}$ ,  $V_{SENSE}$ , I/O-0, I/O-1, internal 2.5 V  $V_{REF}$ , die Temp, and  $V_{DD-I}$  current copy can be monitored. The output voltage on MUX-OUT is limited to the voltage on VDD. This allows the microcontroller to gather critical module data and react accordingly to enhance the safety of the system.

Figure 38. Multiplexer monitoring capabilities

There are no additional components required to access the MUX-OUT since it can be connected directly to the microcontroller except for applications where the VDD current has to be monitored. In this case, a resistor from MUX-OUT to GND is required. An external 2.0 k $\Omega$  or greater resistor is recommended (see Figure 39). Optionally, an internal resistor can be activated via the SPI, but the resistance variation is much greater than implementing an external one. As a result, implementing an external resistance will give more accurate readings on the MUX-OUT.

Figure 39. Multiplexer typical application schematic

Note: Although the MC33903/4/5 family of SBCs maximum nominal voltage is 28 V, the VSENSE reading out on MUX-OUT will only cover 5.5 V to 27 V.

#### 4.4 SPI communication

The main communication between the microcontroller and the MC33903/4/5 is through the SPI port, which is made up of MOSI, MISO, SCLK, and CS. The maximum frequency of the SBC's 16-bit SPI is 4.0 MHz and there are 32 bit-addresses available. The logic voltage level of the SBC's SPI port will be determined by the V<sub>DD</sub> voltage, which supplies the microcontroller. There are no additional components required for the SPI port circuitry, but series resistor footprints are recommended on all SPI pins (see Figure 40) in case of aggressive noise immunity requirements. If this is not an issue, these can be populated with  $0 \Omega$  resistors. Note that the series resistance should not exceed 1.0 k $\Omega$  because this may cause some degradation on the signals due to the parasitic capacitance and dependency on the communication speed.

Figure 40. SPI typical application schematic

Note: The MC33903/4/5 SBC family does not allow for SPI daisy chain implementation

#### Configurable I/Os and LIN-terminations 4.5

The MC33903/4/5 family of SBCs offers one to four configurable I/Os and zero to two LIN-Ts dependent on part number (see Table 1, Table 2, and Table 3). These are all rated to withstand -0.6 V up to +40 V (Load Dump) and can be configured as outputs or wake-up inputs. When configured as outputs, these can be used to drive small loads as a high-side switch or a low-side switch with thermal protection in case of overload conditions. These can also be set to high-impedance for lower module current consumption when not in use.

#### 4.5.1 I/O-0 and I/O-1

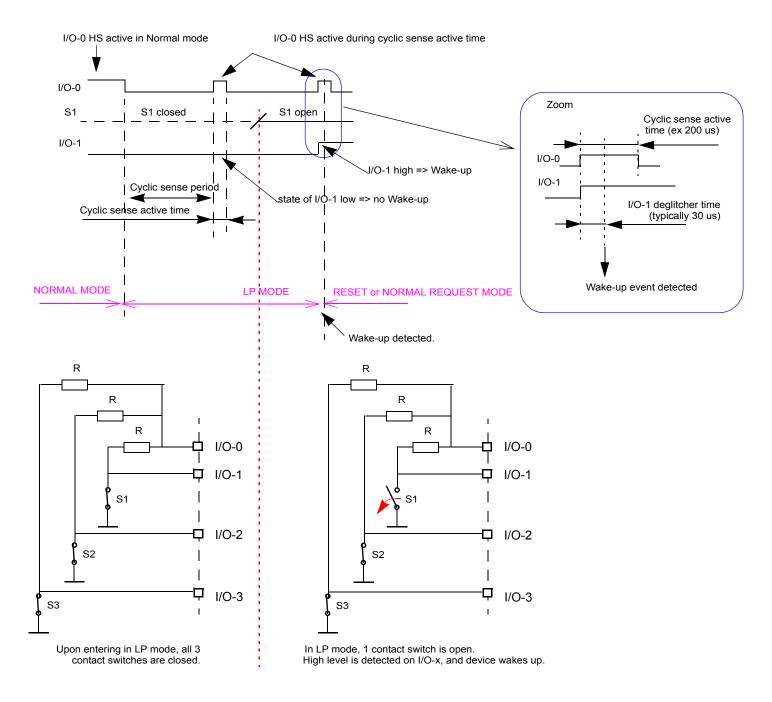

I/O-0 and I/O-1 are configured as wake-up inputs by default and the configuration state can be read via the SPI. The SBC will wake-up on both a 'high' to 'low' or 'low' to 'high' transition. I/Os can be configured to continuously monitor for transitions or 'cyclic sense wake-up' can be implemented on I/O-1 to decrease module current consumption.

I/O **WU Input** High-side Low-side 0 yes 20 mA 0.4 mA 1 0.4 mA 0.4 mA yes

Table 5. I/O-0 and I/O-1 functionality

A 22 k $\Omega$  resistor and a 100 nF decoupling capacitor are required for wake-up input implementation. R<sub>BAT</sub> (10 k $\Omega$  recommended) is user defined depending on module current consumption requirements since it may potentially be connected to battery permanently (See Figure 41).

Figure 41. I/O-0 and I/O-1 input typical application schematic

When I/O-0 and I/O-1 are configured as outputs, these can be either high-side or low-side switches. When configured as a high-side, the output will be switched to  $V_{SUP2}$  voltage. When configured as a low-side, the output will be switched to GND. The R resistor shown on the I/O in Table 42 is not required, but it is recommended to improve ESD performance and its value will be dependent on the circuitry the I/O has to drive.

Figure 42. I/O-0 and I/O-1 output typical application schematic

The value of resistor R will also be determined by taking into account the maximum current capability of the I/O. Look at Table 5 for high-side and low-side current capability for I/O-0 and I/O-1.

## 4.5.2 I/O-2 and I/O-3

I/O-2 and I/O-3 are disabled by default and must be configured by SPI during SBC initialization. When configured as wake-up inputs, the SBC will wake-up on both a 'high' to 'low' or 'low' to 'high' transition. These I/Os can be configured to continuously monitor for transitions or 'cyclic sense wake-up' can be implemented on I/O-2 and I/O-3 to decrease module current consumption.

| I/O | WU input | High-side | Low-side |

|-----|----------|-----------|----------|

| 2   | yes      | 20 mA     | N/A      |

| 3   | ves      | 20 mA     | N/A      |

Table 6. I/O-2 and I/O-3 functionality

A 22 k $\Omega$  resistor and a 100 nF decoupling capacitor are required for wake-up input implementation. R<sub>BAT</sub> (10 k $\Omega$  recommended) is user defined depending on module current consumption requirements since it may potentially be connected to battery permanently (See Figure 43).

Figure 43. I/O-2 and I/O-3 input typical application schematic

When I/O-2 and I/O-3 are configured as outputs, these can only be high-side switches and the output will be  $V_{SUP2}$  voltage. The R resistor shown on the I/O in Figure 44 is not required, but it is recommended to improve ESD performance and its value will be dependent on the circuitry the I/O has to drive.

Figure 44. I/O-2 and I/O-3 output typical application schematic

The value of resistor R will also be determined by taking into account the maximum current capability of the I/O. Look at Table 6 for high-side capability of I/O-2 and I/O-3.

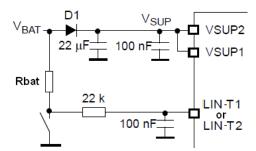

## 4.5.3 LIN-T1 and LIN-T2

LIN-T1 and LIN-T2 have dual functionality and can be configured as I/O-2 and I/O-3 correspondingly. These are disabled by default and must be configured by SPI during SBC initialization. They can be configured as LIN terminations for LIN master node applications or as I/O-2 or I/O3 depending on part number. When these are configured as LIN-Ts, they are controlled by the LIN register and will internally switch to  $V_{SUP2}$  as required by LIN master node application.

Figure 45. LIN-T1 and LIN-T2 typical application schematic

When LIN-T1 and LIN-T2 are configured to function as an I/O, these can be configured as wake-up inputs or high-side outputs. When configured as wake-up inputs, the SBC will wake-up on both a 'high' to 'low' or 'low' to 'high' transition. These can be configured to continuously monitor for transitions or 'cyclic sense wake-up' can be implemented on LIN-T1 and LIN-T2 to decrease module current consumption.

Table 7. LIN-T1 and LIN-T2 functionality

| LIN | WU input | High-side | Low-side |

|-----|----------|-----------|----------|

| T1  | yes      | 20 mA     | N/A      |

| T2  | yes      | 20 mA     | N/A      |

A 22 k $\Omega$  resistor and a 100 nF decoupling capacitor are required for wake-up input implementation. R<sub>BAT</sub> (10 k $\Omega$  recommended) is user defined depending on module current consumption requirements since it may potentially be connected to battery permanently (See Figure 46).

Figure 46. LIN-T1 and LIN-T2 input typical application schematic

When LIN-T1 and LIN-T2 are configured as outputs, these can only be high-side switches and the output will be  $V_{SUP2}$  voltage. The R2 resistor shown on the LIN-T in Figure 47 is not required, but it is recommended to improve ESD performance and its value will be dependent on the circuitry the I/O has to drive.

Figure 47. LIN-T1 and LIN-T2 output typical application schematic

The value of resistor R2 will also be determined by taking into account the maximum current capability of the LIN-T. Look at Table 7 for high-side capability for LIN-T1 and LIN-T2.

# 4.6 Safety interactions with microcontroller and debug

The MC33903/4/5 offers a wide range of functional safety features that allows the module designer to implement highly robust and reliable safety systems. The SBC's optional SAFE active low open drain output structure can be configured to trigger in case of a microcontroller failure, which could be indicated by multiple resets, RST pin shorted to GND, low  $V_{DD}$ , or missed watchdog/s. This will indicate that the module's microcontroller is no longer functional and a safety mechanism must be activated. SAFE pin must be left open if not used.

A safety implementation option is to activate a safety circuitry that is fully independent from the SBC or the microcontroller. Figure 48 shows this option and also allows the main MCU (microcontroller) to activate the safety circuitry even if the SAFE was not triggered. This adds system flexibility by allowing the MCU or the SAFE to activate the Safe Circuitry. All discrete components are determined by Safe Circuitry specifications.

Figure 48. SAFE typical application schematic

Another option is to just turn ON an LED in case of a SAFE fault. Figure 49 show a simple way to accomplish this. The resistor is determined by the LED specifications.

Figure 49. SAFE LED indicator typical application schematic

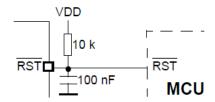

The MC33903/4/5 also implements a  $\overline{RST}$  that allows for a system reset at first power up and for any other serious module conditions that may require a system reset such as battery faults generating VDD undervoltage conditions. The reset duration can be configured to 1.0 ms, 5.0 ms, 10.0 ms, or 20.0 ms via the  $\overline{SPI}$  (1.0 ms by default) depending on application requirements. There are no additional discrete components required to connect the  $\overline{RST}$  (internal ~11 k $\Omega$  pull-up to VDD) to the microcontroller, but a 10 k $\Omega$  pull-up resistor to VDD and a 100nF capacitor to GND are recommended for noise immunity and signal integrity on some applications.

Figure 50. RST typical application schematic

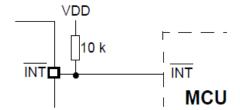

The MC33903/4/5 also offers mask-able interrupts configurable to selectively trigger upon CAN and LIN faults, overvoltage and undervoltage conditions on VAUX, 5V-CAN, VSUP, and VSENSE, missed watchdog/s, thermal issues and overcurrent conditions. The  $\overline{\text{INT}}$  duration can be configured to 25 us or 100 us (default) via the SPI depending on application requirements. Additionally, the microcontroller can request and  $\overline{\text{INT}}$  as needed by sending a SPI command. There are no additional discrete components required to connect the  $\overline{\text{INT}}$  (internal ~10 k $\Omega$  pull-up to VDD) to the microcontroller, but a 10 k $\Omega$  pull-up resistor to VDD is recommended for noise immunity and signal integrity on some applications.

Figure 51. INT typical application schematic

35

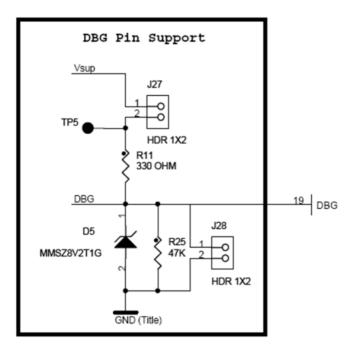

The DBG (debug) pin has dual functionality. It can be used to run the SBC in debug mode (no need to monitor the watchdog) by placing 8.0 V - 10 V on pin or a resistor can be placed to GND. When the resistance to GND is implemented on this pin, the SBC will then react to a module fault in four different safe modes of the SBC depending on the DBG resistor value as shown in Figure 52.

|         | Description     | Enable the SAFE RESITOR value check. If the SAFE resitor value is diferent of the range selected this will set a<br>DEBUG mode or if a mismatch error between this config and the resistior range, this register will define the safe |       |              |       |              |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|--------------|

| SAFE RE | Default state   | Disable                                                                                                                                                                                                                               | Res   | istor at DBG | pin   | SAFE MODE    |

| S S     | 0xx             | Disable (additionaly in DEBUG mode disable the SAFE mode detections)                                                                                                                                                                  | MIN   | TYP          | MAX   | O/ II E MODE |

| [2:0]   | 100             | After bus idle detection AND ignition signal low=> Turn Vdd OFF +WU enable                                                                                                                                                            | 57.5k | 68k          |       | B3           |

| [=.0]   | 101             | After ignition signal low=> Tum Vdd OFF + WU enable                                                                                                                                                                                   | 27.5k | 33k          | 34.5k | B2           |

|         | 110             | After bus idle detection=> Turn Vdd OFF + WU enable                                                                                                                                                                                   | 14k   | 15k          | 16.5k | B1           |

|         | 111             | No further action                                                                                                                                                                                                                     |       |              | 6k    | Α            |

|         | Reset condition | Power down (every time VSUV BATFAIL is set)                                                                                                                                                                                           |       |              |       |              |

Figure 52. DBG resistor values for safe mode

One example circuit that can be implemented to run module in debug mode is by populating J27 and leaving J28 'open' in Figure 53, where the zener diode will maintain ~8.0 V on the DBG pin. The MC33903/4/5 also gives the flexibility to get out of debug mode by sending a specific SPI command (this overrides the hard-wired voltage on DBG).

Figure 53. DBG typical application schematic

To run in typical mode (where watchdog has to be monitored), J27 should be left 'open' and J28 can be populated to allow SAFE MODE A functionality. To allow other SAFE MODE implementations, J27 and J28 can be left open and R25 can be interchanged to the corresponding SAFE MODE resistor value given in Figure 52.

# 4.7 CAN and LIN physical layers

The MC33903/4/5 implements one CAN physical layer and zero to two LIN physical layers dependent on part number (see Table 1, Table 2, and Table 3). The numerous variations of devices that combine both CAN and LIN communication protocols give the engineer great flexibility to design high conformance systems ranging from entry level modules to highly integrated high-end modules.

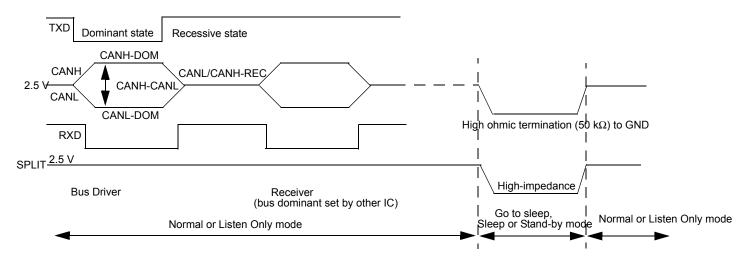

## 4.7.1 CAN

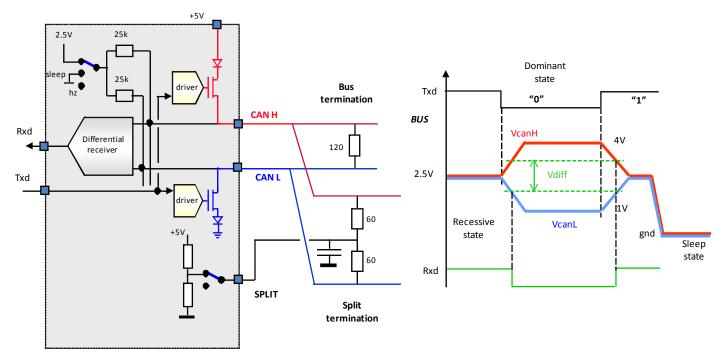

The CAN physical layer interface of the MC33903/4/5 is compliant to the ISO 11898-2 and ISO 11898-5 protocol specifications. This physical layer is specifically supplied by VSUP2 for all devices that have two supply inputs and VSUP for the rest of the devices, which only have a single supply input. The CAN physical layer is internally supplied by the 5V-CAN regulator and communicates with the microcontroller via TxD and RxD. CANH and CANL are biased to 2.5 V when the bus is in recessive state and to GND when the transceiver is in sleep state.

Figure 54. High speed CAN physical interface

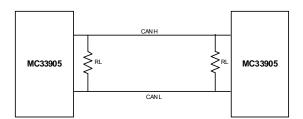

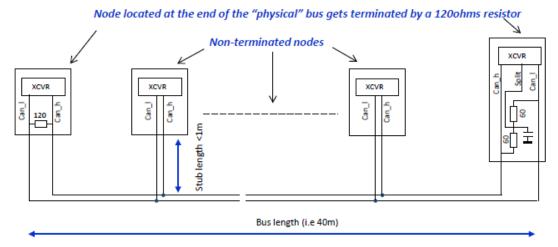

The general CAN network architecture is driven by the ISO 11898 specification and requires that two nodes be terminated with 120  $\Omega$  resistors on both ends of the twisted pair network. As shown in Figure 55.

| Notation         | Unit | Value |      |      | Condition                       |

|------------------|------|-------|------|------|---------------------------------|

|                  |      | min.  | nom. | max. |                                 |

| RL <sup>a)</sup> | 0    | 100   | 120  | 130  | Min. power dissipation: 220 mW. |

a) Dependent on the topology, the Bit rate, and the slew rate deviations from 120 O may be possible. It is, however, necessary to check the applicability of other resistor values in each case. It is furthermore possible to use a single central bus termination. In this case the termination concentrates into one resistor with the value RL/2 offering a power dissipation of at least 440 mW. This central termination might also be implemented using a split termination consisting out of 2 resistors with each RL/4 and at least 220 mW per resistor.

The power dissipation is calculated based on the maximum differential bus voltage of 5V, which is independent from the battery supply system. In case short circuits on the bus wires towards battery have to be supported, the minimum required power dissipation increases depending on the assumed maximum short circuit bus voltage.

Remark: The lower the termination resistor value is the smaller the number of nodes in a network is due to the internal differential resistors of all receivers connected to the bus lines CAN\_H and CAN\_L.

Figure 55. High speed CAN network architecture

The non-terminated nodes should be connected to the network as shown on Figure 56 to comply with the CAN bus network topology as specified by the ISO 11898.

Figure 56. High speed CAN network topology

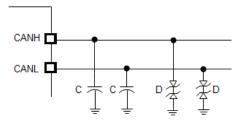

The MC33903/4/5 implements a highly robust CAN interface which can sustain ESD pulses up to +/-8 kV (Human Body Model) at the CANH and CANL pins. If application requires higher ESD voltage robustness, external protection components such as a transient voltage suppressor (TVS) are required to protect these pins. The MMB27VCLT1 (D) is recommended to achieve better ESD results (see Figure 57). Implementing this TVS will improve ESD performance up to +/-15 kV according to ISO 10605-2008 (ESD powered). Additionally, a 47 pF capacitor (C) should be placed on the CANH and CANL pins for noise immunity, ESD, and to lower noise emissions. Figure 58 shows the recommended circuitry for the CAN transceiver.

Figure 57. CANH and CANL ESD external protection typical application schematic

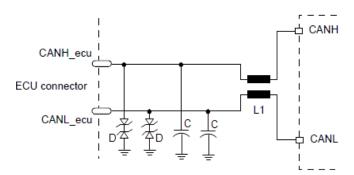

Optionally, a common mode choke (L1) may be implemented on the CAN transceiver if the application requires it. If this is the case, the TDK ACT45B-510 is recommended for noise immunity and emissions. This will increase the immunity for RF noise and lower the noise emitted by the CAN transceiver. Note that the MC33903/4/5 has been EMC certified according to SAE J2962-2 without the need to include a common mode choke on the CAN physical layer.

Figure 58. CANH and CANL typical application schematic

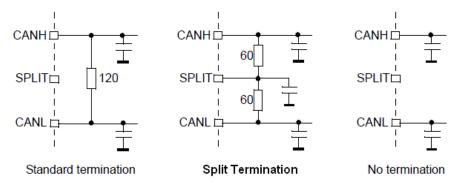

The MC33903/4/5 offers a SPLIT pin that can optionally be implemented to further improve EMC performance and signal stability during recessive state of the CAN bus. This also adds flexibility and various options for connecting the terminating CAN nodes. If SPLIT is not used, it must be left open.

Figure 59. CAN termination options

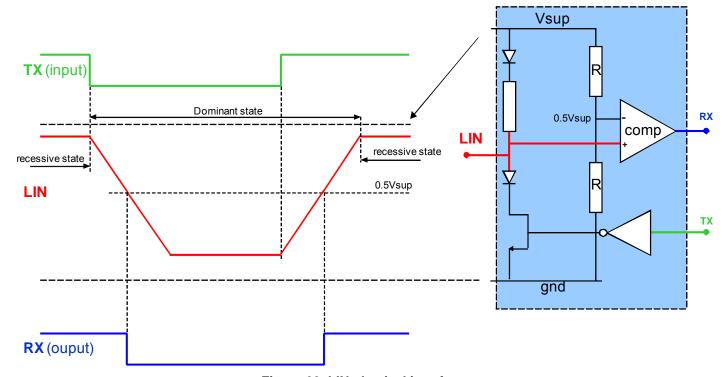

#### 4.7.2 LIN

The MC33903/4/5 offers zero to two LIN transceivers that are compliant to LIN 2.1 and J2602-2 protocol specifications. The LIN interfaces are specifically supplied by VSUP2 for all devices that have two supply inputs and Vsup for the rest of the devices, which only have a single supply input. Similar to the CAN transceiver, the LIN interface communicates with the microcontroller via TxD and RxD, but at slower baud rates and under a different communication protocol.

Figure 60. LIN physical interface

38

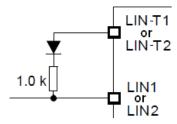

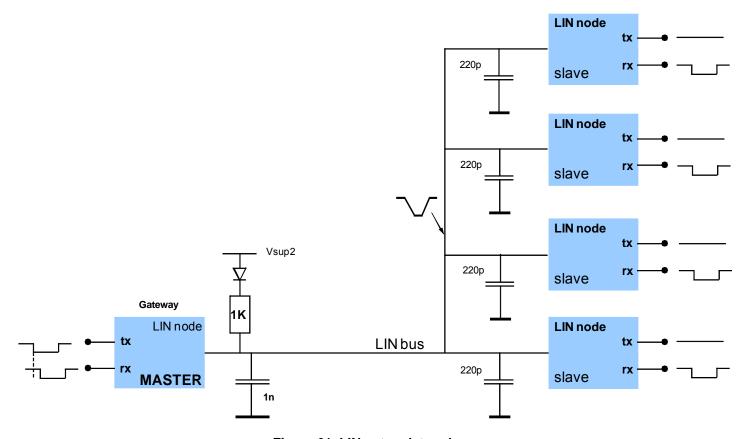

The bus topology is based on single master and multiple slave architecture (see Figure 61). The master module must implement an external 1.0 k $\Omega$  pull-up resistor to VSUP in series with a diode. This is to prevent current flowing from the LIN bus into the module and creating an uncontrolled power supply in case of a 'loss of battery'.

Figure 61. LIN network topology

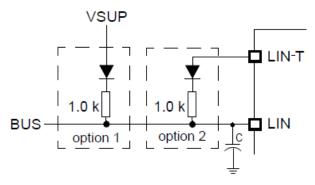

There are two circuitry options for master LIN nodes. The SBC's LIN-Termination pin can be implemented or the 1.0 k $\Omega$  resistor and diode can be connected directly to VSUP (see Figure 62). The recommended diode is 1N4148WS and the resistor can be +/-10% accurate. For better EMC performance, a capacitor must be placed on the LIN pin. The value of this capacitor is subject to OEM approval, it is recommended to have a minimum of 68 pF.

Figure 62. LIN master node application schematic options

# 5 Programming the SBC

Once the module circuitry is all laid out, the designer can then start the software development. The MC33903/4/5 requires some simple, but important initialization and feature configurations that will allow maximizing the functional safety aspects of the SBC. Because the feature set is different dependent on part number, the software may differ from application to application. Note that if the software has been written to drive the MC33905D and exercise all of its features and safety aspects, this same software can be used to drive ANY of the MC33903/4/5 SBCs. The commands that are sent, for which the specific SBC does not have the feature, will be ignored and will not have a negative effect on the module's functionality.

#### 5.1 SPI

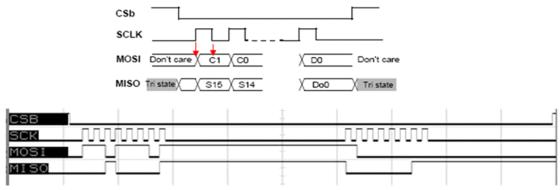

The communication between the SBC and the module's microcontroller is driven by type 2 Serial Peripheral Interface (SPI), where the data is changed on the rising edge of SCLK and sampled on the falling edge as shown on Figure 63.

Figure 63. Serial peripheral interface

Note: SPI does not have daisy chain capability.

Via SPI, the microcontroller can write to specific registers, read these registers to verify content and device status, and additionally it can read any device status flags that may have been set.

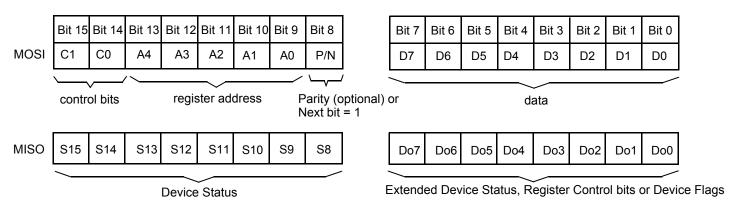

The maximum operating frequency for the SPI bus is 4.0 MHz and it's made up of 16 bits (except for 1 watchdog refresh case). It implements optional parity and any SPI message sent that is not a multiple of 8 clock pulses will be ignored and generate an interrupt. The SPI bus also has  $\overline{\text{CS}}$  short to GND detection. Any SPI message sent will return valid device status data on MISO (i.e. CAN failure, I/O failure, Wake-up, etc.) There are 32 SPI bit register addresses and the overall SPI architecture is as shown on Figure 64.

Figure 64. SPI read and write functionality

Bits 15 and 14 are the control bits to determine if the SPI word sent is a write to register address, read back of the register address, or a read of the device's flags from a register address. Bit 8 is for optional parity selection where a 0 represents no parity and a 1 represents parity is selected. Refer to the datasheet for more parity details.

NXP Semiconductors

40

Table 8. SPI operations (bits 8, 14, & 15)

| Control bits MOSI[15-14], C1-C0 | Type of command                                                                              | Parity/next<br>MOSI[8] P/N | Note for bit 8 P/N                                                                     |  |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|--|--|--|

| 00                              | Read back of register content and block (CAN, I/O, INT, LINs) real time state. See Table 12. | 1                          | Bit 8 must be set to 1, independently of the parity function selected or not selected. |  |  |  |

| 01                              | Write to register address, to control the device operation                                   | 0                          | If bit 8 is set to "0": means parity not selected OR parity is selected AND parity = 0 |  |  |  |

|                                 | the device operation                                                                         | 1                          | if bit 8 is set to "1": means parity is selected AND parity = 1                        |  |  |  |

| 10                              | Reserved                                                                                     |                            |                                                                                        |  |  |  |

| 11                              | Read of device flags form a register address                                                 | 1                          | Bit 8 must be set to 1, independently of the parity function selected or not selected. |  |  |  |

Bits 13 - 9 are the register address bits and are mapped in Table 9.

Table 9. Device registers with corresponding address

| Address<br>MOSI[13-9]<br>A4A0 | Description                              | Quick Ref.<br>Name | Functionality                                                                                                                                                                                                |

|-------------------------------|------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0_0000                        | Analog Multiplexer                       | MUX                | Write "device control bits" to register address.     Read back register "control bits"                                                                                                                       |

| 0_0001                        | Memory byte A                            | RAM_A              |                                                                                                                                                                                                              |

| 0_0010                        | Memory byte B                            | RAM_B              | Write "data byte" to register address.                                                                                                                                                                       |

| 0_0011                        | Memory byte C                            | RAM_C              | 2) Read back "data byte" from register address                                                                                                                                                               |

| 0_0100                        | Memory byte D                            | RAM_D              |                                                                                                                                                                                                              |

| 0_0101                        | Initialization Regulators                | Init REG           |                                                                                                                                                                                                              |

| 0_0110                        | Initialization Watchdog                  | Init<br>watchdog   | Write "device initialization control bits" to register address.                                                                                                                                              |

| 0_0111                        | Initialization LIN and I/O               | Init LIN I/O       | Read back "initialization control bits" from register address                                                                                                                                                |

| 0_1000                        | Initialization Miscellaneous functions   | Init MISC          |                                                                                                                                                                                                              |

| 0_1001                        | Specific modes                           | SPE_MO<br>DE       | Write to register to select device Specific mode, using "Inverted Random Code".      Read "Random Code"                                                                                                      |

| 0_1010                        | Timer_A: watchdog & LP MCU consumption   | TIM_A              |                                                                                                                                                                                                              |

| 0_1011                        | Timer_B: Cyclic Sense & Cyclic Interrupt | TIM_B              | Write "timing values" to register address.     Read back register "timing values"                                                                                                                            |

| 0_1100                        | Timer_C: watchdog LP & Forced Wake-up    | TIM_C              | , , ,                                                                                                                                                                                                        |

| 0_1101                        | Watchdog Refresh                         | watchdog           | Watchdog Refresh Commands                                                                                                                                                                                    |

| 0_1110                        | Mode register                            | MODE               | 1) Write to register to select LP mode, with optional "Inverted Random code" and select Wake-up functionality  2) Read operations:  Read back device "Current mode"  Read "Random Code",  Leave "Debug mode" |

Table 9. Device registers with corresponding address (continued)

| Address<br>MOSI[13-9]<br>A4A0 | Description            | Quick Ref.<br>Name | Functionality                                                                                 |

|-------------------------------|------------------------|--------------------|-----------------------------------------------------------------------------------------------|

| 0_1111                        | Regulator Control      | REG                |                                                                                               |

| 1_0000                        | CAN interface control  | CAN                |                                                                                               |

| 1_0001                        | Input Output control   | I/O                | Write "device control bits" to register address, to select device operation.                  |

| 1_0010                        | Interrupt Control      | Interrupt          | Read back register "control bits".  3) Read device flags from each of the register addresses. |

| 1_0011                        | LIN1 interface control | LIN1               | , g                                                                                           |

| 1_0100                        | LIN2 interface control | LIN2               |                                                                                               |

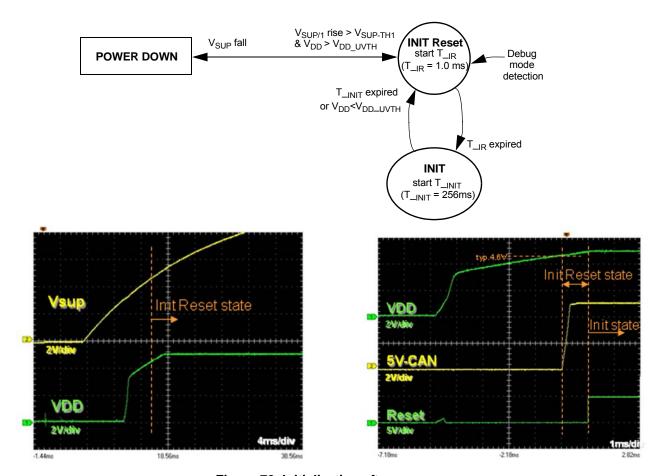

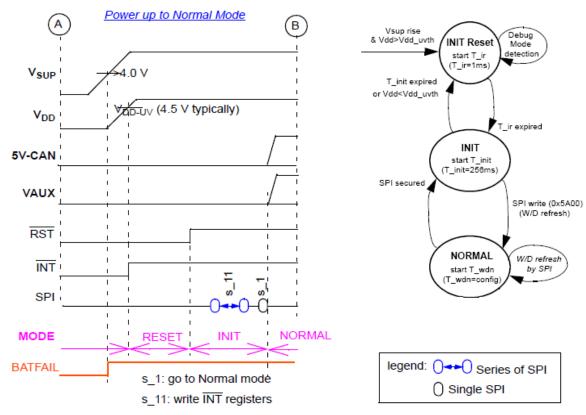

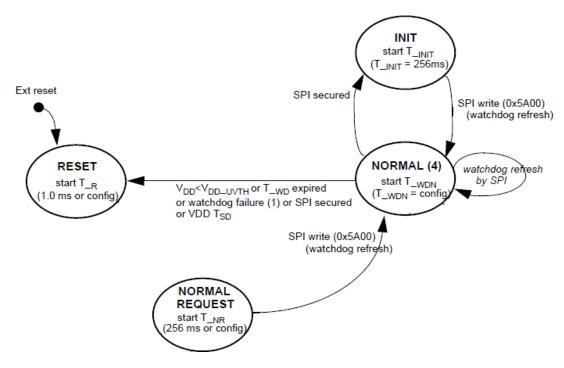

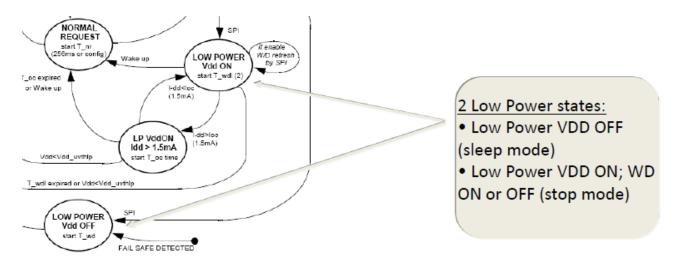

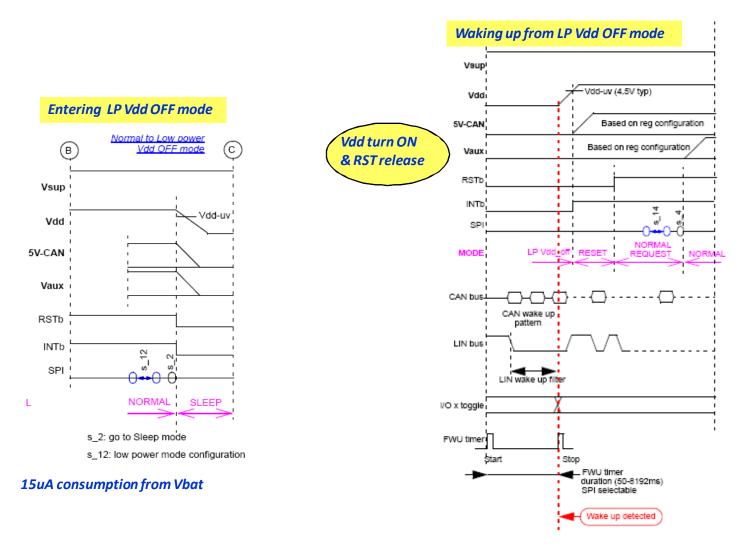

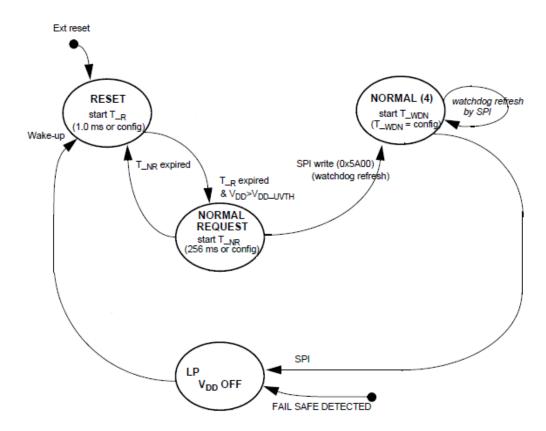

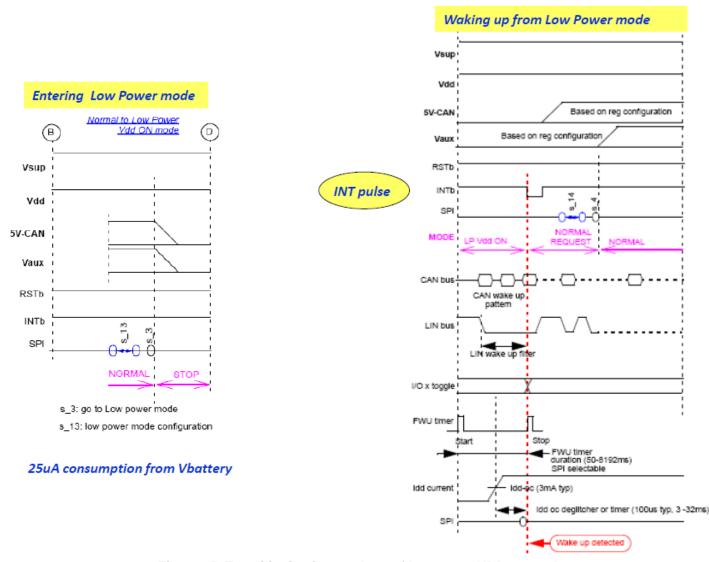

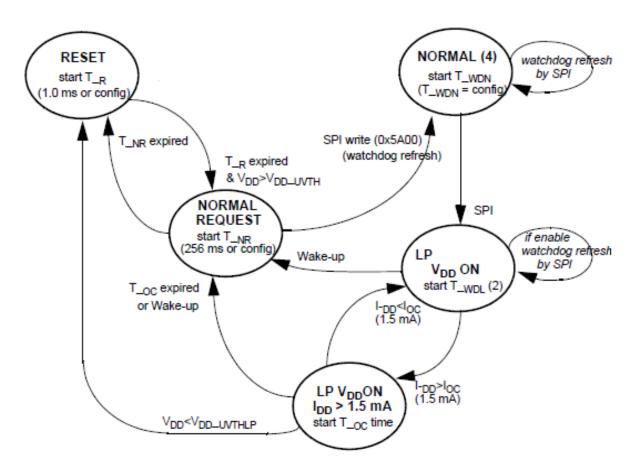

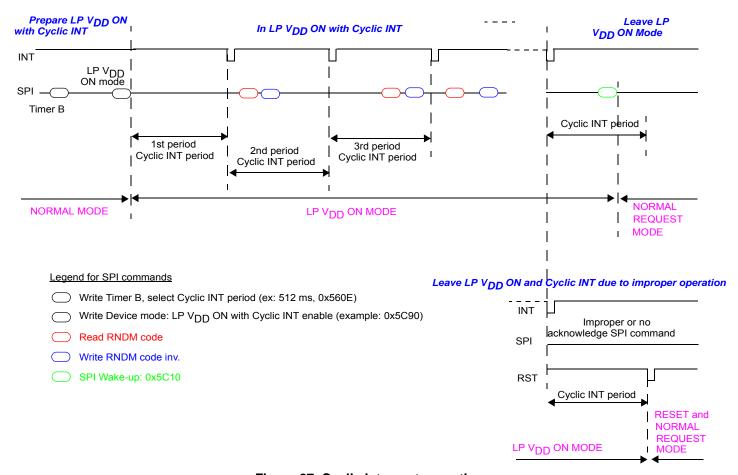

#### 5.2 SBC Modes

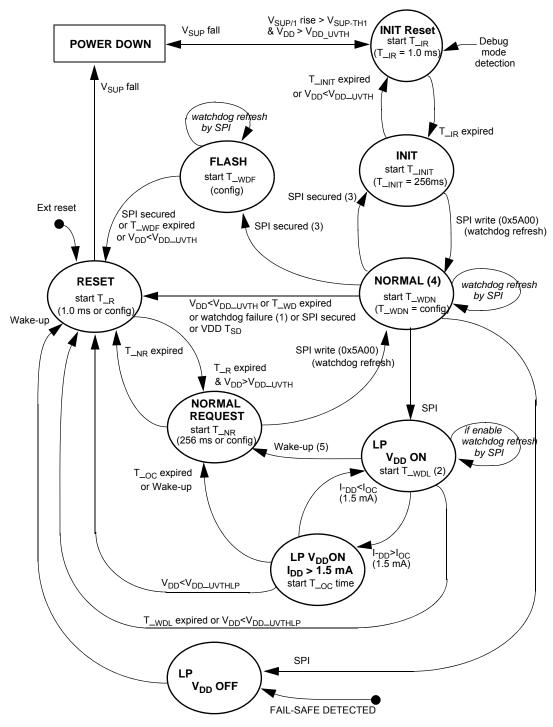

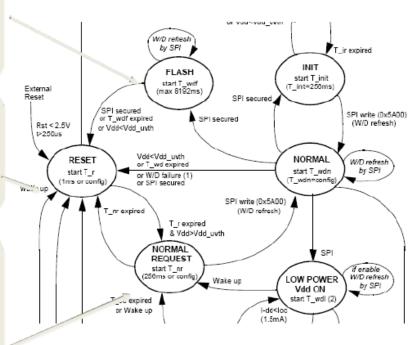

The MC33903/4/5 family of SBCs has various modes of operation to accommodate the majority of module requirements such as low current consumption with microcontroller completely OFF or ON with limited functionality capability, flashing of the module, microcontroller soft start, etc. The SBC has eight different states it can transition through after power up as shown in Figure 65.

Figure 65. State diagram

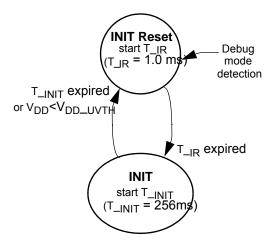

#### 5.2.1 Debug mode

Debug mode is a special operation implementation of the MC33903/4/5 family of SBCs that allows for easy debugging of the software and hardware. When debug mode is detected, all software watchdog operations are disabled. The 256 ms in INIT mode, watchdog refresh of Normal and Flash modes, Normal Request time out (256 ms or user defined) are disabled and do not lead into an INIT Reset or Reset mode transition. When the SBC is running in debug mode, a SPI command can be sent without any watchdog operation time constraints. The MCU software can be debugged in real-time and halted when necessary to verify proper operation.

**Note:** SAFE mode functionality is also available in debug mode operation. In this case, the SBC will activate SAFE mode B2 as shown in Figure 70 (regardless of the resistor value on the DBG pin).

To set the device in Debug mode, 8.0 V to 10 V must be applied on the DBG pin before powering up the SBC. When the SBC transitions from INIT Reset into INIT mode, it will detect if the voltage at the DBG pin is within the specified 8.0 V - 10.0 V range.

Figure 66. Init reset and INIT state diagram

If debug voltage condition is met, the SBC will activate the debug mode operation. The debug status of the device is reported via a flag in the Device Modes register (0xDD80). See Table 10 for more details.

**Table 10. Device Modes**

| Global commands and effects                                             |      |            |           |                     |           |             |          |       |

|-------------------------------------------------------------------------|------|------------|-----------|---------------------|-----------|-------------|----------|-------|

|                                                                         | MOSI | bits 15-14 | bits 13-9 | bit 8               | bit 7     |             | bits 6-0 |       |

| Read device current mode, Leave debug mode.                             |      | 00         | 01 110    | 1                   | 0         |             | 000 0000 |       |

| Keep SAFE pin as is.  MOSI in hexadecimal: 1D 00                        | MISO | bit        | 15-8      | bit                 | 7-3       |             | bit 2-0  |       |

|                                                                         |      | Fix S      | Status    | device cur          | rent mode | Random code |          |       |

|                                                                         | MOSI | bits 15-14 | bits 13-9 | bit 8               | bit 7     | bits 6-0    |          |       |

| Read device current mode                                                |      | 00         | 01 110    | 1                   | 1         |             | 000 0000 |       |

| Release SAFE pin (turn OFF).  MOSI in hexadecimal: 1D 80                | MISO | bit        | 15-8      | bit                 | 7-3       | bit 2-0     |          |       |

|                                                                         |      | Fix S      | Status    | device cur          | rent mode | Random code |          |       |

|                                                                         | MOSI | bits 15-14 | bits 13-9 | bit 8               | bit 7     |             | bits 6-0 |       |

| Read device current mode, Leave debug mode.  Keep SAFE pin as is.       |      | 11         | 01 110    | 1                   | 0         |             | 000 0000 |       |

| MOSI in hexadecimal: DD 00 MISO reports Debug and SAFE state (bits 1,0) | MISO | bit        | 15-8      | bit 7-3             |           | bit 2       | bit 1    | bit 0 |

|                                                                         |      | Fix S      | Status    | device current mode |           | Х           | SAFE     | DEBU  |

Table 10. Device Modes (continued)

| Global commands and effects                                               |      |            |           |            |           |          |          |       |

|---------------------------------------------------------------------------|------|------------|-----------|------------|-----------|----------|----------|-------|

|                                                                           | MOSI | bits 15-14 | bits 13-9 | bit 8      | bit 7     |          | bits 6-0 |       |

| Read device current mode, Keep DEBUG mode<br>Release SAFE pin (turn OFF). |      | 11         | 01 110    | 1          | 1         | 000 0000 |          |       |

| MOSI in hexadecimal: DD 80 MISO reports Debug and SAFE state (bits 1,0)   | MISO | bit 15-8   |           | bit 7-3    |           | bit 2    | bit 1    | bit 0 |

|                                                                           |      | Fix S      | Status    | device cur | rent mode | Х        | SAFE     | DEBUG |

If the voltage on the DBG pin falls below the specified 8V, the SBC will exit debug mode, all the watchdog operations are enabled, and a proper watchdog refresh is expected. The SBC can also exit out of debug mode by reading the Device Modes register (0xDD00) as specified in Table 10. This SPI command has priority over the voltage measured on the DBG pin and is especially useful when the module requires exiting out of debug mode regardless of the hardware configuration.

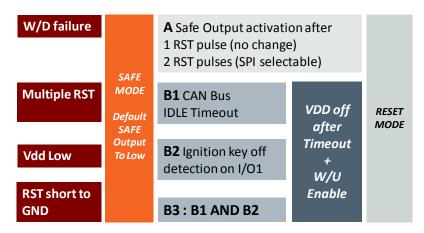

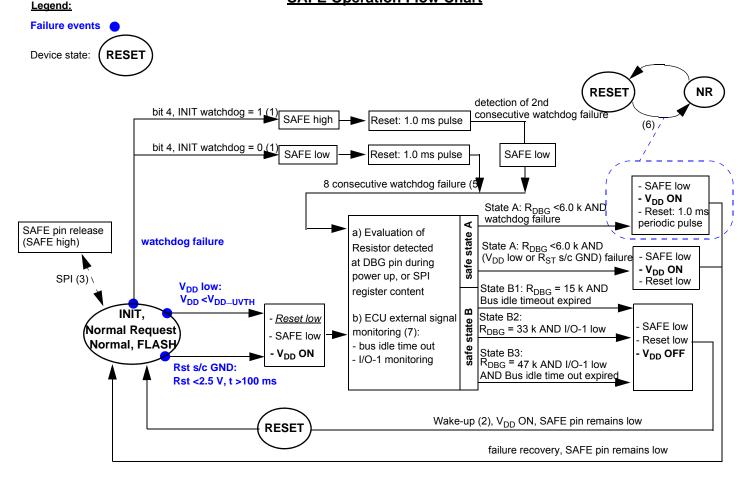

#### 5.2.2 SAFE Modes

The MC33903/4/5 family of SBC includes four different SAFE modes that are hardware configuration selectable by means of a specific resistor value placed on the DBG pin (see Table 11). These SAFE Modes can also be verified and initialized by software SPI command. The INIT MISC register allows for the SAFE mode verification and modification (see Table 16). This functional safety feature provides flexibility to the module designer to implement a robust and safe system. The fast reaction of the SBC to a module fault is predictable and can accommodate for lower power consumption in such event. The SAFE output also provides a 'plan B' in case of a microcontroller failure where the module will be placed in a known state.

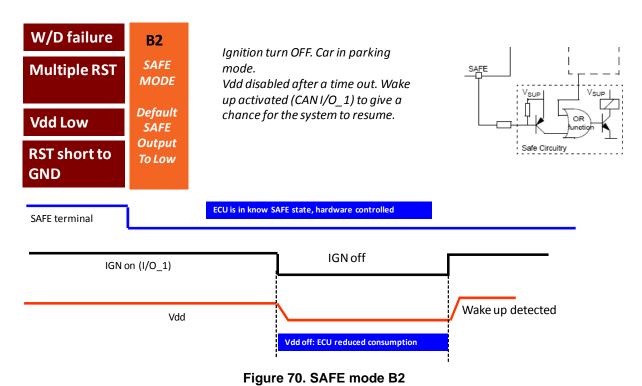

Note: SAFE mode functionality is also available in debug mode operation. In this case, the SBC will activate SAFE mode B2 as shown in Figure 70 (regardless of the resistor value on the DBG pin).

Table 11. Fail-safe Options

| Resistor at DBG pin | SPI coding - register INIT MISC bits [2,1,0] (higher priority that resistor coding)                                         | Safe mode code | V <sub>DD</sub> status                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------|

| <6.0 k              | bits [2,1,0) = [111]: verification enable: resistor at DBG pin is typically 0 k $\Omega$ (RA) - Selection of SAFE mode A    | А              | remains ON                                                                             |

| typically<br>15 k   | bits [2,1,0) = [110]: verification enable: resistor at DBG pin is typically 15 k $\Omega$ (RB1) - Selection of SAFE mode B1 | B1             | Turn OFF 8.0 s after CAN traffic bus idle detection.                                   |

| typically<br>33 k   | bits [2,1,0) = [101]: verification enable: resistor at DBG pin is typically 33 k $\Omega$ (RB2 - Selection of SAFE mode B2  | B2             | Turn OFF when I/O-1 low level detected.                                                |

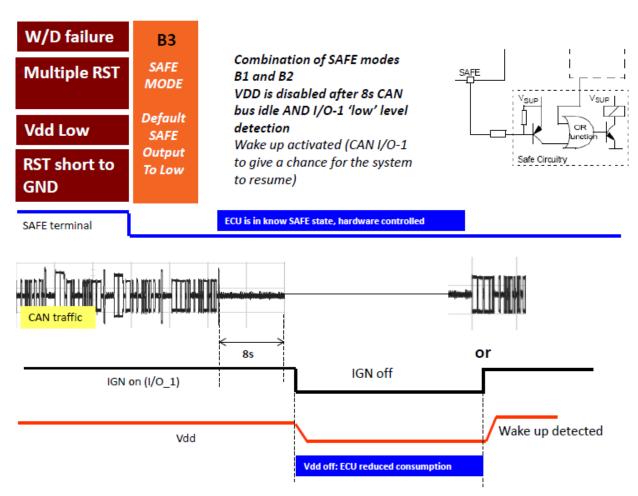

| typically<br>68 k   | bits [2,1,0) = [100]: verification enable: resistor at DBG pin is typically 68 k $\Omega$ (RB3) - Selection of SAFE mode B3 | В3             | Turn OFF 8.0 s after CAN traffic bus idle detection AND when I/O-1 low level detected. |

The SAFE active 'low' output is triggered upon a watchdog failure, multiple resets, VDD low, or if the RST pin is shorted to GND. The SBC reaction to any of these faults will then be dependent on the resistor value on the DBG pin. The V<sub>DD</sub> may remain ON or turn OFF after specified conditions are met (see Table 11).

A, B1, B2, B3 are HW configurable Resistor on DBG pin

Figure 67. Fail-safe modes

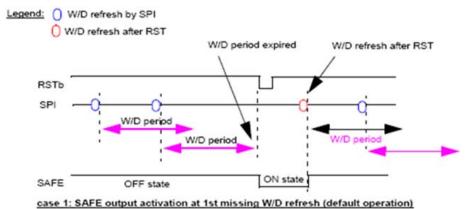

When the SBC goes into SAFE mode A, the VDD remains ON keeping the microcontroller powered up until the failure condition recovers and the microcontroller is then able to properly control the device and refresh the watchdog. The SAFE output activation can be initialized to trigger on the first missing watchdog or on the second consecutive missing watchdog (refer to Figure 68) via the INIT Watchdog register specified in Table 14.

case 2: SAFE output activation at 2nd missing W/D refresh (SPI selectable)

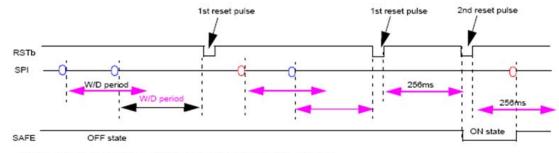

Figure 68. Watchdog and fail-safe operation

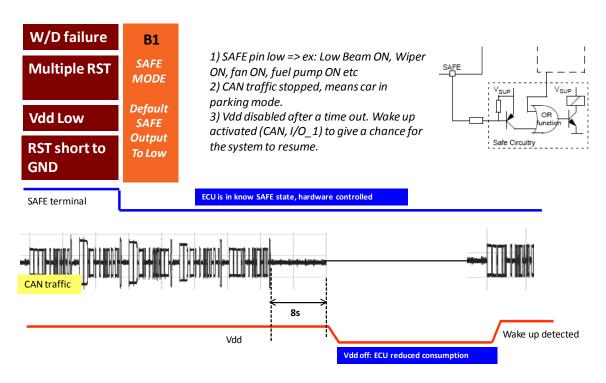

During SAFE mode B1, the VDD will remain ON keeping the microcontroller powered up for as long as the CAN bus is active. The VDD will shut down if CAN bus traffic goes idle for typically 8.0 seconds, but the SBC is CAN and I/O-1 wake-up enabled allowing the system to recover.

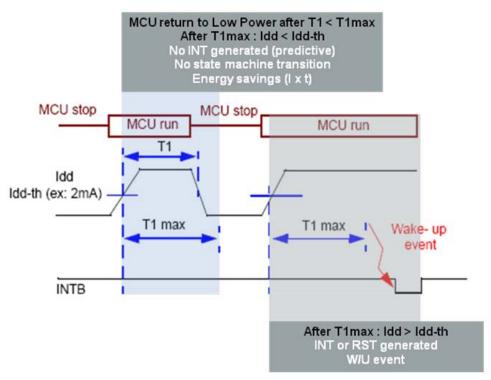

Figure 69. SAFE mode B1