Document Number:AN4852 Rev. 0, Dec 2013

# Using the SENT Transmitter Module in S12ZVC Devices

by: Luis Olea

# **1** Introduction

This application note describes the Single Edge Nibble Transmission (SENT) transmitter module in the <u>S12VC 16-bit</u> <u>microcontroller devices</u>. The fundamentals of the Single Edge Nibble Transmission protocol (SENT, SAE J2716) are discussed in the overview section of the document. The further sections describe in detail how to use the SENT module in a typical application.

# 2 Overview

The Single Edge Nibble Transmission protocol is targeted for use in those applications where high-resolution data is transmitted from a sensor to the ECU. It can be considered as an alternative to conventional sensors providing analog output voltage and for PWM output sensors. It can be also considered as a low-cost alternative to the Local Interconnect Network (LIN) or Controller Area Network (CAN) communication standards.

The electronic power steering, throttle position sensing, pedal position sensing, airflow mass sensing, liquid level sensing applications, etc., can be used as examples of target applications for SENT compatible sensor devices.

#### Contents

| 1 | Introduction                                    | 1 |

|---|-------------------------------------------------|---|

| 2 | Overview                                        | 1 |

| 3 | Using the SENT transmitter module on the S12ZVC |   |

| 4 | Stop mode                                       | 7 |

| 5 | Example software                                | 7 |

| 6 | References                                      | 8 |

© 2013 Freescale Semiconductor, Inc.

# 2.1 SENT Encoding Scheme

SENT is an unidirectional communication standard where data from a sensor is transmitted independently without any intervention of the data receiving device (e.g. the MCU). A signal transmitted by the sensor consists of a series of pulses, where the distance between consecutive falling edges defines the transmitted 4-bit data nibble representing values from 0 to 15. Total transmission time is dependent on transmitted data values and on clock variation of the transmitter (sensor). A consecutive SENT transmission starts immediately after the previous transmission ends (the trailing falling edge of the SENT transmission CRC nibble is also the leading falling edge of the consecutive SENT transmission Synchronization/Calibration nibble, see Figure 1).

A SENT communication fundamental unit of time (unit time - UT, nominal transmitter clock period) can be in the range of 3 microseconds to 10 microseconds, according to the SAE J2716 specification. The maximum allowed clock variation is  $\pm 20\%$  from the nominal unit time which allows the use of low-cost RC oscillators in the sensor device.

#### NOTE

A three microsecond fundamental unit time will be considered as nominal for unification of further timing descriptions.

The transmission sequence consists of the following pulses:

- 1. Synchronization/Calibration pulse (56 unit times)

- 2. 4-bit Status nibble pulse (12 to 27 unit times)

- 3. Up to six 4-bit Data nibble pulses (12 to 27 unit times each)

- 4. 4-bit Checksum nibble pulse (12 to 27 unit times)

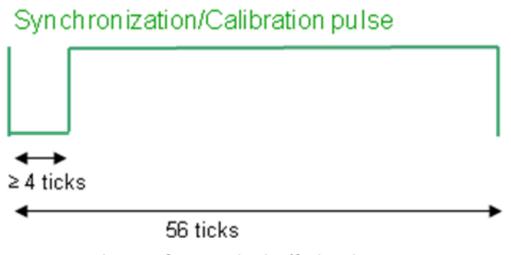

### 2.1.1 Synchronization/Calibration Pulse

Since the SAE J2716 specification allows a  $\pm 20\%$  transmitter clock deviation from the nominal unit time, the Synchronization/Calibration pulse provides information on the actual transmitter (sensor) unit time period. The time between Synchronization/Calibration pulse falling edges defines 56 unit time periods. The receiver can calculate the actual unit time period of the sensor from the pulse width, and can thus re-synchronize. The actual sensor data is measured during the Synchronization/Calibration pulse duration.

The pulse starts with the falling edge and remains low for five or more unit times. The remainder of the pulse width is driven high.

Figure 1. Synchronization/Calibration pulse

Using the SENT Transmitter Module in S12ZVC Devices, Rev. 0, Dec 2013

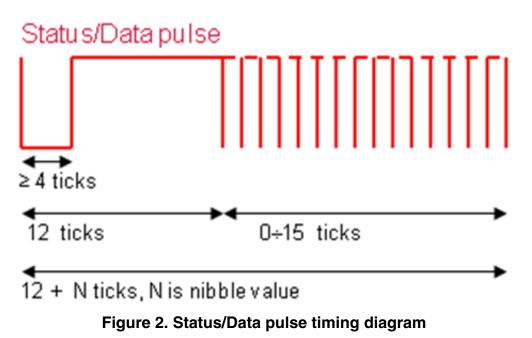

### 2.1.2 Status and Communication Nibble Pulse

The Status nibble contains 4-bit status information of the sensor (e.g. fault indication and mode of operation). It can also contain a serial message (one bit as a serial data bit, one bit as a start bit). The complete 16-bit serial message is then transmitted in 16 consecutive SENT transmissions (refer to SAE J2716 at www.sae.org for detailed description).

The width of the Status nibble pulse is dependent on the nibble value. The status nibble pulse and data nibble pulse formats are identical. Refer to Data Nibble Pulse.

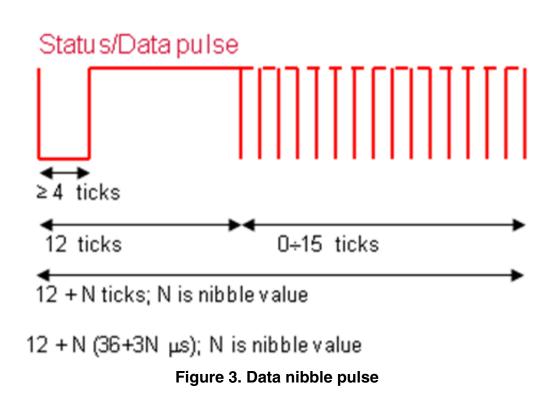

### 2.1.3 Data Nibble Pulse

A single data nibble pulse carries 4-bit sensor data. A maximum of six data nibbles can be transmitted in one SENT transmission. The total number of data nibbles depends on the size of the data provided by the sensor and this is fixed during the sensor operation.

The width of the data nibble pulse is dependent on the nibble value. The pulse starts with the falling edge and remains low for five or more unit times. The remainder of the pulse width is driven high. The next pulse falling edge occurs after 12 unit times from the initial falling edge plus the number of unit times equal to the nibble value. The data pulse width in the number of unit times is defined.

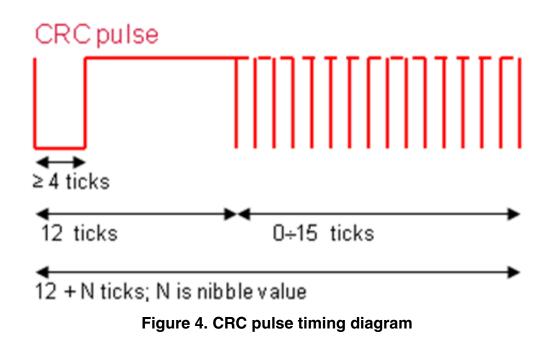

### 2.1.4 Checksum Nibble Pulse

The checksum nibble contains a 4-bit CRC. The checksum is calculated using the  $x^4 + x^3 + x^2 + 1$  polynomial with the seed value of 5 (0b0101), and is calculated over all nibbles except for the status and communication nibble (according to SAE J2716).

The CRC allows detection of the following errors:

- 1. All single bit errors.

- 2. All odd number of errors.

- 3. All single burst errors of length  $\leq 4$ .

- 4. 87.5% of single burst errors of length = 5.

- 5. 93.75% of single burst errors of length > 5.

Refer to SAE J2716 (www.sae.org) for more information about the SENT CRC polynomial error detection.

# 2.2 SENT physical layer

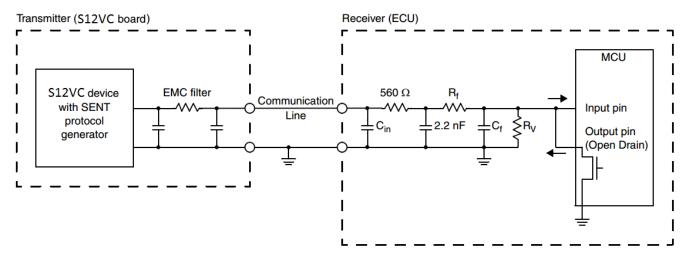

The recommended SENT receiver circuit is illustrated in the following diagram:

#### Figure 5. SENT physical layer recommended circuit

The receiver input is formed by the parasitic capacitance of the input pin and its ESD protection, and the 560  $\Omega/2.2$  nF EMC low-pass filter to suppress RF noise coupled to the communication line. The open-drain output pin on the MCU pulls down the communication line to generate the master trigger pulse.

The transmitter provides a bidirectional open-drain I/O pin with an EMC filter to suppress the RF noise coupled to the communication line. The communication line is pulled down by its output driver to generate the SENT pulse sequence.

Signal shaping is required to limit the radiated emissions. The maximum limits for the falling and rising edge durations are  $TFALL = 6.5 \ \mu s$  and  $TRISE = 18 \ \mu s$  with a maximum allowed 0.1  $\mu s$  falling edge jitter.

#### using the SENT transmitter module on the S12ZVC

The overall resistance of all connectors is limited to 1  $\Omega$ , the bus wiring to 0.1 nF/m capacitance, and the maximum cable length to 5 m. The transmitter-receiver network devices are protected from short-to-ground and short-to-supply conditions. Upon recovery from these faults, normal operation is resumed.

# 3 Using the SENT transmitter module on the S12ZVC

The following sections provide an example of how application software may initialize the SENT transmitter module and start transmitting data on an S12ZVC. Example software AN4852SW.zip can be downloaded from freescale.com.

### 3.1 Initialization

All configuration options need to be defined before enabling the transmitter. This is the recommended initialization sequence:

- 1. Configure the SENT tick rate in the TICKRATE register.

- 2. Set required Pause-Pulse options in the PPULSE register.

- 3. Define all protocol related configuration options in the CONFIG register (number of data nibbles, CRC method). Enable the transmitter and lock all static configuration bits in the TICKRATE, PPULSE and CONFIG registers by clearing the CONFIG[TXINIT] bit. Writing configuration bits in CONFIC and clearing CONFIG[TXINIT] can be done in a single write access to the CONFIG register.

- 4. Set interrupt enable bits in the interrupt enable register (INTEN) as required by the chosen transfer mode.

### 3.2 Sending data

To send data simply write it to the transmit buffer register (TXBUF) and clear the transmit buffer empty bit (INTFLG[TBE]) to start the transmission. The following sections describe the transmission options that are supported by the hardware.

### 3.2.1 Single or double buffered transmission option

The option to have a single or double buffered transmitter allows the software designer to choose between the different advantages when programming an application.

Double buffer transmission offers the time of an entire message for the software to prepare the data (typically about 200 unittime ticks, depending on message length). The down side is that the data is relatively old when it gets transmitted, given that it was prepared while the previous message was sent.

Single buffer transmission has the capability to transmit the most up-to-date data. The disadvantage is that the preparation of the transmit data has to occur in a shorter time (less than the length of the calibration pulse, which is 56 unit-time ticks) compared to the double buffered transmission option.

### 3.2.2 Pause pulse option

The pause pulse is an idle time after the checksum nibble pulse of each message. This time makes the message periods longer so that software can have more time to prepare new data. To configure the pause pulse do the following steps:

- 1. Set the pause pulse count ticks in PPULSE[PPCOUNT] bit field.

- 2. Choose fixed or adapted pause pulse length:

- If PPULSE[PPFIXED] is set to 1, the pause length is fixed to the number of ticks defined by PPULSE[PPCOUNT], any value smaller than 12 is taken as 12 (this is the minimum pause length).

- If PPULSE[PPFIXED] is set to 0, the pause length set in PPCOUNT is the tick length of the entire message, meaning that the pause pulse will vary according to message data length so that all messages have a fixed tick time. If the entire message is less than 12 ticks wide then a minimum pause pulse of 12 ticks is appended.

- 3. Enable the pause pulse setting PPULSE[PPEN] = 1.

#### NOTE

For SENT a fixed or adapted pause pulse must not be longer than 768 ticks.

### 3.2.3 Automatic or software triggered transmission

When CONFIG[SINGLE]=0 automatic transmission is enabled. This is the default mode of transmission, which consists in back-to-back continuously transmitted messages.

When CONFIG[SINGLE]=1, software triggered transmission is enabled. This gives the application the possibility to synchronize message transmission to events external to the SENT module, such as timers or interrupts.

Software triggered transmission eliminates the possible occurrence of an underflow because the transmission does not start until the application decides to transmit the data.

To transmit data using software triggered transmission:

- 1. Initialize SENT module (see Initialization) with software triggered mode (CONFIG[SINGLE]=1).

- 2. Load data in the transmit buffer (TXBUF[DATA]).

- 3. Clear the transmit buffer empty flag (INTFLG[TBE]=0).

#### NOTE

This mode requires the pause pulse to be enabled.

# 4 Stop mode

In Stop mode the bus clock of the S12ZVC device is stopped. Therefore any ongoing SENT transmission is aborted and the SENT TX out pin goes idle when a transition to Stop mode occurs. Software should take care of doing a proper Stop mode handling since an aborted message will be perceived as a transmitter reset.

Use one of the following options for doing a safe transition to Stop mode:

- If using software triggered transmission mode, or single and double buffered transmission with pause pulse, the software can simply wait until the transmission is completed before going to Stop mode. Check the Pause pulse rising edge flag to be set (INTFLG[PPRE]=1) before going to Stop mode.

- When in modes that have no pause pulse, the only way to Stop transmission is to let the transmitter go into under-run error by not providing new data for transmission. This stops the transmission at the end of the calibration pulse of a new message. Software can wait for this condition to go into Stop mode. After wake up the software must handle the under-run condition before transmitting SENT messages again.

### 5 Example software

This application note includes the software that carries out the initialization described in Initialization and Sending data.

For your use with this application note please download AN4852SW.zip from freescale.com.

# 6 References

For your reference, see the following documents related to SENT protocol:

- AN4219: SENT/SPC driver for MPC5510 Microcontroller family, available in freescale.com

- AN4432: SEND/SPC Driver for the MPC560xP and MPC564xL Microcontroller Families, available in freescale.com

- SAE J2716: Single edge nibble transmission for automotive applications, available in http://www.sae.org

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductors products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claims alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-complaint and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

$\label{eq:FreescaleTM} Freescale TM and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.$

© 2013 Freescale Semiconductor, Inc.

Document Number: AN4852 Rev. 0, Dec 2013