**Errata sheet**

# **Document information**

| Info     | Content                                                                                                                                                          |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Keywords | LPC834M101FHI33; LPC832M101FDH20; LPC83x errata                                                                                                                  |  |

| Abstract | This errata sheet describes both the known functional problems and any deviations from the electrical specifications known at the release date of this document. |  |

|          | Each deviation is assigned a number and its history is tracked in a table.                                                                                       |  |

ES\_LPC83x

# **Errata sheet LPC83x**

# **Revision history**

| Rev | Date     | Description                                                                                             |

|-----|----------|---------------------------------------------------------------------------------------------------------|

| 1.2 | 20220104 | Added BOD.1 details in <u>Section 5 "Errata notes"</u> .                                                |

|     |          | • Added '1B' in <u>Table 1 "Device revision table"</u> and <u>Table 2 "Functional problems table"</u> . |

| 1.1 | 20180403 | Added VDD.1                                                                                             |

| 1   | 20160606 | Initial version                                                                                         |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

# 1. Product identification

The LPC83x devices typically have the following top-side marking:

The LPC83x devices typically have the following top-side marking for HVQFN33 packages:

83xF

XXXX XXXX

yywwxR

The last two letters in the last line (field 'xR') identify the boot code version and device revision.

Table 1. Device revision table

| Revision identifier (xR) | Revision description    |

|--------------------------|-------------------------|

| '1A'                     | Initial device revision |

| '1B'                     | Second device revision  |

Field 'yy' states the year the device was manufactured. Field 'ww' states the week the device was manufactured during that year.

# 2. Errata overview

# Table 2. Functional problems table

| Functional problems | Short description                                                                                                           | Revision identifier | Detailed description |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|

| DPD.2               | Deep power-down mode is not functional outside certain voltage and temperature ranges.                                      | '1A', 1B'           | Section 3.1          |

| SYSOSC.2            | When using an external crystal oscillator, the $V_{\text{DD}}$ supply voltage must be 1.9 V or above.                       | '1A', 1B'           | Section 3.2          |

| UART.1              | The UART controller sets the Idle status bits for receive and transmit before the transmission of the stop bit is complete. | '1A', 1B'           | Section 3.3          |

| VDD.1               | The minimum wait time of the power supply ramp must be minimum 2 ms.                                                        | '1A', 1B"           | Section 3.4          |

# Table 3. AC/DC deviations table

| AC/DC deviations | Short description | Detailed description |

|------------------|-------------------|----------------------|

| n/a              | n/a               | n/a                  |

# Table 4. Errata notes

| Note | Short description                                                                                                              | Detailed description |

|------|--------------------------------------------------------------------------------------------------------------------------------|----------------------|

|      | Brown-out detect (BOD) peripheral (reset and interrupt) is not functional for temperatures below -20 °C for 0.4% of the parts. | Section 5.1          |

Errata sheet LPC83x

#### **Functional problems detail** 3.

# 3.1 DPD.2

### Introduction:

The LPC83x has a supply voltage (V<sub>DD</sub>) from 1.8 V to 3.6 V and can operate from -40 °C to 85 °C. The LPC83x supports four reduced power modes (sleep, deep-sleep, power-down, and deep power-down mode). Deep power-down mode allows for maximal power savings where the entire system is shut down except for the general purpose registers in the PMU and the self wake-up timer. Only the general purpose registers in the PMU maintain their internal states in deep power-down mode.

### **Problem:**

At temperatures  $\leq$  25 °C, the deep power-down mode is not functional if the  $V_{DD}$  supply voltage is > 3.4 V. At temperatures > 25 °C, the deep power-down mode is not functional if the  $V_{DD}$  supply voltage is > 3.35 V.

### Work-around:

Deep power-down mode operates correctly for the entire temperature range (-40 °C to 85 °C) if the VDD supply is between 1.8 V and 3.35 V. For temperatures ≤ 25 °C, ensure that the supply voltage is not > 3.4 V (V<sub>DD</sub> = 1.8 V to 3.4 V) when using deep power-down mode. For temperatures > 25 °C, ensure that the supply voltage is not > 3.35 V (V<sub>DD</sub> = 1.8 V to 3.35 V) when using deep power-down mode.

### 3.2 SYSOSC.1

### Introduction:

On the LPC83xM, the  $V_{DD}$  supply voltage range is from 1.8 V to 3.6 V. The LPC83xM has various clock sources such as the internal oscillator (IRC), system oscillator, CLKIN, and watchdog oscillator.

An external crystal oscillator can be connected between the XTALIN and XTALOUT pins to use the system oscillator as a clock source. The system oscillator can also be bypassed by setting the BYPASS bit in the SYSOSCCTRL register, and an external clock source can be fed directly to the XTALIN pin.

#### **Problem:**

An external crystal oscillator connected to the system oscillator does not function when the  $V_{DD}$  power supply is below 1.9 V.

#### Work-around:

The  $V_{DD}$  supply voltage must be 1.9 V or above when connecting an external crystal oscillator to the system oscillator. If the  $V_{DD}$  supply voltage is below 1.9 V, an external clock source can be fed to the XTALIN by bypassing the system oscillator or the other clock sources mentioned above can be used.

### 3.3 **UART.1**

# Introduction:

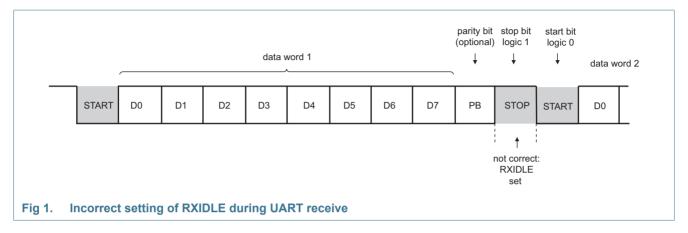

In receive mode, the UART controller provides a status bit (the RXIDLE bit in the UART STAT register) to check whether the receiver is currently receiving data. If RXIDLE is set, the receiver indicates it is idle and does not receive data.

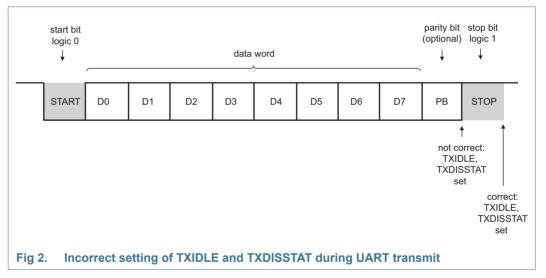

In transmit mode, the UART controller provides two status bits (TXIDLE and TXDISSTAT bits in the UART STAT register) to indicate whether the transmitter is currently transmitting data. The TXIDLE bit is set by the controller after the last stop bit has been transmitted. The TXDISSTAT bit is set by the controller after the transmitter has sent the last stop bit and has become fully idle following a transmit disable executed by setting the TXDIS bit in the UART CTRL register.

The status bits can be used to implement software flow control, but their setting does not affect normal UART operation.

#### **Problem:**

The RXIDLE bit is incorrectly set for a fraction of the clock cycle between the reception of the last data bit and the reception of the start bit of the next word, that is while the stop bit is received. RXIDLE is cleared at the beginning of the start bit.

Both, TXIDLE and TXDISSTAT are set incorrectly between the last data bit and the stop bit while the transfer is still ongoing.

# Work-around:

When writing code that checks for the setting of any of the status bits RXIDLE, TXIDLE, TXDISSTAT, check the value of the status bit in the STAT register:

- If status bit = 1, add a delay of one UART bit time (if STOPLEN = 0, one stop bit) or two bit times (if STOPLEN = 1, two stop bits) and check the value of the status bit again:

- If status bit = 1, the receiver is idle.

- If status bit = 0, the receiver is receiving data.

- If the status bit = 0, the receiver is receiving data.

# 3.4 VDD.1

## Introduction:

On the LPC83x, the  $V_{DD}$  supply voltage range is from 1.8 V to 3.6 V. The LPC83x datasheet specifies a power-up ramp condition for the user application. Before ramping up, the minimum wait time ( $t_{wait}$ ) of the power supply on the  $V_{DD}$  pin (200 mV or below) is 12  $\mu$ s.

### Problem:

The device might not always start-up if the minimum wait time ( $t_{wait}$ ) is 12  $\mu$ s. The required minimum time ( $t_{wait}$ ) specification is 2 ms.

### Work-around:

None.

# 4. AC/DC deviations detail

n/a

# 5. Errata notes

# 5.1 BOD.1

Brown-out detect (BOD) peripheral (reset and interrupt) is not functional for temperatures below -20 °C for 0.4% of the parts. No workaround on device revision '1A'. Issue is fixed on '1B'.

# **Errata sheet LPC83x**

#### **Contents** 6.

| 1   | Product identification 3     | 3.4 | VDD.1                   |

|-----|------------------------------|-----|-------------------------|

| 2   | Errata overview 3            | 4   | AC/DC deviations detail |

| 3   | Functional problems detail 4 | 5   | Errata notes            |

|     | DPD.2 4                      |     |                         |

| 3.2 | SYSOSC.1                     | 6   | Contents 9              |

| 3.3 | UART 1 5                     |     |                         |

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

**Limited warranty and liability** — Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFIRE, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, μVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks

Table continues on the next page...

and service marks licensed by Power.org. M, M Mobileye and other Mobileye trademarks or logos appearing herein are trademarks of Mobileye Vision Technologies Ltd. in the United States, the EU and/or other jurisdictions.

© NXP B.V. 2016-2022.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 13 April 2022 Document identifier: ES\_LPC83X