# S32G3 VEHICLE NETWORK PROCESSING REFERENCE DESIGN BOARD (S32G-VNP-GLDBOX3)

The S32G-VNP-GLDBOX3 is a compact, highly optimized and integrated reference design board featuring S32G vehicle network processor. With its highperformance computing capacity and rich input/output (I/O), this board can provide reference for a variety of automotive applications such as service-oriented gateways, vehicle central compute, domain controllers, safety processors and black boxes. Carmakers, suppliers and software ecosystem partners can directly use the RDB to help accelerate development for shorter time-to-market.

## **TECHNICAL HIGHLIGHTS**

- Supports service-oriented gateway, vehicle compute and domain controller applications

- Hardware Security Engine (HSE), Ethernet Packet Forwarding Engine (PFE), and Low Latency Communications Engine (LLCE)

- Multiple network interfaces with 18 CAN/CAN FD and 12 Ethernet ports

- Supports low-power mode and multiple wake-up sources

- Strengthens safety design with power management

## FEATURES

- Hardware key features:

- 1x NOR flash (64 MB) 1 x eMMC (32 GB), 1x SD card slot

- 1x LPDDR4 (4 GB)

- 6x 100BASE-T1 Ethernet

| 140 |       |

|-----|-------|

|     | 2.000 |

- 4x 1000BASE-T Ethernet

- 1x 1G/2.5GBASE-T Ethernet

- 1x 100BASE-TX Ethernet

- 16x LLCE\_CAN, 2 x FlexCAN

- 4x LLCE\_LIN, 1 x LINFlexD

- 1x FlexRay

- 1x USB 2.0

- 5x ADC,

- 1x DSPI, 1x I2C, 1xWKUP

- 1x PCle X1

- 1x M.2 M-key, 1x M.2 E-key

- On-board chip functional safety features:

- ASIL D S32G399A vehicle network processor

- ASIL D VR5510 power management IC

- ASIL D PF53 core supply regulator

- ASIL B SJA1110A Ethernet switch

## **ENABLEMENT TOOLS**

- NXP S32 Design Studio, Yocto, EB Tresos™

- Linux<sup>®</sup>, FreeRTOS<sup>™</sup>, Real-Time Drivers (RTD)

- S32G Vehicle Integration Platform (GoldVIP)

- Compiler: Green Hills®, GCC

- Debugger: Lauterbach, S32G Debug Probe

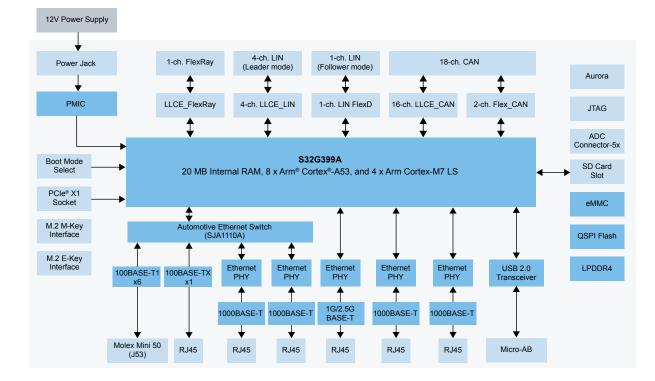

### SYSTEM BLOCK DIAGRAM

#### S32G399A PROCESSOR SPECIFICATIONS

| 4x Arm <sup>®</sup> Cortex <sup>®</sup> -M7 LS pairs and 8x Cortex-A53 cores (opt. cluster LS)                     |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 MB system RAM, 32 KB standby RAM, DRAM I/F,<br>QuadSPI I/F, eMMC/SDXC                                           |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |

| FlexCAN, LINflexD, FlexRay, DSPI, I <sup>2</sup> C, PCle <sup>®</sup> 3.0, USB 2.0                                 |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |

| 1-Gbit GMAC, 3x 2.5-Gbit EMAC (PFE_MAC0, PFE_<br>MAC1, PFE_MAC2),                                                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |

| HSE, XRDC,<br>eFuse, Lifecycle                                                                                     | Safety                                                                                                                                                                                                  | 2x Safe DMA,<br>FCCU and<br>LBIST/MBIST                                                                                                                                                                                                                                                                                     |

| 12-bit SAR ADC, System timer module, software watchdog timer, periodic interrupt timer, FlexTimer, real-time clock |                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                    | cores (opt. cluster<br>20 MB system RA<br>QuadSPI I/F, eMN<br>FlexCAN, LINflex<br>USB 2.0<br>1-Gbit GMAC, 3x<br>MAC1, PFE_MAC<br>HSE, XRDC,<br>eFuse, Lifecycle<br>12-bit SAR ADC,<br>watchdog timer, p | cores (opt. cluster LS)<br>20 MB system RAM, 32 KB standby<br>QuadSPI I/F, eMMC/SDXC<br>FlexCAN, LINflexD, FlexRay, DSPI, I <sup>2</sup><br>USB 2.0<br>1-Gbit GMAC, 3x 2.5-Gbit EMAC (P<br>MAC1, PFE_MAC2),<br>HSE, XRDC,<br>eFuse, Lifecycle<br>12-bit SAR ADC, System timer modu<br>watchdog timer, periodic interrupt ti |

#### www.nxp.com/Goldbox3

NXP, the NXP logo and NXP SECURE CONNECTIONS FOR A SMARTER WORLD are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm and Cortex are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2023 NXP B.V.