ColdFire<sup>®</sup> Embedded Devices

# MCF5227x ColdFire<sup>®</sup> embedded microprocessor

# **Target Applications**

- HVAC building and control systems

- Security and access control systems

- · Lighting control systems

- Test and measurement equipment

- · Environmental and building automation

- Point-of-sale systems

- Operator interfaces

- Patient monitoring systems

- Laboratory equipment

- High-end appliances

### Overview

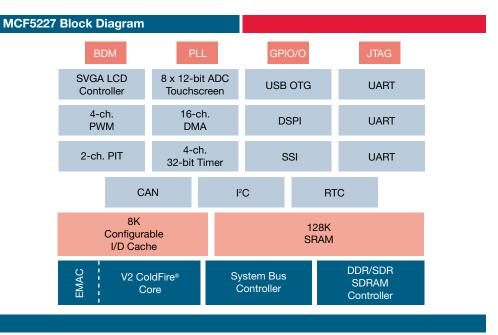

Freescale's MCF5227x ColdFire® microprocessor family is the ideal device for developers looking to add more control options to their consumer or industrial applications. Featuring an integrated LCD controller and touchscreen module, the MCF5227x family is designed to provide an easy way to add support for graphical LCD interfaces to industrial systems. The MCF5227x devices are also equipped with integrated USB On-The-Go (OTG) and CAN modules giving developers the ability to upgrade or standardize their serial communications. The crossbar switch allows the 128K of integrated SRAM to be accessed by the core, DMA, USB OTG and LCD controller, which helps improve performance. These and other features make the MCF5227x devices ideal for human interface applications that require a broad range of peripherals and high performance for multi-functional industrial and consumer applications.

The MCF5227x family is also easy to use. Freescale provides a comprehensive suite of development tools to help developers design in these devices quickly and easily.

# **Cost-Effective Development Tools**

# CodeWarrior<sup>®</sup> Development Studio for ColdFire Architectures V7.0 Complimentary\*\*

CodeWarrior Development Studio for ColdFire Architectures V7.0 is a single tool suite that supports software development for Freescale's ColdFire family of 32-bit products. This support coupled with the cross-platform capabilities of the award-winning CodeWarrior Integrated Development Environment (IDE) simplifies code migration and re-use for faster product development. Processor Expert<sup>™</sup>, a graphical device initialization tool, is also available in the development studio.

## Linux<sup>®</sup> Board Support Package Complimentary\*\*

Linux Board Support Packages (BSPs) for Freescale silicon are tested and certified, ensuring a fully operational tool chain, kernel and board specific modules that are ready to use together within a fix configuration for specific hardware reference platforms. These BSPs provide the foundation you need to begin your project quickly.

### M52277EVB \$449\*

The M52277EVB is a full development system for the MCF5227x microprocessor family. Featuring a 3.5" LCD panel, the M52277EVB allows evaluation of the major features on the MCF5227x devices, including the LCD and touchscreen controller, USB OTG, CAN and several other peripherals.

\*Prices indicated are MSRP \*\*Subject to license agreement

| Part Number    | Temp Ranges    | Package |

|----------------|----------------|---------|

| MCF52277CVM160 | -40°C to +85°C | 196 BGA |

| MCF52274CLU120 | -40°C to +85°C | 176 QFP |

| Features                                                                                                                                           | Benefits                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU and System Configuration                                                                                                                       |                                                                                                                                                                                                                                                        |

| <ul> <li>32-bit V2 ColdFire Central Processing Unit<br/>(CPU) offering 152 MIPS at 160 MHz</li> <li>1.5V Core, 1.8V, 2.5V, 3.3V Bus I/O</li> </ul> | <ul> <li>Offers strong performance and functionality for improved system performance throughout the entire voltage and<br/>temperature range</li> </ul>                                                                                                |

| <ul> <li>Enhanced Multiply Accumulate (eMAC)</li> </ul>                                                                                            | For digital signal processing and fast multiply operations                                                                                                                                                                                             |

| <ul> <li>Cross Bar Switch Technology (XBS)</li> </ul>                                                                                              | Enables concurrent, non-blocking accesses to peripherals, RAM or external memory from multiple bus masters                                                                                                                                             |

| Reset Controller                                                                                                                                   | <ul> <li>Separate reset in and reset out signals</li> <li>Six sources of reset: power-on reset (POR), external, software, watchdog timer, loss of lock and JTAG instruction</li> </ul>                                                                 |

| Interrupt Controllers                                                                                                                              | <ul> <li>Two interrupt controllers supporting up to 64 interrupt sources each, organized as seven programmable levels</li> <li>Combinational path to provide wake-up from low power modes</li> </ul>                                                   |

| Memory                                                                                                                                             |                                                                                                                                                                                                                                                        |

| 128K Dual Ported SRAM                                                                                                                              | Large bank of memory for enhanced performance. Data available in one clock cycle.                                                                                                                                                                      |

| • 8K Cache                                                                                                                                         | Configurable as instruction only, data only or split instruction/data (I/D)                                                                                                                                                                            |

| SDR/DDR SDRAM Controller                                                                                                                           | <ul> <li>Supports a glueless interface to SDR, DDR, and mobile DDR SDRAM devices</li> <li>Supports up to 512 MB of memory; minimum memory configuration of 8 MB</li> </ul>                                                                             |

| <ul> <li>FlexBus (External Interface)</li> </ul>                                                                                                   | <ul> <li>Glueless connections to 8-, 16- and 32-bit external memory devices</li> <li>Up to six chip selects available</li> </ul>                                                                                                                       |

| Power Management                                                                                                                                   |                                                                                                                                                                                                                                                        |

| Low Power Operating Modes                                                                                                                          | <ul> <li>Fully static operation with processor sleep and whole chip stop modes</li> <li>Very rapid response to interrupts from low-power sleep mode</li> <li>Software controlled disable of external clock output for low power consumption</li> </ul> |

| <ul> <li>Peripheral power management register to<br/>enable/disable clocks to most modules</li> </ul>                                              | Allows the enable/disable of clocks to most peripherals, lowering overall power consumption                                                                                                                                                            |

| Peripherals                                                                                                                                        |                                                                                                                                                                                                                                                        |

| Integrated LCD Controller                                                                                                                          | <ul> <li>Support for single (non-split) screen monochrome/color LCD panels and self-refresh type LCD panels</li> <li>Maximum supported panel size of 800 x 600</li> </ul>                                                                              |

| ADC and Touchscreen Controller                                                                                                                     | <ul> <li>12-bit 125K sample/sec ADC for touchscreen and general purpose measurements</li> <li>True touchscreen controller (embedded touchscreen circuitry) with support for 4/5/7 and 8 wire configurations</li> </ul>                                 |

| USB Host, Device and On-the-Go Module                                                                                                              | USB 1.1 and 2.0 compliant full-speed USB controller with DMA                                                                                                                                                                                           |

| FlexCAN Module                                                                                                                                     | <ul> <li>Full implementation of the CAN protocol specification version 2.0B</li> <li>Flexible Message Buffers configurable as receive or transmit</li> </ul>                                                                                           |

| <ul> <li>Synchronous Serial Interface (SSI)</li> </ul>                                                                                             | <ul> <li>Supports synchronous transmit and receive sections</li> <li>Normal, network, and gated clock modes of operation</li> </ul>                                                                                                                    |

| Real Time Clock (RTC)                                                                                                                              | <ul> <li>Full clock; days, hours, minutes and seconds</li> <li>Ability to wake processor from low-power modes (wait, doze and stop) via the real time clock interrupts</li> </ul>                                                                      |

| Programmable Interrupt Timers (PIT)                                                                                                                | <ul> <li>Two programmable interrupt timers each with 16-bit counter</li> <li>Configurable as a down counter or free-running counter</li> </ul>                                                                                                         |

| DMA Timers                                                                                                                                         | <ul> <li>Four 32-bit timers with DMA and interrupt request trigger capability</li> <li>Input capture and reference compare modes</li> </ul>                                                                                                            |

| DMA Serial Peripheral Interface (DSPI)                                                                                                             | <ul> <li>Full-duplex, three-wire synchronous transfer; up to 16 pre-programmed transfers</li> <li>Up to three chip selects available</li> </ul>                                                                                                        |

| <ul> <li>3x Universal Asynchronous Receiver<br/>Transmitters (UARTs)</li> </ul>                                                                    | <ul> <li>Data formats can be 5, 6, 7 or 8 bits with even, odd or no parity</li> <li>Error-detection capabilities</li> </ul>                                                                                                                            |

| I <sup>2</sup> C Module                                                                                                                            | <ul> <li>Interchip bus interface for EEPROMS, LCD controllers, A/D converters and keypads</li> <li>Fully compatible with industry standard I<sup>2</sup>C bus</li> </ul>                                                                               |

| Pulse Width Modulation (PWM) Module                                                                                                                | <ul> <li>Four independent PWM channels with programmable period and duty cycle</li> </ul>                                                                                                                                                              |

| DMA Controller                                                                                                                                     | <ul> <li>16 full programmable channels with 32-byte transfer control descriptor</li> </ul>                                                                                                                                                             |

| Phase Locked Loop (PLL)                                                                                                                            | Provides 37.5 MHz–160 MHz clock to CPU                                                                                                                                                                                                                 |

| Up to 55 GPIOs                                                                                                                                     | <ul> <li>Bit manipulation support via set/clear functions</li> <li>Various unused peripheral pins may be used as GPIO</li> </ul>                                                                                                                       |

| Development Support                                                                                                                                |                                                                                                                                                                                                                                                        |

| Background Debug Mode (BDM) Revision B+                                                                                                            | • Real time debug support, with four PC break point registers and a pair of address breakpoint registers with optional d                                                                                                                               |

| JTAG Support                                                                                                                                       | JTAG part identification and part revision numbers                                                                                                                                                                                                     |

Learn More:

For current information about ColdFire products and documentation, please visit **www.freescale.com/coldfire**.

Freescale and the Freescale logo are trademarks or registered trademarks of Freescale Semiconductor, Inc. in the U.S. and other countries. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2008

Document Number: MCF5227XFS / REV 1 Agile Number: 950-00458 / REV A