## QorlQ LS1046A Security (SEC) Reference Manual

Document Number: LS1046ASECRM

Rev. 0, 05/2017

## **Contents**

| Section number |         |               | Title                                                     | Page |

|----------------|---------|---------------|-----------------------------------------------------------|------|

|                |         |               | Chapter 1 Overview of SEC (security engine) functionality |      |

|                |         |               | Chapter 2 Feature summary                                 |      |

|                |         |               | Chapter 3 SEC implementation                              |      |

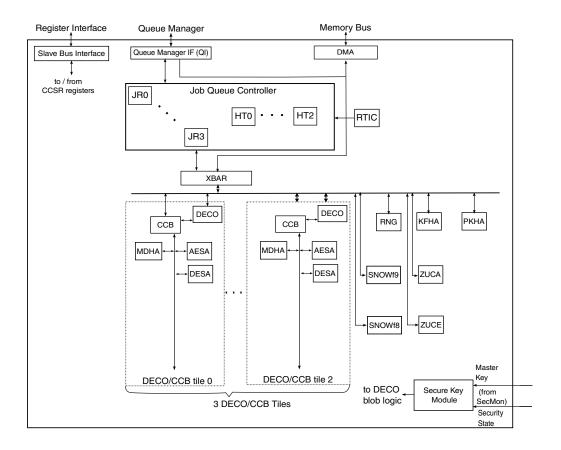

| 3.1            | SEC su  | bmodules      |                                                           | 75   |

| 3.2            | Crypto  | graphic engi  | nes implemented in SEC                                    | 75   |

|                |         |               | Chapter 4 SEC modes of operation                          |      |

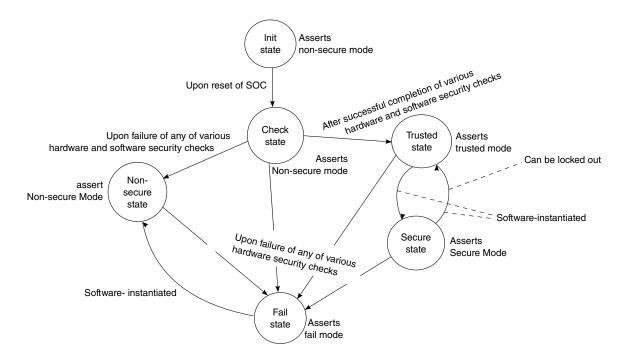

| 4.1            | Securit | y Monitor (S  | SecMon) security states                                   | 77   |

|                | 4.1.1   | The effec     | et of security state on volatile keys                     | 78   |

|                | 4.1.2   | The effect    | et of security state on non-volatile keys                 | 79   |

| 4.2            | Keys av | 79            |                                                           |      |

|                | 4.2.1   | Keys ava      | ilable in trusted mode                                    | 79   |

|                | 4.2.2   | Keys ava      | ilable in secure mode                                     | 80   |

|                | 4.2.3   | Keys ava      | ilable in non-secure mode                                 | 80   |

|                | 4.2.4   | Keys ava      | ilable in fail mode                                       | 81   |

|                |         |               | Chapter 5 SEC hardware functional description             |      |

| 5.1            | System  | Bus Interfac  | ces                                                       | 84   |

|                | 5.1.1   | AXI mas       | ter (DMA) interface                                       | 84   |

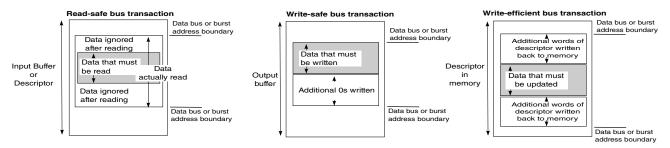

|                |         | 5.1.1.1       | DMA read-safe transactions                                | 84   |

|                |         | 5.1.1.2       | DMA interface write-safe transactions                     | 85   |

|                |         | 5.1.1.3       | DMA write-efficient transactions                          | 85   |

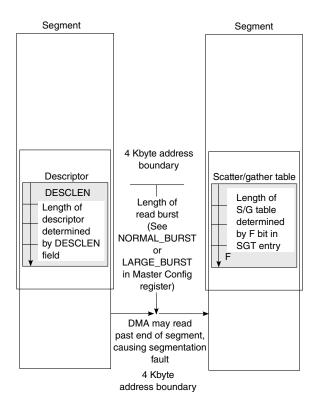

|                |         | 5.1.1.4       | DMA bursts that may read past the end of data structures  | 86   |

|                | 5.1.2   | Register      | interface (IP bus)                                        | 87   |

| 5.2            | SEC se  | rvice interfa | ce concepts                                               | 88   |

| Sec | Section number  |              | Title                                                     | Page |  |

|-----|-----------------|--------------|-----------------------------------------------------------|------|--|

|     | 5.2.1           | SEC desc     | eriptors                                                  | 88   |  |

|     | 5.2.2           | Job termi    | nation status/error codes                                 | 90   |  |

|     | 5.2.3           | Frames a     | nd flows                                                  | 95   |  |

|     | 5.2.4           | Frame de     | escriptors and frames                                     | 96   |  |

|     | 5.2.5           | Frame de     | escriptor flow and flow context                           | 96   |  |

|     | 5.2.6           | Buffer all   | location, release, and reuse                              | 97   |  |

|     | 5.2.7           | User data    | a access control and isolation.                           | 97   |  |

| 5.3 | Service         | interfaces   |                                                           | 98   |  |

|     | 5.3.1           | Job Ring     | interface.                                                | 99   |  |

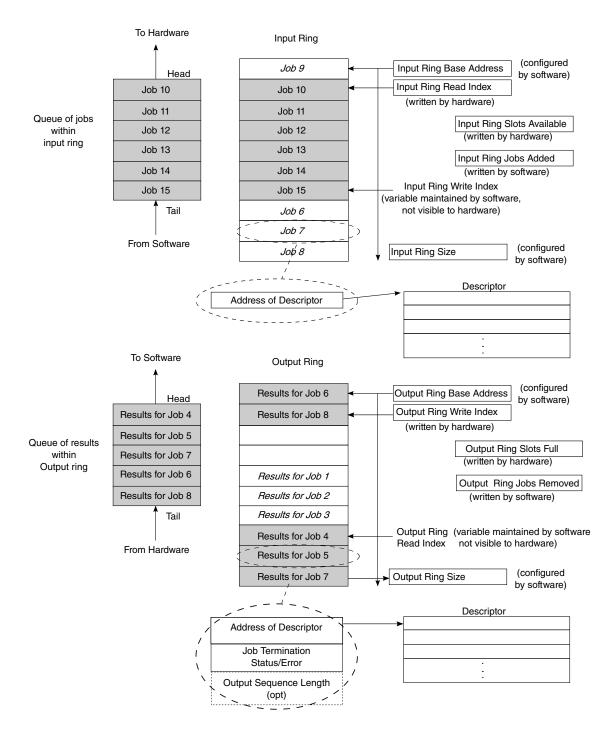

|     |                 | 5.3.1.1      | Configuring and managing the input/output rings, overview | 99   |  |

|     |                 | 5.3.1.2      | Managing the input rings.                                 | 101  |  |

|     |                 | 5.3.1.3      | Managing the output rings                                 | 102  |  |

|     |                 | 5.3.1.4      | Controlling access to job rings                           | 103  |  |

|     |                 | 5.3.1.5      | Order of job completion                                   | 103  |  |

|     |                 | 5.3.1.6      | Initializing job rings                                    | 104  |  |

|     |                 | 5.3.1.7      | Job Ring Registers.                                       | 104  |  |

|     |                 | 5.3.1.8      | Asserting job ring interrupts                             | 104  |  |

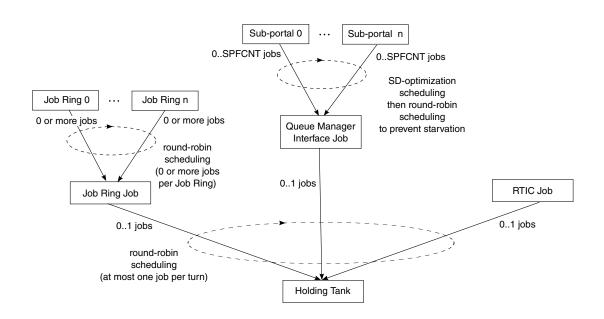

|     | 5.3.2 Queue Mar |              | anager Interface (QI)                                     | 105  |  |

|     |                 | 5.3.2.1      | Requesting and receiving frame descriptors from QMan      | 106  |  |

|     |                 | 5.3.2.2      | Building job descriptors for QI jobs                      | 107  |  |

|     |                 | 5.3.2.3      | Controlling QI access to frame queues and data            | 107  |  |

|     |                 | 5.3.2.4      | Tracking the completion order of QI jobs                  | 108  |  |

|     |                 | 5.3.2.5      | Initializing the Queue Manager Interface                  | 108  |  |

|     |                 | 5.3.2.6      | Done/error notification for QI jobs                       | 109  |  |

|     | 5.3.3           | Register-    | based service interface                                   | 109  |  |

| 5.4 | Job sch         | eduling      |                                                           | 111  |  |

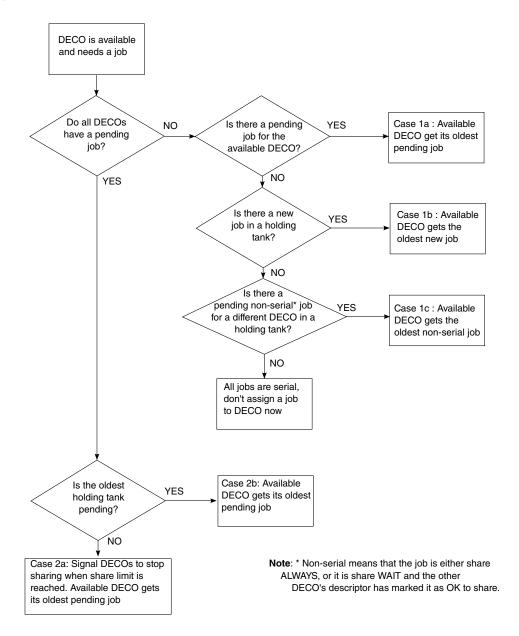

|     | 5.4.1           | Job sched    | duling - default algorithm                                | 111  |  |

|     | 5.4.2           | Job sched    | duling - DECO-specific jobs                               | 114  |  |

| 5.5 | Job exe         | cution hardv | on hardware1                                              |      |  |

| Sec | tion nui | mber Title                                                         | Page |

|-----|----------|--------------------------------------------------------------------|------|

|     | 5.5.1    | Descriptor controller (DECO) and cryptographic control block (CCB) | 115  |

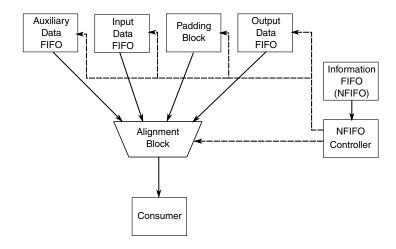

|     |          | 5.5.1.1 Alignment blocks                                           | 116  |

|     | 5.5.2    | Cryptographic hardware accelerators (CHAs) (overview)              | 117  |

|     |          | Chapter 6 Frame queues, frame descriptors, and buffers             |      |

| 6.1 | Frame of | queues                                                             | 119  |

|     | 6.1.1    | Dequeue response                                                   |      |

|     |          | 6.1.1.1 Context_A field (preheader)                                | 121  |

| 6.2 | Frame of | descriptors                                                        | 123  |

|     | 6.2.1    | Processing simple frame jobs                                       | 124  |

|     | 6.2.2    | Processing compound frame jobs.                                    |      |

|     | 6.2.3    | Frame descriptor error handling                                    | 126  |

|     | 6.2.4    | Job descriptor construction from frame descriptor                  | 127  |

|     |          | Chapter 7 Descriptors and descriptor commands                      |      |

| 7.1 | Job des  | criptors                                                           |      |

| 7.2 | Trusted  | l descriptors                                                      | 133  |

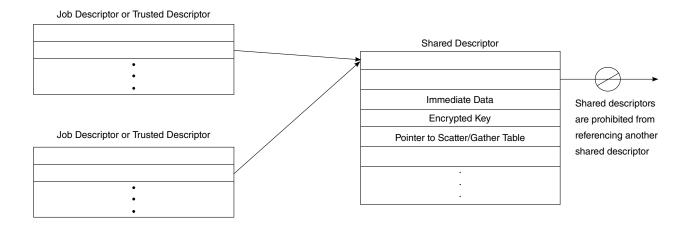

| 7.3 | Shared   | 135                                                                |      |

|     | 7.3.1    | Executing shared descriptors in proper order                       |      |

|     | 7.3.2    | Specifying different types of shared descriptor sharing            | 138  |

|     |          | 7.3.2.1 Error sharing                                              |      |

|     | 7.3.3    | Changing shared descriptors                                        | 139  |

| 7.4 | Using i  | n-line descriptors.                                                | 140  |

| 7.5 | Using r  | replacement job descriptors                                        | 141  |

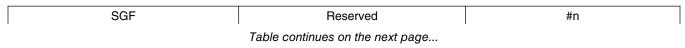

| 7.6 | Scatter/ | /gather tables (SGTs)                                              | 143  |

| 7.7 | Using d  | lescriptor commands                                                | 144  |

|     | 7.7.1    | Command execution order                                            | 145  |

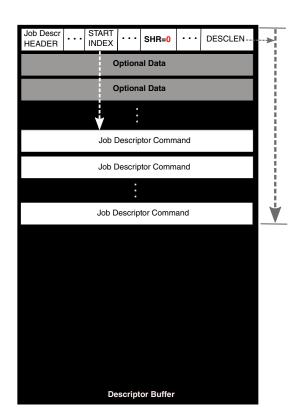

|     |          | 7.7.1.1 Executing commands when SHR = 0                            |      |

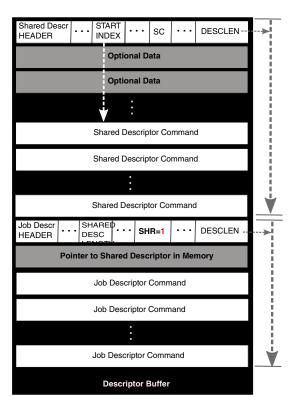

|     |          | 7.7.1.2 Executing commands when SHR = 1                            | 148  |

|     |          |                                                                    |      |

| Sect | ion nur | nber       | Title                                              | Page |

|------|---------|------------|----------------------------------------------------|------|

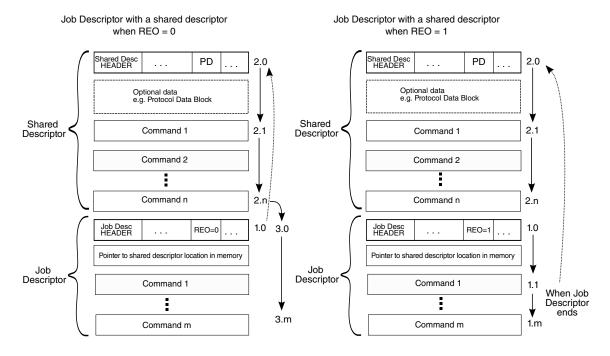

|      |         | 7.7.1.3    | Executing commands when REO = 0                    | 148  |

|      |         | 7.7.1.4    | Executing commands when REO = 1                    | 149  |

|      |         | 7.7.1.5    | Executing additional HEADER commands               | 150  |

|      |         | 7.7.1.6    | Jumping to another job descriptor                  | 151  |

|      | 7.7.2   | Command    | d properties                                       | 152  |

|      |         | 7.7.2.1    | Blocking commands                                  | 152  |

|      |         | 7.7.2.2    | Load/store checkpoint                              | 152  |

|      |         | 7.7.2.3    | Done checkpoint                                    |      |

|      | 7.7.3   | Command    | d types                                            | 153  |

|      | 7.7.4   | SEQ vs n   | non-SEQ commands.                                  |      |

|      |         | 7.7.4.1    | Creating a sequence                                |      |

|      |         | 7.7.4.2    | Using sequences for fixed and variable length data | 156  |

|      |         | 7.7.4.3    | Transferring meta data                             | 157  |

|      |         | 7.7.4.4    | Rewinding a sequence                               | 158  |

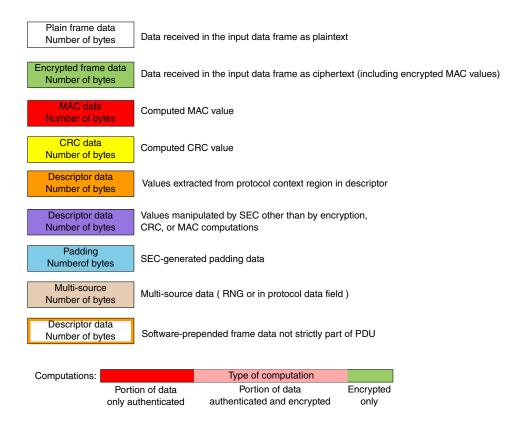

|      | 7.7.5   | Informati  | ion FIFO entries                                   | 158  |

|      | 7.7.6   | Output Fl  | IFO Operation                                      | 159  |

|      | 7.7.7   | Output C   | hecksum logic                                      | 161  |

|      | 7.7.8   | Cryptogra  | aphic class                                        | 162  |

|      | 7.7.9   | Address p  | pointers                                           | 163  |

| 7.8  | HEADI   | ER command | d                                                  | 164  |

| 7.9  | KEY co  | ommands    |                                                    | 169  |

| 7.10 | LOAD    | commands   |                                                    | 173  |

| 7.11 | FIFO L  | OAD comm   | and                                                | 186  |

|      | 7.11.1  | Bit length | h data                                             | 189  |

|      | 7.11.2  | FIFO LO    | AD input data type                                 | 190  |

| 7.12 | ECPAR   | AM comma   | and                                                |      |

| 7.13 | STORE   | command    |                                                    | 196  |

| 7.14 | FIFO S' | TORE comn  | nand                                               | 204  |

| 7.15 | MOVE,   | MOVEB, N   | MOVEDW, and MOVE_LEN commands                      | 210  |

| Sect | ion nun  | nber Title                                                    | Page |  |  |

|------|----------|---------------------------------------------------------------|------|--|--|

| 7.16 | ALGOR    | RITHM OPERATION command                                       | 219  |  |  |

| 7.17 | PROTO    | PROTOCOL OPERATION commands                                   |      |  |  |

| 7.18 | PKHA (   | OPERATION command                                             | 245  |  |  |

|      | 7.18.1   | PKHA OPERATION: clear memory function.                        | 247  |  |  |

|      | 7.18.2   | PKHA OPERATION: Arithmetic Functions                          | 248  |  |  |

|      | 7.18.3   | PKHA OPERATION: copy memory functions                         | 255  |  |  |

|      | 7.18.4   | PKHA OPERATION: Elliptic Curve Functions                      | 257  |  |  |

| 7.19 | SIGNA    | ΓURE command                                                  | 260  |  |  |

| 7.20 | JUMP (   | HALT) command                                                 | 263  |  |  |

|      | 7.20.1   | Jump type                                                     | 264  |  |  |

|      |          | 7.20.1.1 Local conditional jump                               | 264  |  |  |

|      |          | 7.20.1.2 Local conditional increment/decrement jump           | 265  |  |  |

|      |          | 7.20.1.3 Non-local conditional jump                           |      |  |  |

|      |          | 7.20.1.4 Conditional halt                                     | 266  |  |  |

|      |          | 7.20.1.5 Conditional halt with user-specified status          | 266  |  |  |

|      |          | 7.20.1.6 Conditional subroutine call                          | 267  |  |  |

|      |          | 7.20.1.7 Conditional subroutine return                        | 267  |  |  |

|      | 7.20.2   | Test type                                                     | 268  |  |  |

|      | 7.20.3   | JSL and TEST CONDITION fields                                 | 269  |  |  |

|      | 7.20.4   | JUMP command format                                           | 270  |  |  |

| 7.21 | MATH     | and MATHI Commands                                            | 273  |  |  |

| 7.22 | SEQ IN   | PTR command                                                   | 280  |  |  |

| 7.23 | SEQ OU   | JT PTR command                                                | 283  |  |  |

|      |          | Chapter 8 Public Key Cryptography Operations                  |      |  |  |

| 8.1  | Conforn  | nance considerations                                          | 287  |  |  |

| 8.2  | Discrete | e-log key-pair generation                                     | 288  |  |  |

|      | 8.2.1    | Inputs to the discrete-log key-pair generation function.      | 289  |  |  |

|      | 8.2.2    | Assumptions of the discrete-log key-pair generation function. | 289  |  |  |

| Sect | tion nui | mber Title                                                              | Page |

|------|----------|-------------------------------------------------------------------------|------|

|      | 8.2.3    | Outputs from the discrete-log key-pair generation function              | 289  |

|      | 8.2.4    | Operation of the discrete-log key-pair generation function.             | 289  |

|      | 8.2.5    | Notes associated with the discrete-log key-pair generation function     | 290  |

| 8.3  | Using t  | he Diffie_Hellman function                                              | 294  |

|      | 8.3.1    | Diffie_Hellman requirements                                             | 294  |

|      | 8.3.2    | Inputs to the Diffie-Hellman function.                                  | 294  |

|      | 8.3.3    | Assumptions of the Diffie-Hellman function                              | 295  |

|      | 8.3.4    | Outputs from the Diffie-Hellman function                                | 295  |

|      | 8.3.5    | Operation of the Diffie-Hellman function                                | 295  |

|      | 8.3.6    | Notes associated with the Diffie-Hellman function                       | 295  |

| 8.4  | Genera   | ting DSA and ECDSA signatures                                           | 296  |

|      | 8.4.1    | Inputs to the DSA and ECDSA signature generation function               | 297  |

|      | 8.4.2    | Assumptions of the DSA and ECDSA signature generation function          | 297  |

|      | 8.4.3    | Outputs from the DSA and ECDSA signature generation function            | 297  |

|      | 8.4.4    | Operation of the DSA and ECDSA signature generation function            | 298  |

|      | 8.4.5    | Notes associated with the DSA and ECDSA Signature Generation function   | 298  |

| 8.5  | Verifyi  | ng DSA and ECDSA signatures                                             | 301  |

|      | 8.5.1    | Inputs to the DSA and ECDSA signature verification function             | 302  |

|      | 8.5.2    | Assumptions of the DSA and ECDSA signature verification function        | 302  |

|      | 8.5.3    | Outputs from the DSA and ECDSA signature verification function.         | 302  |

|      | 8.5.4    | Operation of the DSA and ECDSA signature verification function          | 302  |

|      | 8.5.5    | Notes associated with the DSA and ECDSA Signature Verification function | 303  |

| 8.6  | RSA Fi   | inalize Key Generation (RFKG)                                           | 306  |

| 8.7  | Implem   | nentation of the RSA encrypt operation                                  | 307  |

| 8.8  | Implem   | nentation of the RSA decrypt operation                                  | 309  |

|      |          | Chapter 9 Protocol acceleration                                         |      |

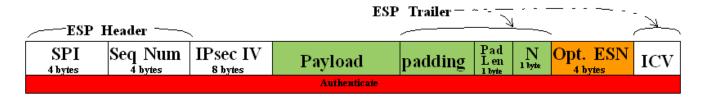

| 9.1  | IPsec E  | SP encapsulation and decapsulation overview.                            | 317  |

|      | 9.1.1    | IPsec ESP encapsulation and decapsulation mode support                  | 319  |

| Section number |           | Title                                                                                             | Page |

|----------------|-----------|---------------------------------------------------------------------------------------------------|------|

| 9.1.2          | IPsec ESP | error codes                                                                                       | 319  |

| 9.1.3          | Programm  | ning for IPsec                                                                                    | 320  |

|                | 9.1.3.1   | PDB format for IPsec ESP Transport (and Legacy Tunnel) encapsulation                              | 321  |

|                | 9.1.3.2   | Common PDB format descriptions for IPsec ESP Transport (and Legacy Tunnel) decapsulation.         | 324  |

|                | 9.1.3.3   | Overriding ESP Transport (and legacy Tunnel) PDB content with the DECO Protocol Override Register | 327  |

|                | 9.1.3.4   | PDB format for IPsec ESP Tunnel encapsulation                                                     | 328  |

|                | 9.1.3.5   | Common PDB format descriptions for IPsec ESP Tunnel decapsulation                                 | 331  |

|                | 9.1.3.6   | Overriding ESP Tunnel PDB content with the DECO Protocol Override Register                        | 334  |

|                | 9.1.3.7   | IPsec ESP encapsulation CBC-specific PDB segment format descriptions                              | 336  |

|                | 9.1.3.8   | IPsec ESP encapsulation AES-CTR-specific PDB segment format descriptions                          | 336  |

|                | 9.1.3.9   | IPsec ESP encapsulation AES-CCM-specific PDB segment format descriptions                          | 337  |

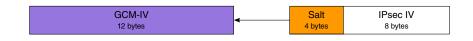

|                | 9.1.3.10  | IPsec ESP encapsulation AES-GCM-specific PDB segment format descriptions                          | 337  |

|                | 9.1.3.11  | IPsec ESP decapsulation CBC-specific PDB segment format descriptions                              | 338  |

|                | 9.1.3.12  | IPsec ESP decapsulation AES-CTR-specific PDB segment format descriptions                          | 338  |

|                | 9.1.3.13  | IPsec ESP decapsulation AES-CCM-specific PDB segment format descriptions                          | 339  |

|                | 9.1.3.14  | IPsec ESP decapsulation AES-GCM-specific PDB segment format descriptions                          | 339  |

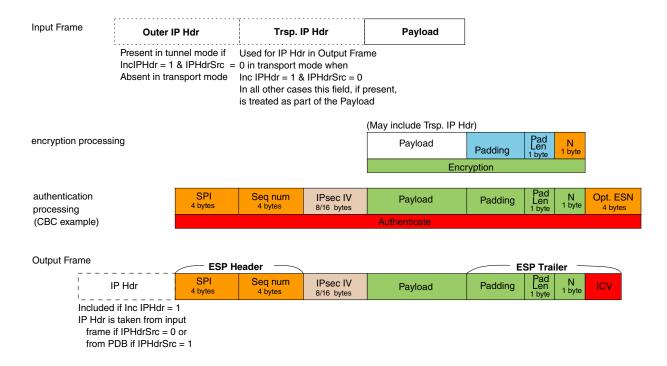

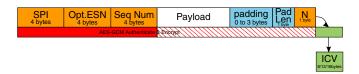

| 9.1.4          | IPsec ESP | Transport (and Legacy Tunnel) encapsulation overview                                              | 340  |

|                | 9.1.4.1   | Encapsulating the IP header in tunnel mode                                                        | 341  |

|                | 9.1.4.2   | Encapsulating the IP header in transport mode                                                     | 341  |

|                | 9.1.4.3   | Process for IPsec ESP Transport (and Legacy Tunnel) encapsulation                                 | 341  |

| 9.1.5          | IPsec ESP | Cryptographic Encapsulation                                                                       | 343  |

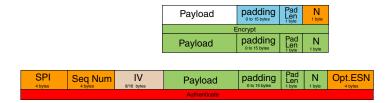

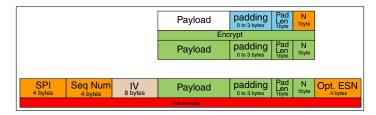

|                | 9.1.5.1   | Process for IPsec encapsulation when using AES-CBC or DES-CBC                                     | 343  |

|                | 9.1.5.2   | Process for IPsec encapsulation when using AES-CTR                                                | 344  |

|                | 9.1.5.3   | Process for IPsec encapsulation when using AES-CCM                                                | 346  |

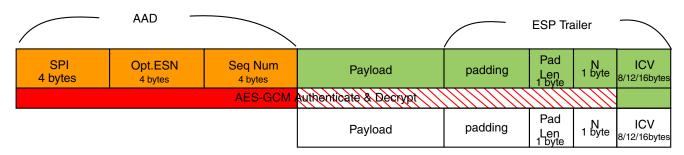

|                | 9.1.5.4   | Process for IPsec encapsulation when using AES-GCM                                                | 348  |

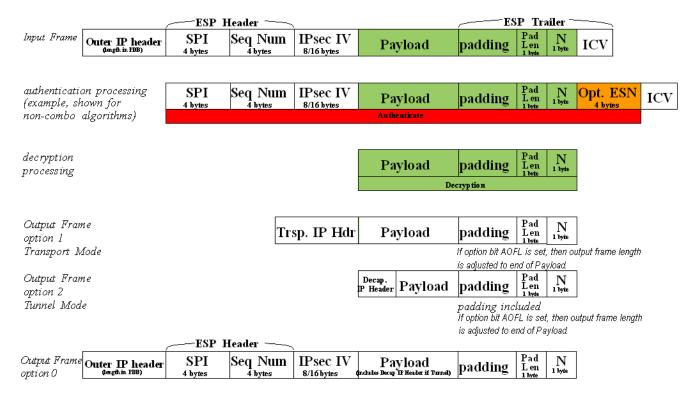

| 9.1.6          | IPsec ESP | Transport (and Legacy Tunnel) decapsulation procedure overview                                    | 349  |

|                | 9.1.6.1   | IPsec ESP Transport Mode outer IP header decapsulation procedure                                  | 351  |

| Sect | Section number |             | Title                                                                                         |     |

|------|----------------|-------------|-----------------------------------------------------------------------------------------------|-----|

|      |                | 9.1.6.2     | IPsec ESP Transport (and Legacy Tunnel) outer IP header decapsulation procedure (tunnel mode) |     |

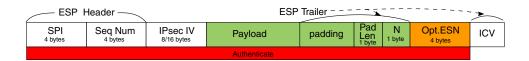

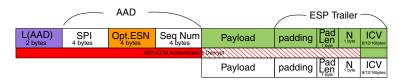

|      | 9.1.7          | IPsec ESI   | P Cryptographic Decapsulation                                                                 | 352 |

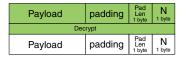

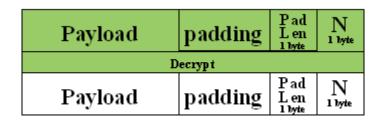

|      |                | 9.1.7.1     | IPsec decapsulation procedure when using AES-CBC or DES-CBC                                   | 352 |

|      |                | 9.1.7.2     | Process for IPsec decapsulation when using AES-CTR                                            | 354 |

|      |                | 9.1.7.3     | Process for IPsec decapsulation when using AES-CCM                                            | 355 |

|      |                | 9.1.7.4     | Process for IPsec decapsulation when using AES-GCM                                            | 356 |

|      |                | 9.1.7.5     | Use of SPI and the sequence number in decapsulation                                           | 357 |

|      |                | 9.1.7.6     | Optional use of ESN in ESP decapsulation                                                      | 358 |

|      |                | 9.1.7.7     | Anti-replay checking in IPsec ESP decapsulation                                               | 358 |

|      |                |             | 9.1.7.7.1 When anti-replay checking is enabled                                                | 359 |

|      |                |             | 9.1.7.7.2 When anti-replay checking is disabled                                               | 359 |

|      |                | 9.1.7.8     | ICV checking during IPsec ESP decapsulation                                                   | 360 |

|      | 9.1.8          | IPsec ESI   | P Tunnel encapsulation overview                                                               | 360 |

|      |                | 9.1.8.1     | Handling the Outer IP Header during ESP Tunnel encapsulation                                  | 360 |

|      |                | 9.1.8.2     | Outer IP Header handling with UDP-encapsulated-ESP                                            | 362 |

|      |                | 9.1.8.3     | ESP Tunnel Outer IP Header manipulation.                                                      | 362 |

|      |                | 9.1.8.4     | ESP Tunnel handling of Next Header                                                            | 363 |

|      | 9.1.9          | IPsec ESI   | P tunnel decapsulation overview                                                               | 363 |

|      |                | 9.1.9.1     | Input material preceding the outer IP header                                                  | 364 |

|      |                | 9.1.9.2     | Handling the Outer IP Header during ESP Tunnel decapsulation                                  | 364 |

|      |                | 9.1.9.3     | Manipulation of the Inner IP Header during ESP Tunnel decapsulation                           | 365 |

|      |                | 9.1.9.4     | Decapsulation Output Frame Length                                                             | 366 |

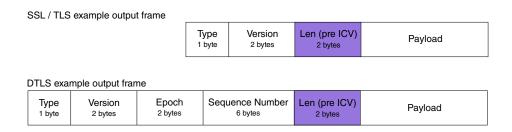

| 9.2  | SSL/TI         | LS/DTLS rec | cord encapsulation and decapsulation overview                                                 | 366 |

|      | 9.2.1          | Programm    | ming and processing details common to all versions of SSL, TLS, and DTLS                      | 367 |

|      |                | 9.2.1.1     | PDB use and format for SSL, TLS, and DTLS encapsulation and decapsulation                     | 368 |

|      |                |             | 9.2.1.1.1 PDB for SSL, TLS, and DTLS when a Block Cipher is used                              | 368 |

|      |                |             | 9.2.1.1.2 PDB for SSL, TLS, and DTLS when AES-Counter mode is used                            | 369 |

|      |                |             | 9.2.1.1.3 PDB for TLS and DTLS when AES-GCM is used                                           | 370 |

|      |                |             |                                                                                               |     |

| Section number |            | Title                                                                       |             |

|----------------|------------|-----------------------------------------------------------------------------|-------------|

|                |            | 9.2.1.1.4 PDB for TLS and DTLS when AES-CCM is used                         | 371         |

|                |            | 9.2.1.1.5 Programming the Options byte with the PDB for SSL, TLS and DT     | LS372       |

|                | 9.2.1.2    | Overriding the PDB for SSL, TLS, and DTLS Encapsulation                     | 374         |

|                | 9.2.1.3    | Computing the pre-encrypted record length during decapsulation              | 375         |

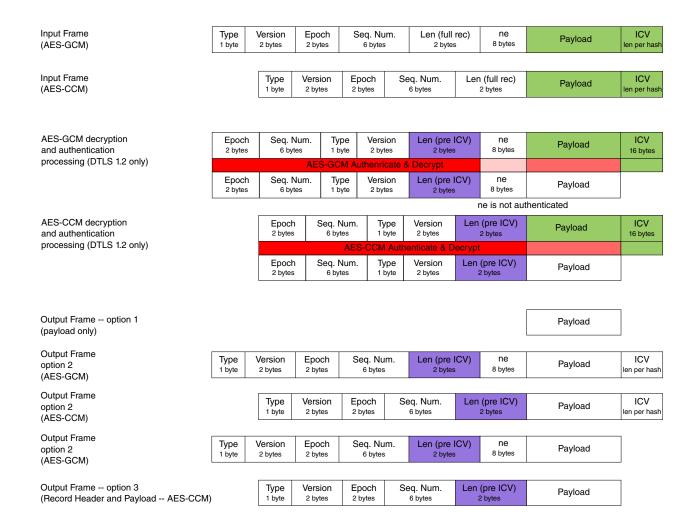

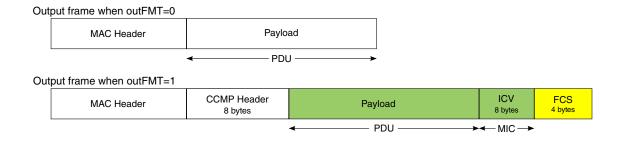

|                | 9.2.1.4    | SSL, TLS, DTLS Decapsulation Output frame options                           | 376         |

|                | 9.2.1.5    | SSL / TLS / DTLS error codes                                                | 378         |

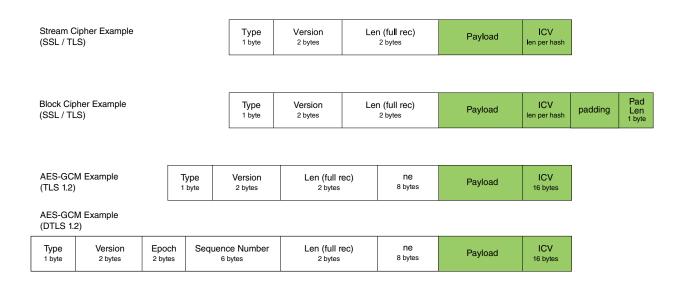

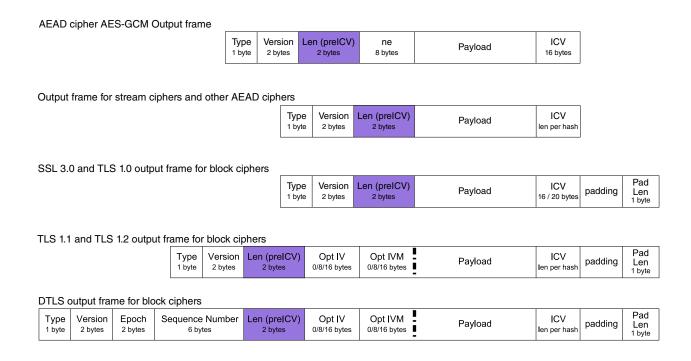

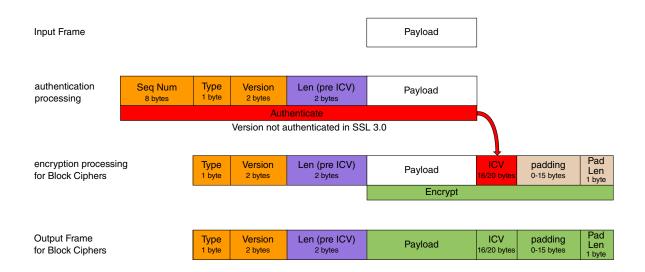

| 9.2.2          | Process fo | or SSL 3.0 and TLS 1.0 record encapsulation                                 | 378         |

|                | 9.2.2.1    | Differences between SSL 3.0 and TLS 1.0 (record encapsulation)              | 379         |

|                | 9.2.2.2    | Processing SSL 3.0 and TLS 1.0 record encapsulation with block ciphers      | 380         |

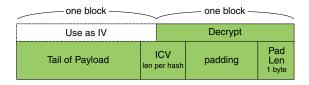

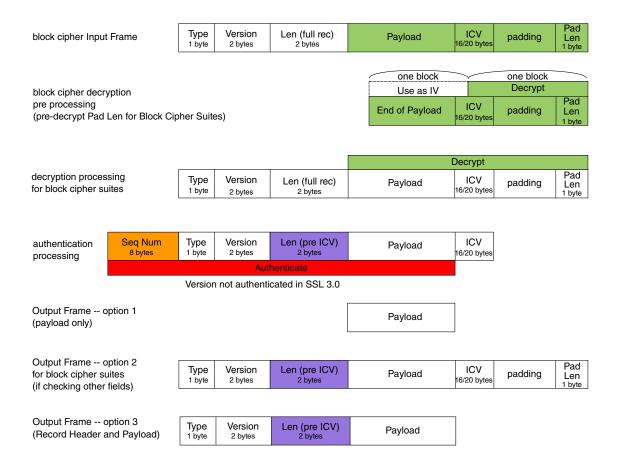

| 9.2.3          | Process fo | or SSL 3.0 and TLS 1.0 record decapsulation                                 | 381         |

|                | 9.2.3.1    | SSL 3.0 and TLS 1.0 Record Decapsulation for block ciphers                  | 382         |

|                | 9.2.3.2    | Differences between SSL 3.0 and TLS 1.0 (record decapsulation)              | 382         |

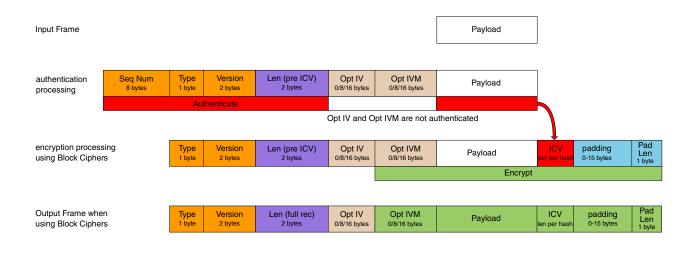

| 9.2.4          | Process fo | or TLS 1.1 and TLS 1.2 record encapsulation                                 | 383         |

|                | 9.2.4.1    | Differences between TLS 1.0, TLS 1.1, and TLS 1.2 Record Encapsulation      | 384         |

|                | 9.2.4.2    | Support for IV generation in TLS 1.1 and TLS 1.2 record encapsulation       | 384         |

|                | 9.2.4.3    | Processing TLS 1.1 and TLS 1.2 record encapsulation with block ciphers (AES | or DES) 386 |

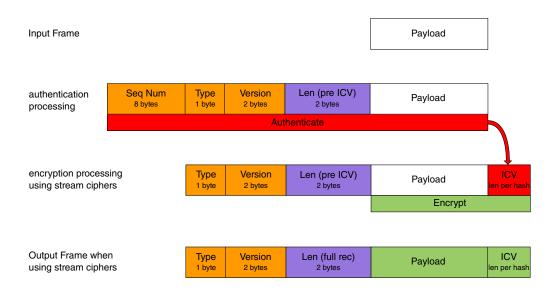

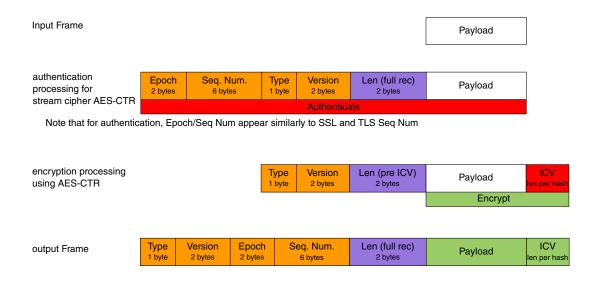

|                | 9.2.4.4    | Processing TLS 1.1 and TLS 1.2 record encapsulation with stream ciphers     | 387         |

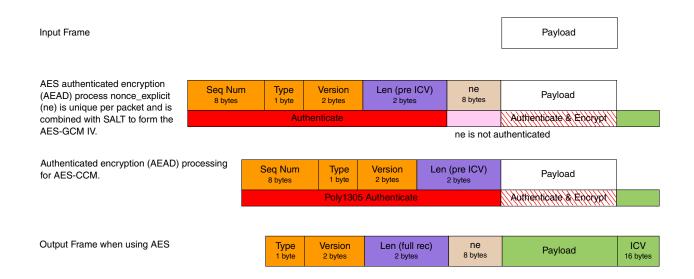

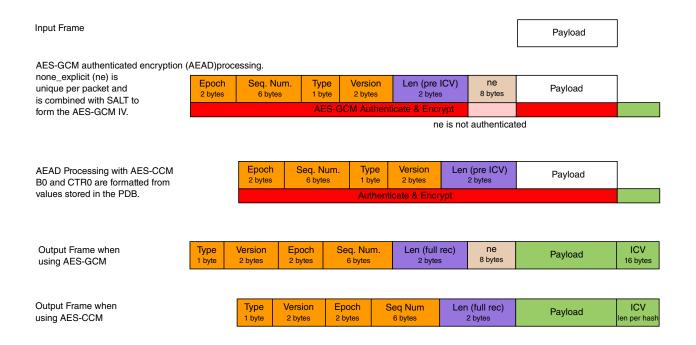

|                | 9.2.4.5    | Processing TLS 1.1 and TLS 1.2 record encapsulation with AEAD ciphers       | 388         |

| 9.2.5          | Process fo | or TLS 1.1 and TLS 1.2 record decapsulation                                 | 389         |

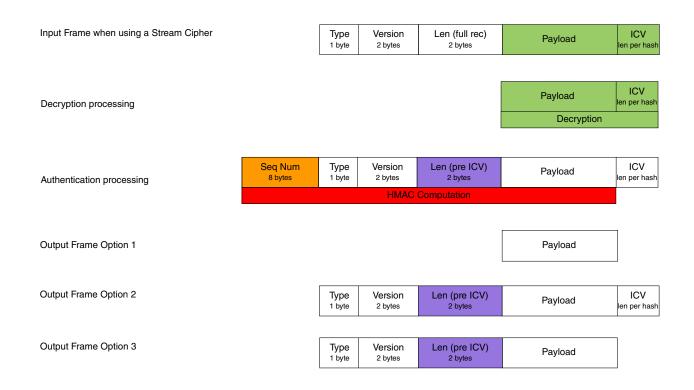

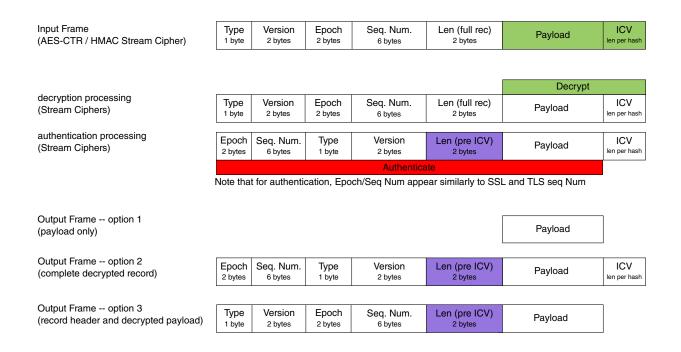

|                | 9.2.5.1    | Decapsulation of TLS 1.1 and TLS 1.2 records when a stream cipher is used   | 390         |

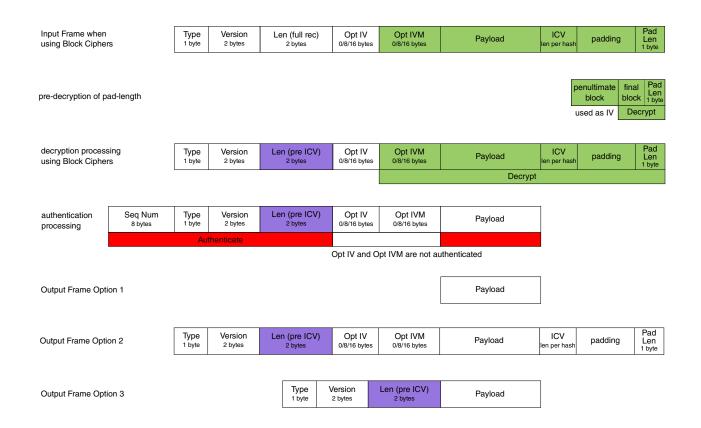

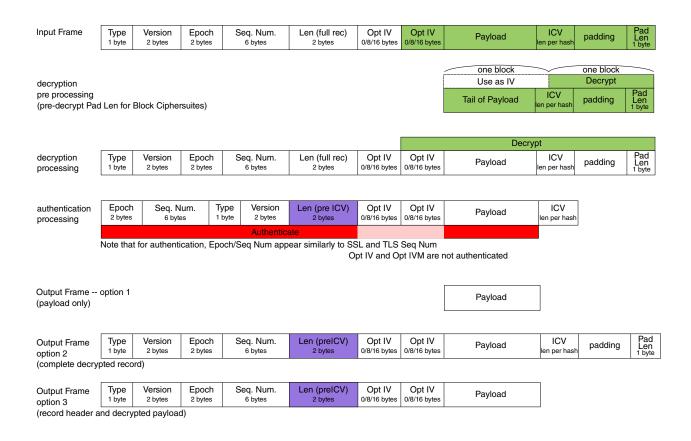

|                | 9.2.5.2    | Decapsulation of TLS 1.1 and TLS 1.2 records when a block cipher is used    | 392         |

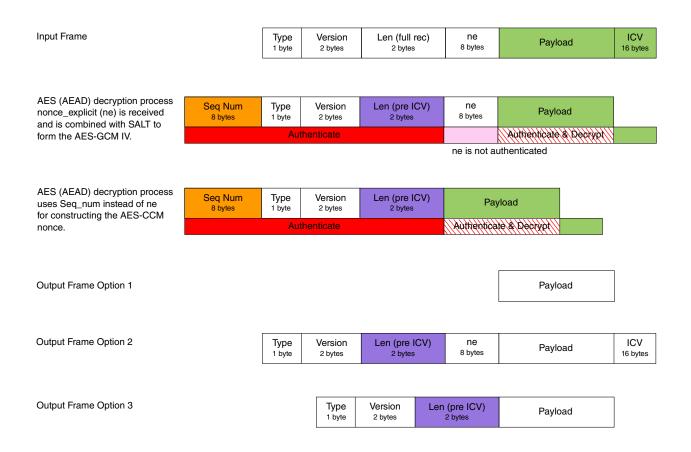

|                | 9.2.5.3    | Decapsulation of TLS 1.2 records when an AEAD is used                       | 393         |

| 9.2.6          | Process fo | or DTLS record encapsulation                                                | 394         |

|                | 9.2.6.1    | Differences between DTLS and TLS                                            | 395         |

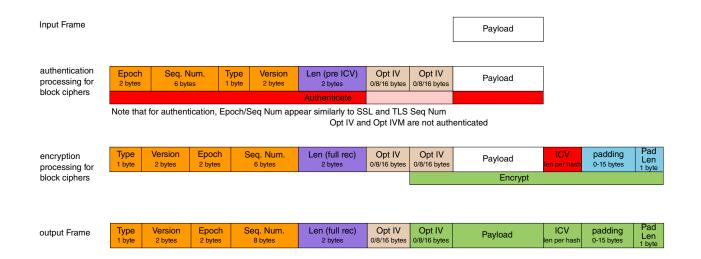

|                | 9.2.6.2    | Process of DTLS Record Encapsulation when using a Block Cipher              | 395         |

|                | 9.2.6.3    | Process of DTLS Record Encapsulation when using a Stream Cipher             | 397         |

|                | 9.2.6.4    | DTLS 1.2 Record Encapsulation when using an AEAD Cipher                     | 398         |

| 9.2.7          | Process fo | or DTLS record decapsulation                                                | 399         |

|                | 9.2.7.1    | Differences between DTLS and TLS                                            | 400         |

NXP Semiconductors

11

| Section number |         | mber        | Title                                                                |     |

|----------------|---------|-------------|----------------------------------------------------------------------|-----|

|                |         | 9.2.7.2     | Process of DTLS Record Decapsulation when using a Block Cipher       | 400 |

|                |         | 9.2.7.3     | Process of DTLS Record Decapsulation when using a Stream Cipher      | 402 |

|                |         | 9.2.7.4     | DTLS 1.2 Record Decapsulation when using an AEAD Cipher              | 403 |

| 9.3            | SRTP p  | acket encap | sulation and decapsulation                                           | 405 |

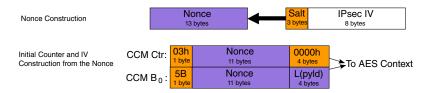

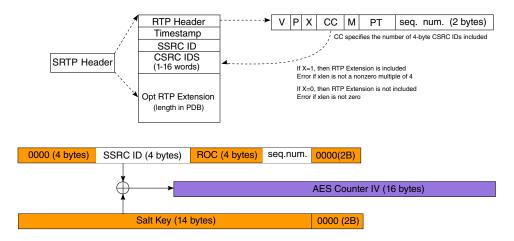

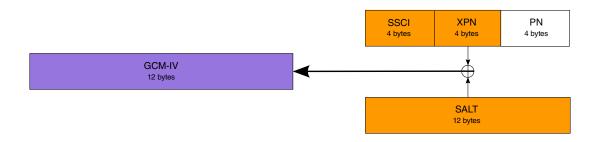

|                | 9.3.1   | Building    | the initial counter value (Counter IV)                               | 406 |

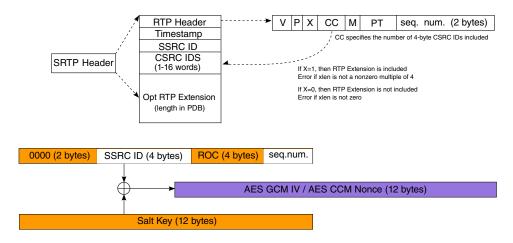

|                | 9.3.2   | Building    | the AEAD Nonce                                                       | 406 |

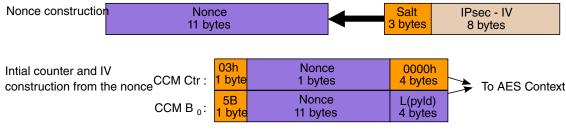

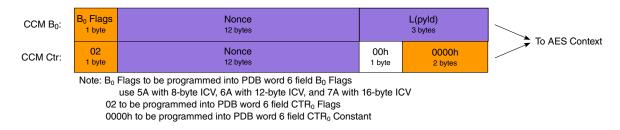

|                | 9.3.3   | Construct   | ting the AESA context from the SRTP AEAD Nonce for AES-CCM mode      | 407 |

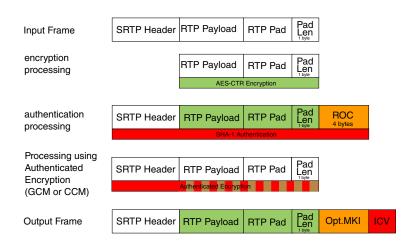

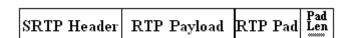

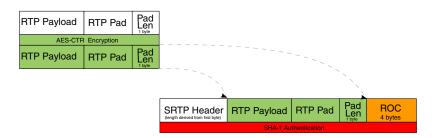

|                | 9.3.4   | SRTP end    | capsulation                                                          | 408 |

|                |         | 9.3.4.1     | Process for SRTP encapsulation                                       | 409 |

|                |         | 9.3.4.2     | Handling the optional MKI                                            | 410 |

|                |         | 9.3.4.3     | SRTP encapsulation PDB format descriptions                           | 410 |

|                |         | 9.3.4.4     | SRTP encapsulation error conditions                                  | 411 |

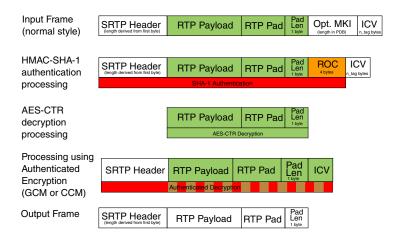

|                | 9.3.5   | SRTP dec    | capsulation overview                                                 | 411 |

|                |         | 9.3.5.1     | Process for SRTP decapsulation                                       | 412 |

|                |         | 9.3.5.2     | SRTP decapsulation PDB format descriptions                           | 413 |

|                |         | 9.3.5.3     | SRTP decapsulation error conditions                                  | 415 |

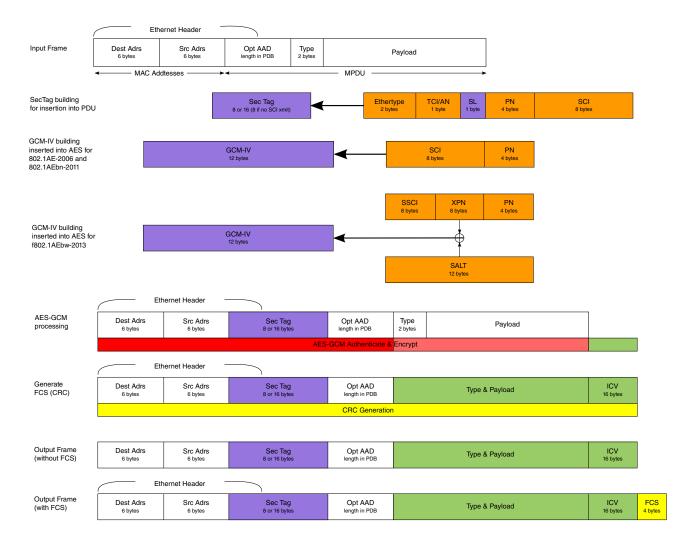

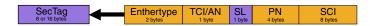

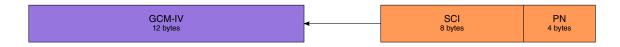

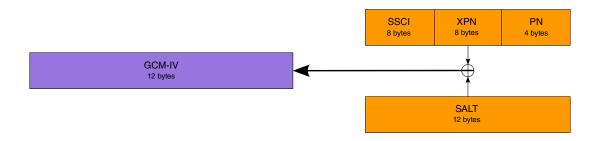

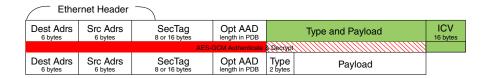

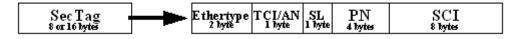

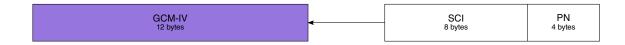

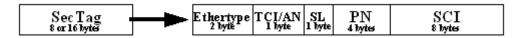

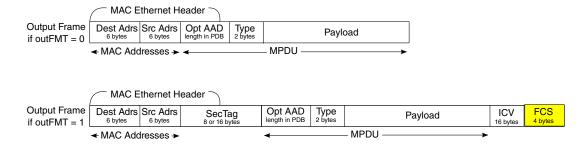

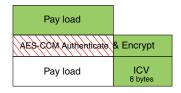

| 9.4            | IEEE 80 | 02.1AE MA   | Csec encapsulation and decapsulation overview                        | 415 |

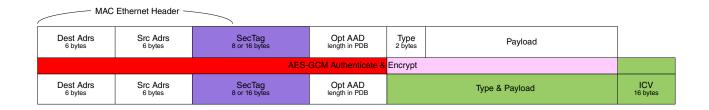

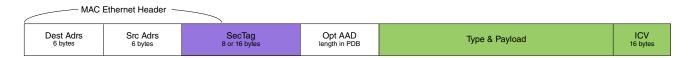

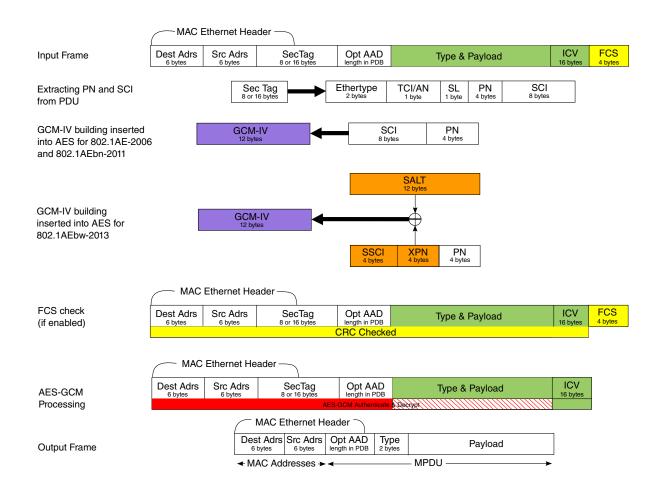

|                | 9.4.1   | Process for | or 802.1AE MACsec encapsulation                                      | 416 |

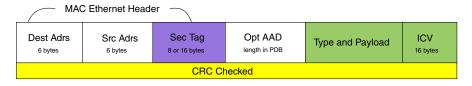

|                |         | 9.4.1.1     | Using the frame check sequence (FCS)                                 | 418 |

|                |         | 9.4.1.2     | Additional notes for GMAC support                                    | 419 |

|                | 9.4.2   | MACsec      | encapsulation PDB format descriptions                                | 420 |

|                | 9.4.3   | Process for | or 802.1AE MACSec decapsulation                                      | 421 |

|                |         | 9.4.3.1     | Automatically switching between two keys                             | 423 |

|                |         | 9.4.3.2     | Additional notes for GMAC support (decapsulation)                    | 424 |

|                | 9.4.4   | MACsec      | decapsulation PDB format descriptions                                | 424 |

| 9.5            | IEEE 80 | 02.11-2012  | WPA2 MPDU encapsulation and decapsulation                            | 425 |

|                | 9.5.1   | Processin   | g Common to WPA2 Encapsulation and Decapsulation                     | 426 |

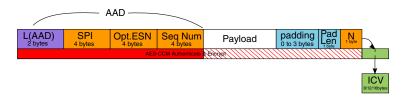

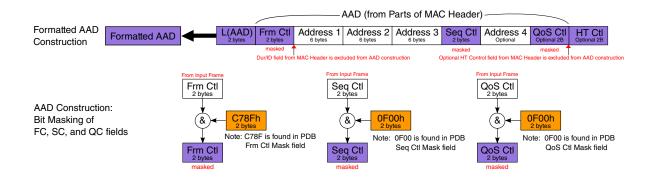

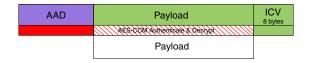

|                |         | 9.5.1.1     | Constructing the AAD for WPA2 encapsulation and decapsulation        | 426 |

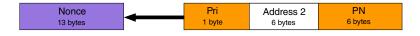

|                |         | 9.5.1.2     | Constructing the CCMP Nonce for WPA2 encapsulation and decapsulation | 427 |

|                |         |             |                                                                      |     |

| Section number |                                                            | mber           | Title                                                                       | Page |  |  |

|----------------|------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|------|--|--|

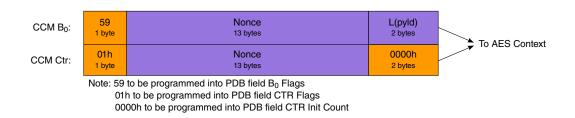

|                |                                                            | 9.5.1.3        | Constructing the AESA context for WPA2 CCMP encapsulation and decapsulation | 427  |  |  |

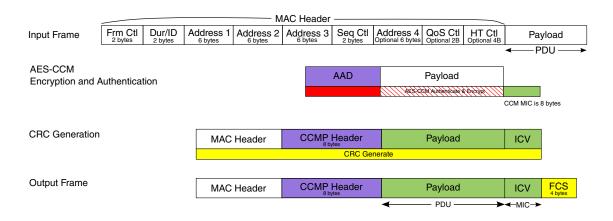

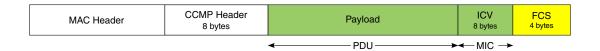

|                | 9.5.2                                                      | Process for    | or WPA2 encapsulation                                                       | 428  |  |  |

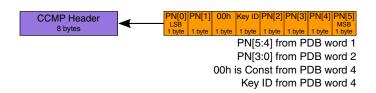

|                |                                                            | 9.5.2.1        | Constructing the CCMP header for WPA2 encapsulation                         | 429  |  |  |

|                |                                                            | 9.5.2.2        | WPA2 Payload Encapsulation                                                  | 430  |  |  |

|                |                                                            | 9.5.2.3        | Computing the FCS for WPA2 encapsulation                                    | 430  |  |  |

|                |                                                            | 9.5.2.4        | WPA2 encapsulation PDB format descriptions                                  | 430  |  |  |

|                |                                                            | 9.5.2.5        | WPA2 encapsulation error conditions                                         | 432  |  |  |

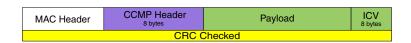

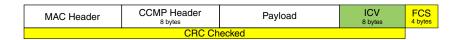

|                | 9.5.3                                                      | Process for    | or WPA2 decapsulation                                                       | 432  |  |  |

|                |                                                            | 9.5.3.1        | WPA2 Decapsulation Anti-replay checking                                     | 433  |  |  |

|                |                                                            | 9.5.3.2        | Using automatic key-switching                                               | 434  |  |  |

|                |                                                            | 9.5.3.3        | WPA2 decapsulation PDB format descriptions                                  | 434  |  |  |

|                |                                                            | 9.5.3.4        | WPA2 decapsulation error conditions                                         | 435  |  |  |

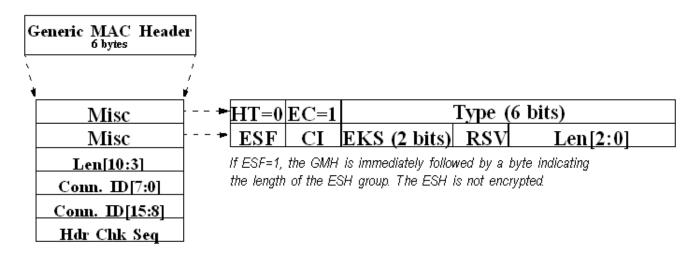

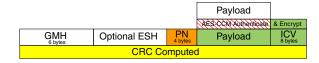

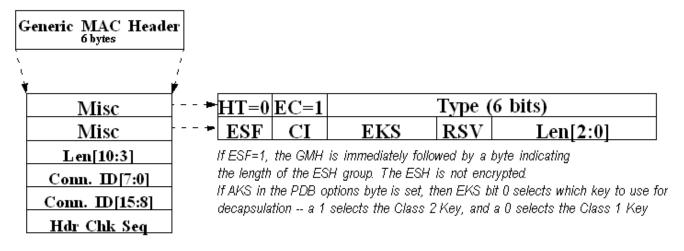

| 9.6            | IEEE 802.16 WiMAX encapsulation and decapsulation overview |                |                                                                             |      |  |  |

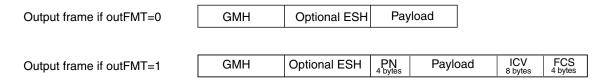

|                | 9.6.1                                                      | Process for    | or IEEE 802.16 WiMAX encapsulation                                          | 437  |  |  |

|                | 9.6.2                                                      | IEEE 802       | 2.16 WiMAX encapsulation PDB format descriptions                            | 439  |  |  |

|                | 9.6.3                                                      | WiMax e        | ncapsulation error conditions                                               | 440  |  |  |

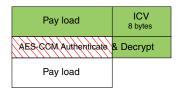

|                | 9.6.4                                                      | Procedure      | e for IEEE 802.16 WiMAX decapsulation                                       | 440  |  |  |

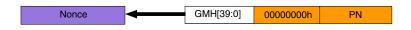

|                |                                                            | 9.6.4.1        | Transforming the GMH (WiMAX decapsulation)                                  | 442  |  |  |

|                |                                                            | 9.6.4.2        | Automatic key switching (WiMAX decapsulation)                               | 443  |  |  |

|                | 9.6.5                                                      | IEEE 802       | 2.16 WiMAX decapsulation PDB format descriptions                            | 443  |  |  |

|                | 9.6.6                                                      | WiMAX          | decapsulation error conditions                                              | 444  |  |  |

| 9.7            | Anti-Re                                                    | eplay built-ir | ı checking                                                                  | 444  |  |  |

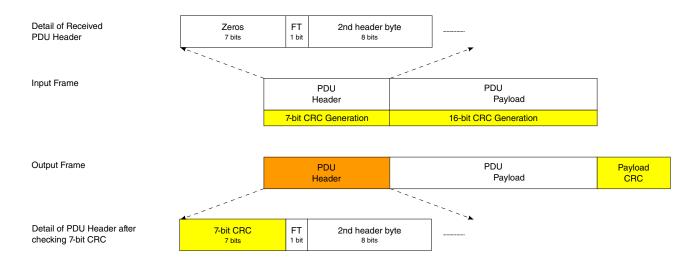

| 9.8            | Process                                                    | for 3G doub    | ole-CRC encapsulation and decapsulation                                     | 447  |  |  |

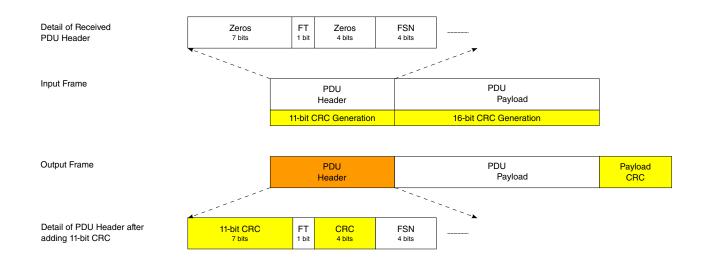

|                | 9.8.1                                                      | 3G doubl       | e-CRC encapsulation process                                                 | 448  |  |  |

|                |                                                            | 9.8.1.1        | Calculating the 7-bit CRC of the PDU header for encapsulation               | 448  |  |  |

|                |                                                            | 9.8.1.2        | Calculating the 11-bit CRC of the PDU header for encapsulation              | 449  |  |  |

|                |                                                            | 9.8.1.3        | Calculating the 16-bit payload CRC for encapsulation                        | 450  |  |  |

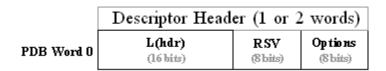

|                | 9.8.2                                                      | 3G doubl       | e-CRC encapsulation PDB format descriptions                                 | 450  |  |  |

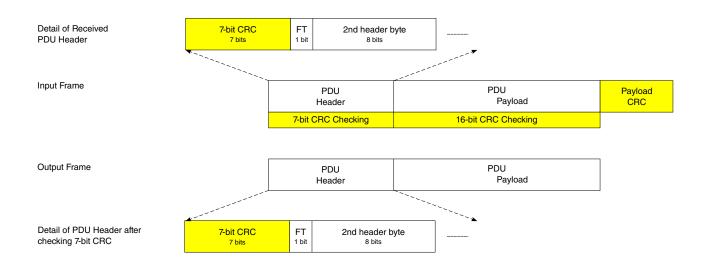

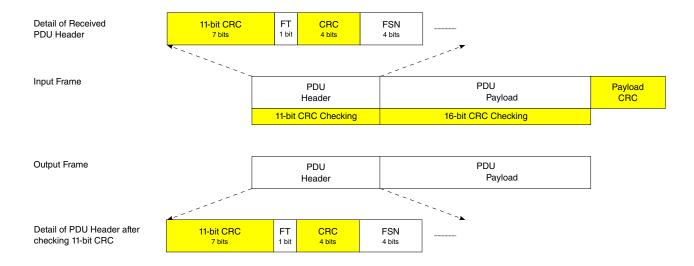

|                | 9.8.3                                                      | 3G doubl       | e-CRC decapsulation process                                                 | 450  |  |  |

|                |                                                            |                |                                                                             |      |  |  |

| Section number |         | nber        | Title                                                          | Page |

|----------------|---------|-------------|----------------------------------------------------------------|------|

|                |         | 9.8.3.1     | Calculating the 7-bit CRC of the PDU header for decapsulation  | 451  |

|                |         | 9.8.3.2     | Calculating the 11-bit CRC of the PDU header for decapsulation | 451  |

|                |         | 9.8.3.3     | Calculating the 16-bit payload CRC for decapsulation           | 452  |

|                | 9.8.4   | 3G doubl    | le-CRC decapsulation PDB format descriptions                   | 452  |

| 9.9            | 3G RLC  | PDU Enca    | psulation and Decapsulation overview                           | 453  |

|                | 9.9.1   | 3G RLC      | PDU encapsulation overview                                     | 453  |

|                | 9.9.2   | Process for | for 3G RLC PDU encapsulation                                   | 454  |

|                | 9.9.3   | 3G RLC      | PDU encapsulation PDB format descriptions                      | 455  |

|                | 9.9.4   | 3G RLC      | PDU decapsulation overview                                     | 456  |

|                | 9.9.5   | Process for | or 3G RLC PDU decapsulation                                    | 457  |

|                | 9.9.6   | 3G RLC      | PDU decapsulation PDB format descriptions                      | 458  |

|                | 9.9.7   | Overridin   | ng the PDB for 3G RLC PDU encapsulation and decapsulation      | 458  |

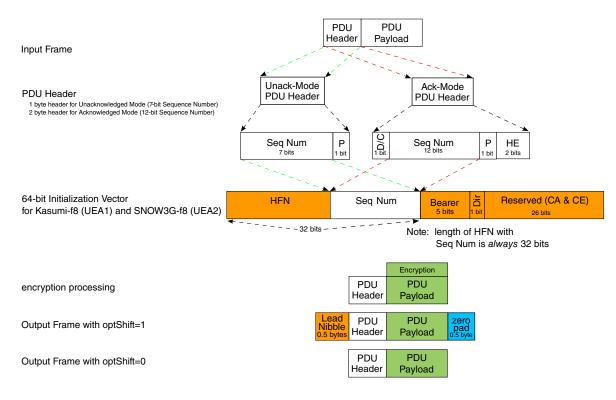

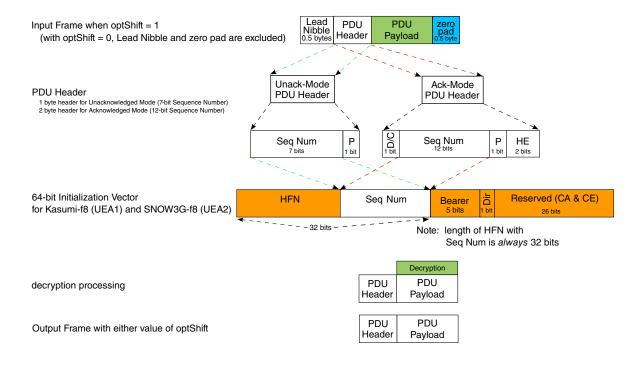

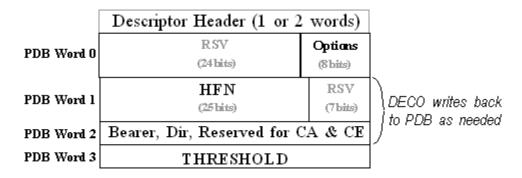

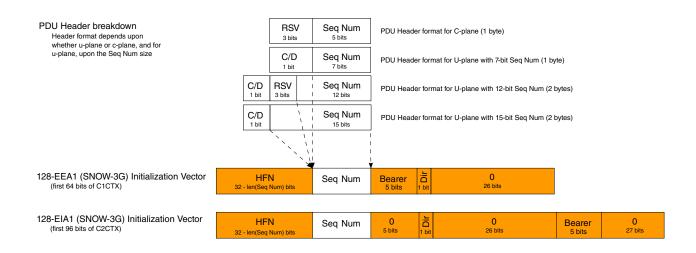

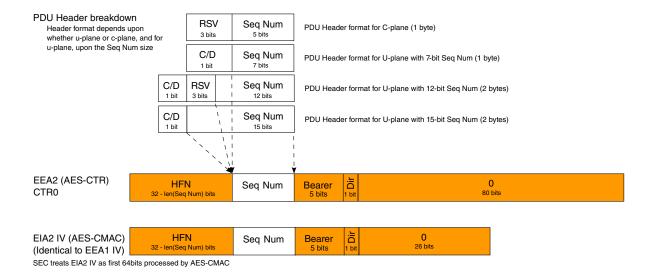

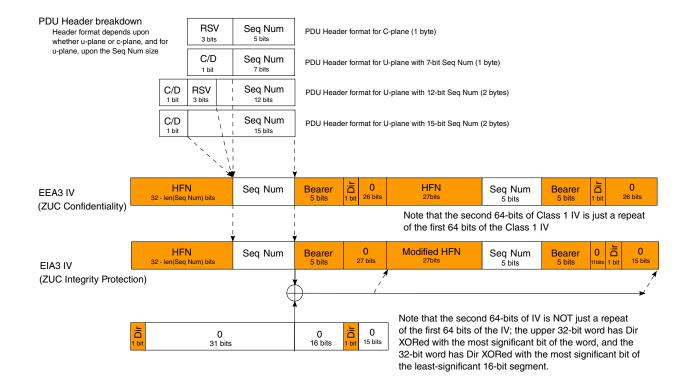

| 9.10           | LTE PD  | CP PDU en   | ncapsulation and decapsulation overview                        | 459  |

|                | 9.10.1  | LTE PDC     | CP PDU IV generation                                           | 460  |

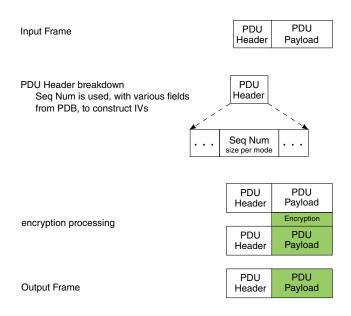

|                | 9.10.2  | LTE PDC     | CP PDU encapsulation process for confidentiality only          | 463  |

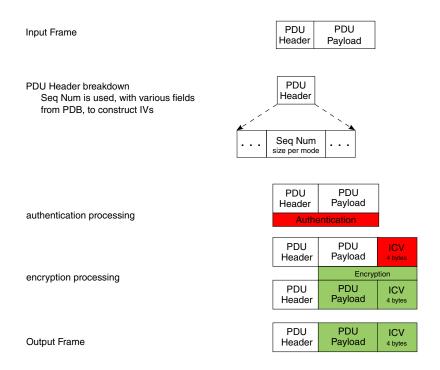

|                | 9.10.3  | LTE PDC     | CP PDU encapsulation for confidentiality and integrity         | 465  |

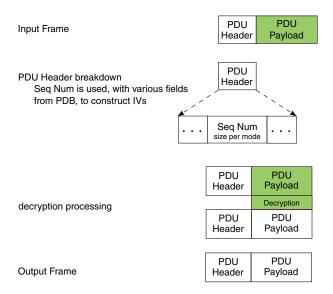

|                | 9.10.4  | LTE PDO     | CP PDU decapsulation process for confidentiality only          | 466  |

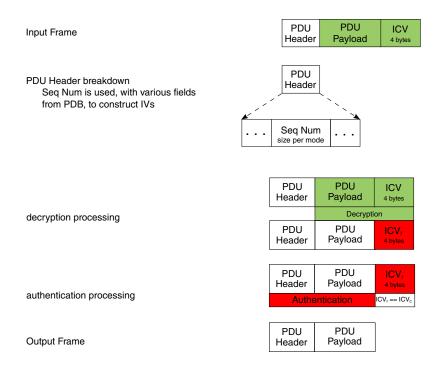

|                | 9.10.5  | LTE PDO     | CP PDU decapsulation for confidentiality and integrity         | 467  |

|                | 9.10.6  | LTE PDO     | CP shared descriptor PDB format descriptions                   | 469  |

|                | 9.10.7  | Overridin   | ng the PDB for LTE PDCP encapsulation and decapsulation        | 469  |

|                |         |             | Chapter 10<br>Key agreement functions                          |      |

| 10.1           | IKEv2 I | PRF overvie | w                                                              | 471  |

|                | 10.1.1  | Using IK    | E PRF to generate SKEYSEED.                                    | 472  |

|                | 10.1.2  | Using IK    | E PRF+ to generate keying material for the IKEv2 SA            | 472  |

|                | 10.1.3  | Using IK    | E PRF+ to generate Child SA key material                       | 473  |

|                | 10.1.4  | Restriction | ons on programming control blocks                              | 473  |

|                | 10.1.5  | IKE PRF     | PDB format descriptions                                        | 474  |

|                | 10.1.6  | Impleme     | ntation details for IKE PRF function                           | 477  |

|                |         |             |                                                                |      |

| Section number |                                            | nber        | Title                                                                 | Page |

|----------------|--------------------------------------------|-------------|-----------------------------------------------------------------------|------|

|                | 10.1.7                                     | Implement   | ation Details for IKE PRF+ function                                   | 478  |

| 10.2           | SSL/TL                                     | S/DTLS pseu | do-random functions (PRF)                                             | 479  |

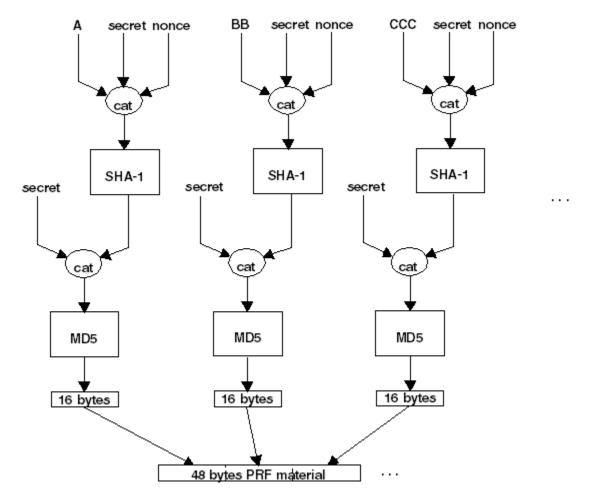

|                | 10.2.1                                     | SSL 3.0 PF  | RF overview                                                           | 479  |

|                |                                            | 10.2.1.1    | SSL 3.0 PRF definitions                                               | 480  |

|                | 10.2.2                                     | Process for | SSL 3.0 PRF                                                           | 481  |

|                | 10.2.3                                     | SSL 3.0 PF  | RF PDB format descriptions                                            | 481  |

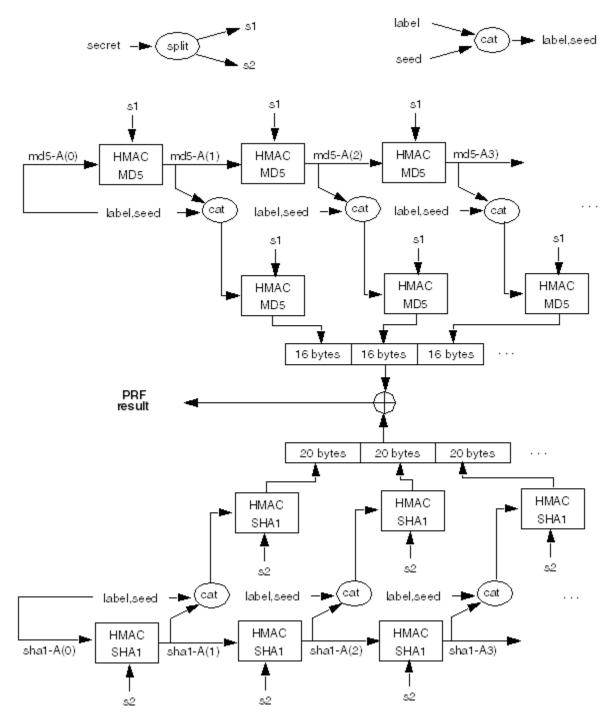

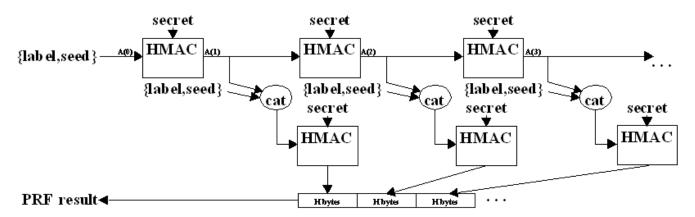

|                | 10.2.4                                     | TLS 1.0/TI  | LS 1.1/DTLS PRF overview                                              | 484  |

|                |                                            | 10.2.4.1    | TLS PRF RFC definitions.                                              | 486  |

|                | 10.2.5                                     | Process for | TLS 1.0, TLS 1.1, DTLS PRF                                            | 487  |

|                |                                            | 10.2.5.1    | How TLS uses PRF material.                                            | 487  |

|                |                                            | 10.2.5.2    | Concatenating input material into one input string (TLS 1.0/1.1/DTLS) | 488  |

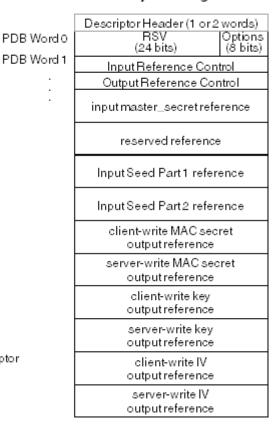

|                | 10.2.6                                     | TLS 1.0, T  | LS 1.1, DTLS PRF PDB format descriptions                              | 489  |

|                | 10.2.7                                     | TLS 1.2 PI  | RF overview                                                           | 492  |

|                | 10.2.8                                     | Process for | TLS 1.2 PRF                                                           | 493  |

|                |                                            | 10.2.8.1    | Concantenating input material into one input string (TLS 1.2)         | 494  |

|                |                                            | 10.2.8.2    | How TLS uses PRF material (TLS 1.2)                                   | 494  |

|                | 10.2.9                                     | TLS 1.2 PI  | RF PDB format descriptions.                                           | 495  |

| 10.3           | Implementation of the derived key protocol |             |                                                                       |      |

|                | 10.3.1                                     | Using DKI   | P with HMAC keys                                                      | 498  |

|                | 10.3.2                                     | Implement   | ation of the Blob Protocol                                            | 499  |

|                |                                            |             | Chapter 11 Cryptographic hardware accelerators (CHAs)                 |      |

| 11.1           | Public-k                                   | ey hardware | accelerator (PKHA) functionality                                      | 502  |

|                | 11.1.1                                     | Modular m   | nath                                                                  | 503  |

|                | 11.1.2                                     | About Mor   | ntgomery values                                                       | 503  |

|                | 11.1.3                                     | Non-modu    | lar Math                                                              | 505  |

|                | 11.1.4                                     | Elliptic-Cu | rve Math                                                              | 505  |

|                |                                            | 11.1.4.1    | Point math over a prime field (Fp)                                    | 506  |

|                |                                            | 11.1.4.2    | Point math over a binary field (F2m)                                  | 507  |

|                |                                            |             |                                                                       |      |

| Section number |           | Title                                                                                       |     |

|----------------|-----------|---------------------------------------------------------------------------------------------|-----|

|                | 11.1.4.3  | About Jacobian projective coordinates                                                       | 508 |

|                | 11.1.4.4  | About the Point at Infinity                                                                 | 509 |

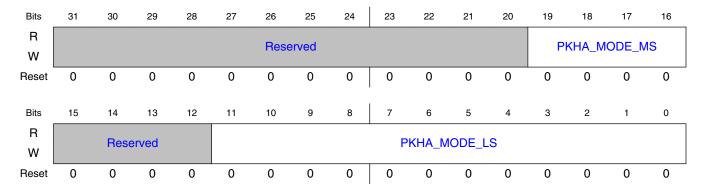

| 11.1.5         | PKHA Mo   | ode Register                                                                                | 509 |

| 11.1.6         | PKHA fun  | octions                                                                                     | 509 |

|                | 11.1.6.1  | Clear Memory (CLEAR_MEMORY) function                                                        | 510 |

|                | 11.1.6.2  | Integer Modular Addition (MOD_ADD) function                                                 | 512 |

|                | 11.1.6.3  | Integer Modular Subtraction (MOD_SUB_1) function                                            | 512 |

|                | 11.1.6.4  | Integer Modular Subtraction (MOD_SUB_2) function                                            | 513 |

|                | 11.1.6.5  | Integer Modular Multiplication (MOD_MUL)                                                    | 513 |

|                | 11.1.6.6  | Integer Modular Multiplication with Montgomery Inputs (MOD_MUL_IM)                          | 514 |

|                | 11.1.6.7  | Integer Modular Multiplication with Montgomery Inputs and Outputs (MOD_MUL_IM_OM) Function  | 515 |

|                | 11.1.6.8  | Integer Modular Exponentiation (MOD_EXP and MOD_EXP_TEQ)                                    | 515 |

|                | 11.1.6.9  | Integer Modular Exponentiation, Montgomery Input (MOD_EXP_IM and MOD_EXP_IM_TEQ) Function   | 516 |

|                | 11.1.6.10 | Integer Simultaneous Modular Exponentiation (MOD_SML_EXP)                                   | 517 |

|                | 11.1.6.11 | Integer Modular Square (MOD_SQR and MOD_SQR_TEQ)                                            | 518 |

|                | 11.1.6.12 | Integer Modular Square, Montgomery inputs (MOD_SQR_IM and MOD_SQR_IM_TEQ)                   | 518 |

|                | 11.1.6.13 | Integer Modular Square, Montgomery inputs and outputs (MOD_SQR_IM_OM and MOD_SQR_IM_OM_TEQ) | 519 |

|                | 11.1.6.14 | Integer Modular Cube (MOD_CUBE and MOD_CUBE_TEQ)                                            | 520 |

|                | 11.1.6.15 | Integer Modular Cube, Montgomery input (MOD_CUBE_IM and MOD_CUBE_IM_TEQ)                    | 520 |

|                | 11.1.6.16 | Integer Modular Cube, Montgomery input and output (MOD_CUBE_IM_OM and MOD_CUBE_IM_OM_TEQ)   | 521 |

|                | 11.1.6.17 | Integer Modular Square Root (MOD_SQRT)                                                      | 522 |

|                | 11.1.6.18 | Integer Modulo Reduction (MOD_AMODN)                                                        | 523 |

|                | 11.1.6.19 | Integer Modular Inversion (MOD_INV)                                                         | 523 |

|                | 11.1.6.20 | Integer Montgomery Factor Computation (MOD_R2)                                              | 524 |

|                |           |                                                                                             |     |

| Section number | Title                                                                                                     |     |

|----------------|-----------------------------------------------------------------------------------------------------------|-----|

| 11.1.6.21      | Integer Greatest Common Divisor (MOD_GCD)                                                                 | 524 |

| 11.1.6.22      | Miller_Rabin Primality Test (PRIME_TEST)                                                                  | 525 |

| 11.1.6.23      | Binary Polynomial (F2m) Addition (F2M_ADD) function                                                       | 525 |

| 11.1.6.24      | Binary Polynomial (F2m) Modular Multiplication (F2M_MUL)                                                  | 526 |

| 11.1.6.25      | Binary Polynomial (F2m) Modular Multiplication with Montgomery Inputs (F2M_MUL_IM) Function               | 527 |

| 11.1.6.26      | Binary Polynomial (F2m) Modular Multiplication with Montgomery Inputs and Output (F2M_MUL_IM_OM) Function |     |

| 11.1.6.27      | Binary Polynomial (F2m) Modular Exponentiation (F2M_EXP and F2M_EXP_TEQ).                                 | 528 |

| 11.1.6.28      | Binary Polynomial (F2m) Simultaneous Modular Exponentiation (F2M_SML_EXP)                                 | 529 |

| 11.1.6.29      | Binary Polynomial (F2m) Modular Square (F2M_SQR and F2M_SQR_TEQ)                                          | 530 |

| 11.1.6.30      | Binary Polynomial (F2m) Modular Square, Montgomery Input (F2M_SQR_IM and F2M_SQR_IM_TEQ)                  | 531 |

| 11.1.6.31      | Binary Polynomial (F2m) Modular Square, Montgomery Input and Output (F2M_SQR_IM_OM and F2M_SQR_IM_OM_TEQ) | 531 |

| 11.1.6.32      | Binary Polynomial (F2m) Modular Cube (F2M_CUBE and F2M_CUBE_TEQ)                                          | 532 |

| 11.1.6.33      | Binary Polynomial (F2m) Modular Cube, Montgomery Input (F2M_CUBE_IM and F2M_CUBE_IM_TEQ)                  | 533 |

| 11.1.6.34      | Binary Polynomial (F2m) Modular Cube, Montgomery Input and Output (F2M_CUBE_IM_OM and F2M_CUBE_IM_OM_TEQ) | 534 |

| 11.1.6.35      | Binary Polynomial (F2m) Modulo Reduction (F2M_AMODN)                                                      | 534 |

| 11.1.6.36      | Binary Polynomial (F2m) Modular Inversion (F2M_INV)                                                       | 535 |

| 11.1.6.37      | Binary Polynomial (F2m) R2 Mod N (F2M_R2) Function                                                        | 536 |

| 11.1.6.38      | Binary Polynomial (F2m) Greatest Common Divisor (F2M_GCD) Function                                        | 536 |

| 11.1.6.39      | ECC Fp Point Add, Affine Coordinates (ECC_MOD_ADD) Function                                               | 537 |

| 11.1.6.40      | ECC Fp Point Add, Affine Coordinates, R2 Mod N Input (ECC_MOD_ADD_R2) Function                            | 537 |

| 11.1.6.41      | ECC Fp Point Double, Affine Coordinates (ECC_MOD_DBL) Function                                            | 538 |

| 11.1.6.42      | ECC Fp Point Multiply, Affine Coordinates (ECC_MOD_MUL and ECC_MOD_MUL_TEQ) Function                      | 539 |

**Title**

**Page**

Section number

| Sect | ion nun  | nber Title                                         | Page |  |

|------|----------|----------------------------------------------------|------|--|

|      | 11.1.7   | Special values for common ECC domains              | 561  |  |

| 11.2 | Kasumi   | f8 and f9 hardware accelerator(KFHA) functionality | 580  |  |

|      | 11.2.1   | KFHA use of the Mode Register                      | 580  |  |

|      | 11.2.2   | KFHA use of the Context Register                   | 581  |  |

|      | 11.2.3   | KFHA use of the Key Register                       | 582  |  |

|      | 11.2.4   | KFHA use of the Data Size Register                 | 582  |  |

|      | 11.2.5   | KFHA error conditions.                             | 582  |  |

| 11.3 | Data enc | cryption standard accelerator (DES) functionality  | 583  |  |

|      | 11.3.1   | DESA use of the Mode Register.                     | 583  |  |

|      | 11.3.2   | DESA use of the Key Register                       | 584  |  |

|      | 11.3.3   | DESA use of the Key Size Register                  | 584  |  |

|      | 11.3.4   | DESA use of the Data Size Register                 | 584  |  |

|      | 11.3.5   | DESA Context Register                              | 585  |  |

|      | 11.3.6   | Save and store operations in DESA context data     | 585  |  |

| 11.4 | Cyclic-r | edundancy check accelerator (CRCA) functionality   | 585  |  |

|      | 11.4.1   | CRCA modes of operation                            | 586  |  |

|      | 11.4.2   | CRCA use of the Mode Register                      | 586  |  |

|      | 11.4.3   | CRCA Key Register                                  | 588  |  |

|      | 11.4.4   | CRCA Key Size Register                             | 588  |  |

|      | 11.4.5   | CRCA Data Size Register                            | 588  |  |

|      | 11.4.6   | CRCA Context Register                              | 588  |  |

|      | 11.4.7   | Save and restore operations in CRCA context data   | 589  |  |

| 11.5 | Random   | -number generator (RNG) functionality              | 589  |  |

|      | 11.5.1   | RNG features summary                               | 589  |  |

|      | 11.5.2   | RNG functional description                         | 590  |  |

|      |          | 11.5.2.1 RNG state handles                         | 590  |  |

|      |          | 11.5.2.2 RNG NIST certification                    | 590  |  |

|      | 11.5.3   | RNG operations.                                    | 592  |  |

|      | 11.5.4   | RNG use of the Key Registers                       | 593  |  |

|      |          |                                                    |      |  |

| Sect | Section number                      |               | Title                                                                  | Page |  |

|------|-------------------------------------|---------------|------------------------------------------------------------------------|------|--|

|      | 11.5.5                              | RNG use       | of the Context Register                                                | 593  |  |

|      | 11.5.6                              | RNG use       | of the Data Size Register                                              | 594  |  |

| 11.6 | SNOW                                | 3G f8 accele  | erator functionality                                                   | 594  |  |

|      | 11.6.1                              | Difference    | es between SNOW 3G f8 and SNOW 3G f9                                   | 594  |  |

|      | 11.6.2                              | SNOW 30       | G f8 use of the Mode Register                                          | 595  |  |

|      | 11.6.3                              | SNOW 30       | G f8 use of the Context Register                                       | 596  |  |

|      | 11.6.4                              | SNOW 30       | G f8 use of the Data Size Register                                     | 596  |  |

|      | 11.6.5                              | SNOW 30       | G f8 use of the Key Register                                           | 597  |  |

|      | 11.6.6                              | SNOW 30       | G f8 use of the Key Size Register                                      | 597  |  |

| 11.7 | SNOW                                | 3G f9 accele  | erator functionality                                                   | 597  |  |

|      | 11.7.1                              | SNOW 30       | G f9 use of the Mode Register                                          | 598  |  |

|      | 11.7.2                              | SNOW 30       | G f9 use of the Context Register                                       | 599  |  |

|      | 11.7.3                              | SNOW 30       | G f9 use of the Data Size Register                                     | 600  |  |

|      | 11.7.4                              | SNOW 30       | G f9 use of the Key Register                                           | 600  |  |

|      | 11.7.5                              | SNOW 30       | G f9 use of the Key Size Register                                      | 601  |  |

|      | 11.7.6                              | SNOW 30       | G f9 use of ICV check                                                  | 601  |  |

| 11.8 | Message                             | e digest hard | ware accelerator (MDHA) functionality                                  | 601  |  |

|      | 11.8.1                              | MDHA us       | se of the Mode Register                                                | 602  |  |

|      | 11.8.2 MDHA use of the Key Register |               | 603                                                                    |      |  |

|      |                                     | 11.8.2.1      | Using the MDHA Key Register with normal keys                           | 603  |  |

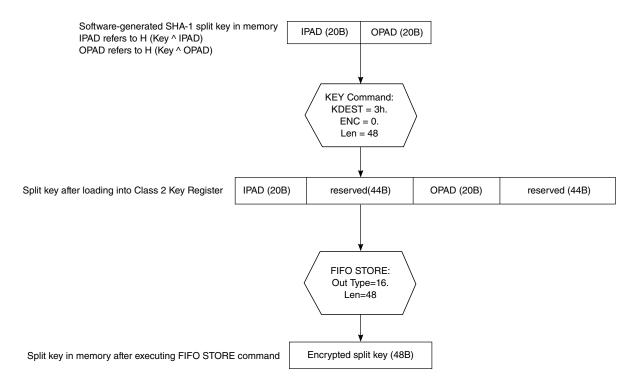

|      |                                     | 11.8.2.2      | Using the MDHA Key Register with IPAD/OPAD "split keys"                | 603  |  |

|      |                                     |               | 11.8.2.2.1 Definition and function of IPAD/OPAD split keys             | 604  |  |

|      |                                     |               | 11.8.2.2.2 Process flow of using the Key Register with split keys      | 604  |  |

|      |                                     |               | 11.8.2.2.3 Using padding with the split key type to align with storage | 604  |  |

|      |                                     |               | 11.8.2.2.4 Length of a split key                                       | 604  |  |

|      |                                     |               | 11.8.2.2.5 Loading/storing a split key with a key command              | 604  |  |

|      |                                     |               | 11.8.2.2.6 Loading/storing a split key with a FIFO STORE command       | 605  |  |

|      |                                     |               | 11.8.2.2.7 Sizes of split keys                                         | 605  |  |

|      |                                     |               | 11.8.2.2.8 Constructing an HMAC-SHA-1 split key in memory              | 605  |  |

| Section number |         | nber          | Title                                                        | Page |

|----------------|---------|---------------|--------------------------------------------------------------|------|

|                |         | 11.8.2.3      | MDHA use of the Key Size Register                            | 606  |

|                | 11.8.3  | MDHA us       | se of the Data Size Register                                 | 606  |

|                | 11.8.4  | MDHA us       | se of the Context Register                                   | 607  |

|                | 11.8.5  | Save and 1    | restore operations in MDHA context data                      | 607  |

| 11.9           | AES acc | celerator (AE | ESA) functionality                                           | 607  |

|                | 11.9.1  | Difference    | es between the AES encrypt and decrypt keys                  | 607  |

|                | 11.9.2  | AESA as l     | both Class 1 and Class 2 CHA                                 | 608  |

|                | 11.9.3  | AESA mo       | odes of operation                                            | 609  |

|                | 11.9.4  | AESA use      | e of registers                                               | 610  |

|                | 11.9.5  | AESA use      | e of the parity bit                                          | 611  |

|                | 11.9.6  | AES ECB       | mode                                                         | 611  |

|                |         | 11.9.6.1      | AES ECB mode use of the Mode Register                        | 611  |

|                |         | 11.9.6.2      | AES ECB mode use of the Context Register                     | 612  |

|                |         | 11.9.6.3      | AES ECB Mode use of the Data Size Register                   | 612  |

|                |         | 11.9.6.4      | AES ECB Mode use of the Key Register                         | 612  |

|                |         | 11.9.6.5      | AES ECB Mode use of the Key Size Register                    | 612  |

|                | 11.9.7  | AES CBC       | C, OFB, CFB128 modes                                         | 613  |

|                |         | 11.9.7.1      | AES CBC, OFB, and CFB128 modes use of the Mode Register      | 613  |

|                |         | 11.9.7.2      | AES CBC, OFB, and CFB128 modes use of the Context Register   | 614  |

|                |         | 11.9.7.3      | AES CBC, OFB, and CFB128 modes use of the Data Size Register | 614  |

|                |         | 11.9.7.4      | AES CBC, OFB, and CFB128 modes use of the Key Register       | 615  |

|                |         | 11.9.7.5      | AES CBC, OFB, and CFB128 modes use of the Key Size Register  | 615  |

|                | 11.9.8  | AES CTR       | mode                                                         | 615  |

|                |         | 11.9.8.1      | AES CTR mode use of the Mode Register                        | 615  |

|                |         | 11.9.8.2      | AES CTR mode use of the Context Register                     | 616  |

|                |         | 11.9.8.3      | AES CTR mode use of the Data Size Register                   | 616  |

|                |         | 11.9.8.4      | AES CTR mode use of the Key Register                         | 616  |

|                |         | 11.9.8.5      | AES CTR mode use of the Key Size Register                    | 617  |

|                | 11.9.9  | AES XTS       | mode                                                         | 617  |

|                |         |               |                                                              |      |

| Section number |           | Title                                                            | Page |  |

|----------------|-----------|------------------------------------------------------------------|------|--|

|                | 11.9.9.1  | AES XTS mode use of the Mode Register                            | 617  |  |

|                | 11.9.9.2  | AES XTS mode use of the Context Register                         | 617  |  |

|                | 11.9.9.3  | AES XTS mode use of the Data Size Register                       | 618  |  |

|                | 11.9.9.4  | AES XTS mode use of the Key Register                             | 618  |  |

|                | 11.9.9.5  | AES XTS mode use of the Key Size Register                        | 619  |  |

| 11.9.10        | AES XCB   | C-MAC and CMAC modes.                                            | 619  |  |

|                | 11.9.10.1 | AES XCBC-MAC and CMAC modes use of the Mode Register             | 619  |  |

|                | 11.9.10.2 | AES XCBC-MAC and CMAC Modes use of the Context Register          | 621  |  |

|                | 11.9.10.3 | AES XCBC-MAC and CMAC modes use of the Class 1 ICV Size Register | 621  |  |

|                | 11.9.10.4 | AES XCBC-MAC and CMAC modes use of the Data Size Register        | 622  |  |

|                | 11.9.10.5 | AES XCBC-MAC and CMAC modes use of the Key Register              | 622  |  |

|                | 11.9.10.6 | AES XCBC-MAC and CMAC modes use of the Key Size Register         | 622  |  |

|                | 11.9.10.7 | ICV checking in AES XCBC-MAC and CMAC modes                      | 622  |  |

| 11.9.11        | AESA CC   | M mode                                                           | 623  |  |

|                | 11.9.11.1 | Generation encryption.                                           | 623  |  |

|                | 11.9.11.2 | Decryption verification.                                         | 623  |  |

|                | 11.9.11.3 | AES CCM mode use of the Mode Register                            | 624  |  |

|                | 11.9.11.4 | AES CCM mode use of the Context Register                         | 625  |  |

|                | 11.9.11.5 | AES CCM mode use of the Data Size Register                       | 626  |  |

|                | 11.9.11.6 | AES CCM mode use of the Key Register                             | 626  |  |

|                | 11.9.11.7 | AES CCM mode use of the Key Size Register                        | 626  |  |

|                | 11.9.11.8 | AES CCM mode use of the ICV check                                | 627  |  |

| 11.9.12        | AES GCM   | I mode                                                           | 627  |  |

|                | 11.9.12.1 | GMAC                                                             | 628  |  |

|                | 11.9.12.2 | GCM data types                                                   | 628  |  |

|                | 11.9.12.3 | IV processing                                                    | 628  |  |

|                | 11.9.12.4 | GCM initialization.                                              | 628  |  |

|                | 11.9.12.5 | AES GCM mode use of the Mode Register                            | 628  |  |

|                | 11.9.12.6 | AES GCM mode use of the Context Register                         | 630  |  |

|                |           |                                                                  |      |  |

| Secti | ection number |               | Title                                                       | Page |

|-------|---------------|---------------|-------------------------------------------------------------|------|

|       |               | 11.9.12.7     | AES GCM Mode use of the Data Size Register                  | 630  |

|       |               | 11.9.12.8     | AES GCM mode use of the Class 1 IV Size Register            | 631  |

|       |               | 11.9.12.9     | AES GCM mode use of the AAD Size Register                   | 631  |

|       |               | 11.9.12.10    | AES GCM mode use of the Class 1 ICV Size Register           | 631  |

|       |               | 11.9.12.11    | AES GCM mode use of the Key Register                        | 631  |

|       |               | 11.9.12.12    | AES GCM mode use of the Key Size Register                   | 631  |

|       |               | 11.9.12.13    | AES GCM mode use of the ICV check                           | 632  |

|       | 11.9.13       | AESA optii    | mization modes.                                             | 632  |

|       |               | 11.9.13.1     | CTR-XCBC and CTR-CMAC modes data format                     | 632  |

|       |               | 11.9.13.2     | CTR-XCBC and CTR-CMAC modes message format                  | 632  |

|       |               | 11.9.13.3     | CTR-CMAC-LTE for LTE PDCP control-plane processing          | 633  |

|       |               | 11.9.13.4     | Authentication-only data                                    | 633  |

|       |               | 11.9.13.5     | AES optimization modes use of the Mode Register             | 633  |

|       |               | 11.9.13.6     | AES optimization modes use of the Context Register          | 635  |

|       |               | 11.9.13.7     | AES optimization modes use of the Data Size Register        | 638  |

|       |               | 11.9.13.8     | AES optimization modes use of the AAD Size Register         | 639  |

|       |               | 11.9.13.9     | AES optimization modes use of the Class 1 ICV Size Register | 639  |

|       |               | 11.9.13.10    | AES optimization modes use of the Class 1 Key Register      | 640  |

|       |               | 11.9.13.11    | AES optimization modes use of the Class 2 Key Register      | 640  |

|       |               | 11.9.13.12    | AES optimization modes use of the Class 1 Key Size Register | 640  |

|       |               | 11.9.13.13    | AES optimization modes use of the Class 2 Key Size Register | 641  |

|       |               | 11.9.13.14    | AES optimization modes use of the ICV check                 | 641  |

|       |               | 11.9.13.15    | AES optimization modes error conditions                     | 641  |

| 11.10 | ZUC enc       | ryption accel | erator (ZUCE) functionality                                 | 643  |

|       | 11.10.1       | Differences   | between ZUCE and ZUCA                                       | 643  |

|       | 11.10.2       | ZUCE use      | of the Mode Register                                        | 644  |

|       | 11.10.3       | ZUCE use      | of the Context Register                                     | 644  |

|       | 11.10.4       | ZUCE use      | of the Data Size Register                                   | 645  |

|       | 11.10.5       | ZUCE use      | of the Key Register                                         | 645  |

|       |               |               |                                                             |      |

| Secti | ion num   | nber Title                                                  | Page |

|-------|-----------|-------------------------------------------------------------|------|

|       | 11.10.6   | ZUCE use of the Key Size Register                           | 646  |

| 11.11 | ZUC aut   | thentication accelerator (ZUCA) functionality               | 646  |

|       | 11.11.1   | ZUCA use of the Mode Register                               | 646  |

|       | 11.11.2   | ZUCA use of the Context Register                            | 647  |

|       | 11.11.3   | ZUCA use of the Data Size Register                          | 649  |

|       | 11.11.4   | ZUCA use of the Key Register                                | 649  |

|       | 11.11.5   | ZUCA use of the Key Size Register                           | 649  |

|       | 11.11.6   | ZUCA use of ICV checking                                    | 649  |

|       |           | Chapter 12<br>Trust Architecture modules                    |      |

| 12.1  | Run-time  | e integrity checker (RTIC)                                  | 651  |

|       | 12.1.1    | RTIC modes of operation                                     | 651  |

|       | 12.1.2    | RTIC initialization and operation                           | 651  |

|       | 12.1.3    | RTIC use of the Throttle Register                           | 652  |

|       | 12.1.4    | RTIC use of command, configuration, and status registers    | 652  |

|       | 12.1.5    | Initializing RTIC                                           | 653  |

|       | 12.1.6    | RTIC Memory Block Address/Length Registers                  | 653  |

| 12.2  | SEC virt  | 654                                                         |      |

|       | 12.2.1    | Virtualization.                                             |      |

|       | 12.2.2    | Security domain identifiers (SDIDs)                         | 654  |

|       | 12.2.3    | TrustZone SecureWorld                                       | 655  |

| 12.3  | Special-1 | purpose cryptographic keys                                  | 655  |

|       | 12.3.1    | Initializing and clearing black and trusted descriptor keys | 656  |

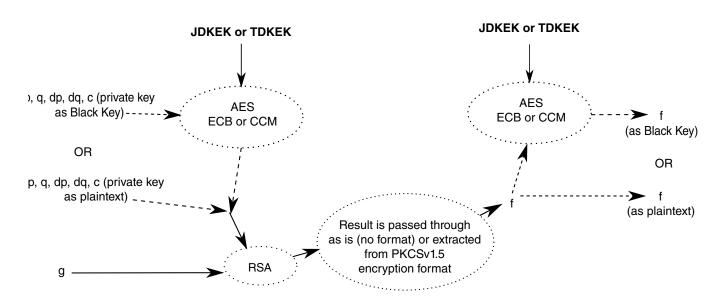

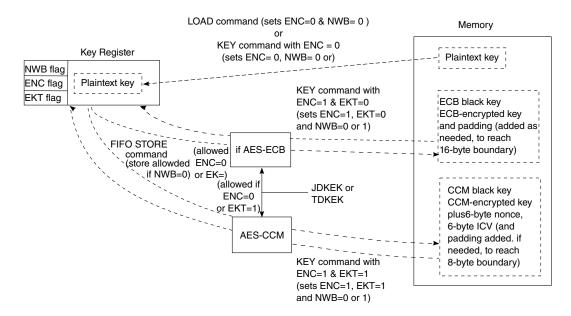

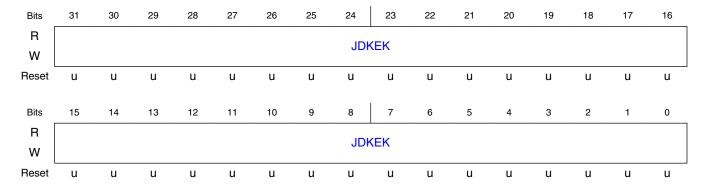

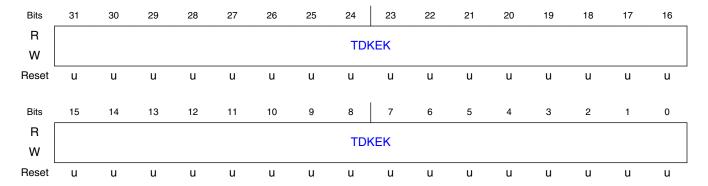

|       | 12.3.2    | Black keys and JDKEK/TDKEK                                  | 656  |

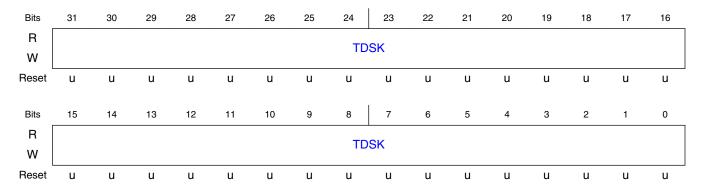

|       | 12.3.3    | Trusted descriptors and TDSK                                | 656  |

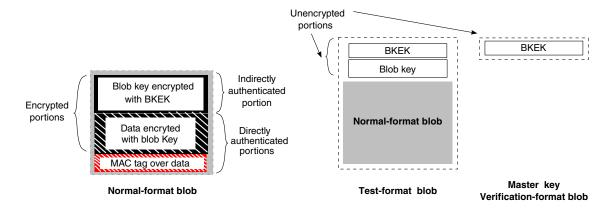

|       | 12.3.4    | Master key and blobs                                        | 656  |

| 12.4  | Black ke  | eys                                                         | 657  |

|       | 12.4.1    | Black key encapsulation schemes                             | 657  |

|       | 12.4.2    | Differences between black and red keys                      | 657  |

| 12.4.3<br>12.4.4 | Loading red keys                                                                                                        | 658                                                    |