### **Freescale Semiconductor**

MCF54455RM Rev. 6.1, 03/2012

## MCF54455 Reference Manual

by: Microcontroller Solutions Group

This is the MCF54455 Reference Manual set consisting of the following files:

- MCF54455 Reference Manual Errata, Rev 1

- MCF54455 Reference Manual, Rev 6

© Freescale Semiconductor, Inc., 2012. All rights reserved.

### **Freescale Semiconductor**

**Reference Manual Errata**

MCF54455RMAD Rev. 1, 11/2011

## MCF54455 Reference Manual Errata

by: Microcontroller Solutions Group

This errata document describes corrections to the *MCF54455 Reference Manual*, order number MC54455RM. For convenience, the addenda items are grouped by revision. Please check our website at http://www.freescale.com for the latest updates.

The current available version of the *MCF54455 Reference Manual* is Revision 6.

### Table of Contents

| 1 | Errata for Revision 6 | 2 |

|---|-----------------------|---|

| 2 | Revision History      | 2 |

Errata for Revision 6

## 1 Errata for Revision 6

### Table 1. MCF54455 Reference Manual Rev 6 Errata

| Location                                                                | Description                                        |

|-------------------------------------------------------------------------|----------------------------------------------------|

| Section 16.2, "External Signal<br>Description"/Table 16-2/Page<br>16-11 | Add pin N7 to the VSS pin list for the 360 TEPBGA. |

## 2 Revision History

Table 2 provides a revision history for this document.

Table 2. Revision History Table

| Rev. Number | Substantive Changes                                                             | Date of Release |

|-------------|---------------------------------------------------------------------------------|-----------------|

| 1.0         | Initial release. Correct errors in section 16.2, "External Signal Description". | 11/2011         |

### THIS PAGE IS INTENTIONALLY LEFT BLANK

### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2011. All rights reserved.

MCF54455RMAD Rev. 1 November 2011

## **MCF54455 Reference Manual**

### **Devices Supported:**

MCF54450 MCF54451 MCF54452 MCF54453 MCF54454 MCF54455

Document Number: MCF54455RM Rev. 6 5/2011

## NP

### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2009, 2011. All rights reserved.

MCF54455RM Rev. 6 5/2011

## **Table of Contents**

| About This Book             | xxv   |

|-----------------------------|-------|

| Audience                    | xxv   |

| Suggested Reading           | xxv   |

| General Information         |       |

| ColdFire Documentation      | xxvi  |

| Conventions                 | xxvi  |

| Register Figure Conventions | xxvii |

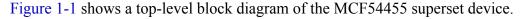

## Chapter 1 Overview

| MCF54   | 45 <i>x</i> Family Comparison                                                                                                                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block D | Diagram                                                                                                                                                                                                                                                    |

| Operati | ng Parameters                                                                                                                                                                                                                                              |

| Packag  | les                                                                                                                                                                                                                                                        |

| Chip Le | evel Features                                                                                                                                                                                                                                              |

| Module  | -by-Module Feature List                                                                                                                                                                                                                                    |

| 1.6.1   | Version 4 ColdFire variable-length RISC processor                                                                                                                                                                                                          |

| 1.6.2   | On-chip Memories                                                                                                                                                                                                                                           |

| 1.6.3   | Phase Locked Loop (PLL)                                                                                                                                                                                                                                    |

| 1.6.4   | Power Management                                                                                                                                                                                                                                           |

| 1.6.5   | Chip Configuration Module (CCM) 1-5                                                                                                                                                                                                                        |

| 1.6.6   | Reset Controller                                                                                                                                                                                                                                           |

| 1.6.7   | System Control Module                                                                                                                                                                                                                                      |

| 1.6.8   | Crossbar Switch                                                                                                                                                                                                                                            |

| 1.6.9   | Peripheral Component Interconnect (PCI) Bus1-6                                                                                                                                                                                                             |

| 1.6.10  | Universal Serial Bus (USB) 2.0 On-The-Go (OTG) Controller 1-6                                                                                                                                                                                              |

|         | DDR SDRAM Controller 1-6                                                                                                                                                                                                                                   |

| 1.6.12  | FlexBus (External Interface) 1-7                                                                                                                                                                                                                           |

| 1.6.13  | Synchronous Serial Interface (SSI) 1-7                                                                                                                                                                                                                     |

| 1.6.14  | ATA Controller                                                                                                                                                                                                                                             |

| 1.6.15  | Fast Ethernet Media Access Controller (FEC MAC)    1-7                                                                                                                                                                                                     |

| 1.6.16  | Random Number Generator (RNG)    1-8                                                                                                                                                                                                                       |

| -       | Real Time Clock   1-8                                                                                                                                                                                                                                      |

|         | Software Watchdog Timer 1-8                                                                                                                                                                                                                                |

|         | Programmable Interrupt Timers (PIT) 1-8                                                                                                                                                                                                                    |

| 1.6.20  | DMA Timers                                                                                                                                                                                                                                                 |

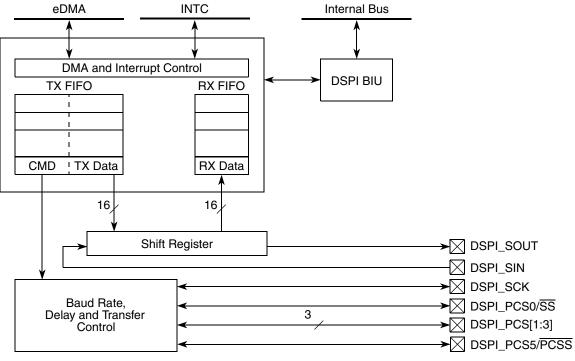

| 1.6.21  | DMA Serial Peripheral Interface (DSPI) 1-8                                                                                                                                                                                                                 |

| 1.6.22  | Universal Asynchronous Receiver Transmitters (UARTs) 1-9                                                                                                                                                                                                   |

|         | Block D<br>Operati<br>Packag<br>Chip Le<br>Module<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4<br>1.6.5<br>1.6.6<br>1.6.7<br>1.6.8<br>1.6.9<br>1.6.10<br>1.6.11<br>1.6.12<br>1.6.13<br>1.6.14<br>1.6.15<br>1.6.16<br>1.6.17<br>1.6.18<br>1.6.19<br>1.6.20<br>1.6.21 |

|     | 1.6.23 | I2C Module                      | 1-9 |

|-----|--------|---------------------------------|-----|

|     | 1.6.24 | Interrupt Controllers           | 1-9 |

|     | 1.6.25 | Edge Port Module                | 1-9 |

|     | 1.6.26 | DMA Controller                  | 1-9 |

|     | 1.6.27 | General Purpose I/O interface 1 | -10 |

|     | 1.6.28 | System Debug Support 1          | -10 |

|     | 1.6.29 | JTAG Support 1                  | -10 |

| 1.7 | Memor  | y Map Overview                  | -10 |

|     | 1.7.1  | Internal Peripheral Space 1     | -11 |

| 1.8 | Docum  | entation                        | -12 |

## Chapter 2 Signal Descriptions

| 2.1 | Introduo | ction                                            | 2-1    |

|-----|----------|--------------------------------------------------|--------|

| 2.2 | Signal I | Properties Summary                               | 2-1    |

| 2.3 |          | Primary Functions                                |        |

|     | 2.3.1    | Reset Signals                                    | 2-9    |

|     | 2.3.2    | PLL and Clock Signals                            | . 2-10 |

|     | 2.3.3    | Mode Selection                                   | . 2-10 |

|     | 2.3.4    | FlexBus Signals                                  | . 2-11 |

|     | 2.3.5    | SDRAM Controller Signals                         | . 2-12 |

|     | 2.3.6    | PCI Controller Signals                           | . 2-13 |

|     | 2.3.7    | Serial Boot Facility Signals                     | . 2-14 |

|     | 2.3.8    | External Interrupt Signals                       | . 2-14 |

|     | 2.3.9    | DMA Signals                                      | . 2-14 |

|     | 2.3.10   | Fast Ethernet Controller (FEC0 and FEC1) Signals | . 2-14 |

|     | 2.3.11   | I2C I/O Signals                                  | . 2-15 |

|     | 2.3.12   | ATA Controller Signals                           | . 2-16 |

|     | 2.3.13   | DMA Serial Peripheral Interface (DSPI) Signals   | . 2-17 |

|     | 2.3.14   | Synchronous Serial Interface (SSI) Signals       | . 2-17 |

|     | 2.3.15   | Universal Serial Bus (USB) Signals               | . 2-18 |

|     | 2.3.16   | UART Module Signals                              | . 2-18 |

|     | 2.3.17   | DMA Timer Signals                                | . 2-19 |

|     | 2.3.18   | Debug Support Signals                            | . 2-19 |

|     | 2.3.19   | Test Signals                                     | . 2-20 |

|     |          | Power and Ground Pins                            |        |

| 2.4 | Externa  | al Boot Mode                                     | . 2-21 |

|     |          |                                                  |        |

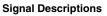

### Chapter 3 ColdFire Core

| 3.1 | Introduc | tion     | 3-2 |

|-----|----------|----------|-----|

|     | 3.1.1    | Overview | 3-2 |

| 3.2 | Memor   | y Map/Register Description                       |

|-----|---------|--------------------------------------------------|

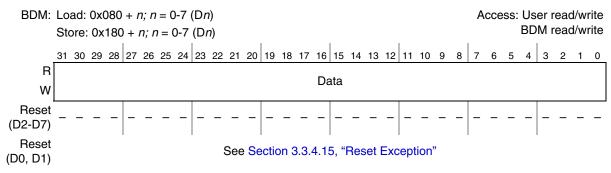

|     | 3.2.1   | Data Registers (D0–D7) 3-7                       |

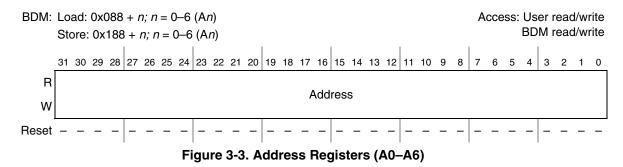

|     | 3.2.2   | Address Registers (A0–A6)                        |

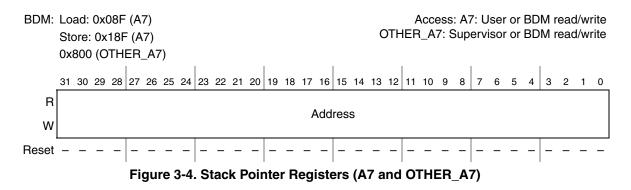

|     | 3.2.3   | Supervisor/User Stack Pointers (A7 and OTHER_A7) |

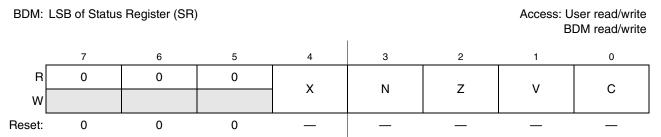

|     | 3.2.4   | Condition Code Register (CCR)                    |

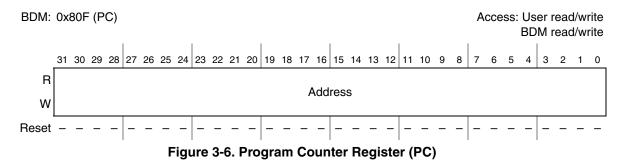

|     | 3.2.5   | Program Counter (PC)                             |

|     | 3.2.6   | Cache Programming Model                          |

|     | 3.2.7   | MMU Programming Model                            |

|     | 3.2.8   | Vector Base Register (VBR) 3-10                  |

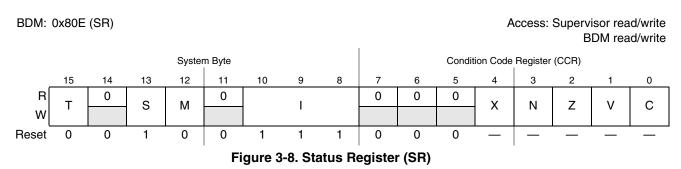

|     | 3.2.9   | Status Register (SR)                             |

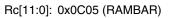

|     | 3.2.10  | Memory Base Address Register (RAMBAR)            |

| 3.3 | Functio | nal Description                                  |

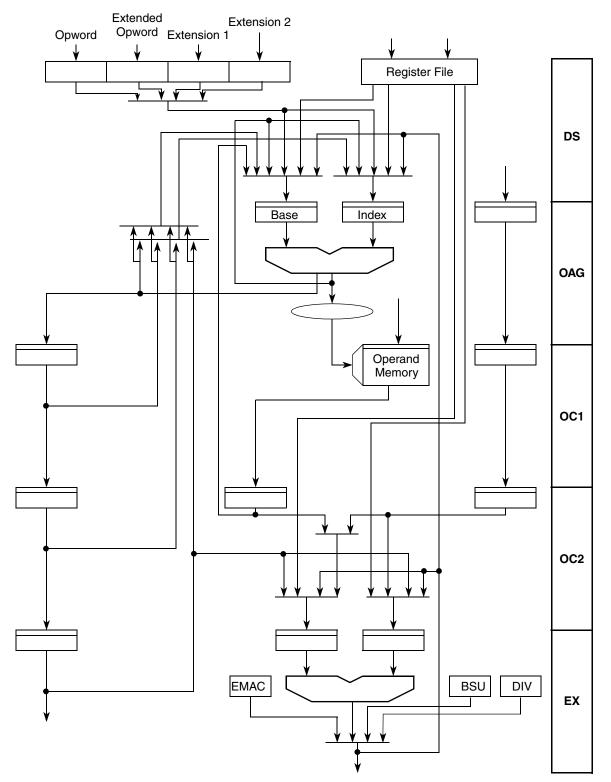

|     | 3.3.1   | Version 4 ColdFire Microarchitecture             |

|     | 3.3.2   | Instruction Set Architecture (ISA_C)             |

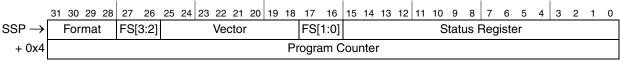

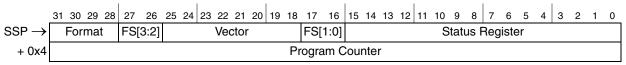

|     | 3.3.3   | Exception Processing Overview                    |

|     | 3.3.4   | Processor Exceptions                             |

|     | 3.3.5   | Instruction Execution Timing                     |

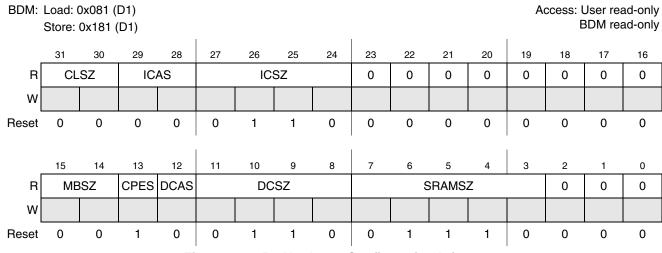

## Chapter 4 Memory Management Unit (MMU)

| <ul> <li>4.1.1 Block Diagram</li> <li>4.1.2 Features</li> <li>4.2 Memory Map/Register Definition</li> <li>4.2.1 Address Space ID (ASID)</li> <li>4.2.2 MMU Base Address Register (MMUBAR)</li> <li>4.2.3 MMU Control Register (MMUCR)</li> <li>4.2.4 MMU Operation Register (MMUOR)</li> <li>4.2.5 MMU Status Register (MMUSR)</li> <li>4.2.6 MMU Fault, Test, or TLB Address Register (MMUAR)</li> <li>4.2.7 MMU Read/Write Tag Entry Registers (MMUTR)</li> <li>4.2.8 MMU Read/Write Data Entry Register (MMUDR)</li> <li>4.3 Functional Description</li> <li>4.3.1 Virtual Memory Management Architecture</li> <li>4.3.3 Virtual Memory Architecture Processor Support</li> <li>4.3.4 Effective Address Attribute Determination</li> <li>4.3.5 MMU Functionality</li> <li>4.3.6 MMU TLB</li> <li>4.3.8 MMU Implementation</li> <li>4.3.9 MMU Inplementation</li> </ul> | 4.1 Introduction |         | ction                                            | . 4-1 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|--------------------------------------------------|-------|

| <ul> <li>4.2 Memory Map/Register Definition</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | 4.1.1   | Block Diagram                                    | . 4-1 |

| 4.2.1       Address Space ID (ASID)         4.2.2       MMU Base Address Register (MMUBAR)         4.2.3       MMU Control Register (MMUCR)         4.2.4       MMU Operation Register (MMUOR)         4.2.5       MMU Status Register (MMUSR)         4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.8       MMU Operation                          |                  | 4.1.2   | Features                                         | . 4-2 |

| 4.2.2       MMU Base Address Register (MMUBAR)         4.2.3       MMU Control Register (MMUCR)         4.2.4       MMU Operation Register (MMUOR)         4.2.5       MMU Status Register (MMUSR)         4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation                                                | 4.2              | Memor   | y Map/Register Definition                        | . 4-3 |

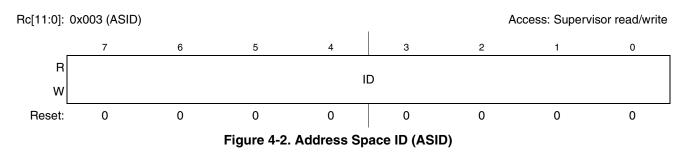

| 4.2.3       MMU Control Register (MMUCR)         4.2.4       MMU Operation Register (MMUOR)         4.2.5       MMU Status Register (MMUSR)         4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                  |                  | 4.2.1   | Address Space ID (ASID)                          | . 4-4 |

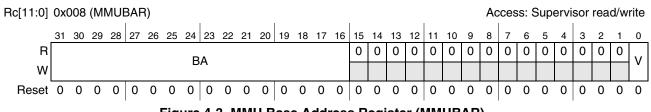

| 4.2.4       MMU Operation Register (MMUOR)         4.2.5       MMU Status Register (MMUSR)         4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                                       |                  | 4.2.2   | MMU Base Address Register (MMUBAR)               | . 4-4 |

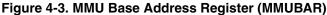

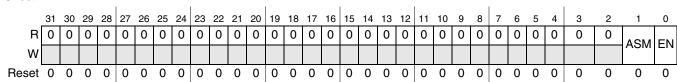

| 4.2.5       MMU Status Register (MMUSR)         4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                                                                                          |                  | 4.2.3   | MMU Control Register (MMUCR)                     | . 4-5 |

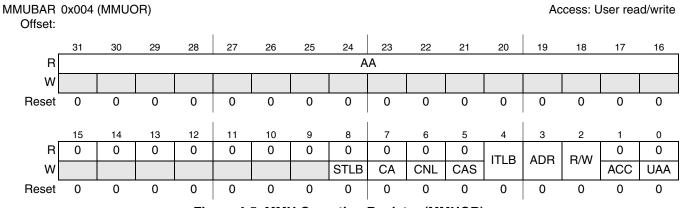

| 4.2.6       MMU Fault, Test, or TLB Address Register (MMUAR)         4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                                                                                                                                          |                  | 4.2.4   | MMU Operation Register (MMUOR)                   | . 4-6 |

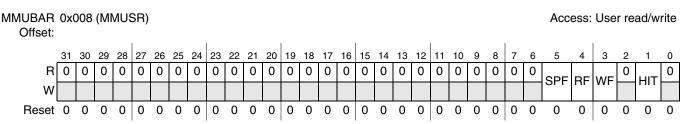

| 4.2.7       MMU Read/Write Tag Entry Registers (MMUTR)         4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                                                                                                                                                                                                               |                  | 4.2.5   | MMU Status Register (MMUSR)                      | . 4-7 |

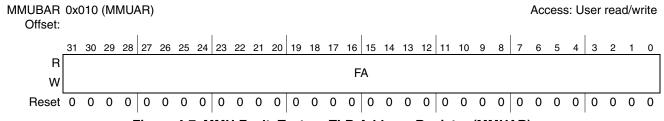

| 4.2.8       MMU Read/Write Data Entry Register (MMUDR)         4.3       Functional Description         4.3.1       Virtual Memory Management Architecture         4.3.2       Debugging in a Virtual Environment         4.3.3       Virtual Memory Architecture Processor Support         4.3.4       Effective Address Attribute Determination         4.3.5       MMU Functionality         4.3.6       MMU TLB         4.3.7       MMU Operation         4.3.8       MMU Implementation                                                                                                                                                                                                                                                                                                                                                                              |                  | 4.2.6   | MMU Fault, Test, or TLB Address Register (MMUAR) | . 4-8 |

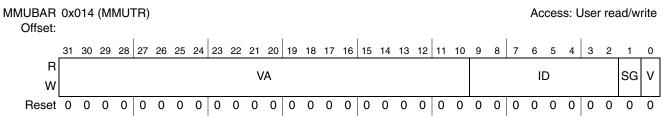

| 4.3       Functional Description       4         4.3.1       Virtual Memory Management Architecture       4         4.3.2       Debugging in a Virtual Environment       4         4.3.3       Virtual Memory Architecture Processor Support       4         4.3.4       Effective Address Attribute Determination       4         4.3.5       MMU Functionality       4         4.3.6       MMU TLB       4         4.3.7       MMU Operation       4         4.3.8       MMU Implementation       4                                                                                                                                                                                                                                                                                                                                                                     |                  | 4.2.7   | MMU Read/Write Tag Entry Registers (MMUTR)       | . 4-8 |

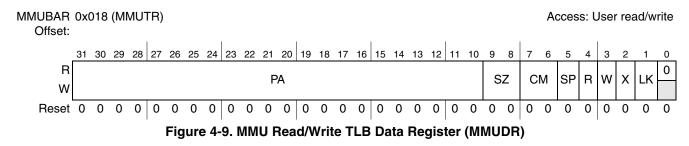

| 4.3.1Virtual Memory Management Architecture44.3.2Debugging in a Virtual Environment44.3.3Virtual Memory Architecture Processor Support44.3.4Effective Address Attribute Determination44.3.5MMU Functionality44.3.6MMU TLB44.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | 4.2.8   | MMU Read/Write Data Entry Register (MMUDR)       | . 4-9 |

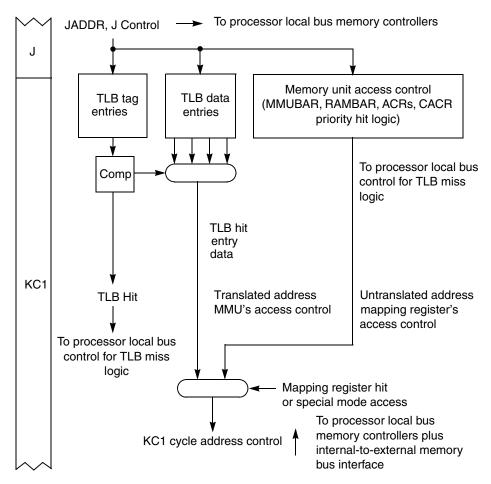

| 4.3.2Debugging in a Virtual Environment44.3.3Virtual Memory Architecture Processor Support44.3.4Effective Address Attribute Determination44.3.5MMU Functionality44.3.6MMU TLB44.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.3              | Functio | nal Description                                  | 4-10  |

| 4.3.3Virtual Memory Architecture Processor Support44.3.4Effective Address Attribute Determination44.3.5MMU Functionality44.3.6MMU TLB44.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | 4.3.1   | Virtual Memory Management Architecture           | 4-11  |

| 4.3.4Effective Address Attribute Determination44.3.5MMU Functionality44.3.6MMU TLB44.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | 4.3.2   | Debugging in a Virtual Environment               | 4-15  |

| 4.3.5MMU Functionality44.3.6MMU TLB44.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 4.3.3   | Virtual Memory Architecture Processor Support    | 4-15  |

| 4.3.6       MMU TLB       4         4.3.7       MMU Operation       4         4.3.8       MMU Implementation       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | 4.3.4   | Effective Address Attribute Determination        | 4-17  |

| 4.3.7MMU Operation44.3.8MMU Implementation4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | 4.3.5   | MMU Functionality                                | 4-18  |

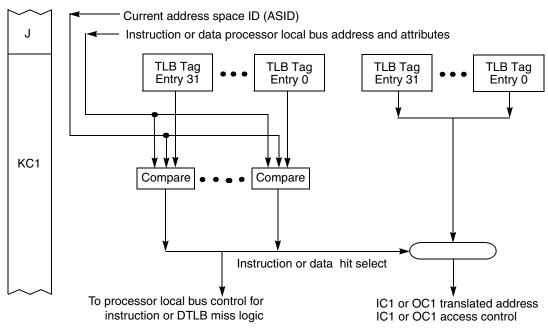

| 4.3.8 MMU Implementation 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  | 4.3.6   | MMU TLB                                          | 4-18  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 4.3.7   | MMU Operation                                    | 4-18  |

| 4.2.0 MMLLInstructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | 4.3.8   | MMU Implementation                               | 4-20  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                  | 4.3.9   | MMU Instructions                                 | 4-23  |

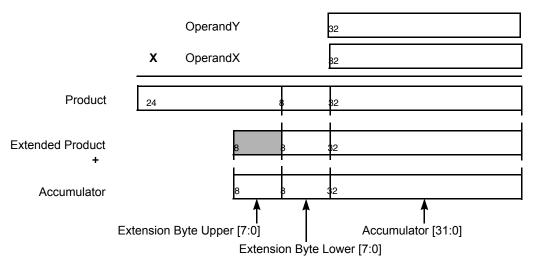

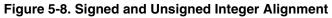

### Chapter 5 Enhanced Multiply-Accumulate Unit (EMAC)

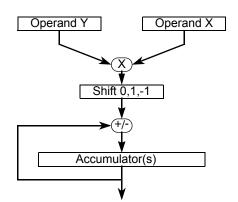

| 5.1 | Introduc | ction                                                | . 5-2 |

|-----|----------|------------------------------------------------------|-------|

|     | 5.1.1    | Overview                                             | . 5-2 |

| 5.2 | Memory   | / Map/Register Definition                            | . 5-4 |

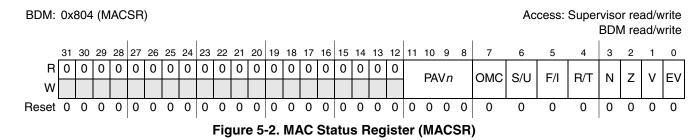

|     | 5.2.1    | MAC Status Register (MACSR)                          | . 5-4 |

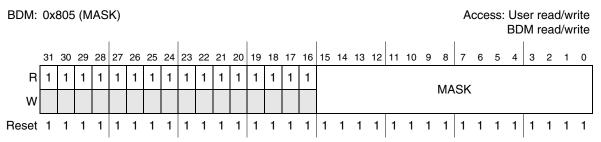

|     | 5.2.2    | Mask Register (MASK)                                 | . 5-6 |

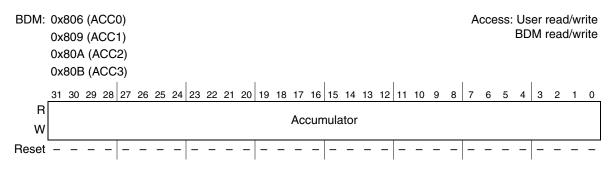

|     | 5.2.3    | Accumulator Registers (ACC0-3)                       | . 5-8 |

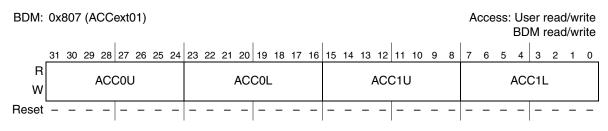

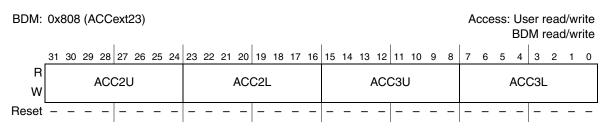

|     | 5.2.4    | Accumulator Extension Registers (ACCext01, ACCext23) | . 5-8 |

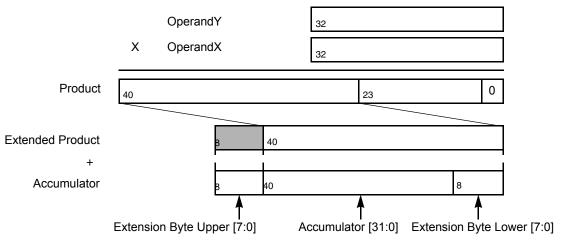

| 5.3 | Functio  | nal Description                                      | . 5-9 |

|     | 5.3.1    | Fractional Operation Mode                            | 5-11  |

|     | 5.3.2    | EMAC Instruction Set Summary                         | 5-13  |

|     | 5.3.3    | EMAC Instruction Execution Times                     | 5-14  |

|     | 5.3.4    | Data Representation                                  | 5-15  |

|     | 5.3.5    | MAC Opcodes                                          | 5-15  |

### Chapter 6

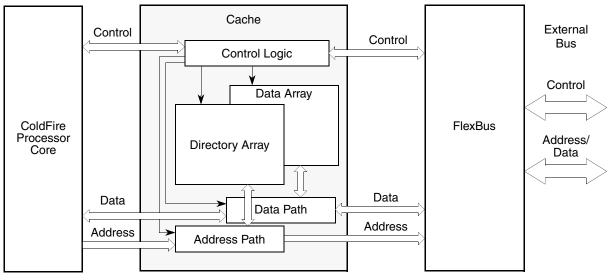

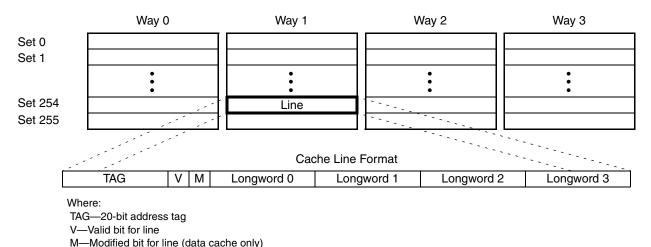

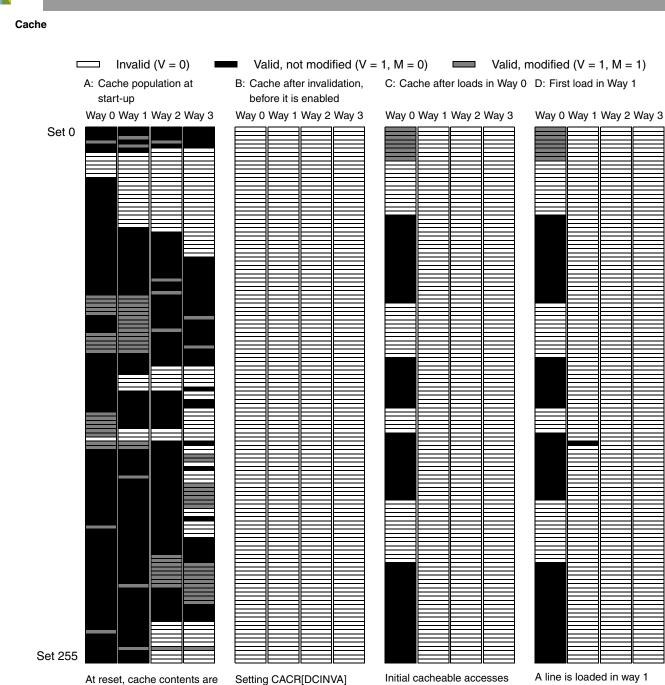

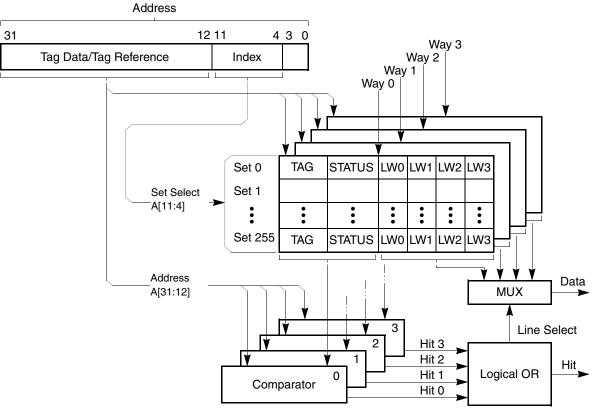

### Cache

| 6.1 Introduction |            | ction                                                            |

|------------------|------------|------------------------------------------------------------------|

|                  | 6.1.1      | Block Diagram                                                    |

|                  | 6.1.2      | Overview                                                         |

| 6.2              | Cache      | Organization                                                     |

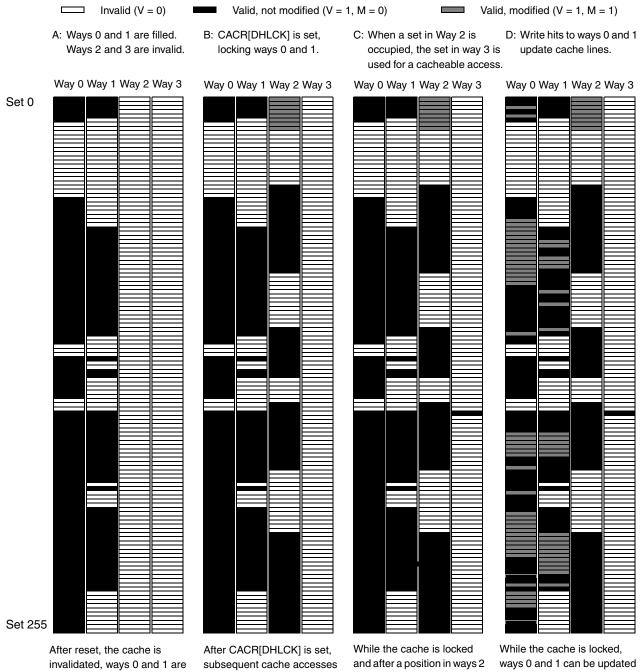

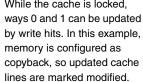

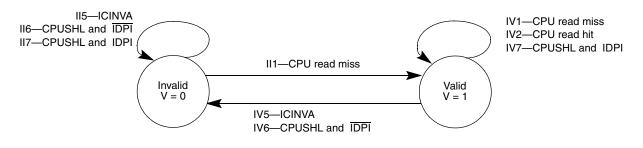

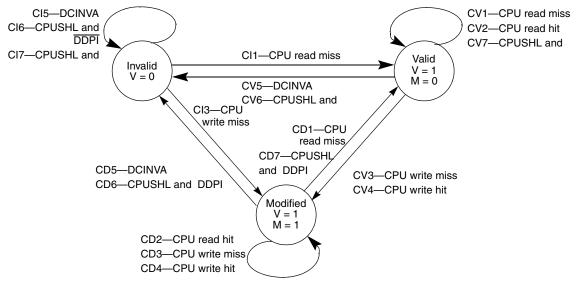

|                  | 6.2.1      | Cache Line States: Invalid, Valid-Unmodified, and Valid-Modified |

|                  | 6.2.2      | The Cache at Start-Up                                            |

| 6.3              | Memor      | y Map/Register Definition                                        |

|                  | 6.3.1      | Cache Control Register (CACR)                                    |

|                  | 6.3.2      | Access Control Registers (ACR <i>n</i> )                         |

| 6.4              | Functio    | nal Description                                                  |

|                  | 6.4.1      | Caching Modes                                                    |

|                  | 6.4.2      | Cache Protocol                                                   |

|                  | 6.4.3      | Cache Coherency (Data Cache Only)6-16                            |

|                  | 6.4.4      | Memory Accesses for Cache Maintenance                            |

|                  | 6.4.5      | Cache Locking                                                    |

|                  | 6.4.6      | Cache Management                                                 |

|                  | 6.4.7      | Cache Operation Summary                                          |

|                  | 6.4.8      | CPUSHL Enhancements                                              |

| 6.5              | Initializa | ation/Application Information6-28                                |

### Chapter 7 Static RAM (SRAM)

| 7.1 Introduction | 7-1 |

|------------------|-----|

|------------------|-----|

|     | 7.1.1      | Overview                            | 7-1 |

|-----|------------|-------------------------------------|-----|

|     | 7.1.2      | Features                            | 7-1 |

| 7.2 | Memor      | y Map/Register Description          | 7-2 |

|     | 7.2.1      | SRAM Base Address Register (RAMBAR) | 7-2 |

| 7.3 | Initializa | ation/Application Information       | 7-4 |

|     | 7.3.1      | SRAM Initialization Code            | 7-4 |

|     | 7.3.2      | Power Management                    | 7-5 |

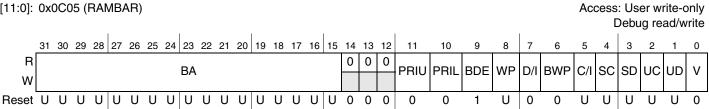

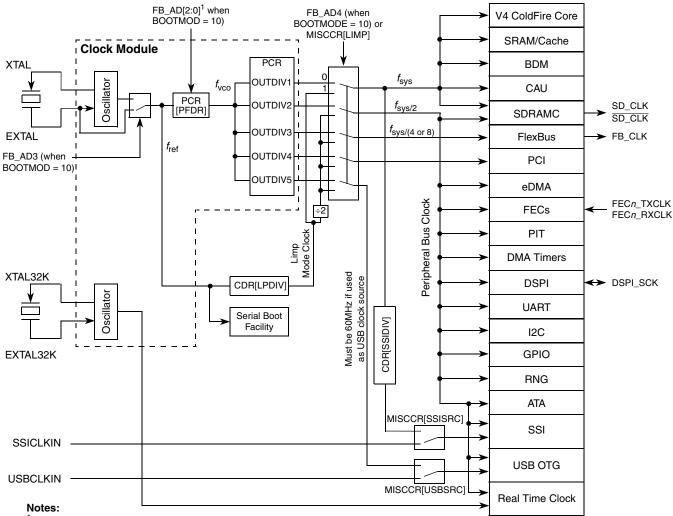

### Chapter 8 Clock Module

| 8.1 | 3.1 Introduction |                                            |  |

|-----|------------------|--------------------------------------------|--|

|     | 8.1.1            | Block Diagram                              |  |

|     | 8.1.2            | Features                                   |  |

|     | 8.1.3            | Modes of Operation                         |  |

| 8.2 | Memory           | / Map/Register Definition                  |  |

|     | 8.2.1            | PLL Control Register (PCR)                 |  |

|     | 8.2.2            | PLL Status Register (PSR)                  |  |

| 8.3 | Functio          | nal Description                            |  |

|     | 8.3.1            | PLL Frequency Multiplication Factor Select |  |

|     | 8.3.2            | Lock Conditions                            |  |

|     | 8.3.3            | Loss-of-Lock                               |  |

|     | 8.3.4            | System Clock Modes                         |  |

|     | 8.3.5            | Clock Operation During Reset               |  |

### Chapter 9 Power Management

| Introdu | ction                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------|

| 9.1.1   | Features                                                                                                     |

| Memor   | y Map/Register Definition                                                                                    |

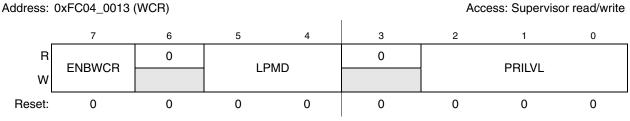

| 9.2.1   | Wake-up Control Register (WCR)                                                                               |

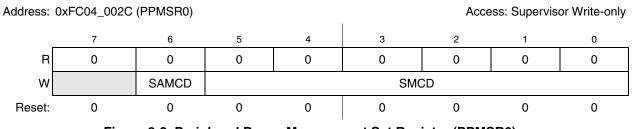

| 9.2.2   | Peripheral Power Management Set Register (PPMSR0)9-3                                                         |

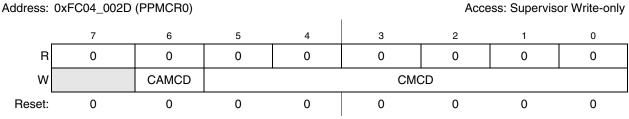

| 9.2.3   | Peripheral Power Management Clear Register (PPMCR0)9-4                                                       |

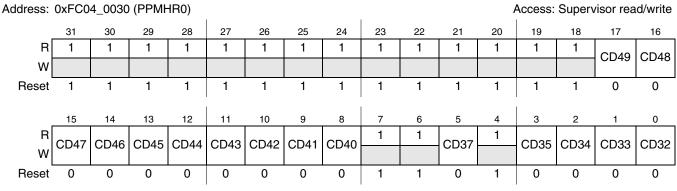

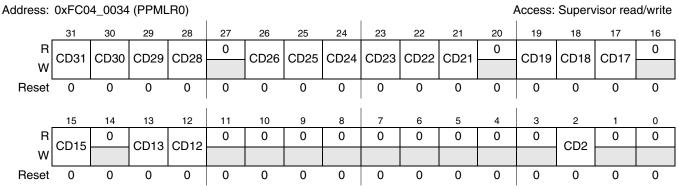

| 9.2.4   | Peripheral Power Management Registers (PPMHR0 and PPMLR0)9-4                                                 |

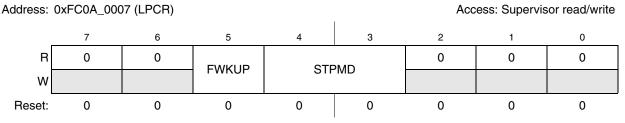

| 9.2.5   | Low-Power Control Register (LPCR)                                                                            |

| Functio | nal Description                                                                                              |

| 9.3.1   | Peripheral Shut Down                                                                                         |

| 9.3.2   | Limp mode                                                                                                    |

| 9.3.3   | Low-Power Modes                                                                                              |

| 9.3.4   | Peripheral Behavior in Low-Power Modes                                                                       |

| 9.3.5   | Summary of Peripheral State During Low-power Modes                                                           |

|         | 9.1.1<br>Memory<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.2.5<br>Function<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4 |

|      |           | Universal Serial Bus Interface – On-The-Go Module |

|------|-----------|---------------------------------------------------|

| 10.1 | Introdu   | ction                                             |

|      | 10.1.1    | Overview                                          |

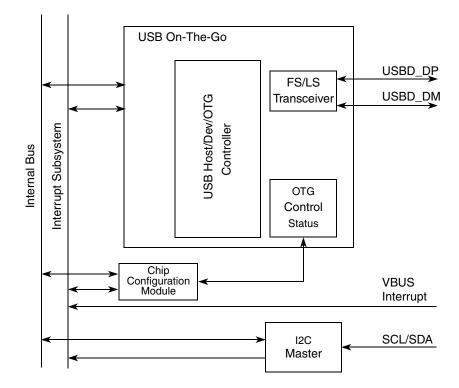

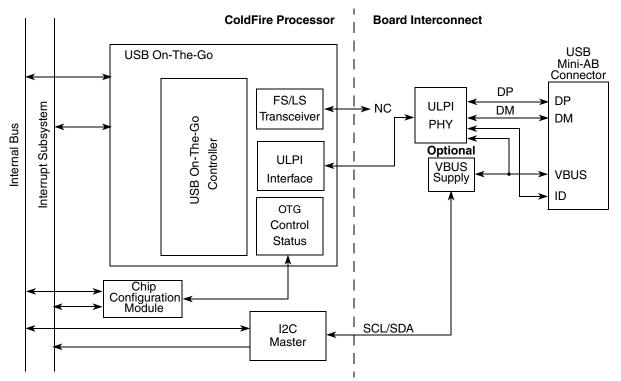

|      | 10.1.2    | Block Diagram                                     |

|      | 10.1.3    | Features                                          |

|      | 10.1.4    | Modes of Operation                                |

| 10.2 | Externa   | al Signal Description                             |

|      |           | USB OTG Control and Status Signals 10-6           |

| 10.3 | Memor     | y Map/Register Definition                         |

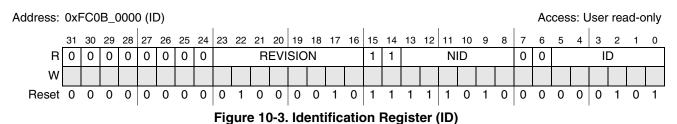

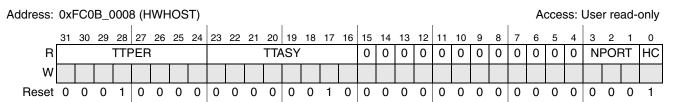

|      | 10.3.1    | Module Identification Registers 10-9              |

|      | 10.3.2    | Device/Host Timer Registers 10-13                 |

|      | 10.3.3    | Capability Registers                              |

|      | 10.3.4    | Operational Registers 10-18                       |

| 10.4 | Functio   | nal Description                                   |

|      | 10.4.1    | System Interface                                  |

|      | 10.4.2    | DMA Engine                                        |

|      | 10.4.3    | FIFO RAM Controller 10-47                         |

|      | 10.4.4    | Physical Layer (PHY) Interface 10-47              |

| 10.5 | Initializ | ation/Application Information                     |

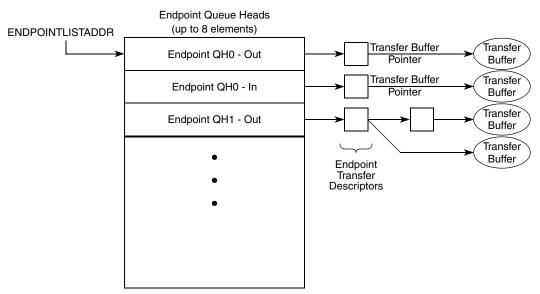

|      | 10.5.1    | Host Operation                                    |

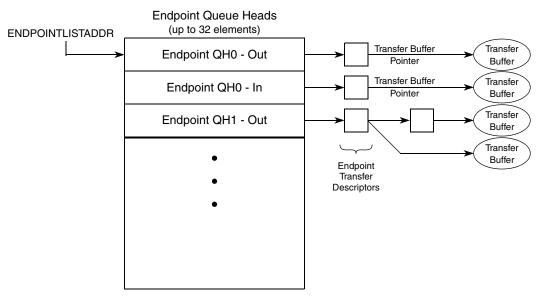

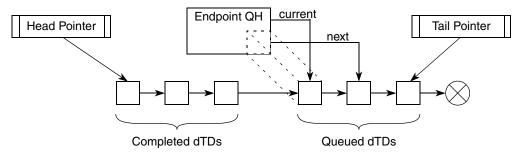

|      | 10.5.2    | Device Data Structures                            |

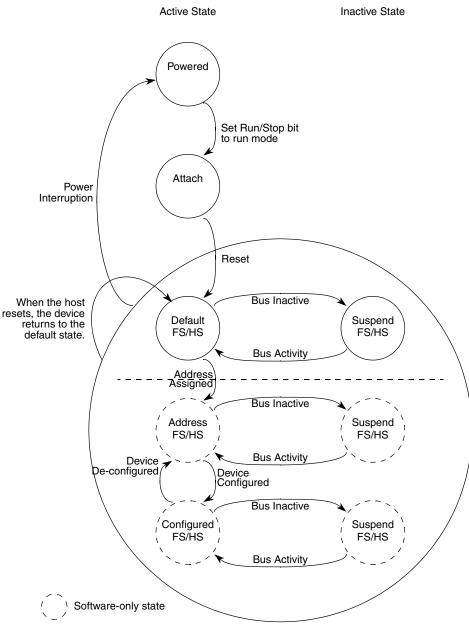

|      | 10.5.3    | Device Operation                                  |

|      | 10.5.4    | Servicing Interrupts 10-74                        |

|      | 10.5.5    | Deviations from the EHCI Specifications           |

### Chapter 10 Universal Serial Bus Interface – On-The-Go Modul

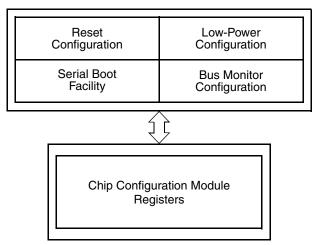

### Chapter 11 Chip Configuration Module (CCM)

| 11.1 | Introduc | ction                                                  |

|------|----------|--------------------------------------------------------|

|      | 11.1.1   | Block Diagram                                          |

|      | 11.1.2   | Features                                               |

|      | 11.1.3   | Modes of Operation                                     |

| 11.2 | Externa  | Il Signal Descriptions                                 |

|      | 11.2.1   | BOOTMOD[1:0] 11-2                                      |

|      | 11.2.2   | FB_AD[7:0] (Reset Configuration Override) 11-2         |

| 11.3 | Memory   | y Map/Register Definition 11-2                         |

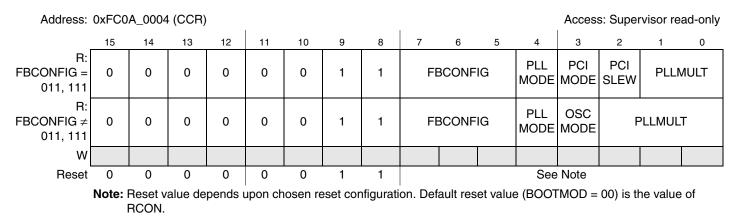

|      | 11.3.1   | Chip Configuration Register (CCR) 11-3                 |

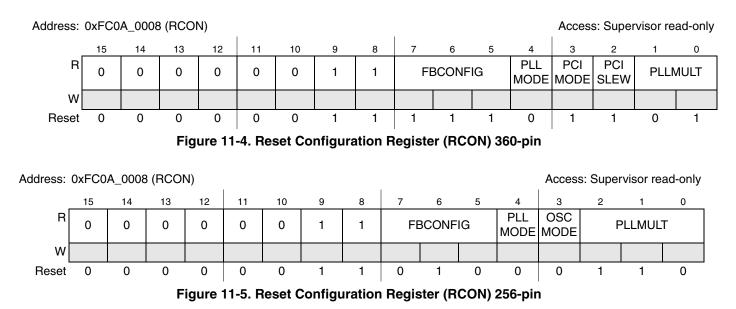

|      | 11.3.2   | Reset Configuration Register (RCON) 11-7               |

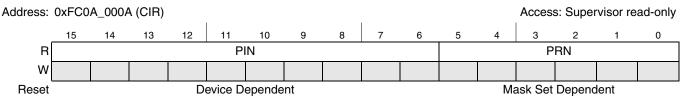

|      | 11.3.3   | Chip Identification Register (CIR) 11-8                |

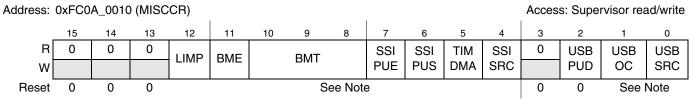

|      | 11.3.4   | Miscellaneous Control Register (MISCCR) 11-8           |

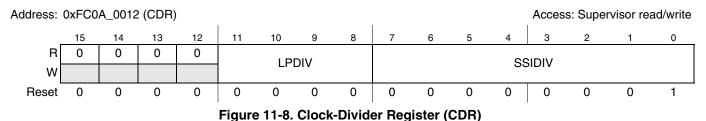

|      | 11.3.5   | Clock-Divider Register (CDR) 11-11                     |

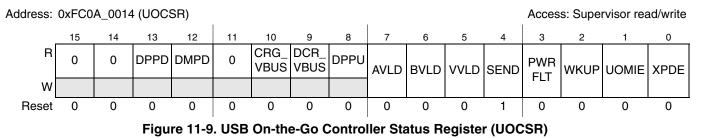

|      | 11.3.6   | USB On-the-Go Controller Status Register (UOCSR) 11-11 |

|      |          |                                                        |

| 11.4 Functional Description |      |                         |       |

|-----------------------------|------|-------------------------|-------|

| 11.                         | .4.1 | Reset Configuration     | 11-13 |

| 11.                         | .4.2 | Boot Configuration      | 11-19 |

| 11.                         | .4.3 | Low Power Configuration | 11-20 |

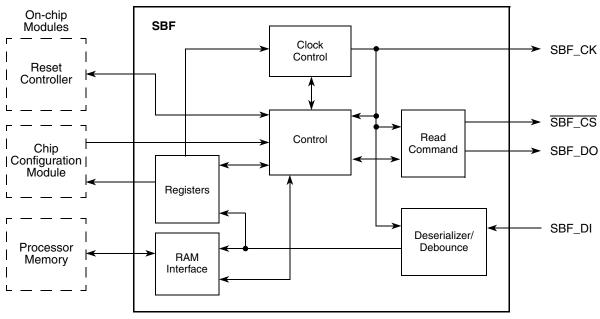

### Chapter 12 Serial Boot Facility (SBF)

| 12.1 | Introduc   | ction                                                           |

|------|------------|-----------------------------------------------------------------|

|      | 12.1.1     | Overview                                                        |

|      | 12.1.2     | Features                                                        |

| 12.2 | Externa    | I Signal Description                                            |

| 12.3 | Memory     | / Map/Register Definition                                       |

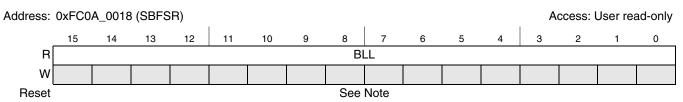

|      | 12.3.1     | Serial Boot Facility Status Register (SBFSR) 12-3               |

|      | 12.3.2     | Serial Boot Facility Control Register (SBFCR) 12-3              |

| 12.4 | Functio    | nal Description                                                 |

|      | 12.4.1     | Serial Initialization and Shift Clock Frequency Adjustment 12-4 |

|      | 12.4.2     | Reset Configuration and Optional Boot Load 12-5                 |

|      | 12.4.3     | Execution Transfer                                              |

| 12.5 | Initializa | ation Information                                               |

|      | 12.5.1     | SPI Memory Initialization                                       |

|      | 12.5.2     | FAST_READ Feature Initialization 12-7                           |

### Chapter 13

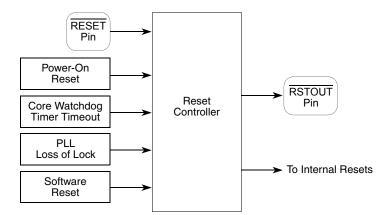

### **Reset Controller Module**

| 13.1 | Introdu | ction                             |

|------|---------|-----------------------------------|

|      | 13.1.1  | Block Diagram                     |

|      | 13.1.2  | Features                          |

| 13.2 | Externa | Il Signal Description             |

|      | 13.2.1  | RESET                             |

|      | 13.2.2  | RSTOUT                            |

| 13.3 | Memor   | y Map/Register Definition         |

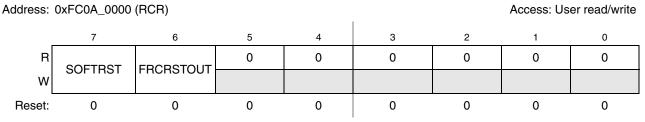

|      | 13.3.1  | Reset Control Register (RCR) 13-2 |

|      | 13.3.2  | Reset Status Register (RSR) 13-3  |

| 13.4 |         | nal Description                   |

|      | 13.4.1  | Reset Sources                     |

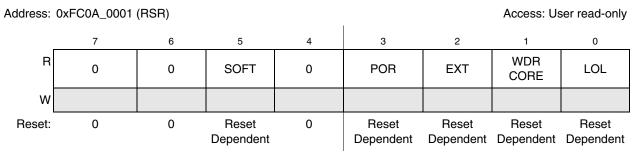

|      | 13.4.2  | Reset Control Flow                |

|      | 13.4.3  | Concurrent Resets                 |

### Chapter 14 System Control Module (SCM)

|      |              | - | • •  |          |

|------|--------------|---|------|----------|

| 14.1 | Introduction |   | <br> | <br>14-1 |

|      | 14.1.1  | Overview                                             |       |

|------|---------|------------------------------------------------------|-------|

|      | 14.1.2  | Features                                             |       |

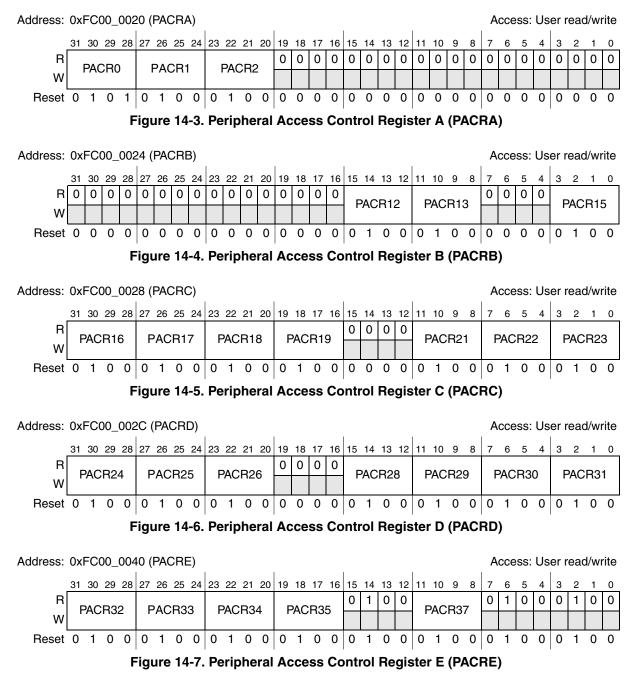

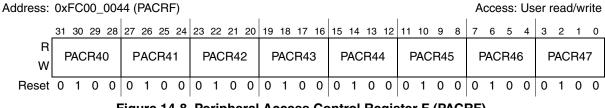

| 14.2 | Memor   | y Map/Register Definition                            |       |

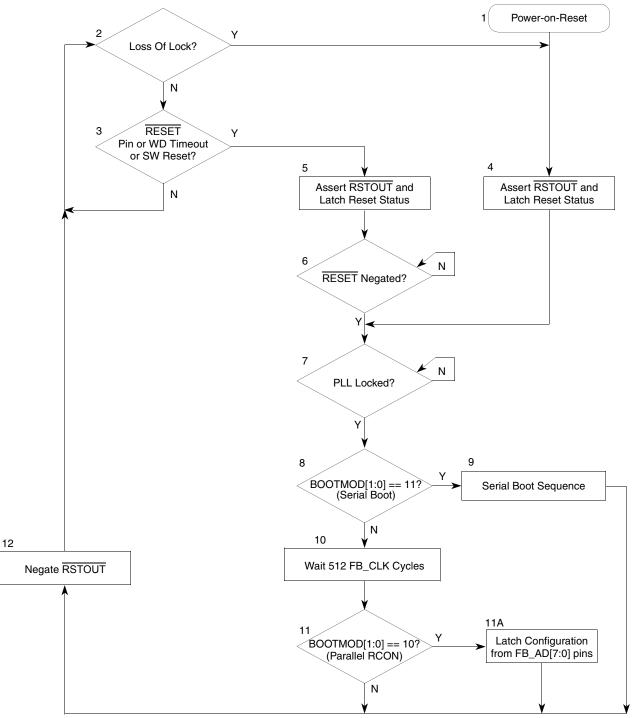

|      | 14.2.1  | Master Privilege Register (MPR)                      |       |

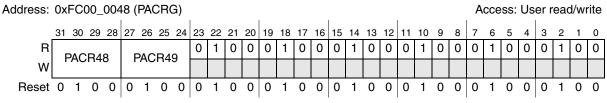

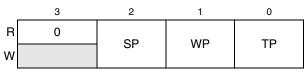

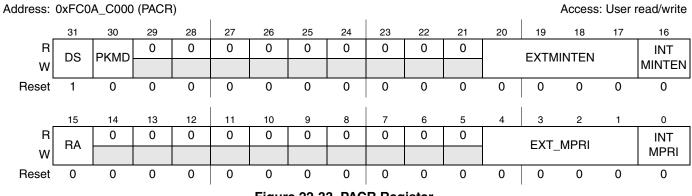

|      | 14.2.2  | Peripheral Access Control Registers (PACR <i>x</i> ) |       |

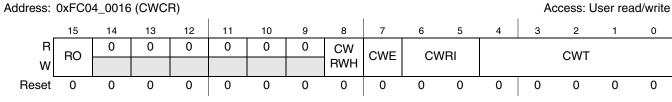

|      | 14.2.3  | Core Watchdog Control Register (CWCR)                |       |

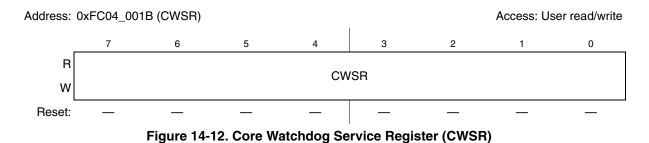

|      | 14.2.4  | Core Watchdog Service Register (CWSR)                |       |

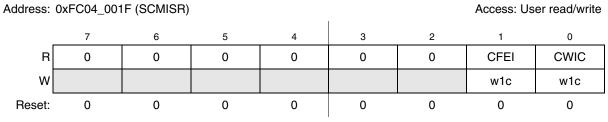

|      | 14.2.5  | SCM Interrupt Status Register (SCMISR)               |       |

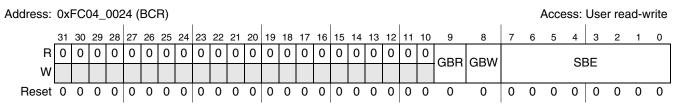

|      | 14.2.6  | Burst Configuration Register (BCR)                   | 14-10 |

|      | 14.2.7  | Core Fault Address Register (CFADR)                  | 14-10 |

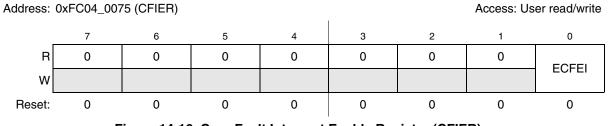

|      | 14.2.8  | Core Fault Interrupt Enable Register (CFIER)         | 14-11 |

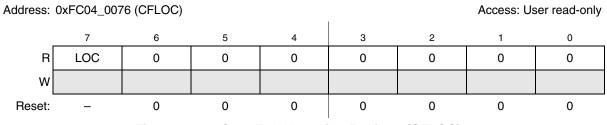

|      | 14.2.9  | Core Fault Location Register (CFLOC)                 | 14-11 |

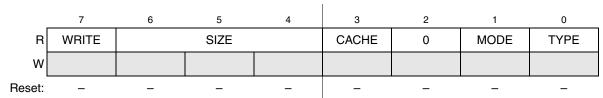

|      | 14.2.10 | Ore Fault Attributes Register (CFATR)                | 14-12 |

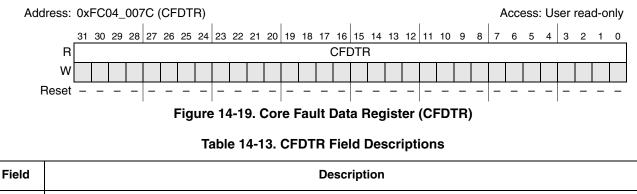

|      | 14.2.11 | Core Fault Data Register (CFDTR)                     | 14-13 |

| 14.3 | Functio | nal Description                                      | 14-13 |

|      | 14.3.1  | Access Control                                       | 14-13 |

|      | 14.3.2  | Core Watchdog Timer                                  | 14-13 |

|      | 14.3.3  | Core Data Fault Recovery Registers                   | 14-14 |

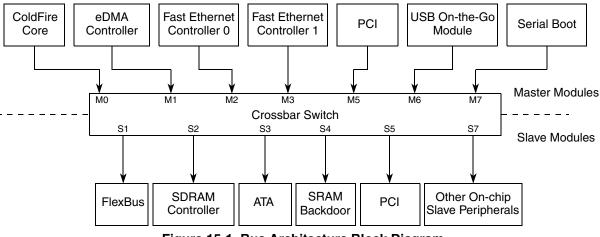

# Chapter 15 Crossbar Switch (XBS)

| 15.1 | Overvie    | w 1                                          | 15-1 |

|------|------------|----------------------------------------------|------|

| 15.2 | Feature    | s1                                           | 15-3 |

| 15.3 | Modes      | of Operation                                 | 15-3 |

| 15.4 | Memory     | / Map / Register Definition 1                | 15-3 |

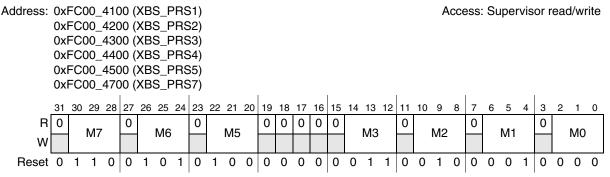

|      | 15.4.1     | XBS Priority Registers (XBS_PRS <i>n</i> ) 1 | 15-4 |

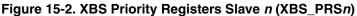

|      | 15.4.2     | XBS Control Registers (XBS_CRS <i>n</i> ) 1  | 15-5 |

| 15.5 | Functio    | nal Description                              | 15-7 |

|      | 15.5.1     | Arbitration 1                                | 15-7 |

| 15.6 | Initializa | ation/Application Information1               | 15-8 |

# Chapter 16 Pin Multiplexing and Control

| 16.1 | Introduction |                                                   |   |

|------|--------------|---------------------------------------------------|---|

|      | 16.1.1       | Overview                                          | 3 |

|      | 16.1.2       | Features                                          | 3 |

| 16.2 | Externa      | I Signal Description                              | 3 |

| 16.3 | Memory       | / Map/Register Definition                         | 2 |

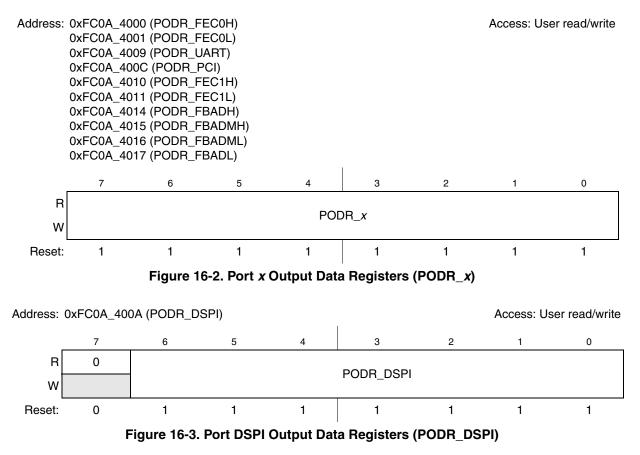

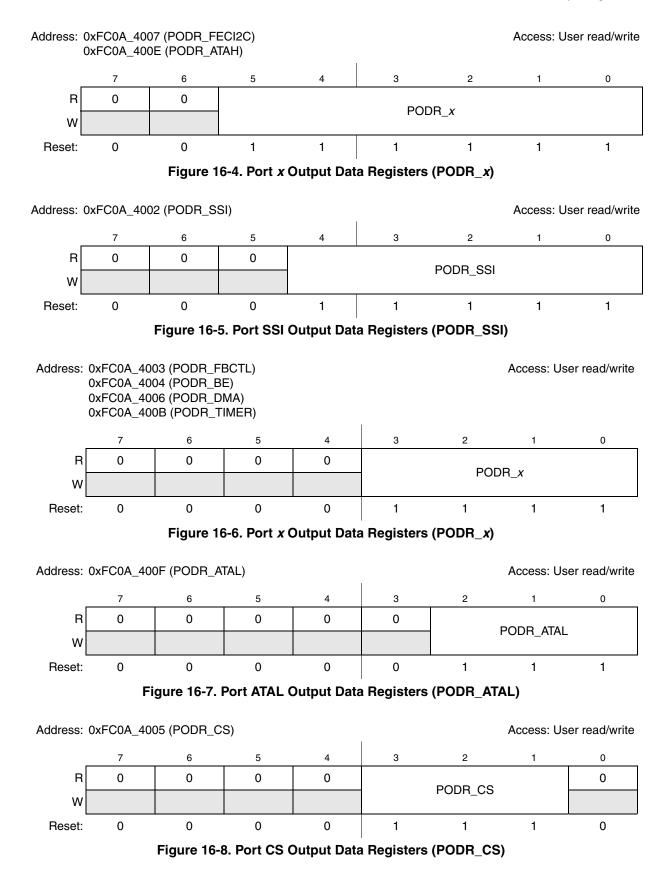

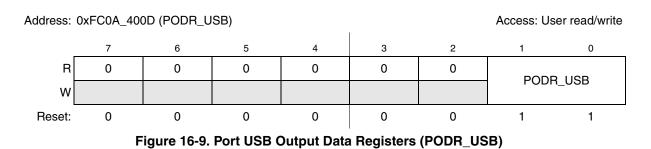

|      | 16.3.1       | Port Output Data Registers (PODR_x) 16-16         | 3 |

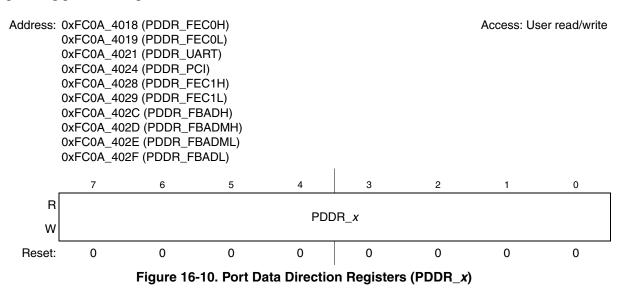

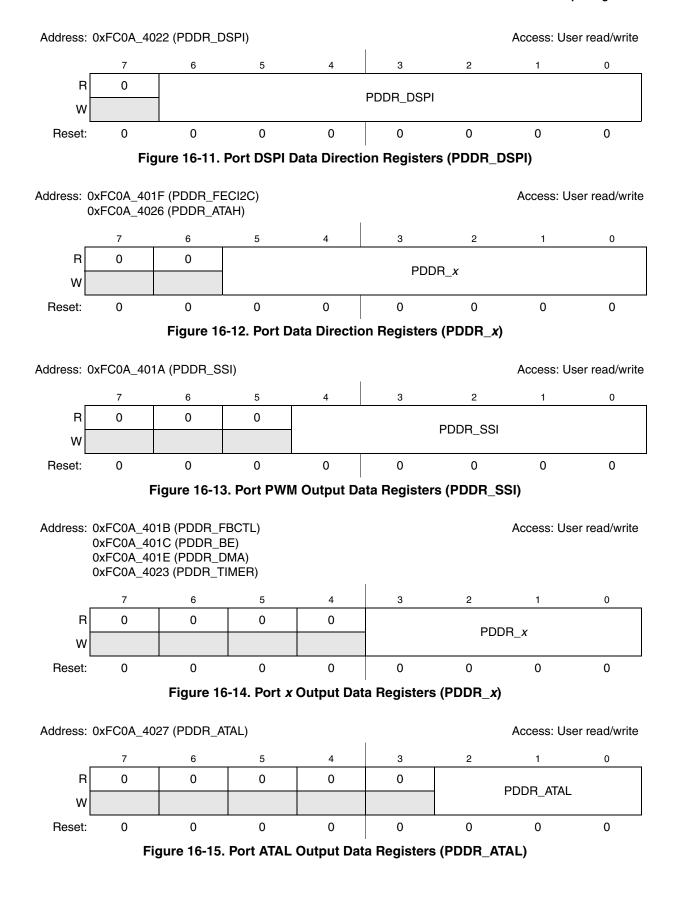

|      | 16.3.2       | Port Data Direction Registers (PDDR_x) 16-18      | 3 |

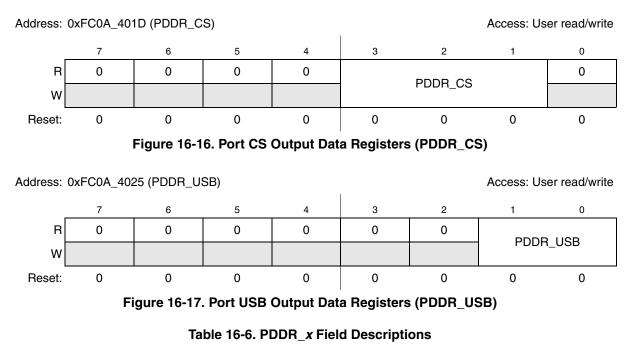

|      | 16.3.3       | Port Pin Data/Set Data Registers (PPDSDR_x) 16-20 | ) |

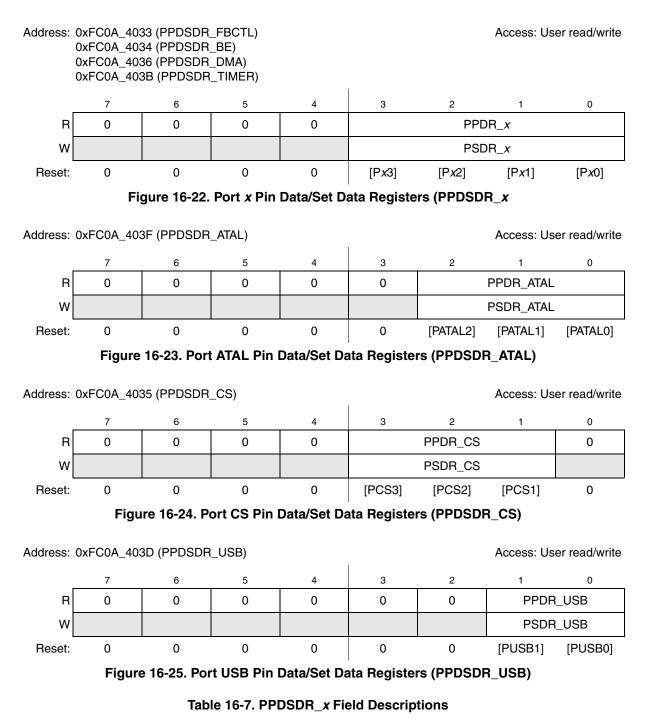

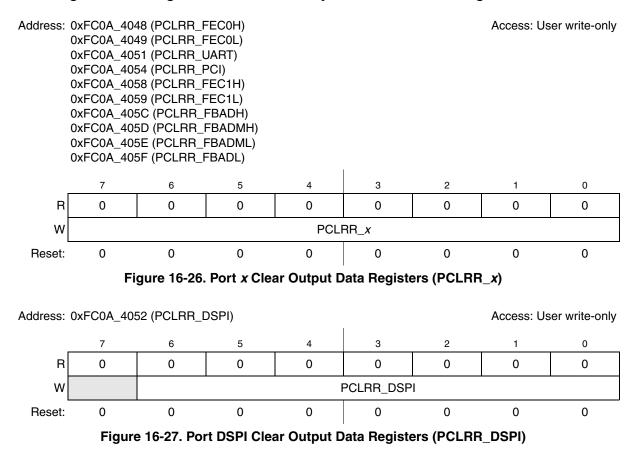

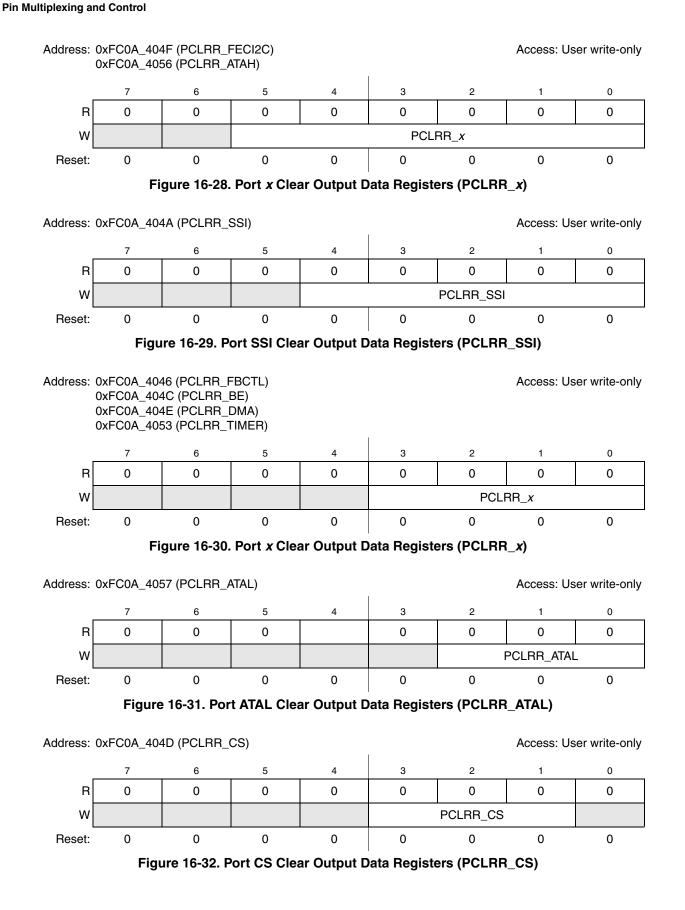

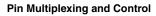

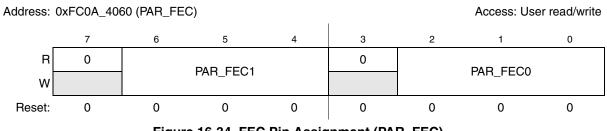

|      | 16.3.4       | Port Clear Output Data Registers (PCLRR_x) 16-23  | 3 |

|      |              |                                                   |   |

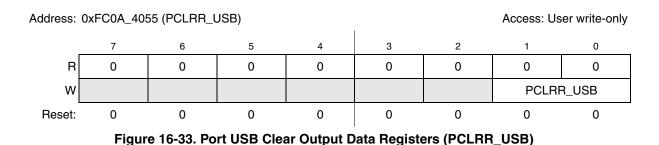

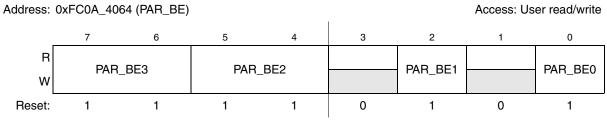

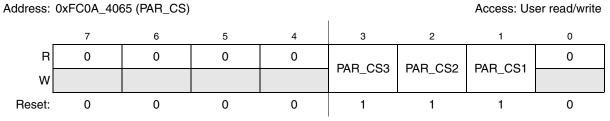

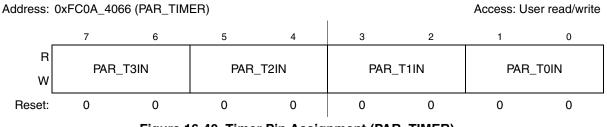

|      | 16.3.5     | Pin Assignment Registers (PAR_x)                | 16-25 |

|------|------------|-------------------------------------------------|-------|

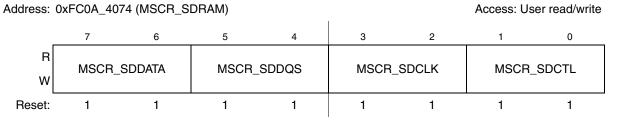

|      | 16.3.6     | SDRAM Mode Select Control Register (MSCR_SDRAM) | 16-38 |

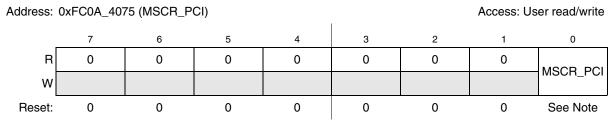

|      | 16.3.7     | PCI Mode Select Control Register (MSCR_PCI)     | 16-39 |

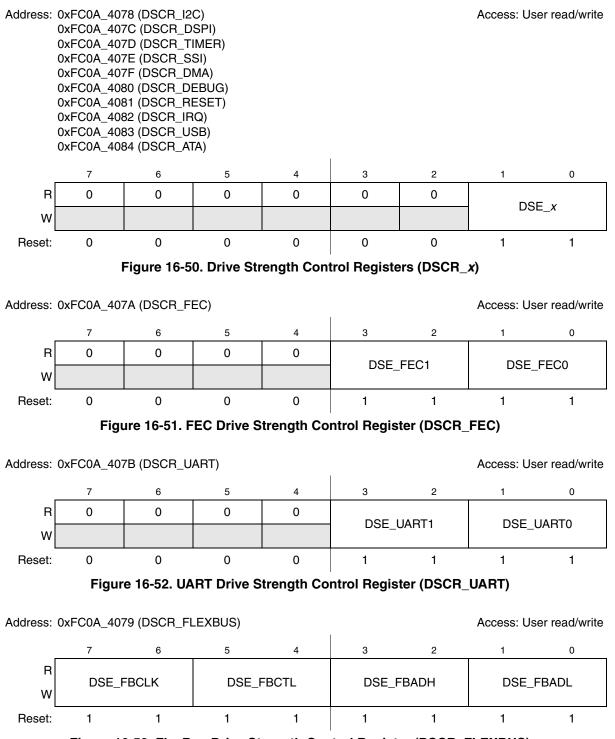

|      | 16.3.8     | Drive Strength Control Registers (DSCR_x)       | 16-39 |

| 16.4 | Functio    | nal Description                                 | 16-42 |

|      | 16.4.1     | Overview                                        | 16-42 |

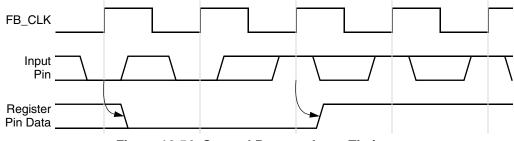

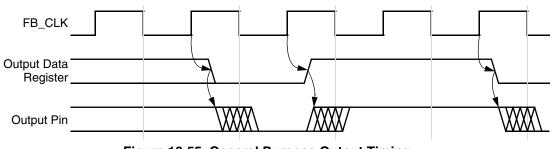

|      | 16.4.2     | Port Digital I/O Timing                         | 16-42 |

| 16.5 | Initializa | ation/Application Information                   | 16-43 |

### Chapter 17 Interrupt Controller Modules

| 17.1 | Introduc   | tion                                                                                             |

|------|------------|--------------------------------------------------------------------------------------------------|

|      | 17.1.1     | 68 K/ColdFire Interrupt Architecture Overview                                                    |

| 17.2 | Memory     | / Map/Register Definition 17-2                                                                   |

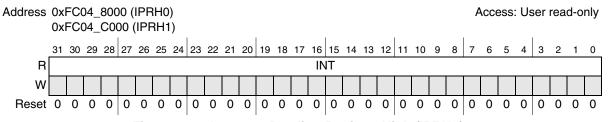

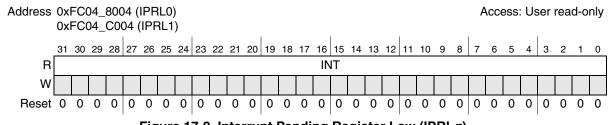

|      | 17.2.1     | Interrupt Pending Registers (IPRHn, IPRLn) 17-4                                                  |

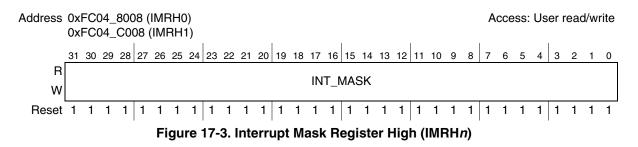

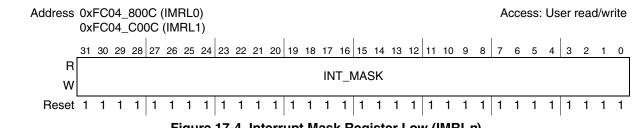

|      | 17.2.2     | Interrupt Mask Register (IMRHn, IMRLn) 17-5                                                      |

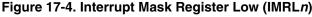

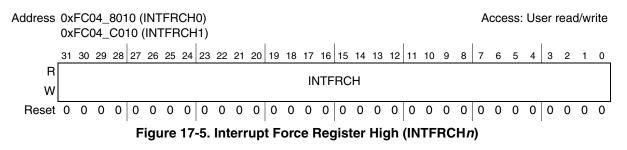

|      | 17.2.3     | Interrupt Force Registers (INTFRCHn, INTFRCLn)                                                   |

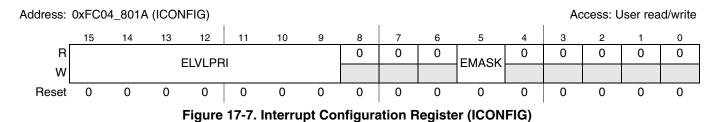

|      | 17.2.4     | Interrupt Configuration Register (ICONFIG) 17-7                                                  |

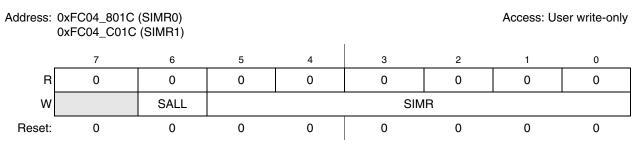

|      | 17.2.5     | Set Interrupt Mask Register (SIMR <i>n</i> ) 17-8                                                |

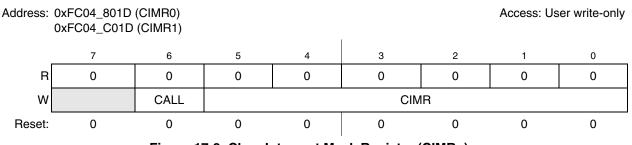

|      | 17.2.6     | Clear Interrupt Mask Register (CIMRn) 17-9                                                       |

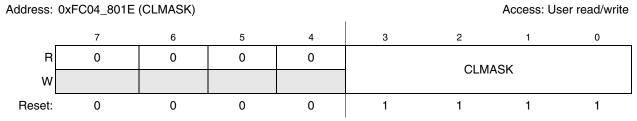

|      | 17.2.7     | Current Level Mask Register (CLMASK) 17-9                                                        |

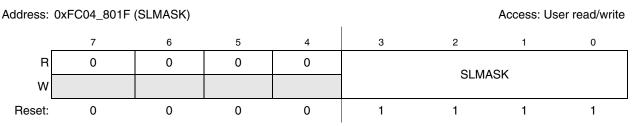

|      | 17.2.8     | Saved Level Mask Register (SLMASK) 17-10                                                         |

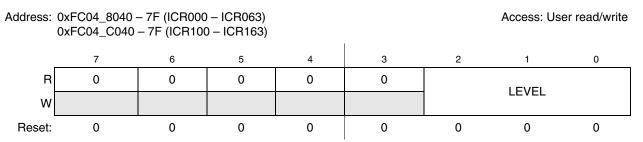

|      | 17.2.9     | Interrupt Control Register (ICR0 <i>n</i> , ICR1 <i>n</i> , ( <i>n</i> = 00, 01, 02,, 63)) 17-11 |

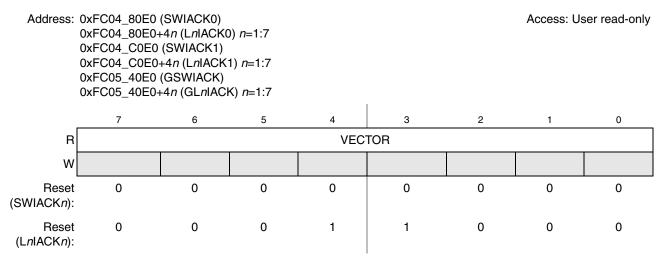

|      | 17.2.10    | Software and Level 1–7 IACK Registers (SWIACKn, L1IACKn–L7IACKn) . 17-15                         |

| 17.3 | Functio    | nal Description                                                                                  |

|      | 17.3.1     | Interrupt Controller Theory of Operation                                                         |

|      | 17.3.2     | Prioritization Between Interrupt Controllers                                                     |

|      | 17.3.3     | Low-Power Wake-up Operation                                                                      |

| 17.4 | Initializa | ation/Application Information                                                                    |

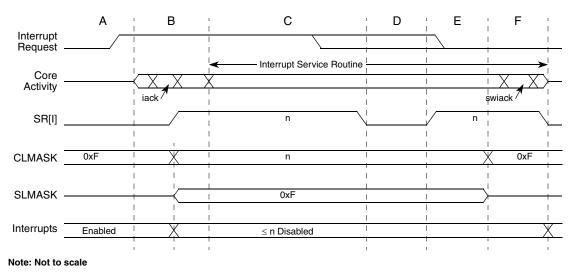

|      | 17.4.1     | Interrupt Service Routines                                                                       |

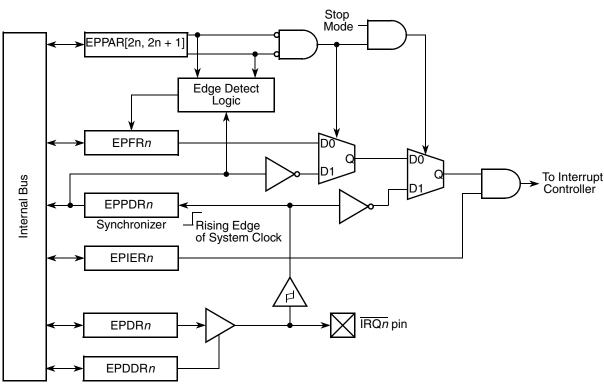

### Chapter 18 Edge Port Module (EPORT)

| 18.1 | Introduo | ction                                         | 18-1 |

|------|----------|-----------------------------------------------|------|

| 18.2 | Low-Po   | wer Mode Operation                            | 18-2 |

| 18.3 | Signal I | Descriptions                                  | 18-2 |

| 18.4 | Memory   | y Map/Register Definition 1                   | 18-2 |

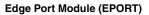

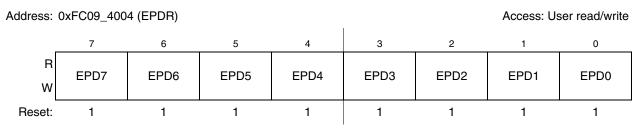

|      | 18.4.1   | EPORT Pin Assignment Register (EPPAR) 1       | 18-3 |

|      | 18.4.2   | EPORT Data Direction Register (EPDDR) 1       | 18-4 |

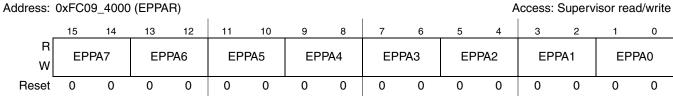

|      | 18.4.3   | Edge Port Interrupt Enable Register (EPIER) 1 | 18-5 |

|      | 18.4.4   | Edge Port Data Register (EPDR) 1              | 18-5 |

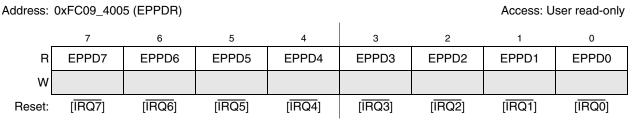

|      | 18.4.5   | Edge Port Pin Data Register (EPPDR) 1         | 18-5 |

|      |          |                                               |      |

| 18.4.6 | Edge Port Flag Register (EPFR) | ••••••••••••••••••••••••••••••••••••••• | 18-6 |

|--------|--------------------------------|-----------------------------------------|------|

|--------|--------------------------------|-----------------------------------------|------|

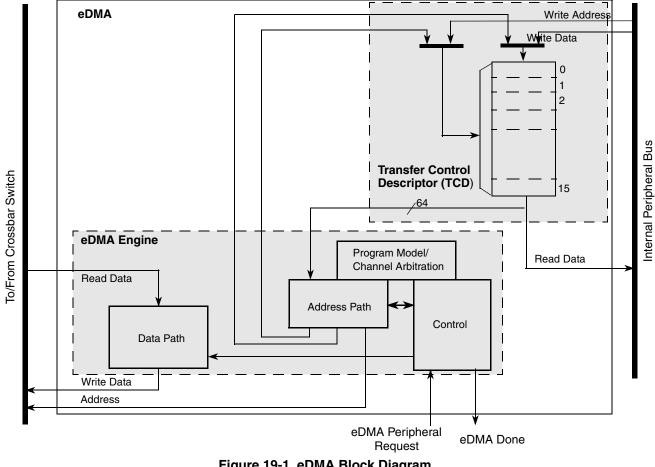

## Chapter 19 Enhanced Direct Memory Access (eDMA)

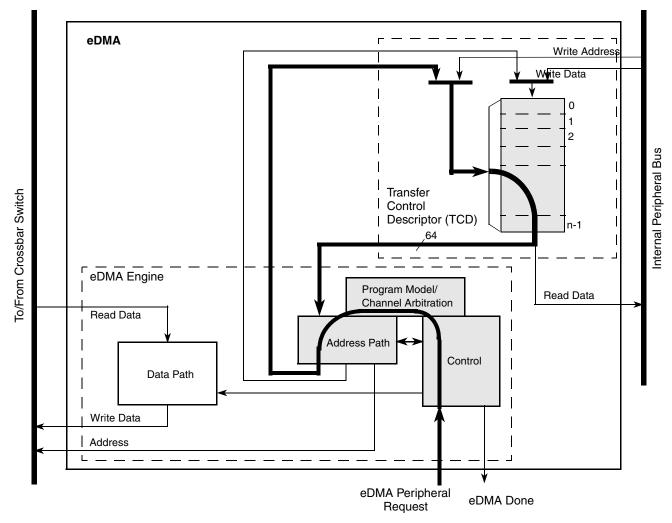

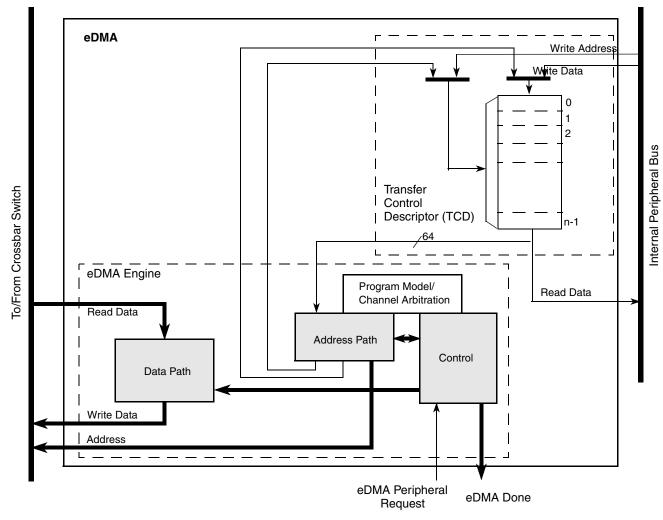

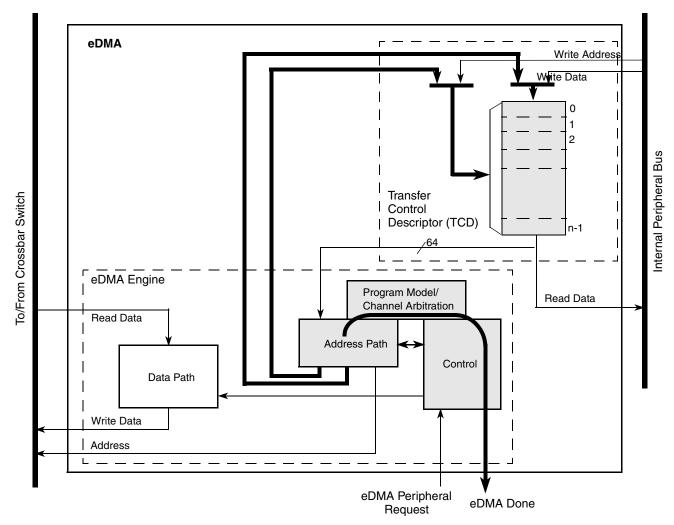

| 19.1 |         | ew                                                     |        |

|------|---------|--------------------------------------------------------|--------|

|      |         | Block Diagram                                          |        |

|      | 19.1.2  | Features                                               | . 19-2 |

| 19.2 |         | of Operation                                           |        |

|      | 19.2.1  | Normal Mode                                            | . 19-2 |

|      |         | Debug Mode                                             |        |

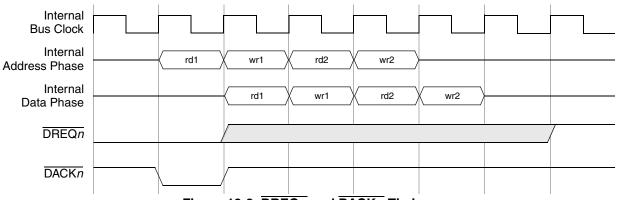

| 19.3 | Externa | al Signal Description                                  | . 19-3 |

|      |         | External Signal Timing                                 |        |

| 19.4 | Memory  | y Map/Register Definition                              |        |

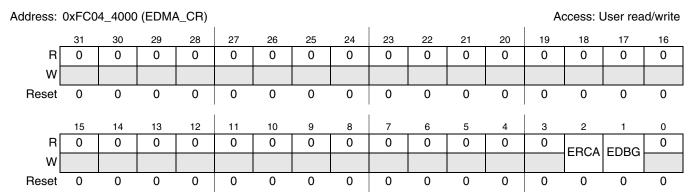

|      | 19.4.1  | eDMA Control Register (EDMA_CR)                        |        |

|      | 19.4.2  | eDMA Error Status Register (EDMA_ES)                   |        |

|      | 19.4.3  |                                                        |        |

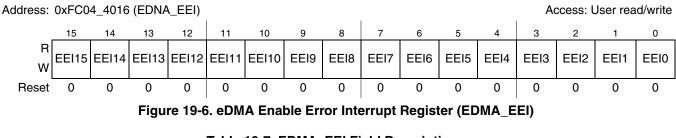

|      |         | eDMA Enable Error Interrupt Registers (EDMA_EEI)       |        |

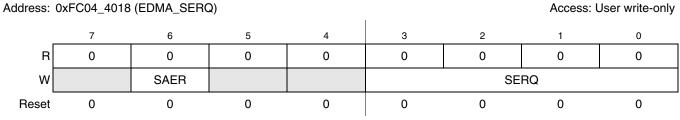

|      | 19.4.5  | eDMA Set Enable Request Register (EDMA_SERQ)           |        |

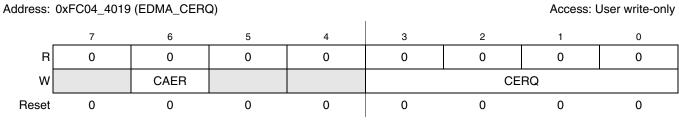

|      | 19.4.6  | eDMA Clear Enable Request Register (EDMA_CERQ)         |        |

|      | 19.4.7  | eDMA Set Enable Error Interrupt Register (EDMA_SEEI)   |        |

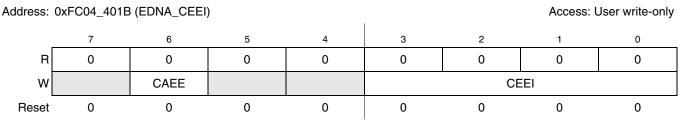

|      | 19.4.8  | eDMA Clear Enable Error Interrupt Register (EDMA_CEEI) |        |

|      | 19.4.9  |                                                        |        |

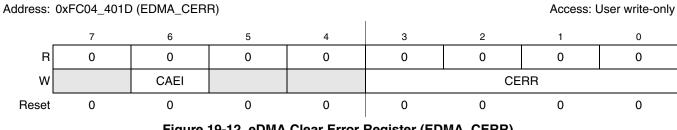

|      |         | eDMA Clear Error Register (EDMA_CERR)                  |        |

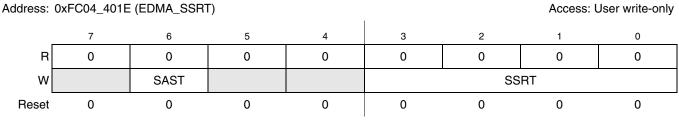

|      |         | eDMA Set START Bit Register (EDMA_SSRT)                |        |

|      |         | eDMA Clear DONE Status Bit Register (EDMA_CDNE)        |        |

|      |         | BeDMA Interrupt Request Register (EDMA_INT)            |        |

|      |         | eDMA Error Register (EDMA_ERR)                         |        |

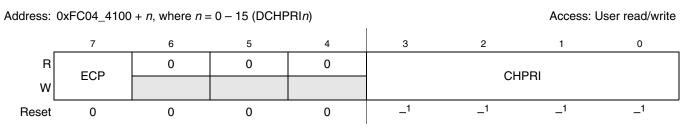

|      |         | eDMA Channel n Priority Registers (DCHPRIn)            |        |

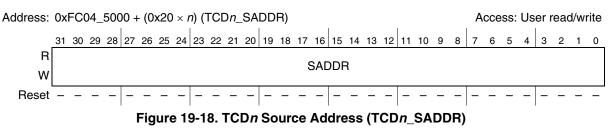

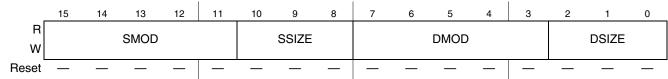

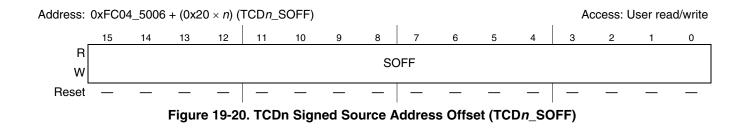

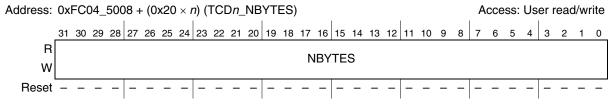

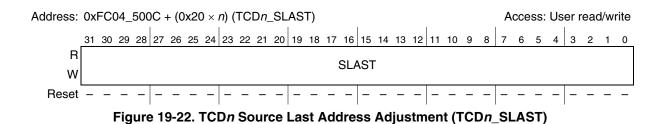

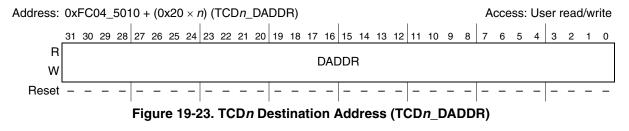

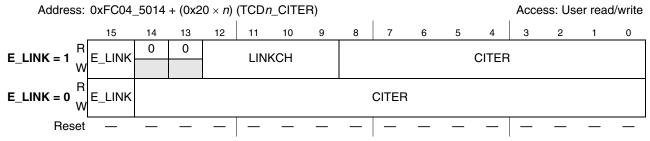

|      |         | Transfer Control Descriptors (TCDn)                    |        |

| 19.5 |         | nal Description                                        |        |

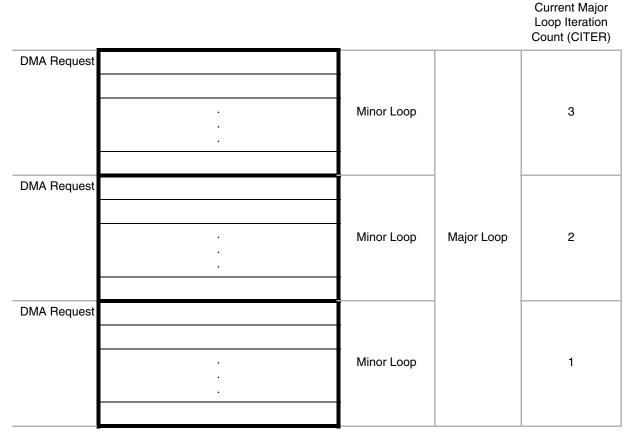

|      | 19.5.1  | eDMA Microarchitecture                                 | 19-24  |

|      |         | eDMA Basic Data Flow                                   |        |

| 19.6 |         | ation/Application Information                          |        |

|      | 19.6.1  | eDMA Initialization                                    |        |

|      | 19.6.2  | DMA Programming Errors                                 |        |

|      | 19.6.3  | DMA Arbitration Mode Considerations                    | 19-31  |

|      | 19.6.4  | DMA Transfer                                           |        |

|      | 19.6.5  | eDMA TCD <i>n</i> Status Monitoring                    | 19-35  |

|      | 19.6.6  | Channel Linking                                        | 19-36  |

|      | 19.6.7  | Dynamic Programming                                    | 19-37  |

### Chapter 20

### FlexBus

| 20.1 | Introdu | ction                                                 |

|------|---------|-------------------------------------------------------|

|      | 20.1.1  | Overview                                              |

|      | 20.1.2  | Features                                              |

|      | 20.1.3  | Modes of Operation                                    |

| 20.2 | Externa | al Signals                                            |

|      | 20.2.1  | Address and Data Buses (FB_An, FB_Dn, FB_ADn) 20-3    |

|      | 20.2.2  | Chip Selects (FB_CS[5:0])                             |

|      |         | Byte Enables/Byte Write Enables (FB_BE/BWE[3:0]) 20-3 |

|      | 20.2.4  | Output Enable (FB_OE) 20-3                            |

|      |         | Read/Write (FB_R/W)                                   |

|      | 20.2.6  | Address Latch Enable (FB_ALE) 20-4                    |

|      | 20.2.7  | Transfer Size (FB_TSIZ[1:0]) 20-4                     |

|      |         | Transfer Burst (FB_TBST) 20-5                         |

|      | 20.2.9  | Transfer Acknowledge (FB_TA) 20-5                     |

| 20.3 |         | y Map/Register Definition                             |

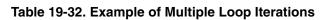

|      |         | Chip-Select Address Registers (CSAR0 – CSAR5) 20-6    |

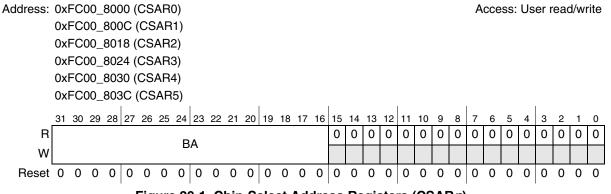

|      | 20.3.2  | Chip-Select Mask Registers (CSMR0 – CSMR5) 20-7       |

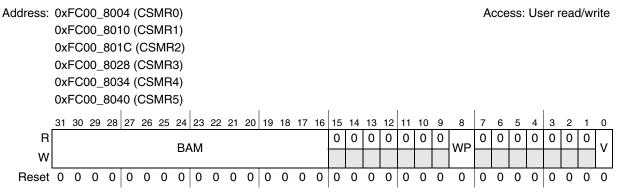

|      | 20.3.3  | Chip-Select Control Registers (CSCR0 – CSCR5) 20-7    |

| 20.4 | Functio | nal Description                                       |

|      | 20.4.1  | Chip-Select Operation                                 |

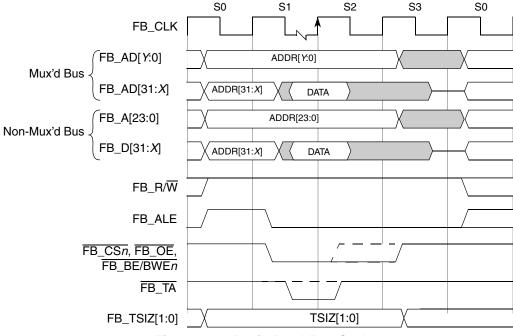

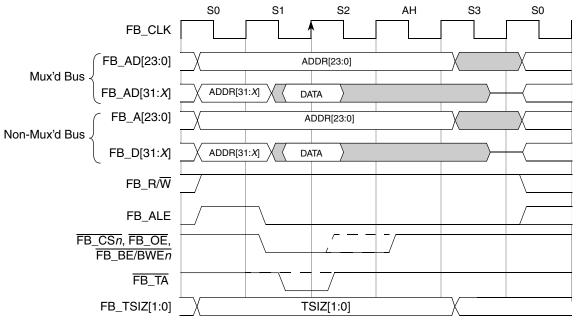

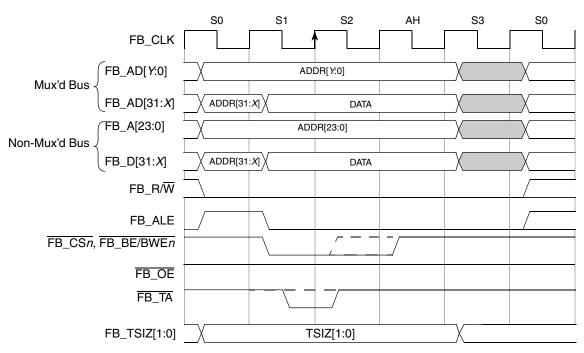

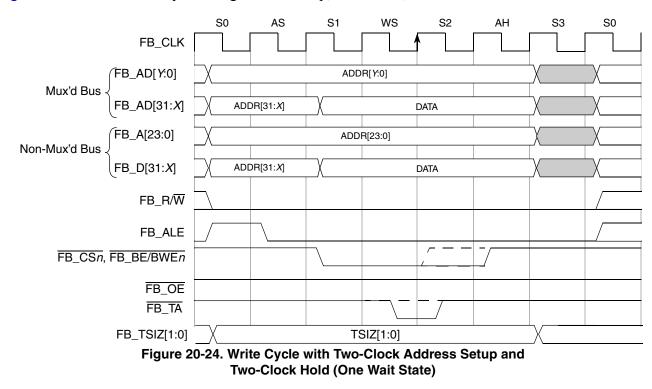

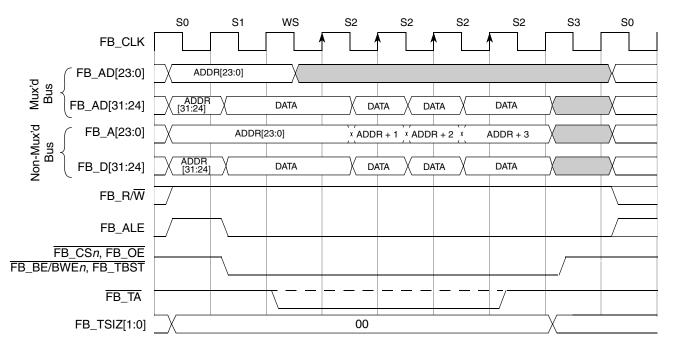

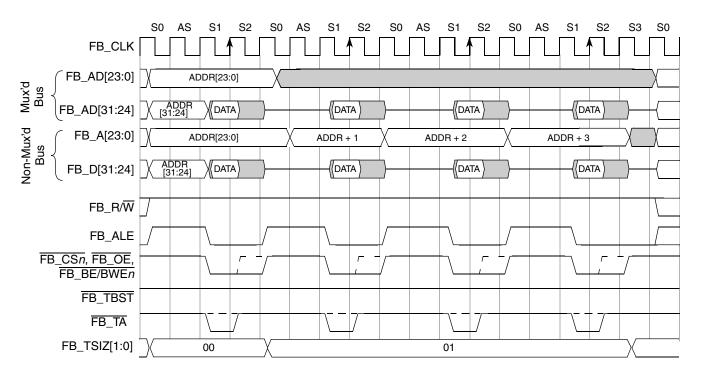

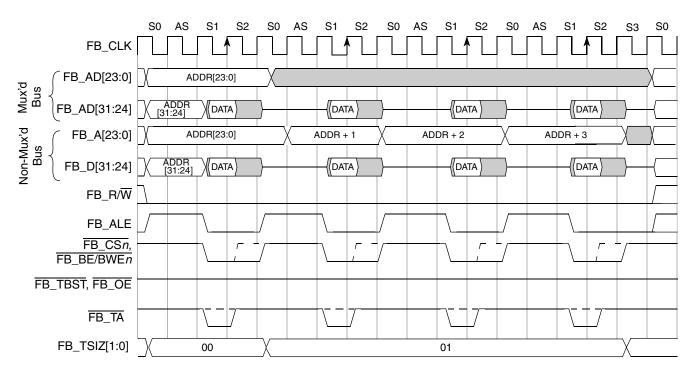

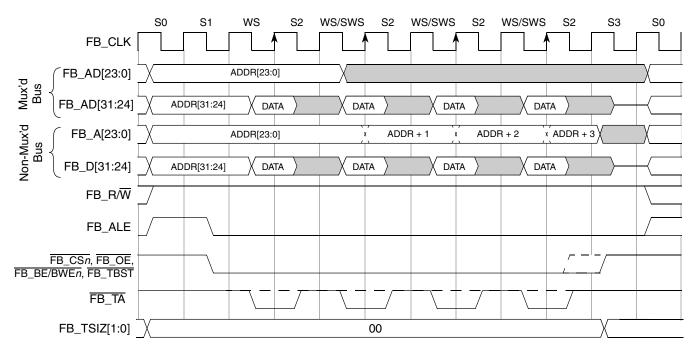

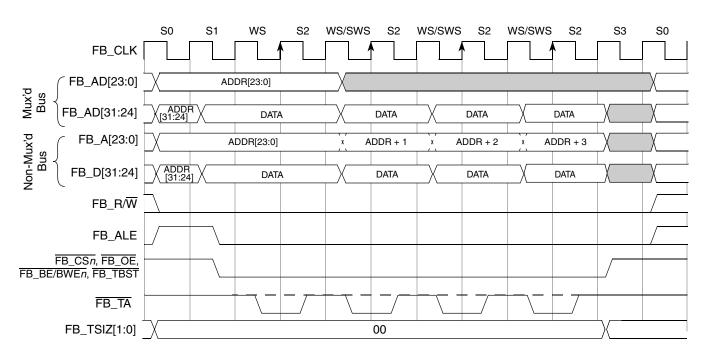

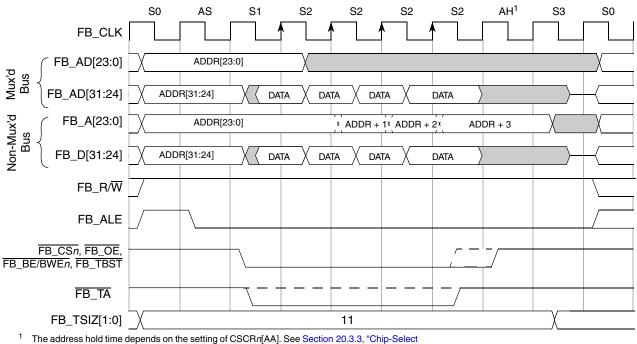

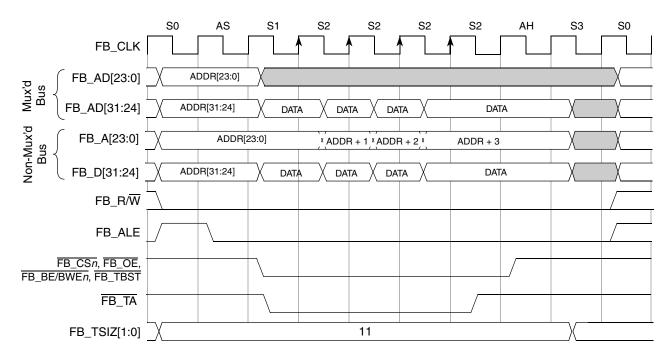

|      | 20.4.2  | Data Transfer Operation 20-11                         |

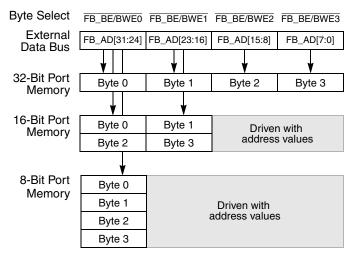

|      | 20.4.3  | Data Byte Alignment and Physical Connections 20-12    |

|      | 20.4.4  | Address/Data Bus Multiplexing 20-12                   |

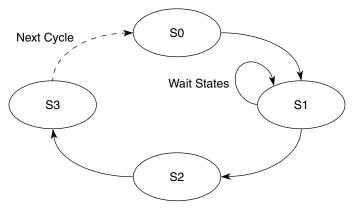

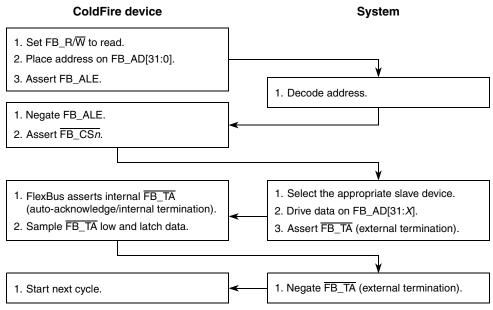

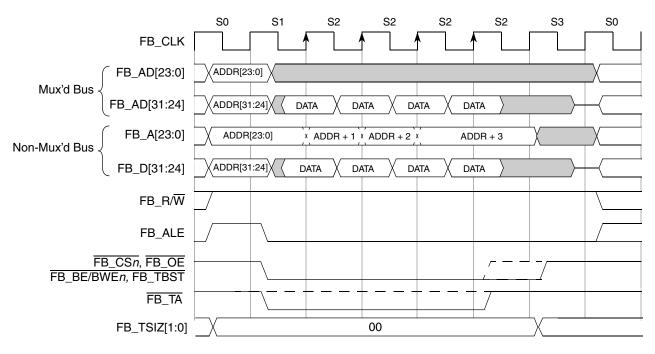

|      | 20.4.5  | Bus Cycle Execution                                   |

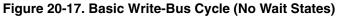

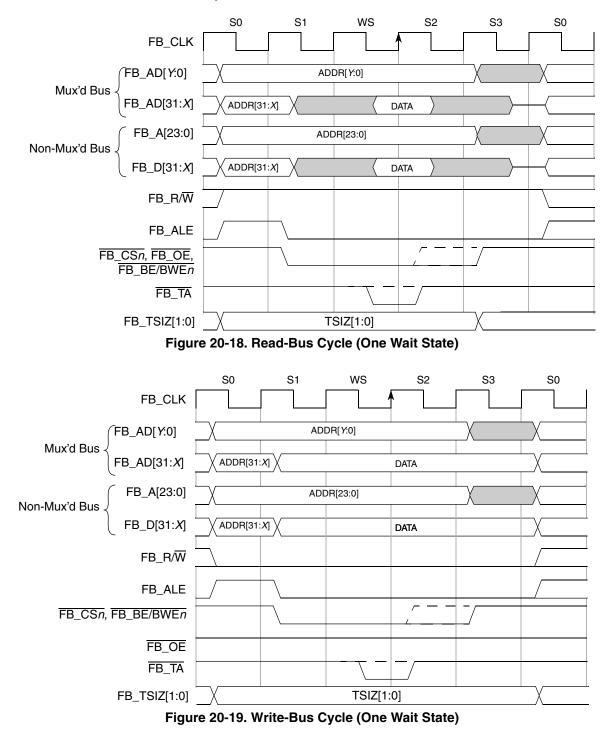

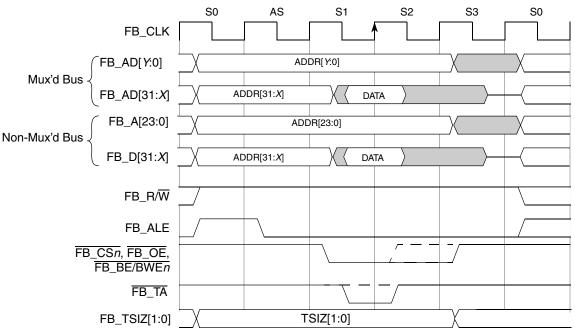

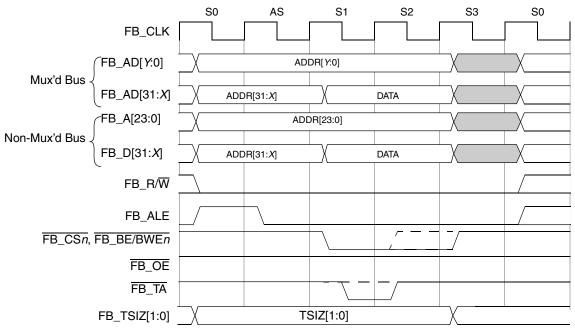

|      | 20.4.6  | FlexBus Timing Examples                               |

|      | 20.4.7  | Burst Cycles                                          |

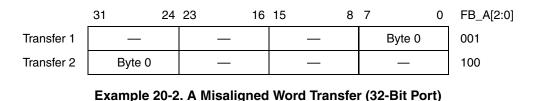

|      | 20.4.8  | Misaligned Operands 20-34                             |

|      | 20.4.9  | Bus Errors                                            |

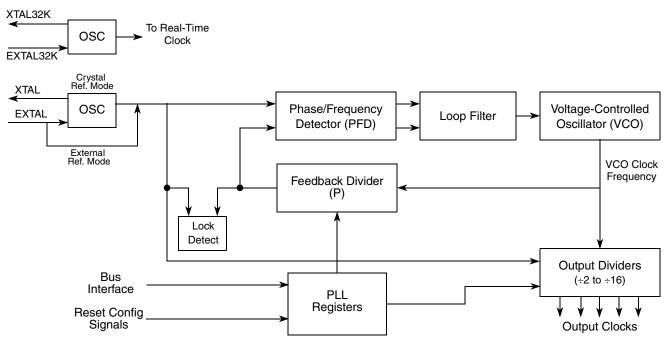

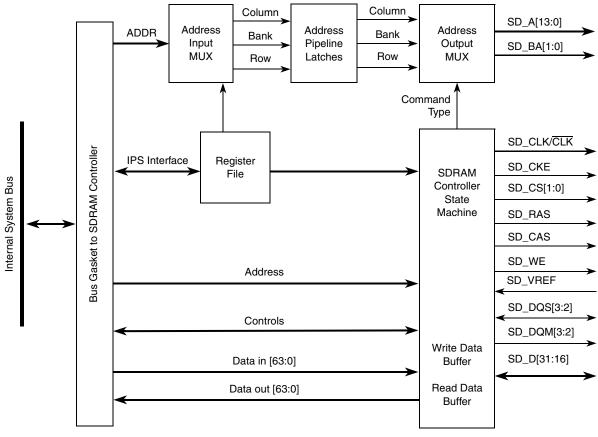

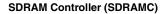

## Chapter 21 SDRAM Controller (SDRAMC)

| 21.1 | Introduo | tion                                 |

|------|----------|--------------------------------------|

|      | 21.1.1   | Block Diagram                        |

|      | 21.1.2   | Features                             |

|      | 21.1.3   | Terminology                          |

| 21.2 | Externa  | I Signal Description                 |

| 21.3 | Interfac | e Recommendations                    |

|      | 21.3.1   | Supported Memory Configurations 21-5 |

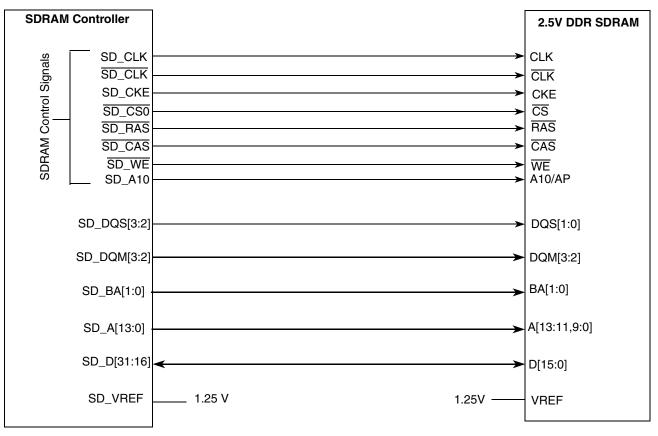

|      | 21.3.2   | SDRAM DDR Component Connections 21-8 |

|      | 21.3.3   | DDR SDRAM Layout Considerations 21-8 |

| 21.4 | Memory   | / Map/Register Definition            |

|      |          |                                      |

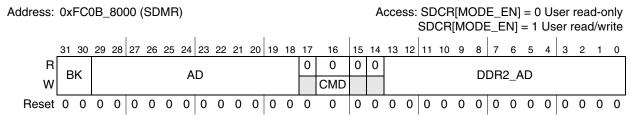

| 21.4.1 SDRAM Mode/Extended Mode F           | Register (SDMR) 21-10               |

|---------------------------------------------|-------------------------------------|

| 21.4.2 SDRAM Control Register (SDCF         | R)                                  |

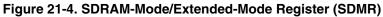

| 21.4.3 SDRAM Configuration Register         | 1 (SDCFG1) 21-12                    |

| 21.4.4 SDRAM Configuration Register         | 2 (SDCFG2) 21-15                    |

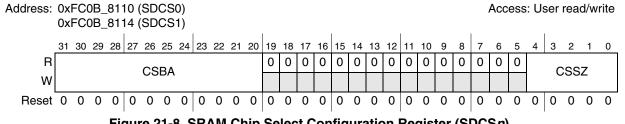

| 21.4.5 SDRAM Chip Select Configuration      | on Registers (SDCS <i>n</i> ) 21-16 |

| 21.5 Functional Description                 |                                     |

| 21.5.1 SDRAM Commands                       |                                     |

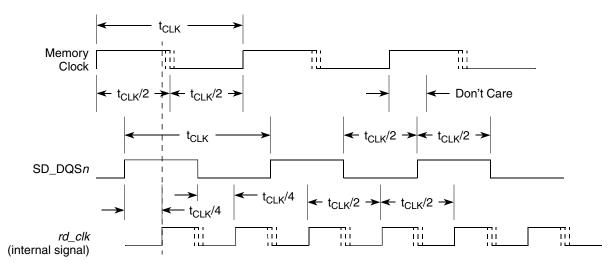

| 21.5.2 Read Clock Recovery (RCR) Blo        | ock 21-26                           |

| 21.6 Initialization/Application Information |                                     |

| 21.6.1 DDR SDRAM Initialization Sequ        | ence                                |

| 21.6.2 Low-power/Mobile SDRAM Initia        | lization Sequence                   |

| 21.6.3 DDR2 SDRAM Initialization Seq        | uence                               |

| 21.6.4 Page Management                      |                                     |

| 21.6.5 Transfer Size                        |                                     |

### Chapter 22 PCI Bus Controller

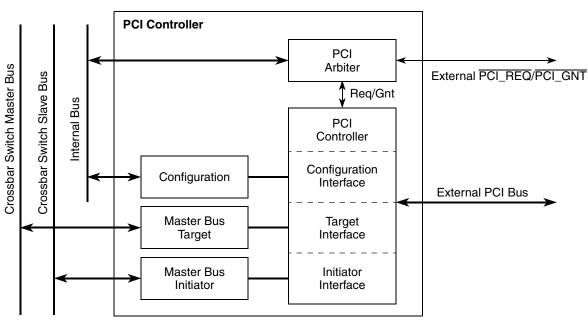

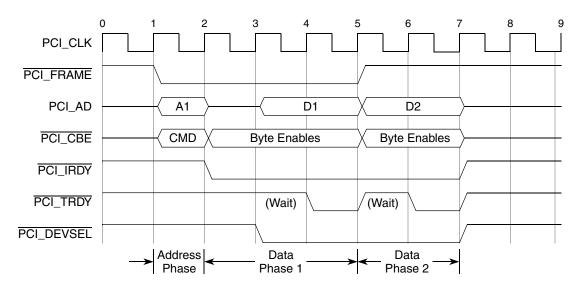

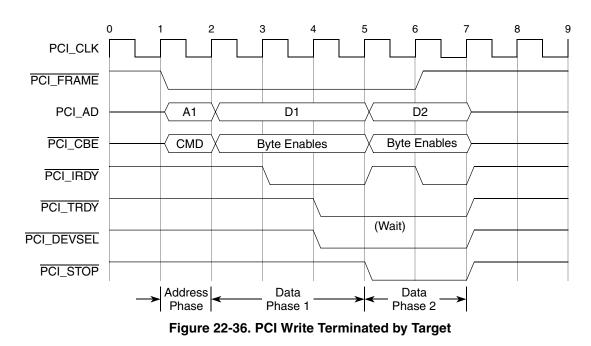

| 22.1 | Introduo | ction                                    | 22-1  |

|------|----------|------------------------------------------|-------|

|      | 22.1.1   | Block Diagram                            | 22-1  |

|      | 22.1.2   | Overview                                 | 22-1  |

|      | 22.1.3   | Features                                 | 22-2  |

|      | 22.1.4   | Modes of Operation                       | 22-2  |

| 22.2 | Externa  | al Signal Description                    | 22-3  |

|      | 22.2.1   | Address/Data Bus (PCI_AD[31:0])          | 22-3  |

|      | 22.2.2   | Clock (PCI_CLK)                          | 22-3  |

|      | 22.2.3   | Command/Byte Enables (PCI_CBE[3:0])      | 22-3  |

|      | 22.2.4   | Device Select (PCI_DEVSEL)               | 22-4  |

|      | 22.2.5   | Frame (PCI_FRAME)                        | 22-4  |

|      | 22.2.6   | Grant (PCI_GNT[3:0])                     | 22-4  |

|      | 22.2.7   | Initialization Device Select (PCI_IDSEL) | 22-4  |

|      | 22.2.8   | Interrupt (PCI_INTA)                     | 22-4  |

|      | 22.2.9   | Initiator Ready (PCI_IRDY)               | 22-4  |

|      | 22.2.10  | Parity (PCI_PAR)                         | 22-4  |

|      | 22.2.11  | Parity Error (PCI_PERR)                  | 22-4  |

|      | 22.2.12  | Request (PCI_REQ[3:0])                   | 22-4  |

|      |          | BReset (PCI_RST)                         |       |

|      | 22.2.14  | System Error (PCI_SERR)                  | 22-5  |

|      |          | Stop (PCI_STOP)                          |       |

|      | 22.2.16  | Target Ready (PCI_TRDY)                  | 22-5  |

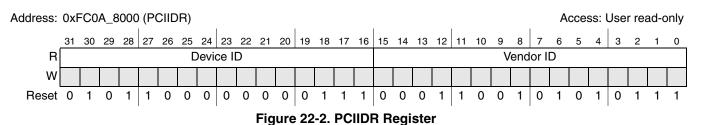

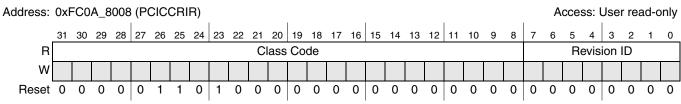

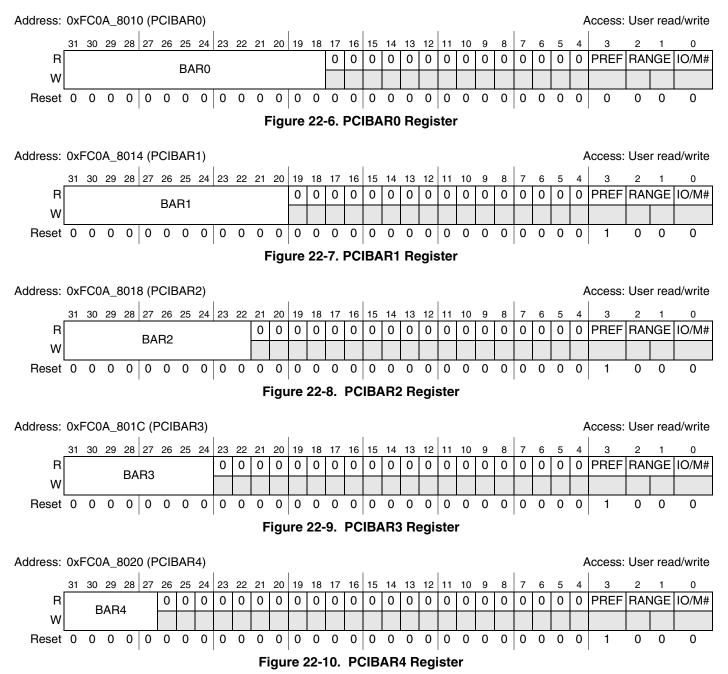

| 22.3 | Memory   | y Map/Register Definition                | 22-5  |

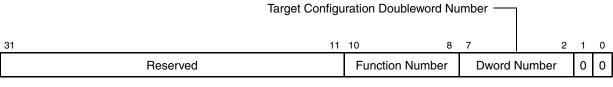

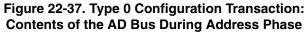

|      | 22.3.1   | PCI Type 0 Configuration Registers       | 22-7  |

|      | 22.3.2   | General Control/Status Registers         | 22-14 |

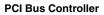

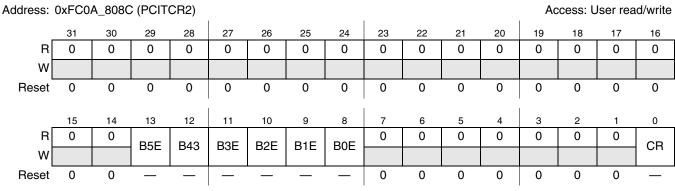

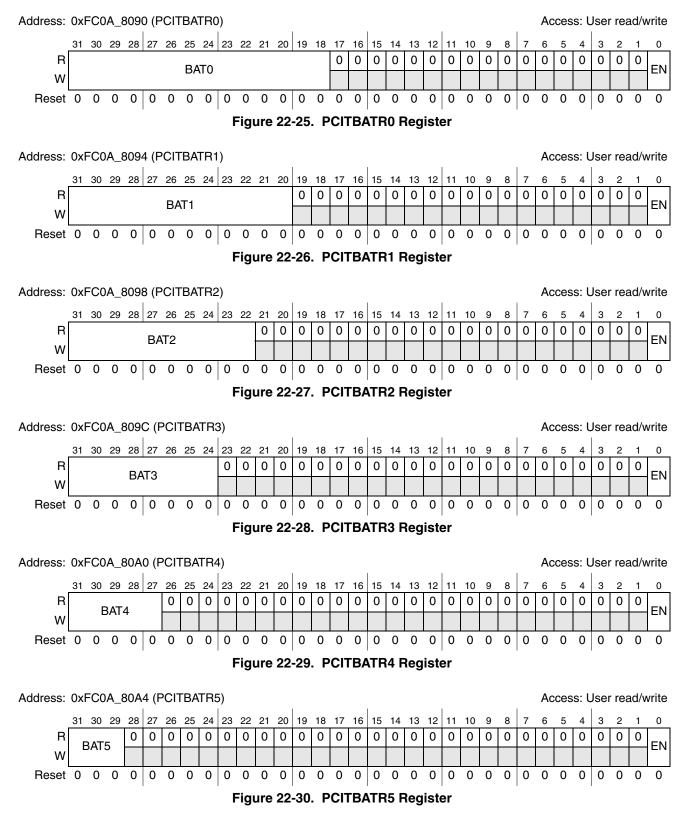

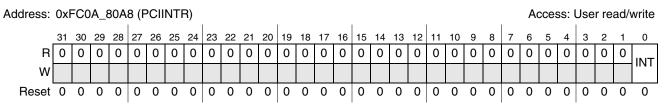

| 22.3.3        | PCI Arbiter Registers                      |

|---------------|--------------------------------------------|

| 22.4 Function | onal Description                           |

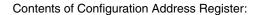

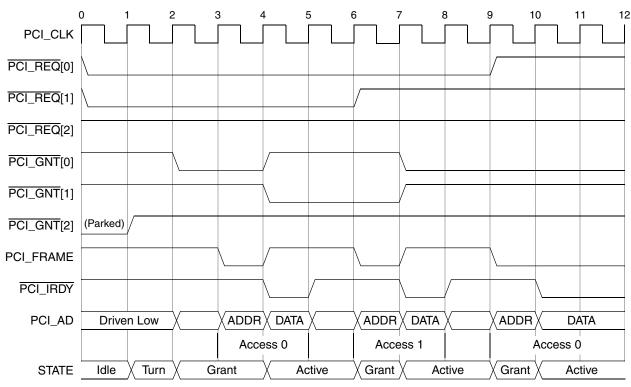

| 22.4.1        | PCI Bus Protocol                           |

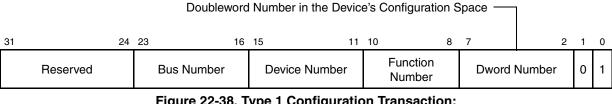

| 22.4.2        | Configuration Interface                    |

| 22.4.3        | Internal Bus Initiator Interface           |

|               | Internal Bus Target Interface              |

| 22.4.5        | PCI Arbiter                                |

| 22.4.6        | PCI Clock Scheme                           |

| 22.4.7        | Interrupts                                 |

| 22.4.8        | Reset                                      |

| 22.5 Applica  | ation Information                          |

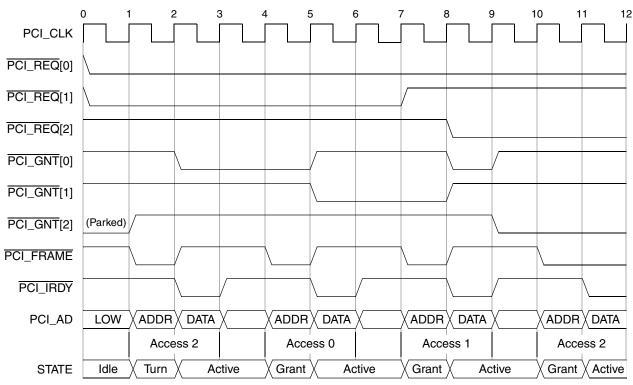

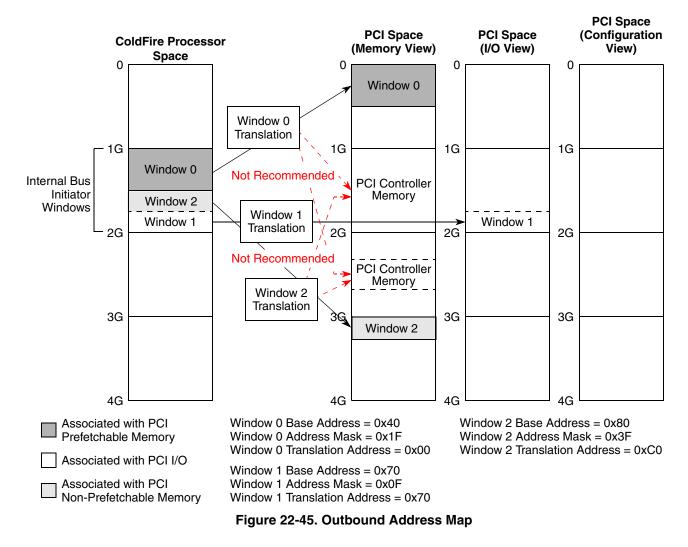

| 22.5.1        | Internal Bus-Initiated Transaction Mapping |

| 22.5.2        | Address Translation                        |

### Chapter 23 Advanced Technology Attachment (ATA)

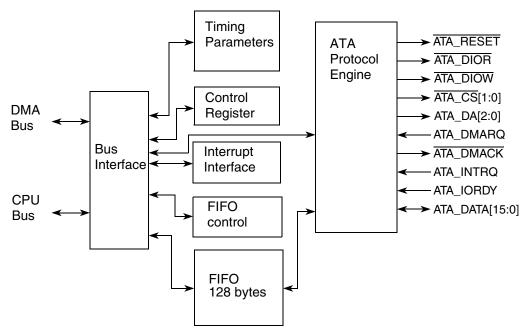

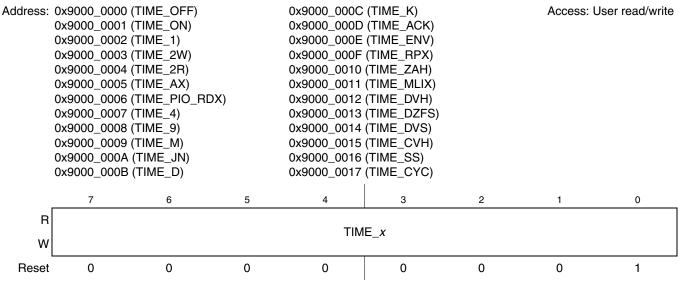

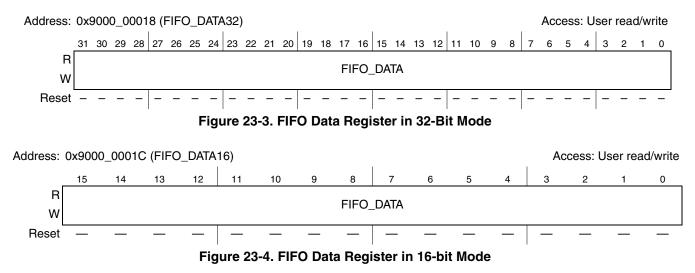

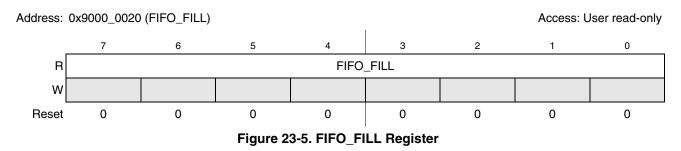

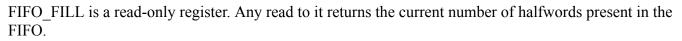

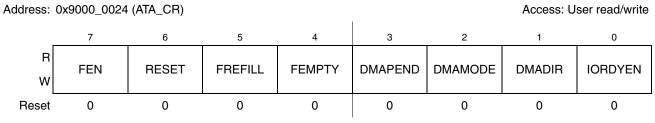

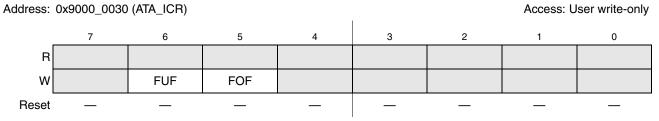

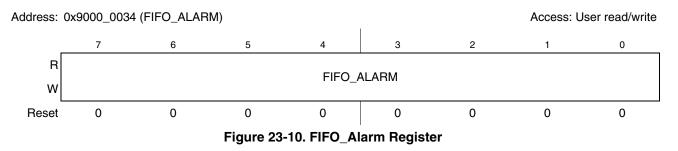

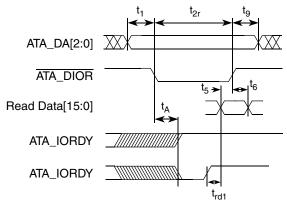

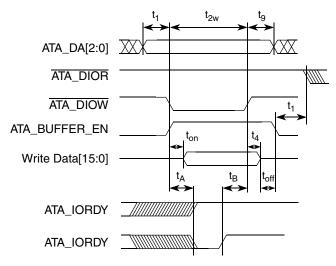

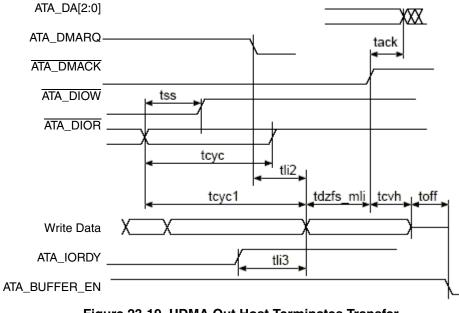

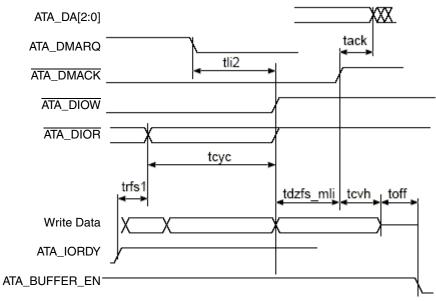

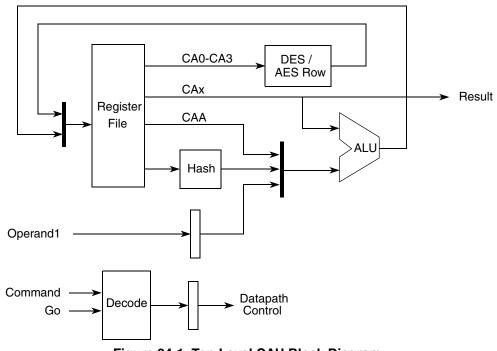

| 23.1.1       Overview       23-1         23.1.2       Features       23-2         23.1.3       Modes of Operation       23-2         23.2       External Signal Description       23-3         23.2.1       Detailed Signal Descriptions       23-3         23.2       External Signal Descriptions       23-3         23.2.1       Detailed Signal Descriptions       23-3         23.3       Memory Map/Register Definition       23-5         23.3.1       Endianness       23-6         23.3.2       Timing Registers (TIME_x)       23-7         23.3.3       FIFO Data Register (FIFO_DATA_n)       23-7         23.3.4       FIFO_FILL Register       23-8         23.3.5       ATA Control Register (ATA_CR)       23-8         23.3.6       Interrupt Registers       23-9         23.3.7       FIFO Alarm Register (FIFO_ALARM)       23-12         23.4       Functional Description       23-13         23.4.1       Timing on ATA Bus       23-13         23.4.2       Resetting ATA Bus       23-13         23.4.3       Programming ATA Bus Timing and IORDYEN       23-21         23.4.4       Access to ATA Bus in PIO Mode       23-21         23.4.5 | 23.1 | Introduc | ction                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|----------------------------------------------|