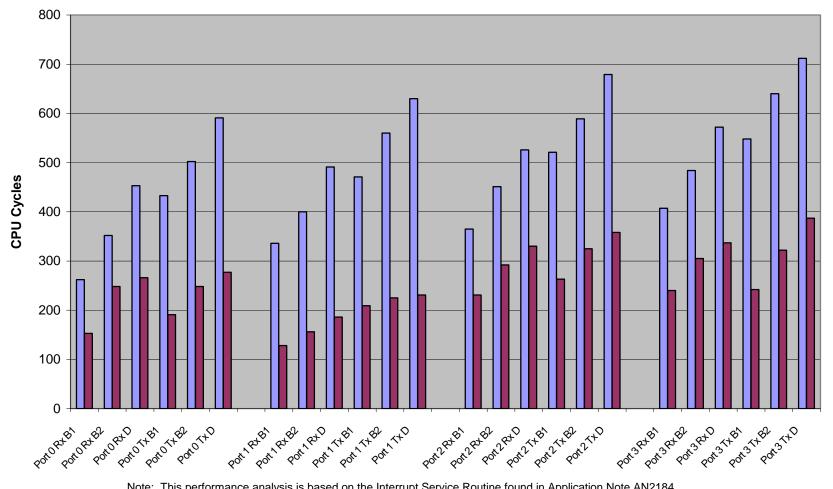

## **PLIC ISR Performance Analysis** (General Purpose)

■ Average CPU Cycles (Cache off) ■ Average CPU Cycles (Cache on)

Note: This performance analysis is based on the Interrupt Service Routine found in Application Note AN2184.

|              | 1                                    |                                     |                               |

|--------------|--------------------------------------|-------------------------------------|-------------------------------|

| Operation    | Average<br>CPU Cycles<br>(Cache off) | Average<br>CPU Cycles<br>(Cache on) | Comments                      |

| Port 0 Rx B1 | 262                                  | 153                                 | These measurments were        |

| Port 0 Rx B2 | 352                                  | 248                                 | taken on the M5272C3          |

| Port 0 Rx D  | 453                                  |                                     | running the General Purpose   |

| Port 0 Tx B1 | 433                                  | 191                                 | PLIC ISR code packaged in     |

| Port 0 Tx B2 | 502                                  | 248                                 | the MCF5272 Initialization    |

| Port 0 Tx D  | 591                                  | 277                                 | Template.                     |

|              |                                      |                                     | The 'CPU Cycles' fields       |

| Port 1 Rx B1 | 336                                  | 128                                 | measure the execution of      |

| Port 1 Rx B2 | 400                                  | 156                                 | the Interrupt Service Routine |

| Port 1 Rx D  | 491                                  | 186                                 | I_PLI_Periodic() running in   |

| Port 1 Tx B1 | 471                                  | 209                                 | SDRAM found in Application    |

| Port 1 Tx B2 | 560                                  | 225                                 | Note, AN2184. These           |

| Port 1 Tx D  | 630                                  | 231                                 | routines can be found in the  |

|              |                                      |                                     | file PerIntVectors.s.         |

| Port 2 Rx B1 | 365                                  | 231                                 |                               |

| Port 2 Rx B2 | 451                                  | 292                                 |                               |

| Port 2 Rx D  | 526                                  | 330                                 |                               |

| Port 2 Tx B1 | 521                                  | 263                                 |                               |

| Port 2 Tx B2 | 589                                  | 325                                 |                               |

| Port 2 Tx D  | 679                                  | 358                                 |                               |

|              |                                      |                                     |                               |

| Port 3 Rx B1 | 407                                  | 240                                 |                               |

| Port 3 Rx B2 | 484                                  | 305                                 |                               |

| Port 3 Rx D  | 572                                  | 337                                 |                               |

| Port 3 Tx B1 | 548                                  | 242                                 |                               |

| Port 3 Tx B2 | 640                                  | 322                                 |                               |

| Port 3 Tx D  | 712                                  | 387                                 | ]                             |

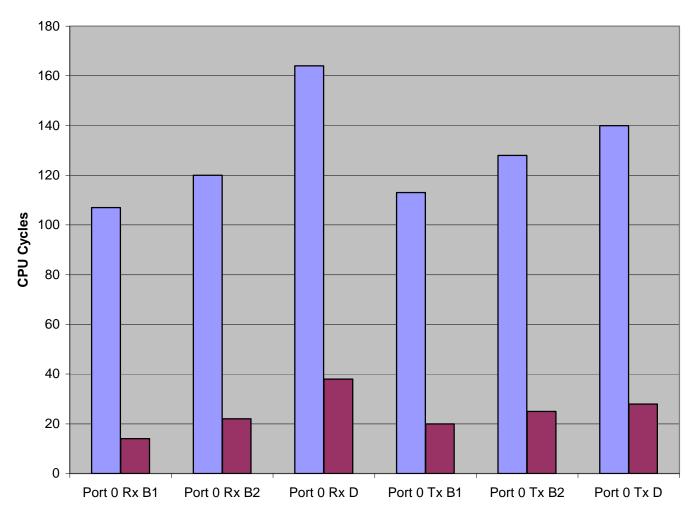

## PLIC ISR Performance Analysis (High Performance)

| Operation    | Average<br>CPU Cycles<br>(Cache off) | Average<br>CPU Cycles<br>(Cache on) | Comments                                                                                                                                                                                                                                                           |

|--------------|--------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 0 Rx B1 | 107                                  | 14                                  | These measurments were                                                                                                                                                                                                                                             |

| Port 0 Rx B2 | 120                                  | 22                                  | taken on the M5272C3                                                                                                                                                                                                                                               |

| Port 0 Rx D  | 164                                  | 38                                  | running the High                                                                                                                                                                                                                                                   |

| Port 0 Tx B1 | 113                                  | 20                                  | Performance PLIC ISR code                                                                                                                                                                                                                                          |

| Port 0 Tx B2 | 128                                  | 25                                  | packaged in the MCF5272                                                                                                                                                                                                                                            |

| Port 0 Tx D  | 140                                  | 28                                  |                                                                                                                                                                                                                                                                    |

|              |                                      |                                     | Initialization Template.<br>The 'CPU Cycles' fields<br>measure the execution of the<br>PLIC Interrupt Service<br>Routine, an optimized<br>version of I_PLI_Periodic(),<br>running in SDRAM. The<br>performance for the<br>remaining ports will be very<br>similar. |

|              | ļ                                    |                                     |                                                                                                                                                                                                                                                                    |

|              |                                      |                                     |                                                                                                                                                                                                                                                                    |