# Media5200 User's Guide

MEDIA5200UG Rev. 0, 5/2006

# NP

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 26668334 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. These products incorporate SuperFlash® technology licensed from SST. The PowerPC and PowerPC 603e are trademarks of IBM Corp. and used under license. © Freescale Semiconductor, Inc. 2006. All rights reserved.

MEDIA5200UG Rev. 0 5/2006

# **About This Book**

This user's manual describes the functionality of the Media5200 Multimedia Development for software and hardware developers.

The information in this book is subject to change without notice. Updates for this document may be found at:

http://www.freescale.com/mobileGT.

### Organization

Following is a summary and brief description of the major sections of this manual:

- Chapter 1, "Introduction," includes general descriptions of the features incorporated on the Media5200 Multimedia Development Platform.

- Chapter 2, "Kit Contents," describes the contents of the Media5200 package.

- Chapter 3, "Getting Started," describes the steps of powering on the Media5200, communicating to a host computer, and installing the desired Real-Time Operating System on the system.

- Chapter 4, "Hardware Description," contains the block diagram and outlines all board settings.

- Chapter 5, "Boot Monitor," describes the steps to download and flash code using Ethernet and UART protocols.

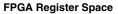

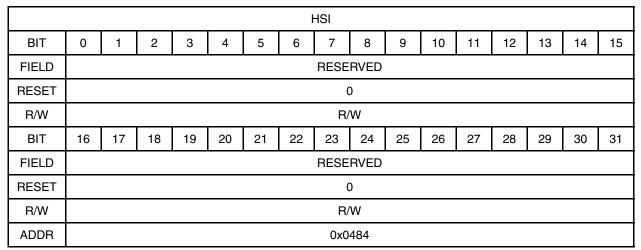

- Chapter 6, "FPGA Register Space," provides the entire register map for the FPGA.

This manual includes the following two appendixes:

- Appendix A, "Build History," provides an overview of various development builds of the Media5200 Multimedia Development Platform.

- Appendix B, "Glossary of Terms and Abbreviations," contains an alphabetical list of terms, phrases, and abbreviations used in this book.

#### **Additional Documentation**

Additional useful documentation for the Media5200 system include:

- MPC5200B User's Manual, (MPC5200BUG)

- Media 5200 Board Schematics

- Media5200 MAIN Board Schematics

- Media5200 AUDIO Board Schematics

- Media5200 POWER Schematics

About This Book

- Media5200 GPS Schematics

- Media5200 MOST Schematics

- Media5200 PCB Layout Files

- U-Boot Quick Reference

- Real-Time Operating System Partners

- Green Hills Software Integrity

- QNX Software Systems Ltd. Neutrino

- Wind River Systems VxWorks

- Linux

# **Chapter 1 Introduction**

The Media5200 Multimedia Development Platform is designed to provide a working hardware environment in which to evaluate the MPC5200B, develop software, and verify the performance of a fully integrated system using actual applications software. The board has built in graphics control, an integrated display as well as physical interface devices for the CAN, I2C and ETHERNET ports.

The MPC5200B microcontroller (MCU) has two external data/address bus structures. The LocalPlus Bus is used to address FLASH, SRAM, peripheral devices and other types of memory. The LocalPlus Bus can perform memory accesses in several multiplexed and non-multiplexed addressing modes. While it is possible to execute code residing in memory devices on the LocalPlus Bus, code execution is generally performed on the SDRAM bus which is specifically made to interface to Synchronous Single- and Double Data Rate Dynamic RAMs. In general, many MPC5200B systems are designed such that programs to be executed are stored as data in FLASH devices residing on the LocalPlus Bus. On system initialization, a program being executed on the LocalPlus Bus will copy the applications code to memory on the SDRAM Bus and then code execution will jump to a device on the SDRAM bus. The SDRAM bus is specifically designed to interface with the MPC5200B's internal instruction cache for superior instruction throughput.

The MPC5200B microcontroller has several external ports to interface the internal peripheral elements to external devices. In general, these ports can be configured to perform different functions. That is, a particular port can be configured to take on one of several different configurations. For instance, the TIMER module can appear on one of two different ports. Also, a port, such as Programmable Serial Controller Port 1, can be configured to be a UART, a CODEC, General Purpose Input/Output or an AC97 interface. The Media5200 Multimedia Development Platform does not provide for all possible configurations of the MPC5200B MCU ports. However, all of the internal peripheral elements are available on at least one port.

The Media5200 Multimedia Development Platform is actually intended to be used by engineers and programmers who are using high level software tools to write and debug software on a fully functional system. The onboard monitor program, U-Boot, is used to control loading programs, setting up communications protocols, loading and examining memory and other such functions. The U-Boot Monitor Program has very limited software debug capabilities. The Media5200 Multimedia Development Platform does provide a very effective platform to execute user applications code.

Introduction

# Chapter 2 Kit Contents

### 2.1 Kit Contents for the Media5200

The following contents are included in the Media5200 kit:

- 1. Media5200 Multimedia Development System with Base and Head Units

- 2. Power supply (input 100-240VAC, 50-60Hz; output 12VDC, 5A)

- a) USA adapter

- b) European adapter

- c) British adapter

- d) Australian adapter

- 3. Serial cable

- 4. GPS antenna (Synergy Systems P/N 10001699)

- 5. MPC5200B Development Kit CD

- 6. Green Hills Software

- a) Evaluation CDs

- b) Thumbdrive with demonstration software

- 7. QNX Systems Software Ltd

- a) Evaluation CDs

- b) Thumbdrive with demonstration software

- 8. Wind River Systems

- a) Evaluation CDs

- b) Thumbdrive with demonstration software

- 9. Linux demonstration thumbdrive

- 10. ALT software demonstration CD

- 11. Other paper collateral

Kit Contents

# **Chapter 3 Getting Started**

#### 3.1 Introduction

This document walks through setup and installation of a desired real-time operating system on the mobileGT® Media5200 Multimedia Development Platform. Its purpose is for the developer to get started with the system as quickly as possible.

### 3.2 Serial Connection

A serial connection is used to communicate between the host terminal (user's PC) and the target system (mobileGT Media5200.) Included with the mobileGT Media5200 is a 9-pin null modem serial cable. Connect this cable from the UART INTO port on the mobileGT Media5200 to the UART port on the host system.

### 3.3 Terminal Emulator Configuration

Use a terminal emulator to connect from the host to the mobileGT Media5200 Target System. HyperTerminal is distributed with Windows if no other is available. The terminal emulator must be set up with the following parameters:

- 115200 baud

- 8 data bits

- no parity

- 1 stop bit

- no flow control.

### 3.4 Power Connection

Power the mobileGT Media5200 Target System by connecting the power supply to the connector on the back of the target system.

### 3.5 Booting Up the System

The Media5200 U-Boot is the only image pre-programmed into the target flash at the factory. The user will need to install the desired RTOS using the provided thumb drives. On power-on, the default U-Boot banner will display informational text similar to

```

U-Boot 1.1.3 (Apr 25 2006 - 22:09:33)

CPU: MPC5200 v2.2 at 396 MHz

Bus 132 MHz, IPB 132 MHz, PCI 33 MHz

Board: Media5200 (FPGA 02090403)

```

Media5200 User's Guide, Rev. 0

Getting Started

```

I2C: 85 kHz, ready

DRAM: 128 MB

FLASH: 64 MB

PCI: Bus Dev VenId DevId Class Int

00 1c 10cf 201e 0380 3f

00 1d 1057 5809 0680 00

GFX: CoralP at 0x40000000

Autostarting. Press any key to abort...

Hit any key to stop autoboot: 0

=>

```

For UBOOT commands, refer to the *U-Boot Quick Reference* document provided on the MPC5200B Development Kit CD, or visit http://www.denx.de/wiki/DULG/Manual.

#### 3.6 **RTOS Installation**

Read the end-user agreement before unpacking the USB thumb drives. Four real-time operating systems (RTOS) are included with the Media5200: Green Hills Software Integrity, Linux, QSSL QNX Neutrino, and Wind River VxWorks. Select the desired RTOS thumb drive and insert into the USB port on the Media5200 Target System, located on the front panel. Press the RESET button at the back of the Media5200.

Once the target system reboots, a script will begin installing the RTOS image located on the USB thumbscrew. The autoboot script will:

- 1. Erase the on-board flash.

- 2. Copy the RTOS image onto RAM

- 3. Copy image from RAM to on-board flash

Once the installation is completed, reboot the system again allow to autoboot. The system will now boot to the operating system.

# **Chapter 4 Hardware Description**

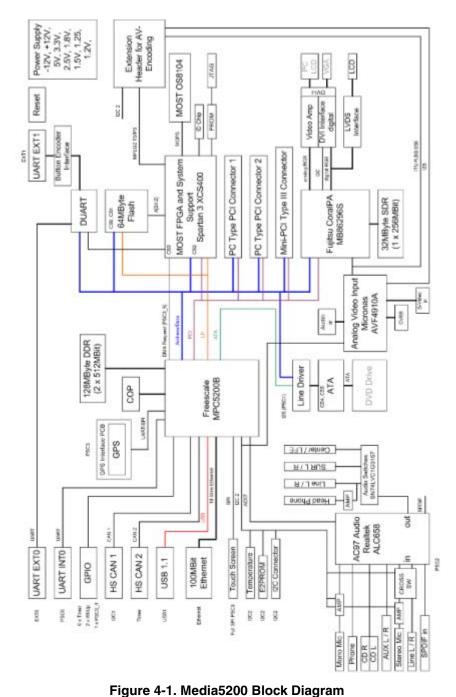

### 4.1 Block Diagram

igure 4-1. Media5200 Diock Diagram

Media5200 User's Guide, Rev. 0

### 4.2 MAIN Board Switches, Jumpers, Connectors, and Headers

#### 4.2.1 MAIN Board Switches

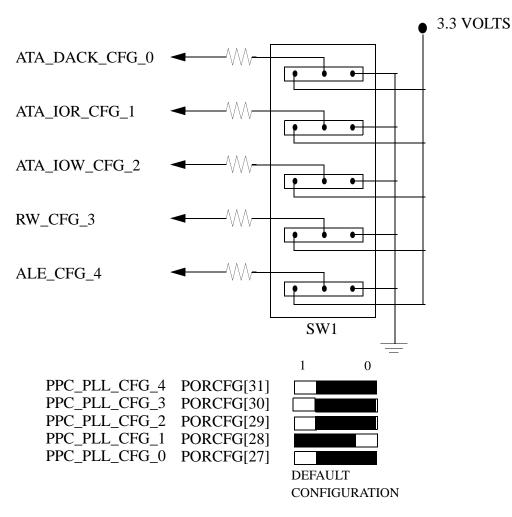

Figure 4-2. MAIN Board Switch SW1 Configuration Settings

\_\_\_\_\_

| Package<br>Ball # | Signal<br>Name | CDM<br>Reset<br>Config.<br>Bit | MPC5200B<br>Reset<br>Config.<br>Reg. BIT | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|----------------|--------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y18               | ATA_DACK       | PORCFG[31]                     | PPC_PLL_CFG_4                            | MPC5200B's PPC Core PLL Configuration                                                                                                                                                                                                                                                                                                                                                                                                        |

| Y17               | ATA_IOR        | PORCFG[30]                     | PPC_PLL_CFG_3                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| W17               | ATA_IOW        | PORCFG[29]                     | PPC_PLL_CFG_2                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| W16               | LP_R/W         | PORCFG[28]                     | PPC_PLL_CFG_1                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V14               | LP_ALE         | PORCFG[27]                     | PPC_PLL_CFG_0                            |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Y13               | LP_TS          | PORCFG[26]                     | xlb_clk_sel                              | bit = 0: XLB_CLK = SYS_PLL FVCO/4<br>bit = 1: XLB_CLK = SYS_PLL_FVCO/8                                                                                                                                                                                                                                                                                                                                                                       |

| H02               | USB1           | PORCFG[25]                     | sys_pll_cfg_0                            | bit =0 : SYS_PLL FVCO = 16x SYS_PLL_FREF<br>bit =1 : SYS_PLL FVCO = 12x SYS_PLL_FREF                                                                                                                                                                                                                                                                                                                                                         |

| H03               | USB2           | PORCFG[24]                     | 2x_FVCO                                  | bit = 0: Fvco = 12x or 16x sys_xtal_in (default)<br>bit = 1: Fvco = 24x or 32x sys_xtal_in                                                                                                                                                                                                                                                                                                                                                   |

| K01               | ETH0           | PORCFG[23]                     | most_graphics_sel                        | bit = 0: Most Graphics boot not enabled<br>bit = 1: Most Graphics boot enabled.                                                                                                                                                                                                                                                                                                                                                              |

| K02               | ETH1           | PORCFG[16]                     | large_flash_sel                          | bit = 0: Large Flash boot not enabled<br>bit = 1: Large Flash boot enabled.                                                                                                                                                                                                                                                                                                                                                                  |

| K03               | ETH2           | PORCFG[21]                     | ppc_msrip                                | PPC Boot Address / Exception Table Loc.<br>bit = 0: 0000 0100 (hex)<br>bit = 1: fff0 0100 (hex)                                                                                                                                                                                                                                                                                                                                              |

| J01               | ETH3           | PORCFG[20]                     | boot_rom_wait                            | bit = 0: 4 IPbus clocks of waitstate*<br>bit = 1: 48 IPbus clocks of waitstate*                                                                                                                                                                                                                                                                                                                                                              |

| J02               | ETH4           | PORCFG[19]                     | boot_rom_swap                            | bit = 0: no byte lane swap - same endian ROM image<br>bit = 1: byte lane swap - different endian ROM image<br>(This option is typically not used because MPC5200 can boot<br>from either endian)                                                                                                                                                                                                                                             |

| L03               | ETH5           | PORCFG[18]                     | boot_rom_size                            | For "non-muxed" boot ROMs<br>bit = 0: 8-bit boot ROM data bus 24-bit boot ROM address<br>bit = 1: 16-bit boot ROM data bus 16-bit boot ROM address<br>For "muxed" boot ROMs boot ROM addr is max 25 significant<br>bits during address tenure.<br>bit = 0: 16-bit ROM data bus<br>bit = 1: 32-bit ROM data bus<br>For "large flash" boot case boot Flash addr is 25 bits.<br>bit = 0: 8-bit Flash data bus<br>bit = 1: 16-bit Flash data bus |

| N02               | ETH6           | PORCFG[17]                     | boot_rom_type                            | bit = 0: non-muxed boot ROM bus, single tenure transfer.<br>bit = 1: muxed boot ROM bus,<br>PPC like with address & data tenures, ALE_b & TS_b active.                                                                                                                                                                                                                                                                                       |

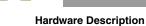

3.3 VOLTS LP\_TS • USB1 • USB2 • SW2 1 0 XLB\_CLK\_SEL PORCFG[26] SYS\_PLL\_CFG PORCFG[25] BOOT\_HIGH PORCFG[24] DEFAULT CONFIGURATION

Figure 4-4. MAIN Board Switch SW3 Manual Reset Switch

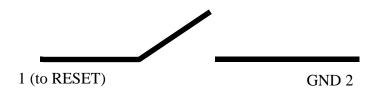

### 4.2.2 MAIN Board Jumpers

| Jumper | Function           | Settings      | Switch<br>Position | Description                                                |

|--------|--------------------|---------------|--------------------|------------------------------------------------------------|

| J1     | LARGE FLASH        | 2 - 3 (3.3 V) | GND 3.3V           | Large Flash Boot enabled                                   |

|        |                    | 1 - 3 (GND)   | GND 3.3V           | Large Flash Boot not enabled<br>(default setting)          |

| J2     | 2xFVCO             | 2 - 3 (3.3 V) | GND 3.3V           | Fvco = 24x or 32x sys_xtal_in                              |

|        |                    | 1 - 3 (GND)   | GND 3.3V           | Fvco = 12x or 16x sys_xtal_in<br>(default setting)         |

| J3     | MOST<br>GRAPHICS   | 2 - 3 (3.3 V) | GND 3.3V           | Most Graphics Boot enabled                                 |

|        |                    | 1 - 3 (GND)   | GND 3.3V           | Most Graphics Boot not enabled<br>(default setting)        |

| J4     | MANY<br>WAITSTATES | 2 - 3 (3.3 V) | GND 3.3V           | 48 IP BUS clock periods of wait states                     |

|        |                    | 1 - 3 (GND)   | GND 3.3V           | 4 IP BUS clock periods of wait states<br>(default setting) |

Table 4-2. MAIN Board Jumpers J1 – J9

| Jumper | Function               | Settings      | Switch<br>Position | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|--------|------------------------|---------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J5     | WIDE BOOT<br>DATA LANE | 1 - 3 (3.3 V) | GND 3.3V           | For "non-muxed" boot ROMs<br>bit = 0: 8-bit boot ROM data bus 24-bit boot<br>ROM address<br>bit = 1: 16-bit boot ROM data bus 16-bit<br>boot ROM address<br>For "muxed" boot ROMs boot ROM addr is<br>max 25 significant bits during address<br>tenure.<br>bit = 0: 16-bit ROM data bus<br>bit = 1: 32-bit ROM data bus<br>For "large flash" boot case boot Flash addr<br>is 25 bits.<br>bit = 0: 8-bit Flash data bus<br>bit = 1: 16-bit Flash data bus<br>bit = 1: 16-bit Flash data bus |  |

|        |                        | 2 - 3 (GND)   | GND 3.3V<br>2 3 1  | For "non-muxed" boot ROMs<br>bit = 0: 8-bit boot ROM data bus 24-bit boot<br>ROM address<br>bit = 1: 16-bit boot ROM data bus 16-bit<br>boot ROM address<br>For "muxed" boot ROMs boot ROM addr is<br>max 25 significant bits during address<br>tenure.<br>bit = 0: 16-bit ROM data bus<br>bit = 1: 32-bit ROM data bus<br>For "large flash" boot case boot Flash addr<br>is 25 bits.<br>bit = 0: 8-bit Flash data bus<br>bit = 1: 16-bit Flash data bus                                   |  |

| J6     | MUXED BOOT             | 1 - 3 (3.3 V) | GND 3.3V<br>2 3 1  | Muxed Boot ROM Bus<br>(PPC like with address & data tenures,<br>ALE_b & TS_b active.)<br>(default setting)                                                                                                                                                                                                                                                                                                                                                                                 |  |

|        |                        | 2 - 3 (GND)   | GND 3.3V<br>2 3 1  | Non-muxed boot ROM bus, single tenure transfer                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

#### Table 4-2. MAIN Board Jumpers J1 – J9 (continued)

| Jumper | Function           | Settings      | Switch<br>Position                                                                               | Description                                                    |

|--------|--------------------|---------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| J7     | BYTE LANE<br>SWAP  | 2 - 3 (3.3 V) | GND 3.3V                                                                                         | byte lane swap—different endian ROM<br>image                   |

|        |                    | 1 - 3 (GND)   | GND 3.3V                                                                                         | No byte lane swap<br>(default setting)                         |

| J8     | BOOT HIGH          | 2 - 3 (3.3 V) |                                                                                                  |                                                                |

|        |                    | 1 - 3 (GND)   |                                                                                                  |                                                                |

| 99     | BOOT HIGH /<br>LOW | 1 - 3 (3.3 V) | GND 3.3V                                                                                         | PPC Boot Address / Exception Table<br>Location<br>0x 0000 0100 |

|        |                    | 2 - 3 (GND)   | $\begin{array}{c} \text{GND} & 3.3\text{V} \\ \hline \bullet & \bullet \\ 2 & 3 & 1 \end{array}$ | PPC Boot Address / Exception Table<br>Location<br>0x FFF0 0100 |

| Jumper | Function    | Switch<br>Positions | Description                                    |

|--------|-------------|---------------------|------------------------------------------------|

| J10    | JTAG_TRST_B | GND 3.3V            | Pull JTAG Reset pin high (enable)              |

|        |             | GND 3.3V            | Pull JTAG Reset pin low (disable)<br>(Default) |

| Jumper | Function                               | Switch<br>Positions                                                              | Description |

|--------|----------------------------------------|----------------------------------------------------------------------------------|-------------|

| J11    | TEST_MODE_0                            | GND 3.3V                                                                         |             |

|        |                                        | GND 3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V<br>3.3V | (Default)   |

| J12    | TEST_MODE_1                            | GND 3.3V                                                                         |             |

|        |                                        | GND 3.3V                                                                         | (Default)   |

| J13    | TEST_SEL_1                             | GND 3.3V                                                                         |             |

|        |                                        | GND 3.3V                                                                         | (Default)   |

| J14    | FPGA Pull Up<br>Power Supply<br>Select | 2.5V 3.3V<br><b>1</b> 3 2                                                        | (Default)   |

|        |                                        | 2.5V 3.3V                                                                        |             |

| lumpor | Function           | Switch     | Description                                     |

|--------|--------------------|------------|-------------------------------------------------|

| Jumper | Function           | Positions  | Description                                     |

| J15    | FPGA<br>Connection |            | Default - Pins connected with zero ohm resistor |

|        |                    | <b>D D</b> | No connection between pins                      |

| J16    | FPGA<br>Connection | <b>[]</b>  | Pins connected with zero ohm resistor           |

|        |                    | •••        | Default - No connection between pins            |

| J17    | FPGA<br>Connection |            | Default - Pins connected with zero ohm resistor |

|        |                    | <b>D D</b> | No connection between pins                      |

| J18    | FPGA<br>Connection |            | Pins connected with zero ohm resistor           |

|        |                    | <b>D D</b> | Default - No connection between pins            |

Table 4-3. MAIN Board Jumpers J10 – J76 (continued)

| Jumper | Function                    | Switch<br>Positions | Description                                     |

|--------|-----------------------------|---------------------|-------------------------------------------------|

| J19    | FPGA<br>Connection          |                     | Pins connected with zero ohm resistor           |

|        |                             | <b>D</b>            | Default - No connection between pins            |

| J20    | JTAG Power<br>Supply Select | 2.5V 3.3V           | (Default)                                       |

|        |                             | 2.5V 3.3V           |                                                 |

| J21    | JTAG Connector              |                     | Default - Pins connected with zero ohm resistor |

|        |                             | <b>D</b>            | No connection between pins                      |

| J22    | JTAG Connector              |                     | Default - Pins connected with zero ohm resistor |

|        |                             |                     | No connection between pins                      |

|        |                             |                     |                                                 |

|        |                 | Courit - In                       |                                                 |

|--------|-----------------|-----------------------------------|-------------------------------------------------|

| Jumper | Function        | Switch<br>Positions               | Description                                     |

| J23    | JTAG Connector  |                                   | Default - Pins connected with zero ohm resistor |

|        |                 | •••                               | No connection between pins                      |

| J24    | JTAG Connector  |                                   | Default - Pins connected with zero ohm resistor |

|        |                 | <b>D D</b>                        | No connection between pins                      |

| J25    | HSWAP<br>ENABLE | 2.5V 3.3V<br>1 3 2                | (Default)                                       |

|        |                 | 2.5V 3.3V                         |                                                 |

| J26    | M66EN           | GND 3.3V                          |                                                 |

|        |                 | GND 3.3V<br><b>•</b> • •<br>1 3 2 | (Default)                                       |

| Jumper | Function                          | Switch<br>Positions | Description                                                                                          |

|--------|-----------------------------------|---------------------|------------------------------------------------------------------------------------------------------|

| J27    | PCI_IDSEL                         | AD29 GND<br>1 3 2   |                                                                                                      |

|        |                                   | AD29 GND<br>1 3 2   | Default                                                                                              |

| J28    | Power On Reset                    | AD29 GND            | Power On Reset pin is pulled up by 100 K $\!\Omega$ resistor.                                        |

|        |                                   | LVI GND<br>1 3 2    | Power On Reset pin is controlled by U7 -<br>MAX6714DUB Reset Supervisor Device.<br>(Default Setting) |

| J29    | RESET INPUT<br>for MAX6714<br>DUB |                     |                                                                                                      |

|        |                                   | • •                 | (Default Setting—no jumper)                                                                          |

| J30    |                                   |                     | CORALP device held in RESET condition.                                                               |

|        |                                   | D D                 | CORALP device controlled by Power On<br>Reset<br>(Default Setting—no jumper)                         |

| Cuitab                                    |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function                                  | Positions                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| INH pin on CAN<br>Driver of CAN1<br>(U15) |                                                                                                                    | Enable CAN Physical Interface Device<br>(U15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| (010)                                     |                                                                                                                    | Default Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                           |                                                                                                                    | CAN Physical Interface Device (U15) not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                           | •••                                                                                                                | (Zero ohm resistor removed.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| INH pin on CAN<br>Driver of CAN2          |                                                                                                                    | Enable CAN Physical Interface Device (U16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| (018)                                     |                                                                                                                    | Default Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                           |                                                                                                                    | CAN Physical Interface Device (U16) not enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                           | •••                                                                                                                | (Zero ohm resistor removed.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| USB MODE<br>Select (U18)                  | 3.3 V GND                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                           | 3.3 V GND                                                                                                          | Default Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| CFG2                                      | 3.3 V CFG2                                                                                                         | Pin 3 — LED_YEL_A<br>(J34 and J40 control CFG2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                           | 3.3 V CFG2                                                                                                         | Pin 3 — LED_YEL_A<br>(J34 and J40 control CFG2)<br>Default Setting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                           | INH pin on CAN<br>Driver of CAN1<br>(U15)<br>INH pin on CAN<br>Driver of CAN2<br>(U16)<br>USB MODE<br>Select (U18) | Positions         INH pin on CAN<br>Driver of CAN1<br>(U15)         INH pin on CAN<br>Driver of CAN2<br>(U16)         INH pin on CAN<br>Driver of CAN2<br>(U16)         USB MODE<br>Select (U18)         3.3 V         GND<br>I         3.3 V         GND<br>I         3.3 V         GND<br>I         3.3 V         GRD<br>I         I         3.3 V         GRD         I         3.3 V         GRD         I         3.3 V         GRD         I         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J         J |  |

| Table 4-3. MAIN Board Jumpers J10 – J76 (continued) |

|-----------------------------------------------------|

|-----------------------------------------------------|

| Jumper | Function                              | Switch<br>Positions | Description                |

|--------|---------------------------------------|---------------------|----------------------------|

| J35    | ETHERNET<br>DEVICE (U19)<br>SLEEP EN  |                     |                            |

|        |                                       | <b>D</b>            | Default setting            |

| J36    | ETHERNET<br>DEVICE (U19)<br>POWERDOWN | <b>[]</b>           |                            |

|        |                                       | <b>D</b>            | Default setting            |

| J37    | MDDIS<br>SETTING                      | GND 3.3V            |                            |

|        |                                       | GND 3.3V            | Default Setting            |

| J38    |                                       | 3.3 V GND<br>       |                            |

|        |                                       | 3.3 V GND<br>1 3 2  | TXSLEW1<br>Default setting |

Hardware Description

| Table 4-5. MAIN board bumpers 510 – 576 (continued) |          |                                                                                    |                                                                    |  |

|-----------------------------------------------------|----------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| Jumper                                              | Function | Switch<br>Positions                                                                | Description                                                        |  |

| J39                                                 |          | 3.3 V GND                                                                          |                                                                    |  |

|                                                     |          | 3.3 V GND                                                                          | TXSLEW0<br>Default Setting                                         |  |

| J40                                                 | CFG2     | CFG2 GND                                                                           | Pin 3 — LED_YEL_C<br>(J34 and J40 control CFG2)                    |  |

|                                                     | CFG2     | $\begin{array}{c} CFG2 & GND \\ \hline \bullet & \bullet \\ 1 & 3 & 2 \end{array}$ | Pin 3 — LED_YEL_C<br>(J34 and J40 control CFG2)<br>Default Setting |  |

| J41                                                 | PAUSE    |                                                                                    |                                                                    |  |

|                                                     |          | 3.3 V PAUSE                                                                        | Default Setting                                                    |  |

| J42                                                 | CFG1     | 3.3 V CFG1                                                                         | Pin 3 — LD5 GREEN<br>(J42 and J44 control CFG1)                    |  |

|                                                     |          | 3.3 V CFG1                                                                         | Pin 3 — LD5 GREEN<br>(J42 and J44 control CFG1)<br>Default Setting |  |

Table 4-3. MAIN Board Jumpers J10 – J76 (continued)

| Jumper | Function                                  | Switch<br>Positions                               | Description                                                        |

|--------|-------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------|

| J43    | CFG3                                      | 3.3 V CFG3                                        | Pin 3 — LED_GRN_A<br>(J43 and J45 control CFG3)                    |

|        |                                           | 3.3 V CFG3                                        | Pin 3 — LED_GRN_A<br>(J43 and J45 control CFG3)<br>Default Setting |

| J44    |                                           | CFG1 GND                                          | (J42 and J44 control CFG1)<br>Pin 3 — LD5 GREEN                    |

|        |                                           | CFG1 GND<br>• • • • • • • • • • • • • • • • • • • | (J42 and J44 control CFG1)<br>Pin 3 — LD5 GREEN<br>Default Setting |

| J45    |                                           | CFG3 GND                                          | Pin 3 — LED_GRN_C<br>(J43 and J45 control CFG3)                    |

|        |                                           | CFG3 GND                                          | Pin 3 — LED_GRN_C<br>(J43 and J45 control CFG3)<br>Default Setting |

| J46    | Vref for Touch<br>Screen Encoder<br>(U23) |                                                   | Power connected to Vref on U23<br>Default Setting                  |

|        |                                           | <b>D</b>                                          | Vref on U23 not powered                                            |

| Jumper | Function                                                    | Switch<br>Positions | Description                                                                                 |

|--------|-------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|

| J47    | Power<br>connection for<br>Touch Screen<br>Decoder          |                     | Connect power to DZ2<br>Default Setting                                                     |

|        |                                                             | ••                  | Power not connected to DZ2                                                                  |

| J48    | Voltage<br>reference for<br>Touch Screen<br>Decoder pin IN4 |                     | Connect regulated power from DZ2 to IN4<br>on Touch Screen Decoder (U23)<br>Default Setting |

|        |                                                             | •••                 | Regulated power from DZ2 not connected to IN4 on Touch Screen Decoder (U23)                 |

| J49    | FPGA_STAT0                                                  |                     | Connect FPGA_STAT0 pin to MINI PCI<br>Connector CN9                                         |

|        |                                                             | ••                  | Do not connect FPGA_STAT0 pin to MINI<br>PCI Connector CN9<br>Default Setting               |

| J50    | FPGA_STAT1                                                  |                     | Connect FPGA_STAT1 pin to MINI PCI<br>Connector CN9                                         |

|        |                                                             | <b>D</b>            | Do not connect FPGA_STAT1 pin to MINI<br>PCI Connector CN9<br>Default Setting               |

| Jumper | Function                    | Switch<br>Positions | Description                                                                   |

|--------|-----------------------------|---------------------|-------------------------------------------------------------------------------|

| J51    | FPGA_STAT2                  |                     | Connect FPGA_STAT2 pin to MINI PCI<br>Connector CN9                           |

|        |                             | <b>D</b>            | Do not connect FPGA_STAT2 pin to MINI<br>PCI Connector CN9<br>Default Setting |

| J52    | FPGA_STAT3                  |                     | Connect FPGA_STAT3 pin to MINI PCI<br>Connector CN9                           |

|        |                             |                     | Do not connect FPGA_STAT3 pin to MINI<br>PCI Connector CN9<br>Default Setting |

| J53    | PCI Connector<br>CLKRUN pin | 3.3V GND            | Default setting                                                               |

|        |                             | ••                  |                                                                               |

| J54    | FPGA_STAT4                  |                     | Connect FPGA_STAT4 pin to MINI PCI<br>Connector CN9                           |

|        |                             | ••                  | Do not connect FPGA_STAT4 pin to MINI<br>PCI Connector CN9<br>Default Setting |

| Jumper | Function                                          | Switch<br>Positions                              | Description                                                                           |

|--------|---------------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|

| J55    | FPGA_STAT5                                        |                                                  | Connect FPGA_STAT5 pin to MINI PCI<br>Connector CN9                                   |

|        |                                                   | ••                                               | Do not connect FPGA_STAT5 pin to MINI<br>PCI Connector CN9<br>Default Setting         |

| J56    | ATA Power<br>Select                               | 5V 3.3V<br>• • • • • • • • • • • • • • • • • • • | ATA Power Supply = 3.3V<br>(Pin 3 is connected to ATA Power Supply)                   |

|        |                                                   | 5V 3.3V<br>1 3 2                                 | ATA Power Supply = 5V<br>(Pin 3 is connected to ATA Power Supply)                     |

| J57    | AVF4910A<br>DVSUP pin<br>Voltage Supply<br>Select | 5V 3.3V                                          | DVSUP pin voltage = 3.3 Volts                                                         |

|        |                                                   | 5V 3.3V<br>• • • • • • • • • • • • • • • • • • • | ADVSUP pin voltage = 5 Volts<br>Default Setting                                       |

| J58    |                                                   | 5V 3.3V                                          | 1 - Vref_i of U29<br>2 - AVF_sync_AVSync<br>3 - D_CTR_I/O_0 of U29                    |

|        |                                                   | 5V 3.3V<br>• • • • • • • • • • • • • • • • • • • | 1 - Vref_i of U29<br>2 - AVF_sync_AVSync<br>3 - D_CTR_I/O_0 of U29<br>Default Setting |

| Jumper | Function                                                     | Switch<br>Positions          | Description                                                                    |  |

|--------|--------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------|--|

| J59    | CORAL P CLK<br>SEL 0                                         | 3.3V GND                     | CORAL P Clock Select<br>CLK SEL0                                               |  |

|        |                                                              | 3.3V GND<br>• • • •<br>1 3 2 | CORAL P Clock Select<br>CLK SEL0<br>default setting                            |  |

| J60    | CORAL P CLK<br>SEL 1                                         | GND 3.3V                     | CORAL P Clock Select<br>CLK SEL1                                               |  |

|        |                                                              | GND 3.3V                     | CORAL P Clock Select<br>CLK SEL1<br>default setting                            |  |

| J61    | CORAL P CLK<br>SEL 2                                         | GND 3.3V                     | CORAL P Clock Select<br>CLK MODE                                               |  |

|        |                                                              | GND 3.3V                     | CORAL P Clock Select<br>CLK MODE<br>default setting                            |  |

| J62    | 14.31818 MHz<br>Clock Device<br>(U33) Power<br>Supply Select | 3.3V 5V                      | 14.31818 MHz Clock Device (U33) Power<br>Supply = 5 Volts                      |  |

|        |                                                              | 3.3V 5V                      | 14.31818 MHz Clock Device (U33) Power<br>Supply = 3.3 Volts<br>Default Setting |  |

\_\_\_\_\_

| Jumper | Function                                    | Switch<br>Positions  | Description                                                                      |  |

|--------|---------------------------------------------|----------------------|----------------------------------------------------------------------------------|--|

| J63    | GPU_cntrl_CLO<br>CK inverter<br>select      |                      | 14.31818 Clock Driver U33 pin 3 is inverted and then drives GPU_cntrl_ CLOCK     |  |

|        | 361601                                      | 1 3 2                | pin 1 - U33 pin 3 OUT<br>pin 2 - U32 inverter output<br>pin 3 - GPU_cntrl_ CLOCK |  |

|        |                                             |                      | 14.31818 Clock Driver U33 pin 3 drives<br>GPU_cntrl_ CLOCK                       |  |

|        |                                             | <b>● ● ● ■</b> 1 3 2 | Pin 1 - U33 Pin 3 OUT<br>Pin 2 - U32 inverter output<br>Pin 3 - GPU_cntrl_ CLOCK |  |

|        |                                             |                      | Default Setting                                                                  |  |

| J64    | PD input of SIL<br>164 (U37)                | GND 3.3V             | PD input of SIL 164 (U37) is supplied by the 3.3 V DVI_D supply.                 |  |

|        |                                             | 1 3 2                |                                                                                  |  |

|        |                                             | GND 3.3V             | PD input of SIL 164 (U37) is connected to GND                                    |  |

|        |                                             | 1 3 2                | Default Setting                                                                  |  |

| J65    |                                             |                      | B and W pins of AD5246 (U38) are shorted together.                               |  |

|        |                                             |                      |                                                                                  |  |

|        |                                             |                      | B and W pins of AD5246 (U38) are not shorted together.                           |  |

|        |                                             | • •                  | Default Setting                                                                  |  |

| J66    | DPS pin on<br>LVDSConnector<br>CN15 voltage |                      | DPS input on Connector CN15 is connected to 3.3 volts.                           |  |

|        | select                                      |                      |                                                                                  |  |

|        |                                             |                      | DPS input on Connector CN15 is left floating                                     |  |

|        |                                             | •                    | Default Setting                                                                  |  |

| Jumper | Function                                           | Switch<br>Positions | Description                                                                         |

|--------|----------------------------------------------------|---------------------|-------------------------------------------------------------------------------------|

| J67    |                                                    | GND<br>1 3 2        | Pin 1 - gnd<br>Pin 2 - RGB_aV_VSYNC<br>Pin 3 - TxIN25 pin of U39                    |

|        |                                                    | GND<br>1 3 2        | Pin 1 - gnd<br>Pin 2 - RGB_sV_VSYNC<br>Pin 3 - TxIN25 pin of U39<br>Default Setting |

| J68    |                                                    | GND<br>1 3 2        | Pin 1 - GND<br>Pin 2 - RGB_sV_HSYNC<br>Pin 3 - TxIN24 pin of U39                    |

|        |                                                    | GND<br>1 3 2        | Pin 1 - GND<br>Pin 2 - RGB_sV_HSYNC<br>Pin 3 - TxIN24 pin of U39<br>Default Setting |

| J69    | R_FB pin of<br>DS90C383<br>(U39) voltage<br>select | 3.3 V GND           | Pin 3 - R_FB pin (U39) - GND                                                        |

|        |                                                    | 3.3V GND            | Pin 3 - R_FB pin (U39) - 3.3 V<br>Default Setting                                   |

| J70    | USB1T11ABQX<br>(U18) PAD pin<br>voltage select     |                     | PAD pin of U18 - GND                                                                |

|        |                                                    | •                   | PAD pin of U18 - no voltage applied<br>Default Setting                              |

| J71    | NOT USED                                           |                     | NOT USED                                                                            |

\_\_\_\_\_

|        | Switch                     |                       |                                                               |  |

|--------|----------------------------|-----------------------|---------------------------------------------------------------|--|

| Jumper | Function                   | Positions             | Description                                                   |  |

| J72    | NOT USED                   |                       | NOT USED                                                      |  |

|        |                            |                       |                                                               |  |

| J73    | NOT USED                   |                       | NOT USED                                                      |  |

|        |                            |                       |                                                               |  |

| J74    | DUART RESET<br>PIN control | POR POR_B             | DUART RESET pin controlled by the inversion of Power On Reset |  |

|        |                            | POR POR_B             | DUART RESET pin controlled by Power On Reset                  |  |

|        |                            | <b>● ● ● ■</b> 1 3 2  | (Default Setting)                                             |  |

| J75    | NC1 (no connect) pin of    |                       | Ground pin 12 (NC1) of Dual Uart (U14)                        |  |

|        | Dual UART                  | GND 3.3V              | Reserved for future use - do not populate.                    |  |

|        |                            | GND 3.3V              | Connect pin 12 (NC1) of Dual UART (U14) to 3.3 Volts.         |  |

|        |                            | <b>U U U</b><br>1 3 1 | Reserved for future use - do not populate.                    |  |

| J76    | NC2 (no connect) pin of    |                       | Ground pin 24(NC1) of Dual UART (U14)                         |  |

|        | Dual UART                  | GND 3.3V              | Reserved for future use - do not populate.                    |  |

|        |                            | GND 3.3V              | Connect pin 24 (NC1) of Dual UART (U14) to 3.3 Volts.         |  |

|        |                            | <b>U U U</b><br>1 3 1 | Reserved for future use - do not populate.                    |  |

### 4.2.3 MAIN Board Connectors

| Pin Name   | Pin |

|------------|-----|

| JTAG_TDO   | 1   |

| JTAG_TDI   | 3   |

| N.C.       | 5   |

| JTAG_TCK   | 7   |

| JTAG_TMS   | 9   |

| SRESET     | 11  |

| HRESET     | 13  |

| TEST_SEL_0 | 15  |

|            |     |

| Pin | Pin Name  |  |  |  |

|-----|-----------|--|--|--|

| 2   | N.C.      |  |  |  |

| 4   | JTAG_TRST |  |  |  |

| 6   | 3.3 VOLTS |  |  |  |

| 8   | N.C.      |  |  |  |

| 10  | N.C.      |  |  |  |

| 12  | GND       |  |  |  |

| 14  | N.C.      |  |  |  |

| 16  | GND       |  |  |  |

#### Table 4-4. MAIN Board Connector CN1 – COP

Table 4-5. MAIN Board Connector CN2- CAN1

| Pin Name | Pin |   | Pin | Pin Name |

|----------|-----|---|-----|----------|

| N.C.     | 1   |   |     |          |

| CANL     | 2   |   | 6   | N.C.     |

| GND      | 3   |   | 7   | CANH     |

| N.C.     | 4   |   | 8   | N.C.     |

| AC GND   | 5   |   | 9   | N.C.     |

|          |     |   |     |          |

|          |     | - |     |          |

| GND      | 10  |   |     |          |

| GND      | 11  |   |     |          |

| Pin Name      | Pin |   | Pin | Pin Name |

|---------------|-----|---|-----|----------|

| N.C.          | 1   |   |     |          |

| CANL          | 2   |   | 6   | N.C.     |

| GND           | 3   |   | 7   | CANH     |

| N.C.          | 4   |   | 8   | N.C.     |

| ANALOG GROUND | 5   |   | 9   | N.C.     |

|               |     |   |     |          |

|               |     |   |     |          |

| GND           | 10  |   |     |          |

| GND           | 11  | 1 |     |          |

#### Table 4-6. MAIN Board Connector CN3 – CAN2

| L | SHIELD 1 |  |

|---|----------|--|

|   |          |  |

| 1 | VBus     |  |

| 2 | D-       |  |

| 3 | D+       |  |

| 4 | GND      |  |

|   |          |  |

| R | SHIELD 2 |  |

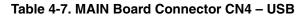

Table 4-8. MAIN Board Connector CN5 SPDIF IN

Pin

Function

1

GND

2

SPDIF\_DA\_INPUT

1

Optimized and the second and

#### Table 4-9. MAIN Board Connector CN6 SPDIF OUT

| PIN NAME | PIN |

|----------|-----|

| -12V     | B1  |

| ТСК      | B2  |

| GND0     | B3  |

| TDO      | B4  |

| +5V_1    | B5  |

| PIN | PIN NAME |  |

|-----|----------|--|

| A1  | TRST     |  |

| A2  | +12      |  |

| A3  | TMS      |  |

| A4  | TDI      |  |

| A5  | +5       |  |

Media5200 User's Guide, Rev. 0

| PIN NAME     | PIN |

|--------------|-----|

|              |     |

| +5V_2        | B6  |

| INTB         | B7  |

| INTD         | B8  |

| PRSNT1       | B9  |

| RESERVED1    | B10 |

| PRSNT2       | B11 |

|              | B12 |

|              | B13 |

| RESERVED 2   | B14 |

| GND1         | B15 |

| CLK          | B16 |

| GND2         | B17 |

| REQ          | B18 |

| 3.3V (I/O) 1 | B19 |

| AD31         | B20 |

| AD29         | B21 |

| GND19        | B22 |

| AD27         | B23 |

| AD25         | B24 |

| 3.3V_1       | B25 |

| C/BE3        | B26 |

| AD23         | B27 |

| GND20        | B28 |

| AD21         | B29 |

| AD19         | B30 |

| 3.3V_2       | B31 |

| AD17         | B32 |

| C/BE2        | B33 |

| GND3         | B34 |

| IRDY         | B35 |

| 3.3V_3       | B36 |

| DEVSEL       | B37 |

| GND4         | B38 |

| PIN | PIN NAME      |

|-----|---------------|

| A6  | INTA          |

| A7  | INTC          |

| A8  | +5V_5         |

| A9  | RESERVED3     |

| A10 | +3.3V (I/O)   |

| A11 | RESERVED 4    |

| A12 |               |

| A13 |               |

| A14 | +3.3V (AUX)   |

| A15 | RST           |

| A16 | +3.3V (I/O)_3 |

| A17 | GNT           |

| A18 | GND9          |

| A19 | PME           |

| A20 | AD30          |

| A21 | +3.3V (I/O)_7 |

| A22 | AD28          |

| A23 | AD26          |

| A24 | GND10         |

| A25 | AD24          |

| A26 | IDSEL         |

| A27 | +3.3V (I/O)_8 |

| A28 | AD22          |

| A29 | AD20          |

| A30 | GND11         |

| A31 | AD18          |

| A32 | AD16          |

| A33 | +3.3V (I/O) 9 |

| A34 | FRAME         |

| A35 | GND12         |

| A36 | TRDY          |

| A37 | GND13         |

| A38 | STOP          |

| PIN NAME     | PIN |

|--------------|-----|

| LOCK         | B39 |

| PERR         | B40 |

| 3.3V_4       | B41 |

| SERR         | B42 |

| 3.3V_5       | B43 |

| C/BE1        | B44 |

| AD14         | B45 |

| GND5         | B46 |

| AD12         | B47 |

| AD10         | B48 |

| M66EN        | B49 |

| GND6         | B50 |

| GND7         | B51 |

| AD08         | B52 |

| AD07         | B53 |

| 3.3V_6       | B54 |

| AD05         | B55 |

| AD03         | B56 |

| GND8         | B57 |

| AD01         | B58 |

| 3.3V_(I/O) 2 | B59 |

| ACK64        | B60 |

| +5V_3        | B61 |

| +5V_4        | B62 |

| PIN  | PIN NAME       |

|------|----------------|

| A39  | +3.3V (I/O) 10 |

| A40  | RESERVED 5     |

| A41  | RESERVED 6     |

| A42  | GND14          |

| A43  | PAR            |

| A44  | AD15           |

| A45  | +3.3V (I/O) 11 |

| A46  | AD13           |

| A47  | AD11           |

| A48  | GND15          |

| A49  | AD09           |

| A50  | GND16          |

| A51  | GND17          |

| A52  | C/BE0          |

| BA53 | +3.3V (I/O)_12 |

| A54  | AD06           |

| A55  | AD04           |

| A56  | GND18          |

| A57  | AD02           |

| A58  | AD00           |

| A59  | +3.3V (I/O) 4  |

| A60  | REQ64          |

| A61  | +5V_6          |

| A62  | +5V_7          |

# Table 4-10. MAIN Board Connector CN7 PCI 1 (continued)

| PIN NAME     | PIN |

|--------------|-----|

| -12V         | B1  |

| ТСК          | B2  |

| GND0         | B3  |

| TDO          | B4  |

| +5V_1        | B5  |

| +5V_2        | B6  |

| INTB         | B7  |

| INTD         | B8  |

| PRSNT1       | B9  |

| RESERVED1    | B10 |

| PRSNT2       | B11 |

|              | B12 |

|              | B13 |

| RESERVED 2   | B14 |

| GND1         | B15 |

| CLK          | B16 |

| GND2         | B17 |

| REQ          | B18 |

| 3.3V (I/O) 1 | B19 |

| AD31         | B20 |

| AD29         | B21 |

| GND19        | B22 |

| AD27         | B23 |

| AD25         | B24 |

| 3.3V_1       | B25 |

| C/BE3        | B26 |

| AD23         | B27 |

| GND20        | B28 |

| AD21         | B29 |

| AD19         | B30 |

| 3.3V_2       | B31 |

| AD17         | B32 |

# Table 4-11. MAIN Board Connector C87 PCI 2

| PIN | PIN NAME      |

|-----|---------------|

| A1  | TRST          |

| A2  | +12           |

| A3  | TMS           |

| A4  | TDI           |

| A5  | +5            |

| A6  | INTA          |

| A7  | INTC          |

| A8  | +5V_5         |

| A9  | RESERVED3     |

| A10 | +3.3V (I/O)   |

| A11 | RESERVED 4    |

| A12 |               |

| A13 |               |

| A14 | +3.3V (AUX)   |

| A15 | RST           |

| A16 | +3.3V (I/O)_3 |

| A17 | GNT           |

| A18 | GND9          |

| A19 | PME           |

| A20 | AD30          |

| A21 | +3.3V (I/O)_7 |

| A22 | AD28          |