# SmartDSP Operating System

# **User Guide**

Revised: November 23, 2015

Freescale, the Freescale logo, CodeWarrior, PowerQUICC, QorIQ, Qorivva, StarCore are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. QorIQ Qonverge, QUICC Engine are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2009-2015 Freescale Semiconductor, Inc. All rights reserved.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

### How to Contact Us

| Corporate Headquarters | Freescale Semiconductor, Inc.        |  |

|------------------------|--------------------------------------|--|

|                        | 6501 William Cannon Drive West       |  |

|                        | Austin, TX 78735                     |  |

|                        | U.S.A.                               |  |

| World Wide Web         | http://www.freescale.com/codewarrior |  |

| Technical Support      | http://www.freescale.com/support     |  |

### 1 Introduction

| 1.1 Features                    |

|---------------------------------|

| 1.2 Architecture                |

| 1.2.1 Platforms                 |

| 1.2.2 Kernel                    |

| 1.2.3 Drivers                   |

| 1.2.4 Utilities                 |

| 1.3 Directory Structure         |

| 1.4 Initialization and Start Up |

| 1.5 SmartDSP OS Linker          |

| 1.5.1 Initialization            |

| 1.5.2 Guidelines                |

| 1.6 Accompanying Documentation  |

| 1.7 More About SmartDSP OS      |

### 2 Kernel Components

| 2.1 Interrupts                   | 22 |

|----------------------------------|----|

| 2.1.1 Interrupt Sources          |    |

| 2.1.2 Interrupt Types            | 23 |

| 2.2 Scheduler                    |    |

| 2.3 Tasks                        | 29 |

| 2.3.1 Task States                | 34 |

| 2.3.2 Background Task            | 35 |

| 2.4 Spinlocks                    | 36 |

| 2.5 Memory Manager               | 37 |

| 2.5.1 Memory Allocation          | 39 |

| 2.5.2 Buffer Management          | 41 |

| 2.6 Memory Management Unit (MMU) | 14 |

| 2.6.1 MMU Features               | 14 |

| 2.6.2 MMU Segment                | 45 |

| 2.6.3 MMU Context                |    |

| 2.6.4 MMU Configuration          | 18 |

9

21

| 2.6.5 MMU Exceptions                                              |

|-------------------------------------------------------------------|

| 2.7 Caches                                                        |

| 2.7.1 Cache Sweep Commands                                        |

| 2.7.2 Configuration of Caches in SmartDSP OS                      |

| 2.8 Queues                                                        |

| 2.9 Multicore Programmable Interrupt Controller (MPIC)            |

| 2.9.1 Features                                                    |

| 2.9.2 Programming Models                                          |

| 2.9.3 Example Calling Sequence                                    |

| 2.9.4 Specific Functionalities                                    |

| 2.9.5 Demo Use Cases                                              |

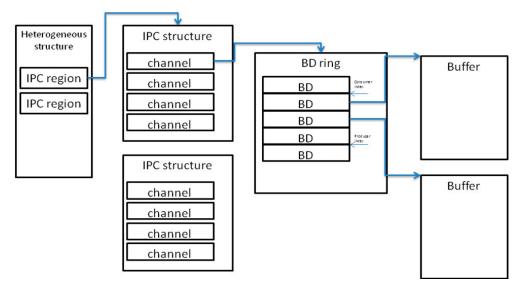

| 2.10 Inter Process Communication (IPC)                            |

| 2.10.1 Functional Specifications                                  |

| 2.10.2 Initialization                                             |

| 2.10.3 Runtime                                                    |

| 2.10.4 Functional Details: Design Concepts                        |

| 2.10.5 Initialization API                                         |

| 2.10.6 Runtime API to Application                                 |

| 2.10.7 IPC Functions                                              |

| 2.10.8 Initialization API Flow                                    |

| 2.10.9 Runtime API Flow                                           |

| 2.11 Intercore Messaging                                          |

| 2.11.1 Configuration of Intercore Messaging                       |

| 2.12 Intercore Message Queues                                     |

| 2.12.1 Configuration of Intercore Message Queues in SmartDSP OS72 |

| 2.12.2 Intercore Options                                          |

| 2.13 Events                                                       |

| 2.13.1 Event Semaphores                                           |

| 2.13.2 Event Queues                                               |

| 2.14 OS Tick Timers                                               |

| 2.14.1 Configuration of OS Tick Timers                            |

| 2.15 Software Timers                                              |

| 2.15.1 Configuration of Software Timers                           |

| 2.16 Hardware Timers                                              |

| 2.16.1 Configuration of Hardware Timers                           |

| 2.17 Debug and Trace Unit (DTU)85                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.17.1 Features                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.17.2 Programming Model                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.17.3 Example Calling Sequence                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.17.4 Specific Functionalities                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.17.5 Reading a Counted Value                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.17.6 Resetting the DTU                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.17.7 Demo Use Cases                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.18 B4860 L1-Defense                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.18.1 Functionality                                                                                                                                                                                                                                                                                                                                                                                                     |

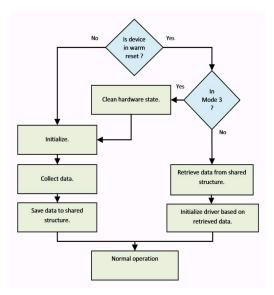

| 2.18.2 Application operation after warm reset                                                                                                                                                                                                                                                                                                                                                                            |

| 2.18.3 Configuration of L1-Defense                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.18.4 Source Code                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.18.5 Demo Use Cases                                                                                                                                                                                                                                                                                                                                                                                                    |

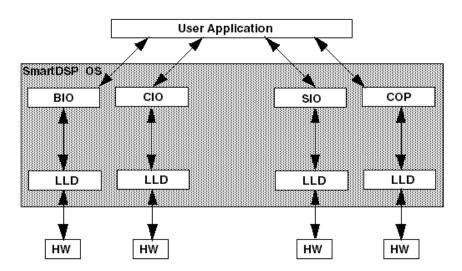

| 3 Hardware Abstraction Layers (HAL) 95                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1 HAL in SmartDSP OS95                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1.1 Conceptual Model                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1.1 Conceptual Model                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.1.1 Conceptual Model                                                                                                                                                                                                                                                                                                                                                                                                   |

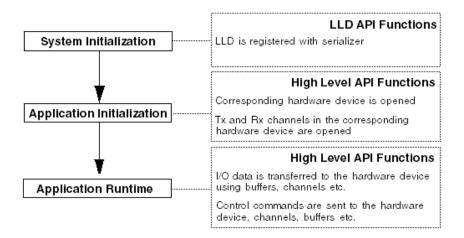

| 3.1.2 Conceptual Workflow                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1.2 Conceptual Workflow                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1.2 Conceptual Workflow                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow98                                                                                                                                                                                                                                                                                                          |

| 3.1.2 Conceptual Workflow                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module101                                                                                                                                                                                                                                              |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers101                                                                                                                                                                                                                           |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow102                                                                                                                                                                                       |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow103                                                                                                                                                          |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers.983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow1033.4 Synchronized I/O (SIO) Module103                                                                                                                     |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers.983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow.1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow1023.4 Synchronized I/O (SIO) Module1033.4.1 SIO Layers103                                                                                                 |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers.983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow1033.4 Synchronized I/O (SIO) Module1033.4.1 SIO Layers1033.4.2 SIO Initialization Workflow104                                                              |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers.983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow1033.4 Synchronized I/O (SIO) Module1033.4.1 SIO Layers1033.4.2 SIO Initialization Workflow1043.4.3 SIO Runtime Workflow104                                 |

| 3.1.2 Conceptual Workflow973.2 Buffered I/O (BIO) Module973.2.1 BIO Layers983.2.2 BIO Initialization Workflow983.2.3 BIO Runtime Workflow1003.3 Coprocessor (COP) Module1013.3.1 COP Layers1013.3.2 COP Initialization Workflow1023.3.3 COP Runtime Workflow1033.4 Synchronized I/O (SIO) Module1033.4.1 SIO Layers1033.4.2 SIO Initialization Workflow1043.4.3 SIO Runtime Workflow1053.5 Character I/O (CIO) Module106 |

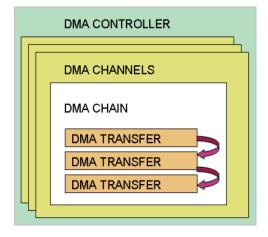

| 4 | Drivers                               | 111 |

|---|---------------------------------------|-----|

|   | 4.1 Direct Memory Access (System DMA) |     |

|   | 4.1.1 Features                        | 112 |

|   | 4.1.2 Architecture                    |     |

|   | 4.1.3 Data Flow                       |     |

|   | 4.1.4 Programming Model               | 115 |

|   | 4.1.5 Resource Management             |     |

|   | 4.1.6 Demo Use Cases.                 |     |

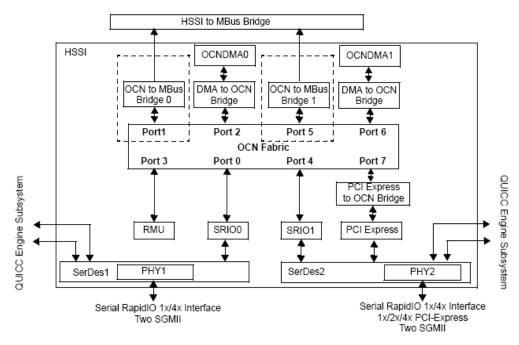

|   | 4.2 OCeaN DMA                         |     |

|   | 4.2.1 Features                        |     |

|   | 4.2.2 Architecture                    |     |

|   | 4.2.3 Demo Use Cases                  |     |

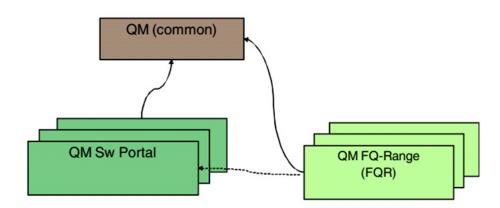

|   | 4.3 Queue Manager (QMAN)              |     |

|   | 4.3.1 Introduction                    |     |

|   | 4.3.2 Functionality.                  |     |

|   | 4.3.3 Functionality.                  | 135 |

|   | 4.3.4 Driver Architecture.            | 135 |

|   | 4.3.5 Programming Model               | 137 |

|   | 4.3.6 Demo Use Cases.                 | 139 |

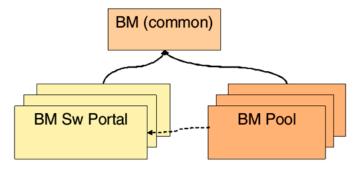

|   | 4.4 Buffer Manager (BMAN)             | 139 |

|   | 4.4.1 Introduction                    | 139 |

|   | 4.4.2 Functionality                   |     |

|   | 4.4.3 BMan's Interfaces.              |     |

|   | 4.4.4 Driver Architecture.            |     |

|   | 4.4.5 Programming Model               |     |

|   | 4.4.6 Source code                     |     |

|   | 4.4.7 Demo Use Cases.                 |     |

|   | 4.5 Serial RapidIO (sRIO)             |     |

|   | 4.5.1 Introduction                    |     |

|   | 4.5.2 Features                        |     |

|   | 4.5.3 Architecture                    |     |

|   | 4.5.4 Data Flow                       |     |

|   | 4.5.5 Programming Model               |     |

|   | 4.5.6 Resource Management             | 152 |

| 4.5.7 Demo Use Cases                                           |     |

|----------------------------------------------------------------|-----|

| 4.5.8 Resource Management                                      | 153 |

| 4.5.9 Demo Use Cases                                           | 153 |

| 4.6 Multi Accelerator Platform Engine–Baseband (MAPLE–B/B2/B3) | 153 |

| 4.6.1 Introduction                                             | 153 |

| 4.6.2 Features                                                 | 153 |

| 4.6.3 Architecture                                             | 154 |

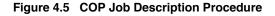

| 4.6.4 Data Flow                                                | 155 |

| 4.6.5 Programming Model                                        | 158 |

| 4.6.6 Demo Use Cases                                           |     |

| 4.7 Common Protocol Radio Interface (CPRI)                     |     |

| 4.7.1 Introduction                                             | 168 |

| 4.7.2 Features                                                 |     |

| 4.7.3 Relevant SoC                                             |     |

| 4.7.4 Architecture                                             | 170 |

| 4.7.5 Components                                               |     |

| 4.7.6 Design Decisions                                         |     |

| 4.7.7 Reconfiguration                                          |     |

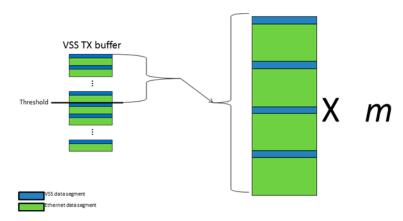

| 4.7.8 CPRI Ethernet Errata A-007968 Workaround                 |     |

| 4.7.9 Programming Model                                        | 178 |

| 4.7.10 CPRI API                                                | 179 |

| 4.7.11 Demo Use Cases                                          |     |

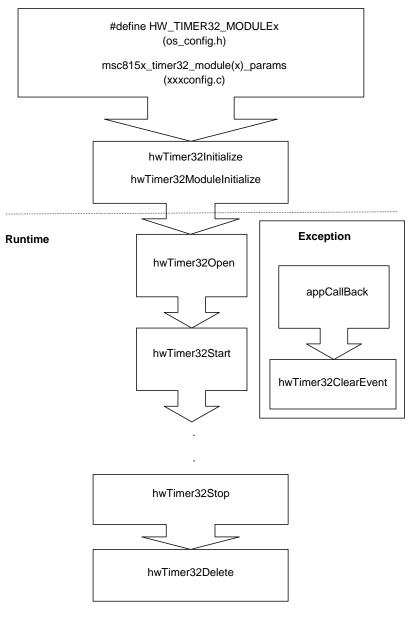

| 4.8 HW_Timer32                                                 |     |

| 4.8.1 Introduction                                             |     |

| 4.8.2 Features                                                 |     |

| 4.8.3 Architecture                                             |     |

| 4.8.4 Programming Model                                        | 190 |

| 4.8.5 Demo Use Cases                                           |     |

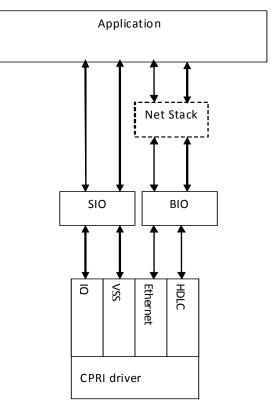

| 4.9 Antenna Interface Controller (AIC)                         |     |

| 4.9.1 Introduction                                             |     |

| 4.9.2 Features                                                 |     |

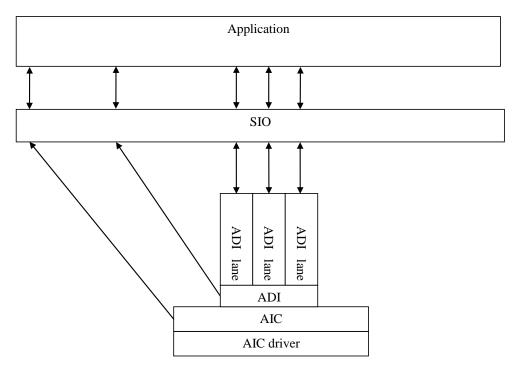

| 4.9.3 Architecture                                             |     |

| 4.9.4 Data Flow                                                | 198 |

| 4.9.5 Programming Model                                        |     |

| 4.9.6 Appendix: References                                     |     |

|                                                                |     |

| 4.10 SmartDSP OS Recovery Support                 |     |

|---------------------------------------------------|-----|

| 4.10.1 Features                                   |     |

| 4.10.2 Architecture                               | 205 |

| 4.10.3 Data Flow                                  | 206 |

| 4.10.4 Programming Model                          | 206 |

| 4.10.5 Demo Use Cases                             |     |

| 4.11 Enhanced Serial Peripheral Interface (eSPI). |     |

| 4.11.1 Introduction                               | 209 |

| 4.11.2 Features                                   | 209 |

| 4.11.3 Architecture                               | 209 |

| 4.11.4 Data Flow                                  |     |

| 4.11.5 Programming Model                          |     |

| 4.11.6 Resource Management                        |     |

| 4.11.7 Demo Use Cases.                            |     |

| 4.11.8 Appendix: References                       |     |

|                                                   | 017 |

### A Using C++ with SmartDSP OS

### Index

217

219

1

# Introduction

The SmartDSP Operating System (OS) is a Real Time Operating System (RTOS) that runs on the following StarCore DSP-based processors:

- B4860

- PSC9131

- PSC9132

- MSC815x/MSC825x

- MSC814x

- MSC812x

- MSC8101

The StarCore CodeWarrior (CW) Development Studio includes SmartDSP OS royalty-free source code. Further, SmartDSP OS has a high-level Application Programming Interface (API) that lets users develop integrated applications for StarCore processors.

This chapter provides information about SmartDSP OS—its features, architecture, startup processes and more.

- <u>1.1 Features</u>

- <u>1.2 Architecture</u>

- <u>1.3 Directory Structure</u>

- <u>1.4 Initialization and Start Up</u>

- 1.5 SmartDSP OS Linker

- <u>1.6 Accompanying Documentation</u>

- <u>1.7 More About SmartDSP OS</u>

### 1.1 Features

In SmartDSP OS, most functions are written in ANSI C. However, when needed, Assembly optimizes time-critical functions by maximizing StarCore's multiple execution units.

Other SmartDSP OS features include the following:

- · small memory footprint ideal for high-speed StarCore processors

- priority-based event-driven scheduling (triggered by user applications or HW)

### Introduction

Architecture

- dual-stack pointer for exception and task handling

- · inter-task and inter-core communication using queues, semaphores, and events.

# 1.2 Architecture

SmartDSP OS design is Cooperative Asymmetric Multi-Processing (CAMP)-based:

- cores run their own OS instances; and,

- OS manages shared resources and supports inter-core communication.

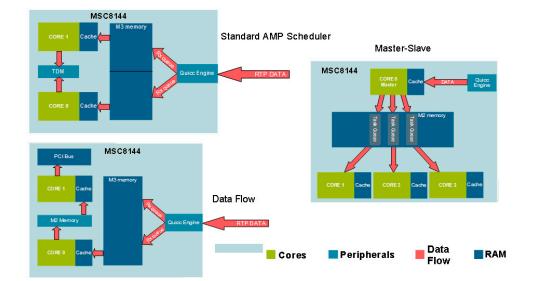

SmartDSP OS also provides an SMP scheduler for MSC814x and MSC815x architectures.

The following sections explain different components of SmartDSP OS architecture:

- 1.2.1 Platforms

- <u>1.2.2 Kernel</u>

- <u>1.2.3 Drivers</u>

- <u>1.2.4 Utilities</u>

### 1.2.1 Platforms

Table 1.1 lists SmartDSP OS-supported platforms.

Table 1.1 SmartDSP OS-supported Platforms

| Platform        | Specific Targets                                                                                                                |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| B4860           | • B4860                                                                                                                         |

| PSC9131/PSC9132 | • PSC9x31, PSC9x32                                                                                                              |

| MSC815x/MSC825x | <ul> <li>MSC8158/MSC8157</li> <li>MSC8156/MSC8154/MSC8152/<br/>MSC8151</li> <li>MSC8256/MSC8524/MSC8252/<br/>MSC8251</li> </ul> |

| MSC814x         | <ul><li>MSC8144</li><li>MSC8144E</li><li>MSC8144EC</li></ul>                                                                    |

| MSC812x         | <ul> <li>MSC8122</li> <li>MSC8126</li> <li>MSC8102</li> </ul>                                                                   |

#### Table 1.1 SmartDSP OS-supported Platforms

| Platform | Specific Targets |

|----------|------------------|

| MSC810x  | • MSC8101        |

|          | • MSC8103        |

### 1.2.2 Kernel

The SmartDSP OS kernel is well-suited for multi-core processors and applications. The kernel has these features:

- · supports HW and SW interrupts

- · supports spinlocks to protect critical multicore data

- · allows user-defined interrupt handlers

- Memory Management Unit (MMU) supports HW memory protection

SmartDSP OS kernel components:

- Caches

- Hardware Abstraction Layer (HAL)

- · Inter-core messaging

- Interrupts (HW, SW, and virtual)

- MMU

- Memory Manager

- · Message and event queues

- Scheduler

- · Semaphores

- Spinlocks

- SW and HW timers

- Tasks

## 1.2.3 Drivers

The SmartDSP OS provides a unified cross-device API<sup>1</sup> for the support of generic HW drivers. Further, it supports drivers providing HW support for relevant Systems-on-a- Chip (SoC):

<sup>1</sup>.See the SmartDSP OS API Reference Manual for more information.

### Introduction

#### Architecture

- Direct Memory Access (DMA)

- On-chip Network DMA (OCeaN DMA)

- Ethernet

- TSEC

- Quick Engine (UEC)

- Serial Rapid Input/Output (sRIO)

- RIONET

- Doorbells

- eMSG

- PCI Express (PEX)

- MAPLE

- Time Division Multiplexing (TDM)

- I<sup>2</sup>C or Generic I<sup>2</sup>C

- SPI or Generic SPI

- Universal Asynchronous Receiver/Transmitter (UART)

- CPRI

- AIC

- SEC

- HW\_Timers

- **NOTE** An SoC is an integrated circuit (IC) containing a core processor, special function processors, multiple memories and buses, standards-based peripherals, custom logic, and mixed-signal components. Together, these features communicate over a dedicated communication infrastructure.

## 1.2.4 Utilities

The SmartDSP OS provides utilities used to develop applications for StarCore processors:

### Table 1.2 Utilities

| Utility                 | Function                                                     |

|-------------------------|--------------------------------------------------------------|

| Configuration tool      | Configures SmartDSP OS (os_config.h).                        |

| UDP/IP packet generator | Create UDP/IP random packets (with customizable parameters). |

### Table 1.2 Utilities

| Utility                                                            | Function                                          |

|--------------------------------------------------------------------|---------------------------------------------------|

| SRTP client/server                                                 |                                                   |

| MJPEG player                                                       | Supports motion JPEG modules.                     |

| RTP player                                                         | Support RTP modules.                              |

| SmartDSP Host Exchange over Asynchronous<br>Transfer (HEAT) server | Supports Ethernet remote file access.             |

| CommExpert                                                         | Generates initialization code for supported DSPs. |

### Introduction

Directory Structure

# **1.3 Directory Structure**

The SmartDSP OS is part of the StarCore CodeWarrior Development Studio and is found in the directory, \StarCore\_Support\SmartDSP.

Table 1.3 lists SmartDSP subdirectories.

Table 1.3 SmartDSP Subdirectories

| Subdirectory   | Content                                                    |  |

|----------------|------------------------------------------------------------|--|

| demos          | Sample projects for supported platforms.                   |  |

| drivers        | C source and header files for compiling a driver library.  |  |

| include        | C header files used by SmartDSP OS components.             |  |

| initialization | C source and header files used for OS initialization.      |  |

| lib            | Compiled libraries used by SmartDSP OS components.         |  |

| source         | C source and header files for building compiled libraries. |  |

| tools          | Utilities provided by SmartDSP OS,                         |  |

| doc            | OS documentation files and device-specific documentation.  |  |

# 1.4 Initialization and Start Up

The SmartDSP OS uses a specified sequence of function calls during initialization.

### Table 1.4

| Initialization Stage       | Description                                                                                                                           |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Environment Initialization | 1. CW startup file begins execution.                                                                                                  |  |

|                            | 2. Calls SmartDSP OS hooks, global variables, and MMU.                                                                                |  |

|                            | 3. Jumps to application's main() function.                                                                                            |  |

|                            | <ul> <li>Based on the SmartDSP OS option,<br/>select from the Build Settings page (see<br/><u>Figure 1.1</u>).</li> </ul>             |  |

|                            | <ul> <li>SmartDSP OS linker files are included<br/>in a project. See <u>1.5.1 Initialization</u> for<br/>more information.</li> </ul> |  |

| SmartDSP OS Initialization | Main() function calls osInitialize() function.                                                                                        |  |

| Application Initialization | Main() function initializes user application.                                                                                         |  |

|                            | <ul> <li>Sample applications, under the demo<br/>directory, use applnit().</li> </ul>                                                 |  |

| Application Startup        | Main() function starts user application.                                                                                              |  |

|                            | <ul> <li>Creates background task in osStart()<br/>function.</li> </ul>                                                                |  |

|                            | <ul> <li>Switches to pending task with the<br/>highest priority.</li> </ul>                                                           |  |

### Introduction

Initialization and Start Up

### Figure 1.1 Build Settings Page

# 1.5 SmartDSP OS Linker

This section details <u>1.5.1 Initialization</u> and <u>1.5.2 Guidelines</u>.

# 1.5.1 Initialization

The **Build Settings** stage (Figure 1.1) of environment initialization offers Yes and No options.

- No: Activates StarCore sc3000-ld linker<sup>1</sup>.

- Yes: Below noted linker files will be included in the application.

#### Table 1.5

| File Type                        | Linker Files                          | Description                                  |  |

|----------------------------------|---------------------------------------|----------------------------------------------|--|

| Application-dependant            | <pre>memory_map_link.l3k</pre>        | Splits memory into local/shared regions.     |  |

|                                  | local_map_link.13k                    | Maps local sections to the memory.           |  |

|                                  | os_msc815x_link.l3k                   | Primary application-dependent file.          |  |

| SmartDSP OS MSC815x-<br>specific | os_msc815x_link_mmu_def<br>ines.13k   | SC3850 MMU attribute definitions             |  |

|                                  | os_msc815x_link_defines<br>.l3k       | MSC815x internal memory map                  |  |

|                                  | os_msc815x_link_app.13k               | SmartDSP OS segment<br>attribute definitions |  |

|                                  | os_msc8156_linker_ads_d<br>efines.l3k | ADS (DDR) memory map                         |  |

NOTE See the following guides for information on linker error messages and troubleshooting: - StarCore SC3000 Linker User Guide for sc3000-ld linker (.13k) - StarCore SC100 Linker User Guide for sc100-ld linker (.lcf)

<sup>1.</sup>For more information see *StarCore SC3000 Linker User Guide*.

Introduction

SmartDSP OS Linker

# 1.5.2 Guidelines

This section lists guidelines for using StarCore Linker:

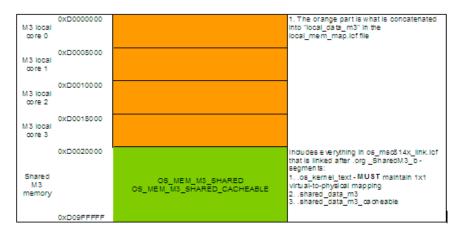

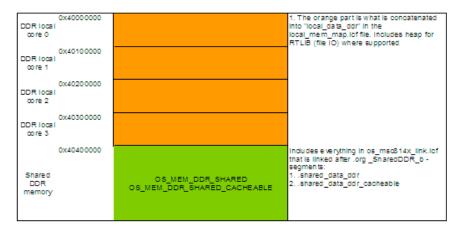

- 1. Consider the following if modifying the physical location of local and shared data.

- a. Consider performance issues; e.g., local\_non\_cacheable is currently in M2 memory.

- b. Check that program sections—used during initialization (before and during MMU programming)—maintain 1x1 virtual-to-physical mapping.

- c. Ensure that the segments .att\_mmu, .oskernel\_local\_data, and .oskernel\_local\_data\_bss are all local per core and confined by symbols \_VirtLocalData\_b, \_LocalData\_size, and \_LocalData\_b (memory\_map\_link.l3k). Symbols initialize the MMU and the stack thus enabling C code to run properly.

- 2. Consider the following if there is insufficient space in a specific memory location.

- a. Check if all allocated space is truly required.

- b. Check if there is a memory space or MMU alignment issue.

Re-align MMU by modifying the linker command file such that larger sections/segments link first; this provides better aligned base addresses.

- c. Check if memory is truly lacking. If so, move non-critical portions to a distant memory.

- 3. SmartDSP OS uses on-chip memory by default.

- DDR is not essential on a board.

- If necessary, a portion of the OS can be moved to the DDR.

- 4. Changes to the linker command file:

- If the debugger is still unable to reach the main () function, then there may be an issue of insufficient space at a specific memory location.

- 5. Memory allocated from a SmartDSP OS-managed heap:

- May provide better linking flexibility.

- 6. Global variables:

- If not set in a specific section then they will be placed in . data or .  $\tt bss.$

- 7. Asymmetric linking (supporting device):

- Allows symbols to be linked to sections yet unmapped by all cores.

- · Allows cores to link symbols to different physical memories and/or implementations

# **1.6 Accompanying Documentation**

The Documentation page describes the documentation included in this version of CodeWarrior Development Studio for StarCore DSP Architectures. You access the Documentation page by:

- a shortcut link on the Desktop that the CodeWarrior installer creates by default, or

- opening START\_HERE.html in CWInstallDir\SC\Help.

# 1.7 More About SmartDSP OS

SmartDSP is the chosen OS for Freescale's highly optimized SW libraries—libraries supporting baseband, video, voice and other DSP applications.

Freescale and its SW partners—by offering a wide variety of SW libraries optimized on FSL's DSP platforms—enable efficient product development. The SW libraries support both up-to-date and legacy voice and video codecs.

Included in the SW libraries are optimized baseband kernel libraries. SmartDSP OS is based on optimized kernels; their unique FSL DSP capabilities enable users to develop highly effective SW applications.

All DSP libraries are implemented on SmartDSP OS—to make use of its rich feature set while maintaining expected levels of efficiency and performance.

For more information on Freescale DSP SW libraries, visit www.freescale.com\dsp.

Introduction More About SmartDSP OS

An OS kernel is an interface between user applications and HW components. The SmartDSP OS kernel has these features:

- Predictable and realtime oriented as it is comprised of a preemptive, priority-based, single core with an event-driven scheduler.

- · Provides interrupt handling, memory management, and task scheduling.

- Allows both user and OS code to be executed in HW and SW interrupts, and tasks.

- Supports a dual-stack pointer-it uses both exception and normal stack StarCore pointer registers.

- Supports multi-core by executing an SDOS instantiation on each core and allowing inter-core communication and synchronization.

- · Provides an API and functionality for most DSP core and DSP subsystem components.

This chapter details the following SmartDSP OS kernel components.

- <u>2.1 Interrupts</u>

- 2.2 Scheduler

- <u>2.3 Tasks</u>

- <u>2.4 Spinlocks</u>

- 2.5 Memory Manager

- 2.6 Memory Management Unit (MMU)

- <u>2.7 Caches</u>

- <u>2.8 Queues</u>

- 2.9 Multicore Programmable Interrupt Controller (MPIC)

- 2.10 Inter Process Communication (IPC)

- 2.11 Intercore Messaging

- <u>2.12 Intercore Message Queues</u>

- <u>2.13 Events</u>

- 2.14 OS Tick Timers

- 2.15 Software Timers

- 2.16 Hardware Timers

- 2.17 Debug and Trace Unit (DTU)

Interrupts

• <u>2.18 B4860 L1-Defense</u>

### 2.1 Interrupts

An interrupt triggers a new event while an interrupt handler executes and services an interrupt request. An SoC can have multiple levels of interrupt concentrators; the kernel program them during application bring-up and runtime. For example,

- MSC8101, MSC812x GIC, LIC, and PIC

- MSC814x, MSC815x, PSC9x3x, B4860 GCR and EPIC

SmartDSP OS uses the ESP stack pointer for interrupt handling.

SC processor interrupts are either MI or NMI:

- MI

- Application can ignore the interrupt request.

- Priorities can vary between interrupt sources.

- NMI

- Interrupt request is critical.

- Interrupt handler must execute.

Consider the following SC interrupt characteristics:

- StarCore SR calls osStart() from main() to enable interrupts.

- User NMI ISR should not call OS functions guarded by disabling and enabling interrupts; e.g., osHwiSwiftDisable() and osHwiSwiftEnable().

- Prevents data or code corruption.

- Based on the broken assumption of atomicity in these code portions—a false assumption in NMI.

### 2.1.1 Interrupt Sources

SmartDSP OS interrupts are primarily generated from a single origin. MSC814x interrupt sources include the following:

- SC3400 core includes trap-generated interrupts (used for SW interrupts), illegal instructions, and debug exceptions.

- DSP subsystem includes MMU, cache, and timer interrupts.

**NOTE** Ensure that SoC-level NMIs, such as NMI\_B and virtual NMIs, are NOT triggered during kernel initialization [prior to calling osStart()].

• DSP SoC includes peripheral-generated interrupts, VIRQ, and external interrupts lines.

# 2.1.2 Interrupt Types

SmartDSP OS kernel supports HWI and SWI interrupts.

# 2.1.2.1 Hardware Interrupts

HW devices such as DMA, OCeaN DMA, and Ethernet controllers can generate HW interrupts. In SmartDSP OS kernel, the OS interrupt dispatcher handles HW interrupts in one of these ways:

- Calls an OS interrupt handler.

- Calls an OS interrupt handler before the interrupt calls a user-defined interrupt handler.

- Calls a user-defined interrupt handler.

HW interrupt characteristics include the following:

- Every interrupt handler should return void, and receive a single parameter.

- The received parameter is part of the interrupt registration; it is set at registration time.

- The parameter can act as a global variable pointer; the variable may change over the course of an application.

- Application-provided interrupt handles must be given a HW interrupt function; this is allocated upon registering the HW interrupt handle.

- HW interrupt prototype function: typedef void (\*os\_hwi\_function)(os\_hwi\_arg).

- HW interrupts are HW platform-specific thus SmartDSP OS kernel contains header files specific to given HW platforms. For example,

- msc814x\_hwi.h header file defines HW interrupts for the MSC814x platform.

- msc815x\_hwi.h header file defines HW interrupts for the MSC815x platform.

SmartDSP OS kernel features include the following:

- Supports edge and level HW interrupts.

- MMU exception interrupts are hardwired for edge mode.

- An application can define edge and level HW interrupts as follows:

- #define LEVEL\_MODE

- #define EDGE\_MODE

- Enables high priority interrupt handlers to finish before low priority interrupt handlers begin executing.

Interrupts

- Respectively, parameters OS\_HWI\_PRIORITY0 and OS\_HWI\_LAST\_PRIORITY specify the highest and lowest priority for HW interrupts.

- Number of priorities depends on PIC or EPIC.

- Interrupt controller is located in the DSP subsystem of these processors:

- MSC8101, MSC812x PIC

- MSC814x, MSC815x, PSC9x3x, B4860 EPIC

- Maximum number of HW interrupt priorities:

- SC140-based SoC = 7

- SC3400/SC3850-based SoC = 31

- See SC3850/SC3400/SC3900 DSP Core Reference Manual.

Table 2.1 lists SmartDSP OS HW interrupt module functions.

#### Table 2.1 Functions Available for Hardware Interrupts

| Flow State                                                                                                                                                                                                                              | Name              | Description                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Kernel bring up (the user<br>application does not call these<br>functions specifically. Instead,<br>osInitialize() calls these<br>functions based on the<br>parameters from os_config.h<br>and configurations from<br>msc81xx_config.c) | osHwiInitialize() | Initializes all interrupt handlers<br>to default ones and enables all<br>NMI in EPIC (where supported).                                                        |

| Application bring up                                                                                                                                                                                                                    | osHwiCreate()     | Installs an interrupt handler in<br>the OS dispatcher. It sets the<br>interrupt priority in the interrupt<br>assignment register and<br>enables the interrupt. |

| Application tear down                                                                                                                                                                                                                   | osHwiDelete()     | Detaches an interrupt handler from the OS dispatcher.                                                                                                          |

Listing 2.1 shows how an application installs a hardware interrupt in the OS dispatcher.

- 1. Application calls the kernel interrupt handler, osHwiCreate().

- 2. Kernel interrupt handler sets interrupt priority in the interrupt assignment register and enables the interrupt.

See SmartDSP OS API Reference Manual for more information.

#### Listing 2.1 Installing a HWI in the OS Dispatcher

### 2.1.2.2 Software Interrupts

A SWI is a program-generated interrupt. SmartDSP OS kernel supports nesting SWIs with HWIs and other priority SWIs. Any HWI or high priority SWI preempt a low priority SWI.

- Highest priority SWIs are specified by parameter OS\_SWI\_PRIORITY0.

- Lowest priority SWIs are specified by OS\_SWI\_PRIORITY15.

An application, using the definition #define OS\_TOTAL\_NUM\_OF\_SWI <num> in the os\_config.h file, can specify the number of SWIs per core.

The SWI prototype function is typedef void (\*os\_hwi\_function) (os\_swi\_count).

Table 2.2 lists SmartDSP OS SWI module functions.

#### Table 2.2 Available SWI Functions

| Flow State                                                                                                                                                                                                                              | Name              | Description                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------|

| Kernel bring up (the user<br>application does not call these<br>functions specifically. Instead,<br>osInitialize() calls these<br>functions based on the<br>parameters from os_config.h<br>and configurations from<br>msc81xx_config.c) | osSwiInitialize() | Initializes the software interrupts module.            |

| Application bring up                                                                                                                                                                                                                    | osSwiFind()       | Finds the first available software interrupt number.   |

|                                                                                                                                                                                                                                         | osSwiCreate()     | Attaches an interrupt handler to a software interrupt. |

**NOTE** An array of SWI handlers is allocated from the OS\_MEM\_LOCAL heap. There is a memory penalty if too high a value is set.

Interrupts

#### Table 2.2 Available SWI Functions

| Flow State            | Name            | Description                                                                                                                                                     |

|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application runtime   | osSwiActivate() | Activates the given software interrupt.                                                                                                                         |

|                       | osSwiCountSet() | Sets the count of the given software interrupt.                                                                                                                 |

|                       | osSwiCountInc() | Increments the count of the given software interrupt and activates it.                                                                                          |

|                       | osSwiCountDec() | Decrements the count of the<br>given software interrupt. This<br>function also activates the<br>software interrupt if the count is<br>zero after the operation. |

| Application tear down | osSwiDelete()   | Detaches the given software interrupt from its handler.                                                                                                         |

Listing 2.2 shows how to create a SWI using functions osSwiFind() and osSwiCreate().

- SWI, g\_swi\_holder1, is generated with the highest priority.

- An interrupt handler, foo, services the interrupt request.

Refer to SmartDSP OS API Reference Manual for more information.

#### Listing 2.2 Creating a SWI

```

osSwiFind(&g_swi_holder1);

status = osSwiCreate(foo,

//software interrupt function

g_swi_holder1,

//software interrupt number

OS_SWI_PRIORITY0,

//software interrupt priority

50);

//user Id

if (status != OS_SUCCESS) OS_ASSERT;

osSwiCountSet(g_swi_holder1, 100);

status = osSwiActivate(g_swi_holder1);

OS_ASSERT_COND(status != OS_SUCCESS);

void foo(os_swi_count count)

{

uint16_t self;

if (count != 100) OS_ASSERT;

status = osSwiSelf(&self);

```

```

if (status != OS_SUCCESS) OS_ASSERT;

status = osSwiDelete(self);

if (status != OS_SUCCESS) OS_ASSERT;

```

# 2.2 Scheduler

A scheduler determines when a specific task or a process must utilize the CPU. In the SmartDSP OS kernel, the scheduler is preemptive and event driven; that is, an event, such as an interrupt, triggers the scheduler to switch to the next higher priority task or process. The SmartDSP OS kernel does not enforce time slots or any other mechanism of load balancing.

In SmartDSP OS, each core has its own scheduler. The scheduler handles the events in this priority order:

1. NMI

}

- 2. HWI

- 3. SWI

- 4. Tasks

In other words, the scheduler considers an NMI as the top priority event, and a task as the lowest priority event.

Software interrupts can be activated by hardware interrupts, other software interrupts, and by tasks. Software interrupts can be preempted by hardware interrupts or higher-priority software interrupts. Hardware and software interrupts can be nested. The idle or background task has the lowest priority, and it should never end. It can include user code and is preempted by software interrupts as well as hardware interrupts and higher priority tasks.

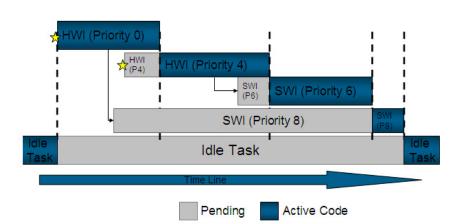

Figure 2.1 shows an example of how the scheduler operates with a single background task in the SmartDSP OS kernel. A higher-priority SWI runs to completion before a lower-priority SWI executes. SWIs are preempted by any HWI or a higher-priority SWI. Hardware interrupts always have priority over software interrupts. Hardware and software interrupts can be nested, and the priorities of each are considered.

Scheduler

Figure 2.1 SmartDSP OS Scheduler Operation

In Figure 2.1, the SmartDSP OS Scheduler operates as follows:

- 1. A HWI with priority 0 (the highest) activates a SWI with priority 8.

- 2. The SWI with priority 8 waits for HWI with priority 0 to finish.

- 3. Another HWI with priority 4 is activated as soon as HWI with priority 0 finishes the HWI with priority 4 is scheduled before the pending SWI with priority 8 (all HWI are scheduled before SWI).

- 4. The HWI with priority 4 begins executing.

- 5. The HWI with priority 4 activates another SWI, with priority 6.

- 6. SWI with priority 6 is scheduled before the pending SWI with priority 8 (SWI with higher priority preempt SWI with lower priority).

- 7. The SWI with priority 6 begins executing.

- 8. The SWI with priority 8 begins executing after SWI with priority 6 finishes.

# 2.3 Tasks

A task represents a specific part of a larger program that is currently loaded in memory. Each task in the SmartDSP OS kernel has its own:

- priority.

- stack and therefore a set of core registers.

- PID and DID (where supported).

- name.

- private data.

A task in the SmartDSP OS kernel is:

- different from SWIs and HWIs because a task has its own context and stack.

- attached to the core on which it was created.

The minimum and default number of tasks in the SmartDSP OS kernel is one. An application can override this setting in the os\_config.h file using this definition:

```

#define OS_TOTAL_NUM_OF_TASKS <num>

```

Tasks cannot be shared between cores or stolen. A task can sleep and/or yield the core. An array of task handlers will be allocated off of the OS\_MEM\_LOCAL heap; therefore you should be aware of the memory penalty of defining too many tasks. The OS\_TASK\_PRIORITY\_HIGHEST and OS\_TASK\_PRIORITY\_LOWEST parameters respectively specify the highest and the lowest priority for tasks. In addition, an application can use the following parameters for specifying a priority other than the highest and the lowest:

- OS\_TASK\_PRIORITY\_01,

- OS\_TASK\_PRIORITY\_02,

- ...

- OS\_TASK\_PRIORITY\_30

The maximum number of priorities for tasks is 32. An application can create multiple tasks with the same priority that will be scheduled in round-robin.

The SmartDSP OS kernel implements cooperative and priority-based scheduling among tasks. The priority of a task can be changed during run time by calling the <code>osTaskPrioritySet()</code> function. This function can be called from any context, HWI, SWI, or by another task.

An application can prohibit the scheduler from switching to a higher priority task by locking it. Locking will prevail even if the dispatcher is invoked due to some other event such as a HWI. Use these functions to lock and unlock the scheduler, respectively:

- osTaskSchedulerLock()

- osTaskSchedulerUnlock()

Tasks

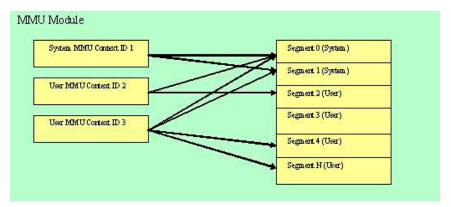

The SmartDSP OS kernel assigns each task with a unique program ID (PID) or data ID (DID) wherever supported in MMU. However, tasks can share a PID and/or a DID if an application specifically adds them to a SmartDSP OS MMU context using these functions:

- osTaskMmuDataContextSet()

- osTaskMmuProgContextSet()

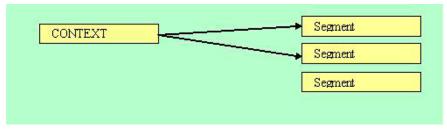

An MMU context defines a PID or DID (depending on the type of context) as well as the set of enabled MMU segments. By default, all tasks have the set of segments enabled in the system context. A task is not required to belong to the same program and data contexts. For example, task A and B may belong to the same data context while task A and C belong to the same program context. This does not require task B and C to share their data context.

Refer to SmartDSP OS API Reference Manual for more information.

Table 2.3 lists the functions available in the tasks module of the SmartDSP OS.

| Table 2.3 | Functions | Available | for | Tasks |

|-----------|-----------|-----------|-----|-------|

|           |           |           |     |       |

| Flow State                                                                                                                                                                                                                              | Name                | Description                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------|

| Kernel bring up (the user<br>application does not call these<br>functions specifically. Instead,<br>osInitialize() calls these<br>functions based on the<br>parameters from os_config.h<br>and configurations from<br>msc81xx_config.c) | osTasksInitialize() | Allocates a scheduler and then<br>allocates tasks and events<br>objects and inserts them in the<br>scheduler.              |

| Application bring up                                                                                                                                                                                                                    | osTaskFind()        | Retrieves the index of an unused task.                                                                                     |

|                                                                                                                                                                                                                                         | osTaskCreate()      | Creates a task. The task is<br>created in the suspended state.<br>Activate the task using<br>osTaskActivate().             |

|                                                                                                                                                                                                                                         |                     | For the background task, pass a pointer to the task created using osTaskCreate() as an argument to the osStart() function. |

| Flow State          | Name             | Description                                                                                                                                                                                                                                                                                                                                               |

|---------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application runtime | osTaskActivate() | Removes the created task from<br>the suspend state. If the task is<br>not suspended, the function has<br>no effect. If the task is not<br>delayed or pending, it is moved<br>to the ready state, and<br>scheduler is called. If this is the<br>highest priority ready task and it<br>is the first in its priority queue,<br>then it will resume or start. |

|                     | osTaskSuspend()  | Moves the task to the suspend state.                                                                                                                                                                                                                                                                                                                      |

|                     | osTaskDelay()    | Delays the running task by<br>blocking the task for the<br>specified number of ticks.                                                                                                                                                                                                                                                                     |

### Table 2.3 Functions Available for Tasks (continued)

Tasks

| Flow State            | Name                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | osTaskYield()               | Schedules a different task in<br>same priority or higher if<br>available. The SmartDSP OS<br>scheduler allows several tasks<br>to have the same priority level.<br>In this case, the tasks should<br>implement cooperative<br>scheduling to allow other tasks<br>to execute first. The<br>osTaskYield() function<br>allows a task to preempt itself in<br>favor of another specific task or<br>next ready task of the same<br>priority. |

|                       | osTaskPriorityReadyCoun t() | Counts the number of tasks that are ready in a specified priority.                                                                                                                                                                                                                                                                                                                                                                      |

|                       | osTaskMmuDataContextSet ()  | Sets a data context for a task. It effects the data MMU segments enabled and the DID.                                                                                                                                                                                                                                                                                                                                                   |

|                       | osTaskMmuProgContextSet ()  | Sets a program context for a task. It effects the program MMU segments enabled and the PID.                                                                                                                                                                                                                                                                                                                                             |

|                       | osTaskSchedulerLock()       | Locks the scheduler so that the running task cannot be replaced.                                                                                                                                                                                                                                                                                                                                                                        |

|                       | osTaskSchedulerUnlock()     | Unlocks the scheduler so that<br>the running task can be<br>replaced.                                                                                                                                                                                                                                                                                                                                                                   |

| Application tear down | osTaskDelete()              | Deletes a task.                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Table 2.3 Functions Available for Tasks (continued)

Listing 2.3 shows how to find an existing task and create a new task using the osTaskFind() and osTaskCreate() functions.

### Listing 2.3 Finding and creating a task

```

uint8_t task_stack[TASK_STACK_SIZE];

```

```

status = osTaskFind(&task_handle);

OS_ASSERT_COND(status == OS_SUCCESS);

os_task_init_param.task_function = F;

os_task_init_param.task_name = N;

os_task_init_param.stack_size = SZ;

os_task_init_param.task_arg = A;

os_task_init_param.task = task_handle;

os_task_init_param.task_priority = OS_TASK_PRIORITY_27;

os_task_init_param.private_data = D2;

os_task_init_param.top_of_stack = S;

/* Stack should be in a memory accessible to the task given its MMU

data context */

status = osTaskCreate(&os_task_init_param);

OS_ASSERT_COND(status == OS_SUCCESS);

```

Listing 2.4 shows how to activate and suspend a task using the osTaskActivate() and osTaskSuspend() functions.

#### Listing 2.4 Activating and suspending a task

```

status = osTaskActivate(task_handle);

OS_ASSERT_COND(status == OS_SUCCESS);

status = osTaskSuspend(task_handle);

OS_ASSERT_COND(status == OS_SUCCESS);

```

Use the source code shown in Listing 2.5 to verify the task suspension. The source code verifies the task status and deletes the task (using the osTaskDelete() function) if the task is suspended. If the task is not suspended, the source code delays the task using the osTaskDelay() function.

#### Listing 2.5 Verifying task suspension

```

if (osTaskStatusGet(task_handle) & OS_TASK_SUSPEND)

{

status = osTaskDelete(task_handle); //Deleting the task

OS_ASSERT_COND(status == OS_SUCCESS);

}

status = osTaskDelay(DELAY_TIME); //Delaying the task

OS_ASSERT_COND(status == OS_SUCCESS);

```

Tasks

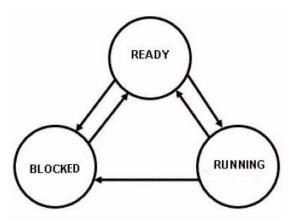

### 2.3.1 Task States

A task exists in one of these states:

- Ready

- Running

- Blocked

Figure 2.2 shows how a task transitions from one state to another.

### Figure 2.2 Task States

A task changes its state from one to another when:

- A task that is ready to run is in a READY state.

- A ready to run task becomes the highest priority task and starts running, its state changes from READY to RUNNING.

- A higher priority task becomes READY and preempts the current task; the currently running task state changes from RUNNING to READY.

- Another higher priority task suspends a READY task; the suspended task state changes from READY to BLOCKED.

- The task suspends or delays itself; the task state changes from RUNNING to BLOCKED.

- A blocked task gets activated by another task, its delay expires, or a waited event occurs; the task state changes from BLOCKED to READY.

- A task, by default, is created in a BLOCKED state.

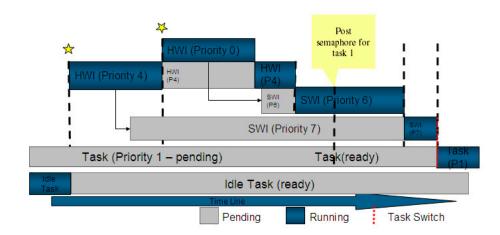

<u>Figure 2.3</u> shows how a task state changes from one to another. In this figure, the arrows represent the SWI activation by HWI and stars represent events, which may or may not immediately trigger their HWI.

An idle task is running. A HWI with priority 0 activates a SWI with priority 6. The SWI (Priority 6) posts the task on the semaphore, which makes the task move from pending to READY state. The task is not yet activated because SWI (Priority 6) and SWI (Priority 7) are still running in the system. The READY task becomes active only when the higher priority event or HWI or SWI finishes execution. Once all the higher priority events finish executing, the scheduler is called and SWI returns back to the interrupt dispatcher. This moves the task from READY to RUNNING state because it is the highest priority task in the system now.

### Figure 2.3 Task States Transition

## 2.3.2 Background Task

The SmartDSP OS kernel requires a task in the background so the system always has at least one task running. The last step of OS initialization activates the background task with the lowest priority. You do not need to explicitly find or create the background task; it is created by the operating system. The background task function pointer is passed as an argument to the <code>osStart()</code> function. The background task uses system MMU settings (wherever supported). MMU has system data settings and system program settings. The background task should not return.

An application can override the default stack size for the background task in the  $os_config.h$  file using this definition:

#define OS\_BACKGROUND\_STACK\_SIZE <size>

**NOTE** An application cannot block, suspend, or delete the background task at any stage during execution.

Spinlocks

## 2.4 Spinlocks

A spinlock is a binary lock which the currently running program waits to become available before continuing the code execution flow. In the SmartDSP OS kernel, spinlocks protect the critical data or code among multiple cores. In addition, spinlocks can be used to synchronize the tasks executing on multiple cores. The spinlock uses atomic test-and-set operations (bmtset.w) for synchronization.

In the SmartDSP OS kernel, a spinlock either:

- protects the critical sections from access by other cores and Interrupt Service Routines (ISR) running on the same core, or

- protects the critical section from access by other cores, but not from access by ISRs running on the same core.

- **NOTE** bmtset.w is StarCore specific. Refer to *SC3850 DSP Core Reference Manual* for more information about bmtset.w.

The data is guarded locally on the core among tasks by enabling/disabling interrupts or by using <code>osHwiSwiftDisable()/osHwiSwiftEnable()</code> functions. Spinlocks should be used only when data is shared between cores.

A spinlock in the SmartDSP OS kernel is 32 bits in memory, non-cacheable, and in memory which supports atomic operations, such as, M2 in MSC814x architecture and M3 in MSC815x architecture.

**NOTE** Do not use the same spinlock on the same core in different priorities (HWI, SWI, and/or tasks) without closing interrupts. A deadlock may occur.

The following functions are used for acquiring spinlocks:

- osSpinLockGet() Acquires the spinlock. This is a blocking operation. Use this function with caution because of the possibility of deadlock.

- osSpinLockIrqGet() Disables interrupts and then acquires the spinlock. This is a blocking operation.

- osSpinLockTryGet() Tries to acquire the given spinlock. Returns whether or not the spinlock is acquired. This is a non-blocking operation.

The following functions are used for releasing spinlocks:

- osSpinLockRelease() Releases the spinlock.

- osSpinLockIrqRelease() Releases the spinlock and then enables interrupts.

- **NOTE** The osSpinLockGet() and osSpinLockRelease() calls do not disable interrupts, which can lead to deadlocks if an ISR tries to access the critical section. Also, performance degradation can occur if one core gets the spinlock and jumps to an ISR from within the critical section, leaving the other cores waiting for the spinlock while the ISR is being served.

To use a fake spinlock, define its address as OS\_GUARD\_DISABLE. OS\_GUARD\_DISABLE is a SmartDSP OS defined macro that when assigned to the spinlock, indicates that no action will take place on the spinlock and the core will not execute any syncio (blocking) instructions. The following source code shows how to use the OS\_GUARD\_DISABLE macro:

```

uint32_t dummy_spinlock_addr = OS_GUARD_DISABLE; /* Won't take

spinlock. Won't execute syncio */

osSpinLockGet((volatile uint32_t *)dummy_spinlock_addr);

```

# 2.5 Memory Manager

The memory manager component of the SmartDSP OS kernel module handles memory allocation and buffer management. The memory manager allocates memory blocks dynamically and frees them when they are no longer in use. The SmartDSP OS memory manager enables efficient allocation, retrieval, and release of memory blocks of known size and alignment without memory fragmentation.