# Integrated Flash Controller

freescale.com/QorIQ

### **1** Introduction

The past few years have witnessed explosive growth in the flash memory market, driven by the use of wireless communication devices, networking and communication products, security systems and other types of electronic equipment (PDAs, digital cameras, MP3 audio players). In the next few years, system designs will demand even more non-volatile memories, either with high density and very high writing throughput for data storage applications or with fast random access for code execution. The flexibility and low cost of flash memory makes it a frequently utilized, well-consolidated and mature technology for most non-volatile memory applications.

#### Integrated Flash Controller

Bus

←→ Single Signal Line

Today, almost every system design uses external memory, since embedded memories can be costly

in terms of price and power consumption. As a result, implementing a memory controller that can manage multiple memory types is now an essential differentiator in the processor market.

The QorlQ P1010 and P1014 processors introduce the new integrated flash controller (IFC), an advanced version of the enhanced local bus controller which includes similar programming and signal interfaces with an extended feature set. The IFC provides access to multiple external memory types, such as NAND flash (SLC and MLC), NOR flash, EPROM, SRAM and other memories where address and data are shared on a bus. These memory controllers offer the system an alternate option and cover a wide range of applications, from networking and communications to consumer and automotive.

#### Drivers for an Integrated Flash Controller

- Market trend toward NAND with larger page sizes

- Increase in flash density with more ECC bits per page

- Command set enhancements

- Emergence of Open NAND Flash Interface (ONFI) standard

- High-speed NAND flash devices using source synchronous DDR mode

## 2 Overview

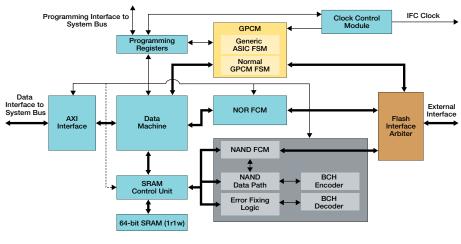

The IFC on the P1010 processor family contains one NAND, one NOR flash controller and one general-purpose chip-select machine (GPCM) controller. It can be programmed such that all four memory banks, each with addressable system memory of 4 GB, can work with NAND, NOR and a GPCM controller depending on the requirement. The IFC can be configured to interface to a NOR or NAND flash device on any bank. In addition, the IFC contains a GPCM that can be used as a synchronous

interface to a variety of devices, including external PHYs, ASICs or FPGAs.

Four chip selects, with common address, data and control bus, are provided in IFC so that a maximum of four flash devices can be connected, but only one can be accessed at a given time. Pin muxing is done internally based on a selected controller (NAND, NOR or GPCM).

The NAND flash controller supports the ONFI 2.0 asynchronous interface and provides an 8- or 16-bit flash memory interface. The controller offers a Bose, Chaudhuri and Hocquenghem (BCH) algorithm for 4- and 8-bit error-correcting code (ECC) for optimized performance and reliability. In addition, the IFC supports boot from NAND flash devices, multiple page sizes (up to 4 KB) and multi-terabyte flash devices.

The NOR flash controller offers compatibility with asynchronous NOR flash (synchronous burst read not supported) and flexibility in timing control that allows interfacing with proprietary NOR devices. Boot from NOR flash devices is also available. Additionally, the GPCM offers the possibility to interface with a multitude of devices, including external PHYs, ASICs or FPGAs. The GPCM provides support for x8/16-bit devices, compatibility with general-purpose addressable devices (SRAM and ROM) and an external access termination signal (IFCTA).

QorlQ P1010/P1014 processors deliver unique product differentiators and can be configured to meet many system application needs. Freescale's innovative IFC technology is a key design component for the future of QorlQ processor platforms. It provides the flexibility needed for emerging applications that require interfacing with a variety external memories, as well as the ability to support large page mainstream flash memories.

## Integrated Flash Controller Features

| NAND Flash Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NOR Flash Features                                                                                                                                                                                                                                                                                                                                                                       | GPCM Features                                                                                                                                                                                                                                                                                                                                                                    | GASIC Features                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>x8/x16 NAND flash interface</li> <li>Support for ONFI-2.0 asynchronous<br/>interface (8/16-bit)</li> <li>BCH code for 4-bit and 8-bit error<br/>correction per sector</li> <li>ECC generation/checking optional</li> <li>Flexible timing control to allow<br/>interfacing with proprietary NAND<br/>devices</li> <li>SLC and MLC flash devices support<br/>with configurable page sizes of up to<br/>4 KB</li> <li>Support for advanced NAND<br/>commands (cache, copy-back and<br/>multi-plane programming)</li> <li>Programmable command and data<br/>transfer sequences up to 15 steps</li> <li>Configurable block size constraint to<br/>multiples of 32 pages, up to 2048</li> <li>Interrupt for error handling and flash<br/>command completion event</li> <li>Internal SRAM of 16 KB</li> <li>Boot chip-select (CS0) available after<br/>system reset, with boot block size of<br/>8 KB, for execute-in-place boot<br/>loading from NAND flash</li> <li>Flash devices with multiple terabytes<br/>of storage</li> </ul> | <ul> <li>Supports asynchronous NOR flash</li> <li>Provides memory mapped interfacing to NOR</li> <li>Supports address data multiplexed (ADM) NOR device</li> <li>Flexible timing control allows interfacing with proprietary NOR devices (write enable controlled writes only)</li> <li>Boot chip-select (CS0) available at system reset</li> <li>Data bus width of 8/16 bits</li> </ul> | <ul> <li>Support for x8/16-bit devices</li> <li>Compatible with general-purpose<br/>addressable devices (SRAM and ROM)</li> <li>External clock is supported by<br/>programmable division ratios</li> <li>Output enable signal</li> <li>Write enable signal</li> <li>Even/odd parity on data bus<br/>supported</li> <li>External access termination signal<br/>(IFCTA)</li> </ul> | <ul> <li>Support for 16/8-bit devices where address and data sequences are shared on the same bus</li> <li>The following address and data sequences are supported on I/O bus 0 16-bit I/O: AADD 0 8-bit I/O: AAADDDD</li> <li>Configurable even/odd parity on address/data bus supported</li> <li>Parity error detection supported</li> </ul> |

## How to Reach Us:

Home Page: www.freescale.com

#### **QorlQ Portfolio Information:** www.freescale.com/QorlQ

#### e-mail:

support@freescale.com

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 1-800-521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 303-675-2140 Fax: 303-675 2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright license granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

# *freescale*

## For current information about QorlQ products and documentation, please visit freescale.com/QorlQ

Freescale, Freescale logo and QorlQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. © 2011 Freescale Semiconductor, Inc. Document Number: INTFCWP/REV 0