# AN12446 Migration Guide for RT1020 to RT1010

Rev. 1 — November 2019

**Application Note**

## **1** Introduction

This document describes the key points of the the migration from the i.MX RT1020 to i.MX RT1010 crossover processor for the embedded system development. It describes the hardware board design considerations, the software, and tools.

This document does not try to compare the advantages or disadvantages of the two silicons, as they have their own target markets. This document is for

#### Contents

| 1 Introduction     | 1 |

|--------------------|---|

| 2 Overview         | 1 |

| 3 System module    | 2 |

| 4 Hardware design  | 5 |

| 5 Revision history | 5 |

|                    |   |

those who have developed embedded system with i.MX 1020, and decide to migrate the project to i.MX RT1010. The audience are expected to have i.MX 1020 experience and wish to start projects with i.MX RT1010.

The i.MX RT1020 expands the i.MX RT crossover processor families by providing high-performance feature set in low-cost LQFP packages, further to simplify board design and layout for customers. The i.MX RT1020 runs on the Arm<sup>®</sup> Cortex<sup>®</sup>-M7 core at 500 MHz.

The i.MX RT1010 is defined as a cost efficient crossover processor for low cost applications, where higher performance and realtime responses are critical. It is powered by a single Arm Cortex-M7 core running up to 500 MHz, which, along with a unique blend of ADC, PWM, Timers modules and I<sup>2</sup>S interfaces, makes the i.MX RT1010 an ideal solution for IOT node, motor control, industrial and audio application. The i.MX RT1010 simplifies the board design and layout for customers. The i.MX RT1010 runs on the Arm Cortex-M7 core at 500 MHz.

### 2 Overview

Table 1 describes the feature differences for RT1010 and RT1020.

| Features         | i.MX RT1020 <sup>1</sup>       | i.MX RT1010                 |

|------------------|--------------------------------|-----------------------------|

| CPU core         | Arm Cortex-M7 500 MHz          | Arm Cortex-M7 500 MHz       |

|                  | Double Precision FPU + MPU     | Single FPU + MPU            |

| PLL              | PLL2 - System PLL (528 MHz)    | PLL2 - System PLL (528 MHz) |

|                  | PLL3 - USB1 PLL (480 MHz)      | PLL3 - USB1 PLL (480 MHz)   |

|                  | PLL4 - Audio PLL               | PLL4 - Audio PLL            |

|                  | PLL6 - ENET PLL                | PLL6 - ENET PLL             |

| Power management | Integrated DCDC/LDO            | Integrated DCDC/LDO         |

| Cache            | 16 K/16 K L1 I/D-cache         | 16 K/8 K L1 I/D-cache       |

| Internal RAM     | 256 KB FlexRAM(Bank0 – Bank7 ) | 128 KB                      |

|                  | (OCRAM+I/DTCM)                 | FlexRAM(Bank0 – Bank 3)     |

|                  |                                | (OCRAM+I/DTCM)              |

Table continues on the next page...

| Serial flash I/F | Dual-channel QSPI NOR and NAND                                                                                                    | Dual-channel QSPI NOR                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                  | Octal flash and RAM                                                                                                               | Octal flash and RAM                                                                     |

|                  | XIP supported                                                                                                                     | XIP supported                                                                           |

| Audio            | Multi-channel I <sup>2</sup> S × 1, SAI/I <sup>2</sup> S × 2, SPDIF Tx/Rx, MQS                                                    | Multi-channel I <sup>2</sup> S × 1, <b>SAI/I<sup>2</sup>S × 1</b> ,<br>SPDIF Tx/Rx, MQS |

| ADC/ACMP         | 12-bits ADC $\times$ 2, ACMP $\times$ 4                                                                                           | 12-bits ADC × 1                                                                         |

| Timers and PWM   | GPT $\times$ 2, PIT $\times$ 4, QTimer $\times$ 2, FlexPWM $\times$ 2,<br>QuadDecoder $\times$ 2, WDOG $\times$ 3, ETM $\times$ 1 | GPT × 2, <b>PIT × 1</b> , <b>FlexPWM × 1</b> ,<br>WDOG × 3, ETM × 1                     |

| Connectivity     | LPUART × 8, LPSPI × 4, LPI <sup>2</sup> C × 4, FlexIO × 1,<br>FlexCAN × 2                                                         | <b>LPUART × 4, LPSPI × 2, LPI<sup>2</sup>C × 2,</b><br>FlexIO × 1                       |

| Security         | DCP, BEE, TRNG, SNVS, SJC                                                                                                         | DCP, OTFAD, TRNG, SNVS, SJC                                                             |

| USB              | USB OTG HS w/PHY × 2                                                                                                              | USB OTG HS w/PHY × 1                                                                    |

| High-speed GPIO  | NA                                                                                                                                | 29 channels                                                                             |

| DRAM I/F         | SDRAM 8/16-bit, 133 MHz                                                                                                           | NA                                                                                      |

| External memory  | 8/16-bit parallel NOR flash                                                                                                       | NA                                                                                      |

|                  | 8/16-bit SLC NAND flash (SW ECC)                                                                                                  |                                                                                         |

| eMMC/SD I/F      | eMMC 4.5/SD 3.0 × 2                                                                                                               | NA                                                                                      |

| Ethernet         | 10/100 with IEEE1588 × 1                                                                                                          | NA                                                                                      |

| Boot Devices     | Serial NOR flash via FlexSPI Interface                                                                                            | Serial NOR flash via FlexSPI                                                            |

|                  | Serial NAND Flash via FlexSPI Interface                                                                                           | Interface                                                                               |

|                  | Parallel NOR flash with the Smart External Memory Controller (SEMC), located on CS0, 16-bit bus width                             |                                                                                         |

|                  | NAND Flash with SEMC interface, located on CS0, 8-bit/16-bit bus width.                                                           |                                                                                         |

|                  | SD/MMC/eSD/SDXC/eMMC4.4 via uSDHC interface, supporting high capacity cards                                                       |                                                                                         |

|                  | Serial NOR/EEPROM boot via LPSPI                                                                                                  |                                                                                         |

|                  |                                                                                                                                   |                                                                                         |

| Table 1. Summary of feature difference | s for RT1010 and RT1020 ( | continued) |

|----------------------------------------|---------------------------|------------|

|----------------------------------------|---------------------------|------------|

1. The i.MX RT1020 feature set varies on packages. For details, refer to the i.MX RT1020 datasheet.

## 3 System module

#### 3.1 Clocks

RT1010's PLL is reused from the RT1020, which means that RT1010 can directly reuse the PLL configurations of the RT1020. However, there are modifications on CCM clock tree. Table 2 describes the CCM clock tree differences for RT1010 and RT1020. For details, refer to RT1010 and RT1020 Reference Manual.

| RT1010 removal | ARM_PODF DIV                                  |

|----------------|-----------------------------------------------|

|                |                                               |

|                | PERIPH_CLK2_PODF DIV                          |

|                | USDHC1_CLK_ROOT                               |

|                | USDHC2_CLK_ROOT                               |

|                | SEMC_CLK_ROOT                                 |

|                | SAI2_CLK_ROOT                                 |

|                | CAN_CLK_ROOT                                  |

| RT1010 add     | FLEXSPI_CLK_SRC MUX                           |

|                | ADC_ALT_CLK                                   |

|                | PII3_sw_clk as a source for SAI1 and SAI3     |

| RT1010 update  | AHB_CLK_ROOT -> CORE_CLK_ROOT                 |

|                | FlexSPI CLK source: SEMC_CLK_ROOT_PRE -> PLL2 |

Table 2. Summary of clock tree differences for RT1010 and RT1020

#### 3.2 High-speed GPIO

The RT1010 provides 29 channels of High-Speed GPIO (HSGPIO). The HSGPIO can be accessed with high frequency. The maximum toggle frequency of HSGPIO is half of the CORE, but the maximum toggle frequency of the pad is about 200 MHz. Therefore, the maximum toggle frequency of HSGPIO is about 200 MHz.

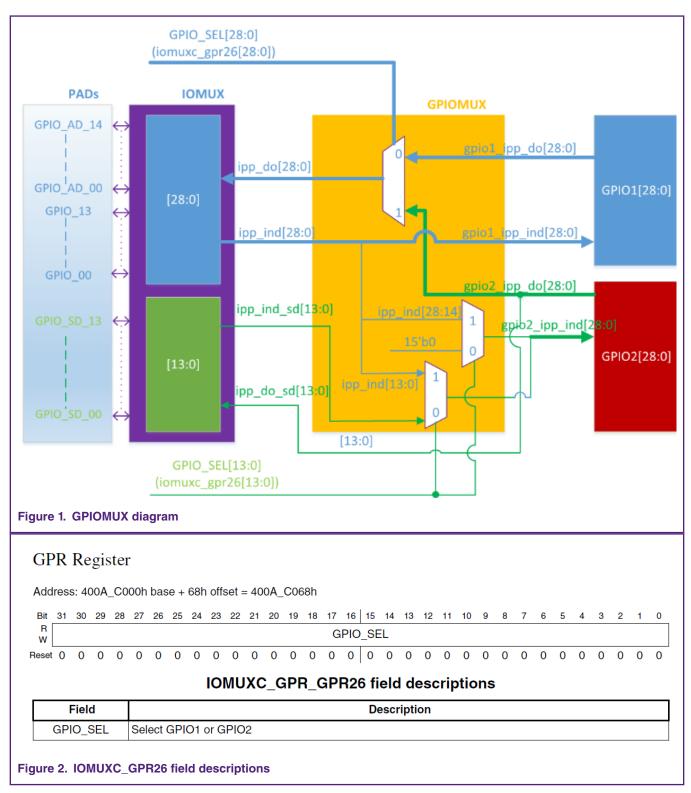

GPIO1 is the general GPIO port and GPIO2 is the HSGPIO port, as shown in Figure 1. The IOMUXC\_GPR26 register controls which port to be mapped to the pad, as shown in Figure 2.

According to Figure 1 and Figure 2, Table 3 can be obtained.

Table 3. High-speed GPIO mapping table

|                        | GPIO        | PAD                      |

|------------------------|-------------|--------------------------|

| IOMUXC_GPR26[28:0] = 0 | GPIO1[28:0] | GPIO[13:0],GPIO_AD[14:0] |

|                        | GPIO2[13:0] | GPIO_SD[13:0]            |

| IOMUXC_GPR26[28:0] = 1 | GPIO1[28:0] | NA                       |

|                        | GPIO2[28:0] | GPIO[13:0],GPIO_AD[14:0] |

#### 3.3 SAI

There are three SAIs in the RT1020 but only two in the RT1010. SAI2 is removed from the RT1010 and only SAI1 and SAI3 are provided in RT1010.

#### 3.4 OTFAD

For on-the-fly decryption and XIP, the RT1020 uses the Bus Encryption Engine (BEE) while RT1010 uses the On-the-fly AES Decryption (OTFAD). No software or hardware changes are required if ROM is used for the image decryption. Since the BEE and OTFAD use different IP, there are some differences. For example, BEE encrypts parameters by PRDB but OTAFD by Key Blob.

#### • BEE

Typical AES engine performs a single-round operation in 1-2 machine cycles.

• OTFAD

Heavily pipelined AES engine, optimized for decryption, performs three rounds per cycle.

### 4 Hardware design

The hardware design key points of the RT1010 is almost same as the RT1020. For details, refer to RT1010 Hardware Design Guide.

# **5 Revision history**

#### Table 4. Revision history

| Revision No. | Date     | Description     |

|--------------|----------|-----------------|

| 0            | May 2019 | Initial release |

| 1            | November | Updated Table1  |

#### How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2019.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: November 2019 Document identifier: AN12446

# arm