# Layerscape<sup>®</sup> 1020A and 1022A Dual-Core Processors

# LS1020A

Last Updated: Apr 11, 2024

The LS1 family, which includes the LS1020A and LS1022A communications processors, is built on Layerscape architecture, the industry's first software-aware, core-agnostic networking architecture to offer unprecedented efficiency and scale.

Members of the value-performance tier, the LS1020A and LS1022A processors provide extensive integration and power efficiency for fanless, small form factor enterprise and consumer networking applications. Incorporating dual Arm® Cortex®-A7 cores running up to 1.2 GHz, the LS1020A and LS1022A processors deliver pre-silicon CoreMark® performance of over 7,000, as well as virtualization support, advanced security features and broadest array of high-speed interconnects and optimized peripheral features ever offered in a sub-3 W processor (LS1022A processor is sub-2W typical).

The LS1020A and LS1022A processors features support for multiple industrial protocols, DDR3L/4 running up to 1600 MHz, integrated hardware-based security engine and QUICC Engine<sup>®</sup>. and ECC protection on both L1 and L2 caches. The LS1020 and LS1022A processors are pin- and software-compatible with the LS1021A processor.

Layerscape processors are part of NXP's EdgeVerse<sup>™</sup> edge computing platform.

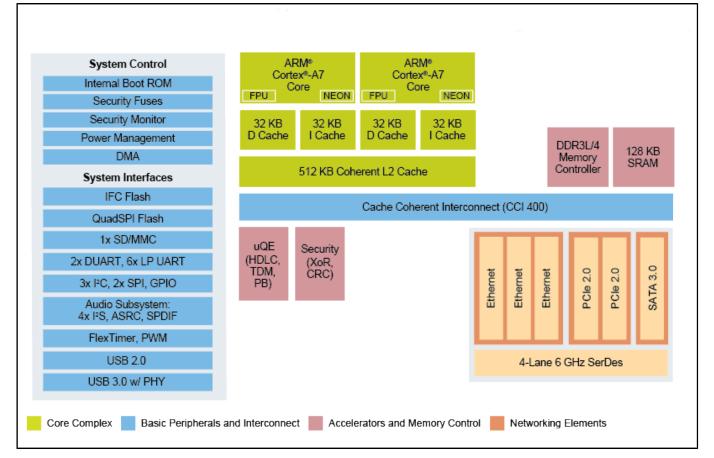

## 29841\_LS1022A\_BD Block Diagram

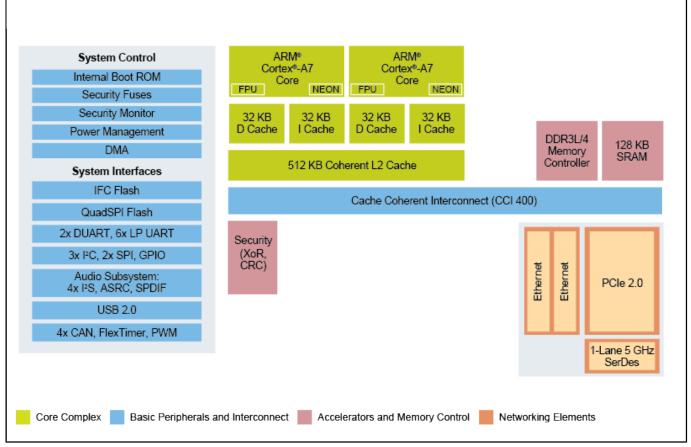

### 29841\_LS1020A\_BD Block Diagram

#### View additional information for Layerscape® 1020A and 1022A Dual-Core Processors.

Note: The information on this document is subject to change without notice.

#### www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.