## Low-Voltage 16-Bit I<sup>2</sup>C-Bus I/O Port with Interrupt and Agile I/O

## PCAL9535A

Last Updated: Nov 7, 2023

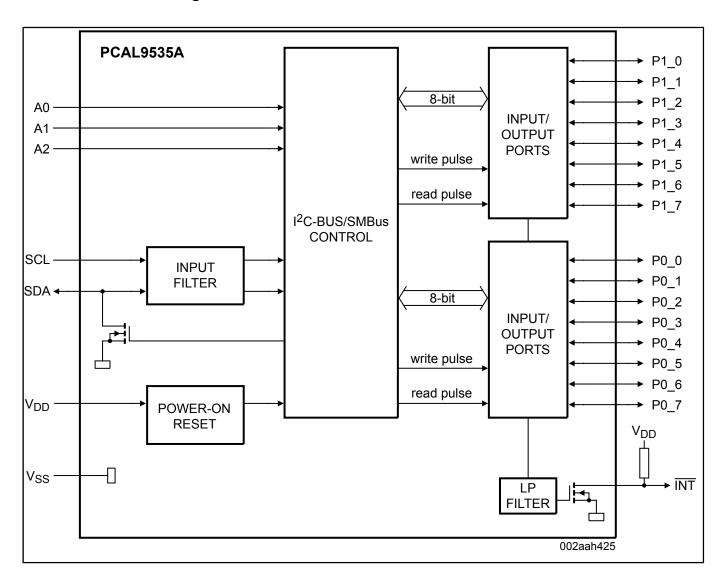

The PCAL9535A is a low-voltage 16-bit General Purpose Input/Output (GPIO) expander with interrupt and reset for I<sup>2</sup>C-bus/SMBus applications. NXP® I/O expanders provide a simple solution when additional I/Os are needed while keeping interconnections to a minimum, for example, in ACPI power switches, sensors, push buttons, LEDs, fan control, etc.

In addition to providing a flexible set of GPIOs, the wide VDD range of 1.65 V to 5.5 V allows the PCAL9535A to interface with next-generation microprocessors and microcontrollers where supply levels are dropping down to conserve power.

The PCAL9535A contains the PCA9535 register set of four pairs of 8-bit configuration, input, output and polarity inversion registers and additionally, the PCAL9535A has Agile I/O, which are additional features specifically designed to enhance the I/O. These additional features are programmable output drive strength, latchable inputs, programmable pull-up/pull-down resistors, maskable interrupt, interrupt status register, programmable open-drain or push-pull outputs.

The PCAL9535A is a pin-to-pin replacement to the PCA9535 and PCA9535A, however, the PCAL9535A powers up with all I/O interrupts masked. This mask default allows for a board bring-up free of spurious interrupts at power-up.

The PCAL9535A open-drain interrupt (INT) output is activated when any input state differs from its corresponding Input Port register state and is used to indicate to the system leader that an input state has changed.

INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I<sup>2</sup>C-bus. Therefore, the PCAL9535A can remain a simple follower device.

The device outputs have 25 mA sink capabilities for directly driving LEDs while consuming low device current.

The power-on reset sets the registers to their default values and initializes the device state machine.

Three hardware pins (A0, A1, A2) select the fixed I<sup>2</sup>C-bus address and allow up to eight devices to share I<sup>2</sup>C-bus/SMBus.

## PCAL9535A Block Diagram

| Note: The information on this document is subject to change without notice.                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                               |

| www.nxp.com                                                                                                                                                                                                                                                                   |

| NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V. |