# S32K39/37/36 Microcontrollers for Electrification Applications

## S32K39-37-36

Last Updated: Sep 8, 2025

S32K39-37-36 is a purpose-built device addressing the new electric vehicle (EV) needs with a compelling combination of performance, integration, networking, security and functional safety capabilities.

S32K39-36 has enough compute power to support up to one six-phase or two three-phase motors controlled by over 200 kHz control loops, while hosting AI/ML algorithms or other monitoring applications. It supports remote smart actuation applications using Time-Sensitive Networking (TSN) Ethernet for new zonal vehicle architectures. It also reduces system cost with ASIL D software resolver and analog integration.

The S32K37 high-compute capabilities are ideal for high-end [battery management systems \(BMS\)](#) applications.

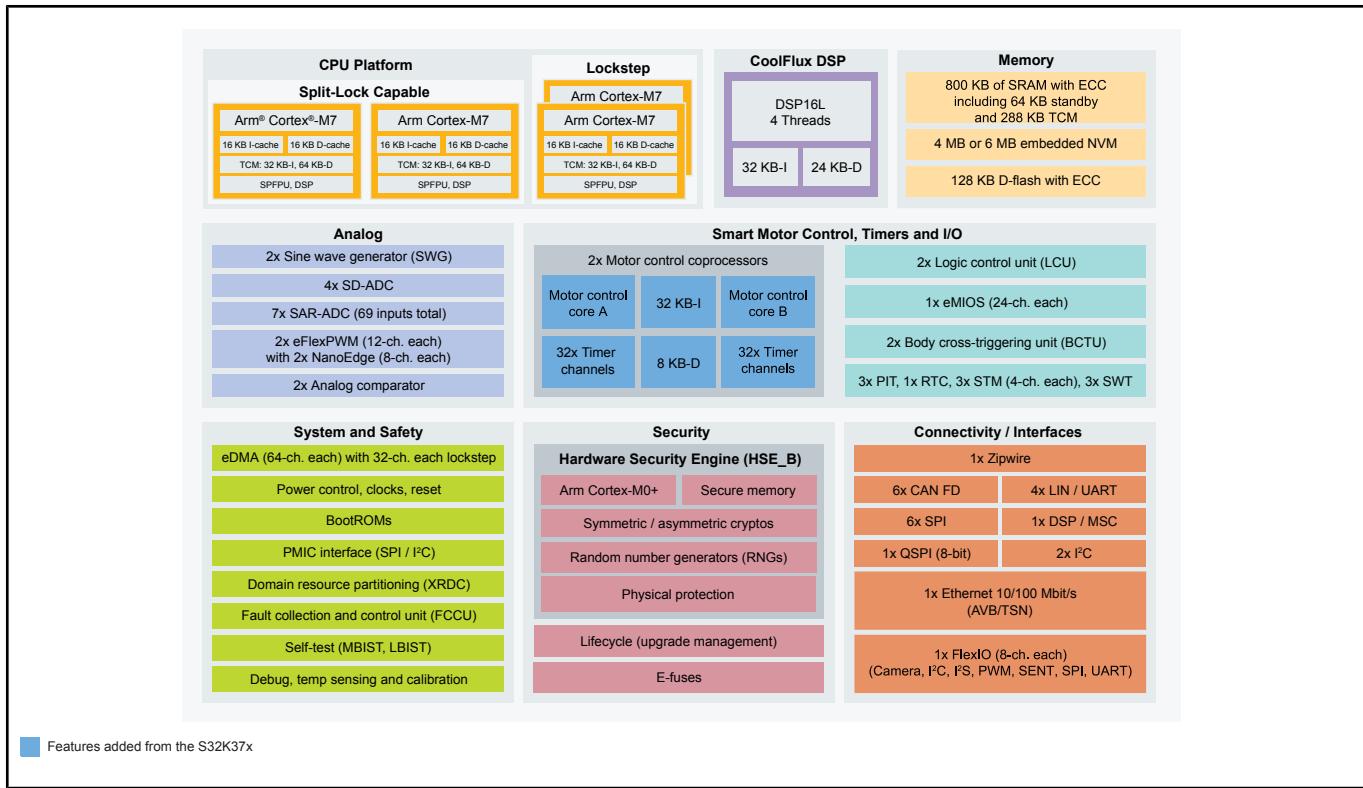

## S32K39 Microcontrollers Block Diagram

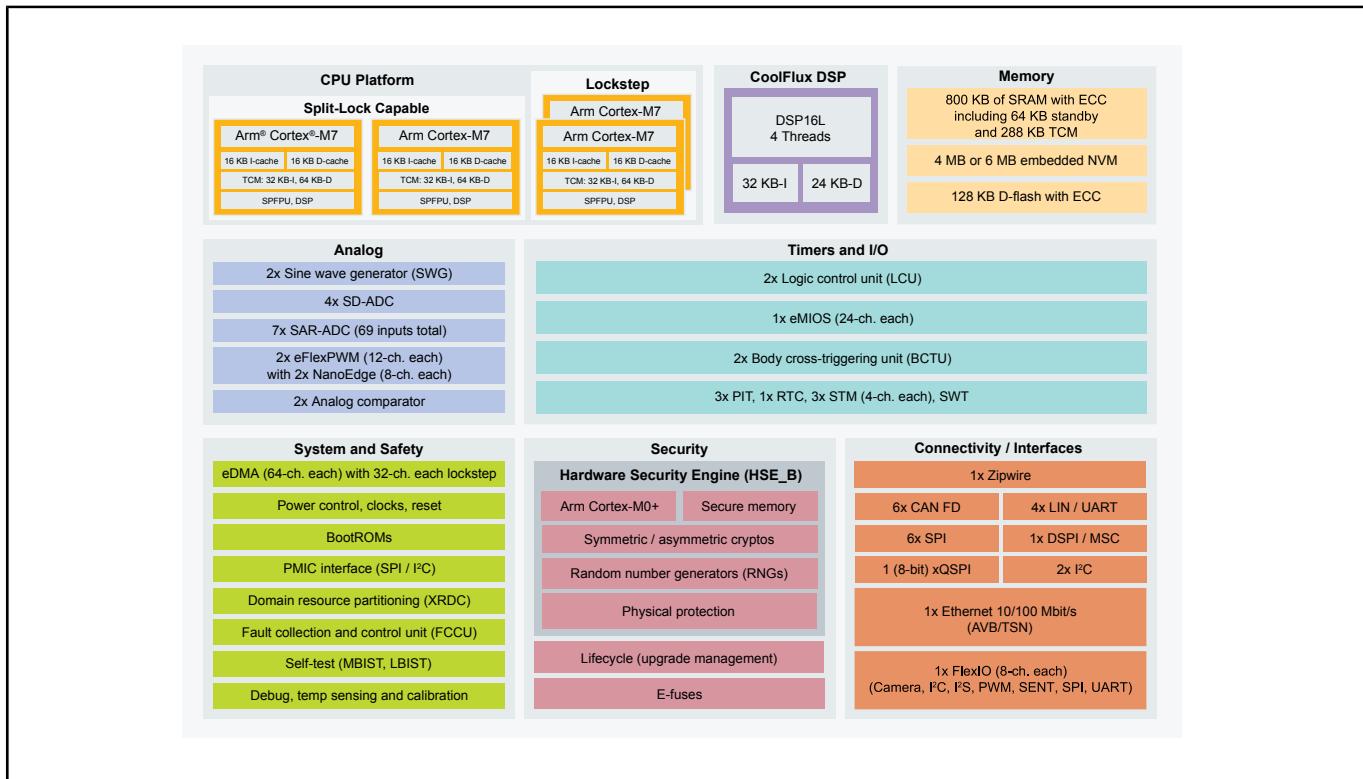

## S32K37 Microcontrollers Block Diagram

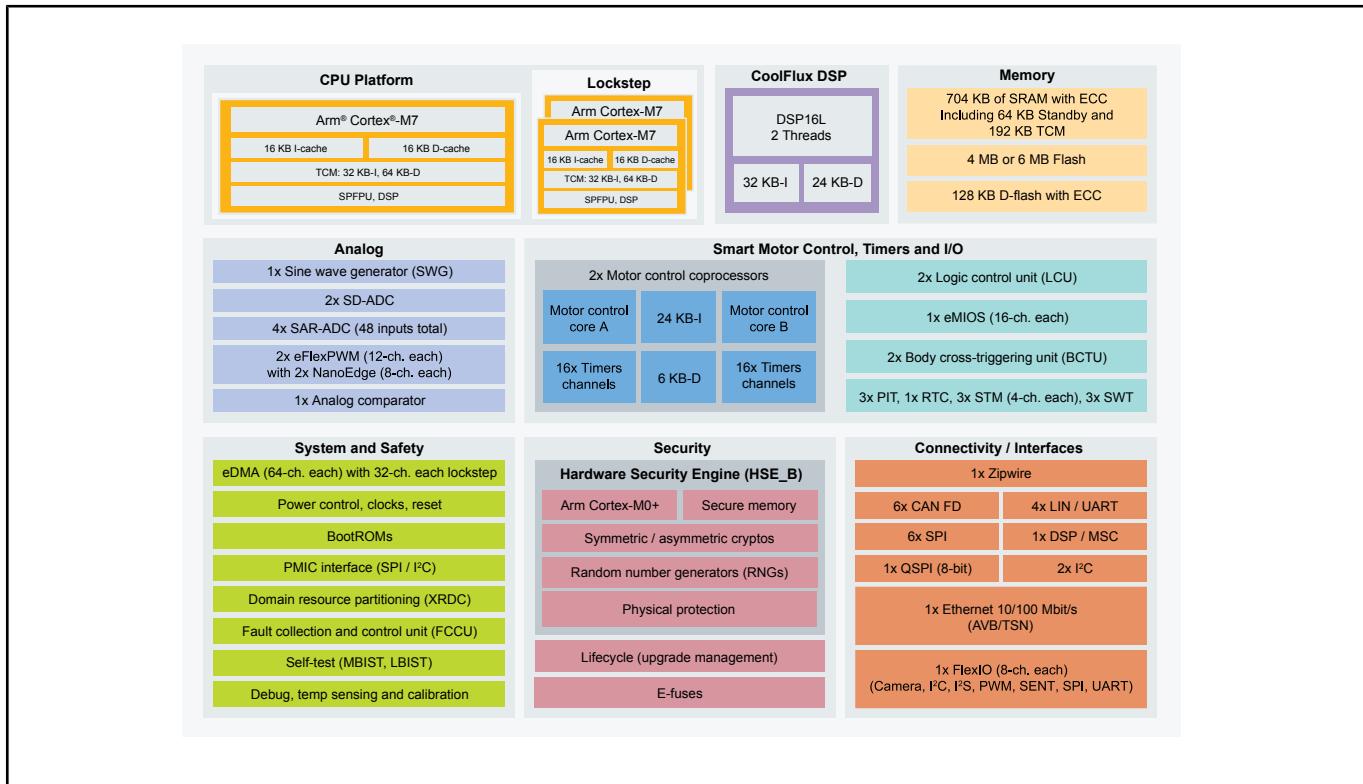

## S32K36 Microcontrollers Block Diagram

## S32K39 Family Features Block Diagram

| Common Features                                                                           | K364                                       | K366                                          | K374                                                    | K376                                    | K394       | K396       |

|-------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|---------------------------------------------------------|-----------------------------------------|------------|------------|

| AEC-Q100, 125 °C, 3.3/5 V                                                                 | 1 x LockStep + 1 Arm® Cortex®-M7 @ 320 MHz |                                               | 1 x LockStep + 2 x Split-Lock Arm® Cortex®-M7 @ 320 MHz |                                         |            |            |

| HSE_B<br>Crypto Security Engine                                                           | 2 x motor control coprocessor (2x 16ch)    |                                               |                                                         | 2 x motor control coprocessor (2x 32ch) |            |            |

| FOTA<br>(Firmware Over-the-Air)                                                           | 4 MB Flash                                 | 6 MB Flash                                    | 4 MB Flash                                              | 6 MB Flash                              | 4 MB Flash | 6 MB Flash |

| Low-Power Operating Modes and Peripherals (LPUART, FlexIO)                                | 704 KB SRAM (incl. 192 KB TCM)             |                                               | 800 KB SRAM (incl. 288 KB TCM)                          |                                         |            |            |

| ASIL D Safety:<br>(ECC Memories, MPU, CRC, Watchdogs)                                     |                                            | 127/ 209+8LVDS I/Os                           | 64-ch eDMA with 32ch LockStep                           |                                         |            |            |

| eMIOS Timers<br>Logic Control Unit<br>Body Cross Triggering Unit<br>Trigger Mux           |                                            | 6 x CAN (FD)                                  | 100 Mbit/s Ethernet (AVB/TSN)                           |                                         |            |            |

| Debug/Trace (SWD/JTAG/ETB)                                                                |                                            | ZipWire                                       |                                                         |                                         |            |            |

| S32 Design Studio IDE<br>S32 Configuration Tool                                           | 2 x sigma-delta ADC with programmable DSP  |                                               | 4 x sigma-delta ADC with programmable DSP               |                                         |            |            |

| Real-Time Drivers (AUTOSAR® and Non-AUTOSAR)                                              | 4 x 12-bit SAR-ADC (48 inputs)             |                                               | 7 x 12-bit SAR-ADC (69 inputs)                          |                                         |            |            |

| Security F/W<br>Safety Software Framework<br>Communication Stacks<br>Application Software |                                            | 2x Sine Wave Generator, 2 x Analog Comparator | Quad SPI (8-bit data width, SDR and DDR mode)           |                                         |            |            |

| ASIL-D SW Resolver, IPCF, MBDT                                                            |                                            |                                               | LQFP-EP-176                                             |                                         |            |            |

|                                                                                           |                                            |                                               | MAPBGA-289                                              |                                         |            |            |

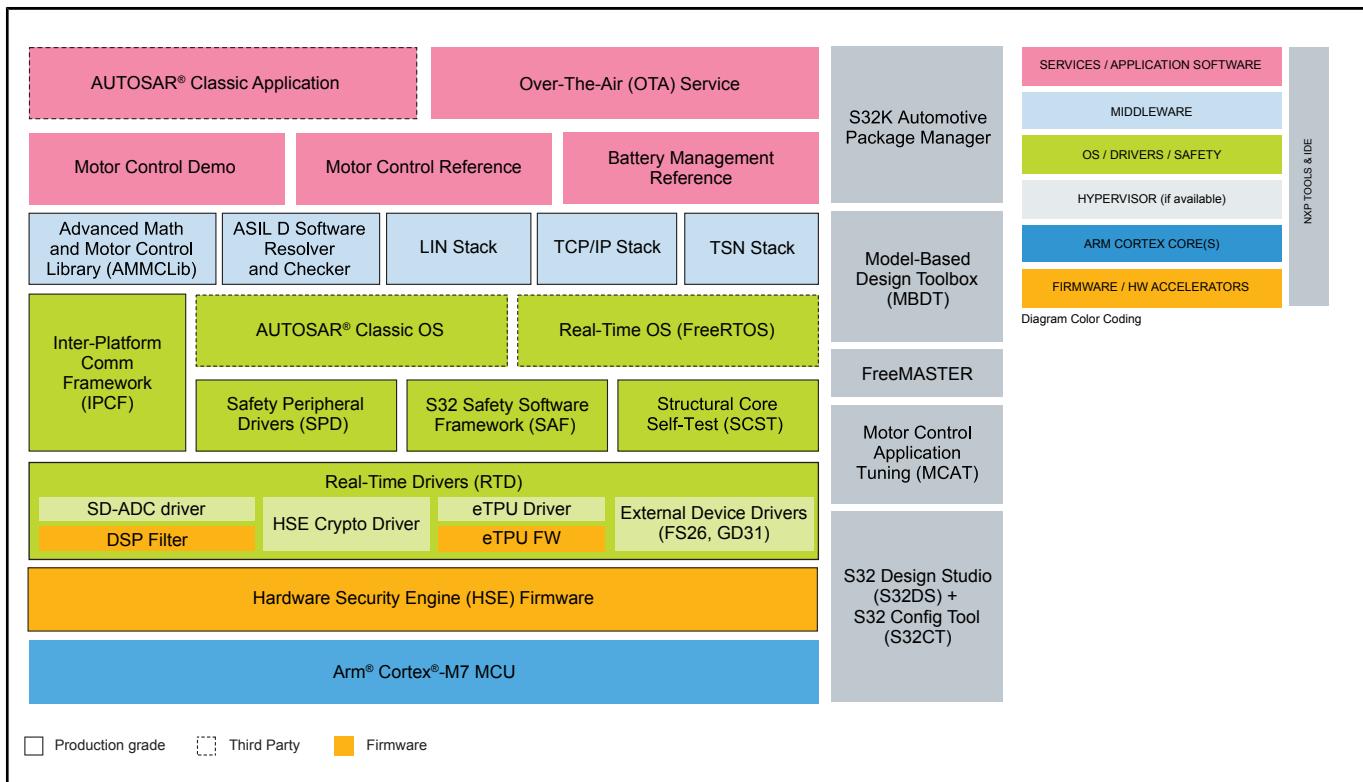

## S32K39/37/36 Software Enablement Block Diagram

View additional information for [S32K39/37/36 Microcontrollers for Electrification Applications](#).

**Note:** The information on this document is subject to change without notice.

[www.nxp.com](http://www.nxp.com)

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2026 NXP B.V.