## **Full NFC Frontend**

## PN512AA0HN1

Last Updated: Mar 18, 2024

PN512 is a broadly adopted NFC frontend - powering more than 10 billion NFC transactions per year.

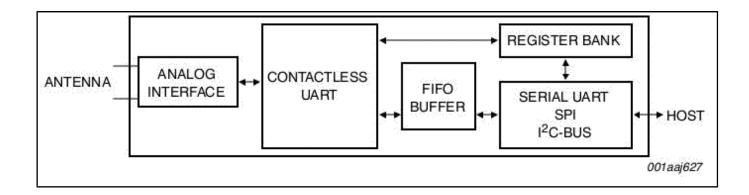

It is a highly integrated NFC frontend for contactless communication at 13.56 MHz. This NFC frontend utilizes an outstanding modulation and demodulation concept completely integrated for different kinds of contactless communication methods and protocols at 13.56 MHz.

The PN512 NFC frontend supports 4 different operating modes:

- Reader/Writer mode supporting ISO/IEC 14443A, MIFARE products and FeliCa scheme

- Reader/Writer mode supporting ISO/IEC 14443B

- Card Operation mode supporting ISO/IEC 14443A, MIFARE products and FeliCa scheme

- NFCIP-1 mode

Enabled in Reader/Writer mode for ISO/IEC 14443A/MIFARE, the PN512's internal transmitter part is able to drive a reader/writer antenna designed to communicate with ISO/IEC 14443A/ MIFARE cards and transponders without additional active circuitry. The receiver part provides a robust and efficient implementation of a demodulation and decoding circuitry for signals from ISO/IEC 14443A/MIFARE compatible cards and transponders. The digital part handles the complete ISO/IEC 14443A framing and error detection (Parity and CRC).

Enabled in Reader/Writer mode for FeliCa, the PN512 NFC frontend supports the FeliCa communication scheme. The receiver part provides a robust and efficient implementation of the demodulation and decoding circuitry for FeliCa coded signals. The digital part handles the FeliCa framing and error detection like CRC. The PN512 supports contactless communication using FeliCa Higher transfer speeds up to 424 kbit/s in both directions.

The PN512 supports all layers of the ISO/IEC 14443B reader/writer communication scheme, given correct implementation of additional components, like oscillator, power supply, coil etc.

and provided that standardized protocols, e.g. like ISO/IEC 14443-4 and/or ISO/IEC 14443B anticollision are correctly implemented.

In Card Operation mode, the PN512 NFC frontend is able to answer to a reader/writer command either according to the FeliCa or ISO/IEC 14443A/MIFARE card interface scheme. The PN512 generates the digital load modulated signals and in addition with an external circuit the answer can be sent back to the reader/writer. A complete card functionality is only possible in combination with a secure IC using the S<sup>2</sup>C interface.

Additionally, the PN512 NFC frontend offers the possibility to communicate directly to an NFCIP-1 device in the NFCIP-1 mode. The NFCIP-1 mode offers different communication mode and transfer speeds up to 424 kbit/s according to the Ecma 340 and ISO/IEC 18092 NFCIP-1 Standard. The digital part handles the complete NFCIP-1 framing and error detection.

Various host controller interfaces are implemented:

- 8-bit parallel interface

- SPI interface

- serial UART (similar to RS232 with voltage levels according pad voltage supply)

- I<sup>2</sup>C interface

Different available versions

The PN512 is available in three versions:

- PN5120A0HN1/C2 (HVQFN32), PN5120A0HN/C2 (HVQFN40) and PN5120A0ET/C2 (TFBGA64), hereafter named as version 2.0

- PN512AA0HN1/C2 (HVQFN32) and PN512AA0HN1/C2BI (HVQFN32 with Burn In), hereafter named as industrial version, fulfilling the automotive qualification stated in AEC-Q100 grade 3 from the Automotive Electronics Council, defining the critical stress test qualification for automotive integrated circuits (ICs).

- PN5120A0HN1/C1(HVQFN32) and PN5120A0HN/C1 (HVQFN40), hereafter named as version 1.0

## View additional information for Full NFC Frontend.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.