June 24, 2010

# **Exploring Options for DDR Memory Interleaving**

FTF-NET-F0401

### Kelley Oswalt Applications Engineer

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorIQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

**Objective**

Discover benefits of interleaving and all the available options for programming interleaving on the DDR controller for devices with single and dual memory controllers.

- Chip select interleaving

- Memory controller interleaving

- Difference between cache line, page, bank and super bank interleaving

- ► How to program the memory mapped registers for each type of interleaving

- 1. DDR memory space organization overview

- 2. Review components of an address issued to DDR SDRAM

- 3. Discuss interleaving with a single memory controller

- Chip Select (Bank) Interleaving

- 4. Discuss interleaving with dual memory controllers

- Chip Select (Bank) Interleaving

- Memory Controller Interleaving

- Cache line interleaving

- Page interleaving

- Bank interleaving

- Super-bank interleaving

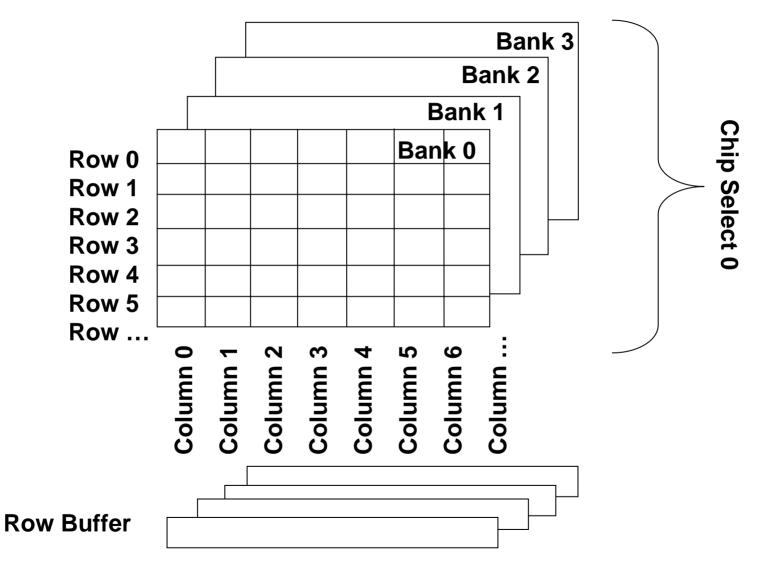

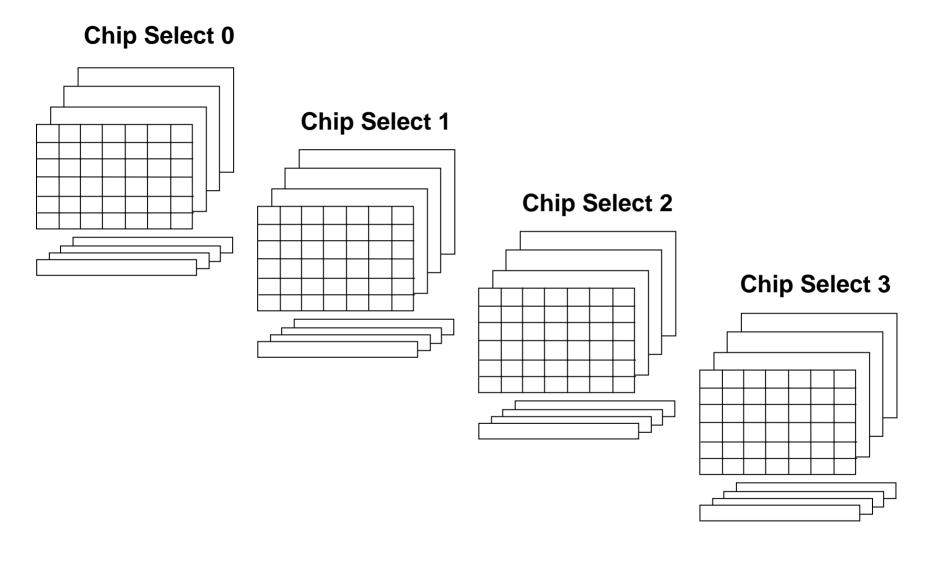

#### **Memory Space Organization**

Freescale, the Freescale logo, AliVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, Qorld, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

### **Memory Space Organization**

- Byte offset (O)—Always 3 bits

- Column select (C)—Varies depending on device size and memory type

- Bank select (B)—2 or 3 bits, depending on device size (4 or 8 sub-banks)

- Row select (R)—Varies depending on device size

- Chip select (S)—1 or 2 bits, depending on number chip selects used (1-4)

For example, a device with 32-bit address space, one memory controller, 4 chip selects, 14 rows, 10 columns and 4 sub-banks would use the bit allocations shown in the figure below.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| - | S | S | R | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0  | 0  | 0  |

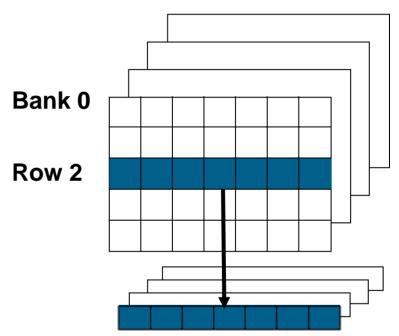

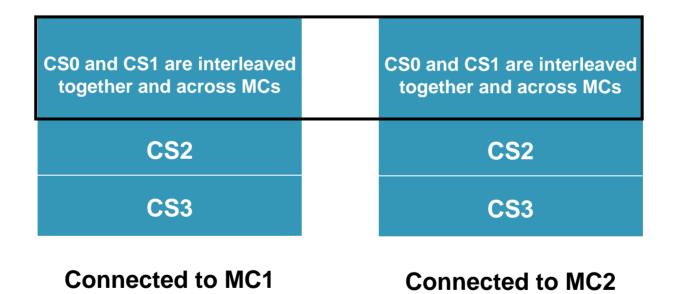

# Stage One of a DRAM Read/Write Operation

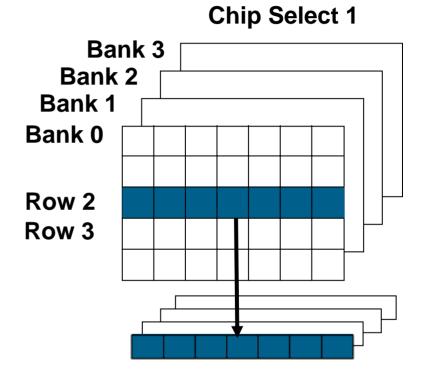

Active Command – Chip Select (S bits), Bank (B bits) and Row (R bits) of address are used to open a page of memory into a buffer so that a *read* or *write* can occur (one page is usually 1K)

**Chip Select 1**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QORIQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

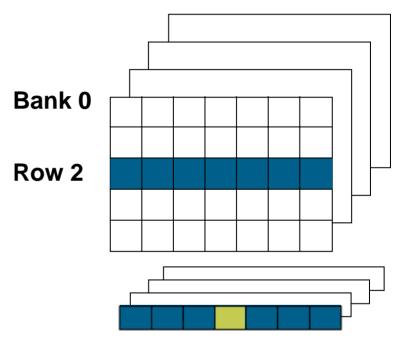

# Stage Two of a DRAM Read/Write Operation

Read/Write – Columns

(C bits) are used during the read/write command to point to the specific address within an open page for the read/write operation

Pages remain open in the buffer until a different page needs to be opened to access a different address.

Freescale, the Freescale logo, AliVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Hiskis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

## **Overview of Interleaving**

- Interleaving re-arranges the address bits such that the probability of hitting an open page is more likely

- Pages remain open in the buffer until a different page needs to be opened to access a different address. Reducing the number of times pages are opened and closed increases performance

- Instead of writing software that can predict which pages are open at certain times to increase *read/write* address hits, hardware can help do this.

## Interleaving with a Single Memory Controller

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VoriiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Chip Select Interleaving**

- For devices that have a single memory controller, Chip Select Interleaving is the only type of interleaving available.

- The memory controller can be programmed to enable up to four chip selects.

- Chip Select Interleaving controls how these four chip selects are interleaved within the memory controller.

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beekti, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, Qorld, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Components of an Address with Interleaving**

#### Without Interleaving:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| - | S | S | R | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0  | 0  | 0  |

With Chip Select Interleaving:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| - | R | R | R | R | R | R | R | R | R | R  | R  | R  | R  | R  | S  | S  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0  | 0  | 0  |

When chip select interleaving is enabled, the memory controller automatically changes the arrangements of address components by moving the chip select bits to the left of the sub-bank bits.

### **Open and Closing Pages**

Any change to an address that only affects the Chip Select (S) bits or Bank (B) bits does not require the page to be closed and re-opened.

Any change to the Row (R) bits causes the open page to be closed and a new one to be opened.

# **Benefit of Interleaving**

Chip Select Interleaving creates a larger continuous memory space of open pages to operate within which improves performance.

Without Interleaving:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| - | S | S | R | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0  | 0  | 0  |

Address space = 0x0000\_XXXX

2^16 = 64 Kbit

With Chip Select Interleaving:

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| - | R | R | R | R | R | R | R | R | R | R  | R  | R  | R  | R  | S  | S  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0  | 0  | 0  |

Address space = 0x0000X\_XXXX

2^18 = 256 Kbit

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Flatform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

## **Transaction Flow with Interleaving**

- Reducing the number of times a page has to be closed and opened actually reduces the number of active commands that have to be sent.

- This allows the DDR controller to use the read/write stage of a transaction more often.

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Beekit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QOIQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Chip Select Interleaving Programming Constraints**

- The size of each chip select participating in chip select interleaving must be equal.

- The start and end address of the combined size of all the chip selects participating in interleaving must be entered in the lowest numbered CSn\_BNDS register.

- LAW must be set up to target interleaved memory.

- The type of chip select interleaving must be indicated in the DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] register.

There are four options within Chip Select Interleaving:

- 1. External memory chip selects 0 and 1 are interleaved

- 2. External memory chip selects 2 and 3 are interleaved

- 3. External memory chip selects 0 and 1 are interleaved together and chip selects 2 and 3 are interleaved together

- 4. External memory chip selects 0 through 3 are all interleaved together

**Interleaving Chip Selects 0 and 1**

# DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] = 1000000

CS0 and CS1 are interleaved together CS2 CS3

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerOUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

## **Interleaving Chip Selects 0 and 1**

#### Table 1. Register Setting for Interleaving Banks 0 and 1

| Register      | Field                 | Bit Setting  | Notes                                                                                |

|---------------|-----------------------|--------------|--------------------------------------------------------------------------------------|

| DDR_SDRAM_CFG | [BA_INTLV_CTL]        | 1000000      | External memory banks 0 and 1 are interleaved                                        |

|               | [CS_0_EN]             | 1            | Chip Select 0 is active and assumes the state set in CS0_BNDS                        |

| CS0_CONFIG    | All Other Fields Used | User Defined | All other fields in CS0_CONFIG are used                                              |

| CS1_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                      |

|               | [ODT_WR_CFG]          | User Defined | (the exception of [ODT_RD_CFG] and [ODT_WR_CFG])                                     |

| CS2_CONFIG    | All Fields Used       | User Defined | All fields in CS2_CONFIG are used if the third chip select is<br>enabled             |

| CS3_CONFIG    | All Fields Used       | User Defined | All fields in CS3_CONFIG are used if the fourth chip select is<br>enabled            |

| CS0_BNDS      | All Fields Used       | User Defined |                                                                                      |

| CS1_BNDS      | All Fields Unused     | _            | and end address in CS0_BNDS must be set to the combined<br>interleaved memory space. |

| CS2_BNDS      | All Fields Used       | User Defined | All fields in CS2_BNDS are used if the third chip select is enabled in CS2_CONFIG    |

| CS3_BNDS      | All Fields Used       | User Defined | All fields in CS3_BNDS are used if the fourth chip select is enabled in CS3_CONFIG   |

**Interleaving Chip Selects 2 and 3**

# DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] = 0100000

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerOUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

## **Interleaving Chip Selects 2 and 3**

#### Table 2. Register Setting for Interleaving Banks 2 and 3

| Register      | Field                 | Bit Setting  | Notes                                                                                                          |

|---------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------|

| DDR_SDRAM_CFG | [BA_INTLV_CTL]        | 0100000      | External memory banks 2 and 3 are interleaved                                                                  |

| CS0_CONFIG    | All Fields Used       | User Defined | All fields in CS0_CONFIG are used if the first chip select is<br>enabled                                       |

| CS1_CONFIG    | All Fields Used       | User Defined | All fields in CS1_CONFIG are used if the second chip select is enabled                                         |

|               | [CS_2_EN]             | 1            | Chip Select 2 is active and assumes the state set in CS2_BNDS                                                  |

| CS2_CONFIG    | All Other Fields Used | User Defined | All other fields in CS2_CONFIG are used                                                                        |

|               | [CS_3_EN]             | Don't care   |                                                                                                                |

| CS3_CONFIG    | [ODT_RD_CFG]          | User Defined | All fields in CS2_CONFIG override all fields in CS3_CONFIG with the exception of [ODT_RD_CFG] and [ODT_WR_CFG] |

|               | [ODT_WR_CFG]          | User Defined |                                                                                                                |

| CS0_BNDS      | All Fields Used       | User Defined | All fields in CS0_BNDS are used if the first chip select is enabled in CS0_CONFIG                              |

| CS1_BNDS      | All Fields Used       | User Defined | All fields in CS1_BNDS are used if the second chip select is<br>enabled in CS1_CONFIG                          |

| CS2_BNDS      | All Fields Used       | User Defined |                                                                                                                |

| CS3_BNDS      | All Fields Unused     | —            | and end address in CS2_BNDS must be set to the combined<br>interleaved memory space.                           |

Freescale, the Freescale logo, AliVec, C-5, CodeTEST, CodeWarrior, ColdFree, C-Warer, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VoriiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

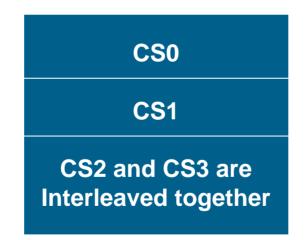

Interleaving CS 0 and 1 Together and CS 2 and 3 Together

# DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] = 1100000

CS0 and CS1 are Interleaved together

CS2 and CS3 are Interleaved together

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerOUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# Interleaving CS 0 and 1 Together and CS 2 and 3 Together

Table 3. Register Setting for Interleaving Banks 0 and 1 as well as Banks 2 and 3

| Register      | Field                 | Bit Setting  | Notes                                                                                                        |

|---------------|-----------------------|--------------|--------------------------------------------------------------------------------------------------------------|

| DDR_SDRAM_CFG | [BA_INTLV_CTL]        | 1100000      | External memory banks 0 and 1 are interleaved together and banks 2 and 3 are interleaved together            |

|               | [CS_0_EN]             | 1            | Chip Select 0 is active and assumes the state set in CS0_BNDS                                                |

| CS0_CONFIG    | All Other Fields Used | User Defined | All other fields in CS0_CONFIG are used                                                                      |

| CS1_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                                              |

|               | [ODT_WR_CFG]          | User Defined | (the exception of [ODT_RD_CFG] and [ODT_WR_CFG]                                                              |

|               | [CS_2_EN]             | 1            | Chip Select 2 is active and assumes the state set in CS2_BNDS                                                |

| CS2_CONFIG    | All Other Fields Used | User Defined | All other fields in CS2_CONFIG are used                                                                      |

| CS3_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                                              |

|               | [ODT_WR_CFG]          | User Defined | <pre>(the exception of [ODT_RD_CFG] and [ODT_WR_CFG])</pre>                                                  |

| CS0_BNDS      | All Fields Used       | User Defined |                                                                                                              |

| CS1_BNDS      | All Fields Unused     | _            | and end address in CS0_BNDS must be set to the combined interleaved memory space shared between CS0 and CS1. |

| CS2_BNDS      | All Fields Used       | User Defined |                                                                                                              |

| CS3_BNDS      | All Fields Unused     | _            | and end address in CS2_BNDS must be set to the combined interleaved memory space shared between CS2 and CS3. |

Freescale, the Freescale logo, AliVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, OorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

**Interleaving Chip Select 0 through 3**

# DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] = xx00100

CS0 through CS3 are Interleaved together

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerOUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processon Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Interleaving Chip Select 0 through 3**

#### Table 4. Register Setting for Interleaving Banks 0 through 3

| Register      | Field                 | Bit Setting  | Notes                                                                                                          |

|---------------|-----------------------|--------------|----------------------------------------------------------------------------------------------------------------|

| DDR_SDRAM_CFG | [BA_INTLV_CTL]        | xx00100      | External memory banks 0 through 3 are all interleaved together                                                 |

|               | [CS_0_EN]             | 1            | Chip Select 0 is active and assumes the state set in CS0_BNDS                                                  |

| CS0_CONFIG    | All Other Fields Used | User Defined | All other fields in CS0_CONFIG are used                                                                        |

| CS1_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                                                |

|               | [ODT_WR_CFG]          | User Defined | the exception of [ODT_RD_CFG] and [ODT_WR_CFG]                                                                 |

| CS2_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                                                |

|               | [ODT_WR_CFG]          | User Defined | the exception of [ODT_RD_CFG] and [ODT_WR_CFG]                                                                 |

| CS3_CONFIG    | [ODT_RD_CFG]          | User Defined |                                                                                                                |

|               | [ODT_WR_CFG]          | User Defined | the exception of [ODT_RD_CFG] and [ODT_WR_CFG]                                                                 |

| CS0_BNDS      | All Fields Used       | User Defined |                                                                                                                |

| CS1_BNDS      | All Fields Unused     | _            | CS2_BNDS and CS3_BNDS. The start and end address in<br>CS0_BNDS must be set to the combined interleaved memory |

| CS2_BNDS      | All Fields Unused     | _            | space.                                                                                                         |

| CS3_BNDS      | All Fields Unused     |              |                                                                                                                |

### **Interleaving with Dual Memory Controllers**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VoriiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Types of Interleaving**

- Chip Select Interleaving

- Can be enabled on either or both controllers

- Behaves exactly like single memory controller interleaving

- Benefits are exactly the same as a single memory controller

- Memory Controller Interleaving

- Only available with dual memory controllers

- Chip Select and Memory Controller Interleaving combined

- Byte offset (O)—Always 3 bits

- Column select (C)—Varies depending on device size and memory type

- ► Bank select (B)—2 or 3 bits, depending on device size (4 or 8 sub-banks)

- Row select (R)—Varies depending on device size

- Chip select (S)—1 or 2 bits, depending on number chip selects used (1-4)

- Memory Controller (M) 1 bit, depending on number of memory controllers used

For example, a device with 36-bit address space, two memory controllers, 4 chip selects, 14 rows, 10 columns and 4 sub-banks would use the bit allocations shown in the figure below.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | - | - | М | S | S | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | R  | R  | R  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

# **Memory Controller Interleaving Types**

- The memory controller (M) bit location in the address is programmable

- Cache-line interleaving

- Page interleaving

- Bank interleaving

- Super-bank interleaving

- Memory Controller Interleaving is combined with Chip Select interleaving if multiple chip selects are desired to participate in memory controller interleaving

- Without chip select interleaving, only CS0 from memory controller 1 will be interleaving with CS0 from memory controller 2

- Bit 29 (64 byte cache line devices)/30 (32 byte cache line devices) of the 36-bit physical address is used to select the memory controller

- Every cache-line transfer switches between each memory controller to increase bandwidth which improves performance

- Re-arranging the M bit also increases the continuous memory space by a power of 2

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | I | - | S | S | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | R  | R  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | М  | С  | С  | 0     |

#### With Chip Select Interleaving Enabled

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | I | - | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | S  | S  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | Μ  | С  | С  | 0     |

- The bit used to select the memory controller is the bit to the left of the highest-order column bits

- Every page line transfer switches between each memory controller

- Re-arranging the M bit also increases the continuous memory space by a power of 2

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | - | - | S | S | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | R  | R  | В  | В  | Μ  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

### With Chip Select Interleaving Enabled

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | - | - | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | S  | S  | В  | В  | Μ  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

## **Bank Interleaving**

- The bit used to select the memory controller is the bit to the left of the bank select bits, which are to the left of the highest-order column bits

- Every bank transfer switches between each memory controller

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | - | - | s | s | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | R  | R  | Μ  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

With Chip Select Interleaving Enabled

| 0 | ) 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|-----|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | -   | - | - | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | S  | S  | М  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

# **Super-bank Interleaving**

- The bit used to select the memory controller is the bit to the left of the Chip Select interleaved bits

- Chip Select Interleaving must be enabled with this mode

- Very similar to Bank interleaving with Chip Select interleaving enabled

- Difference is which bit is used to switch between memory controllers

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33-35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| - | - | - | - | R | R | R | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  | Μ  | S  | S  | В  | В  | С  | С  | С  | С  | С  | С  | С  | С  | С  | С  | 0     |

## **Memory Controller Interleaving Only**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerOUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

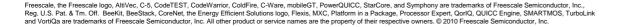

| CS0 interleaved across MCs                 | CS0 interleaved across MCs                 |

|--------------------------------------------|--------------------------------------------|

| CS1 is not interleaved                     | CS1 is not interleaved                     |

| CS2 and CS3 are<br>Interleaved<br>together | CS2 and CS3 are<br>Interleaved<br>together |

|                                            | _                                          |

**Connected to MC2**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, OorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

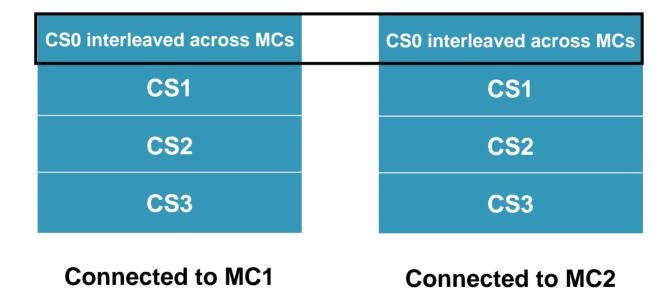

| CS0 and CS1 are interleaved together and across MCs | CS0 and CS1 are interleaved<br>together and across MCs |

|-----------------------------------------------------|--------------------------------------------------------|

| CS2 and CS3 are<br>Interleaved<br>together          | CS2 and CS3 are<br>Interleaved<br>together             |

| Connected to MC1                                    | Connected to MC2                                       |

Freescale, the Freescale logo, Atilvec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

CS0 through CS3 are Interleaved together and across MCs CS0 through CS3 are Interleaved together and across MCs

**Connected to MC1**

**Connected to MC2**

Freescale, the Freescale logo, AlliVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerQUICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2010 Freescale Semiconductor, Inc.

# **Memory Controller Interleaving Programming Constraints**

- CS0 of both memory controllers must be included in the two memory controller interleaving.

- The interleaved DDR LAW must be programmed for the memory space interleaved between the two memory controllers.

- A LAW for each memory controller must be programmed for the memory space not interleaved between the memory controllers.

- The size of chip selects participating in interleaving must be equal.

- The start and end address of combined size of all the chip selects participating in interleaving must be entered in the CS0\_BNDS register of both memory controllers.

- The combined memory space participating in the two memory controller interleaving must be continuous.

- When chip selects other than CS0 are to be interleaved, the chip selects must be combined by setting the correct type of chip select interleaving in the DDR\_SDRAM\_CFG[BA\_INTLV\_CTL] register.

- Finally the memory controller interleaving must be enabled and its type selected in the CS0\_CONFIG register of both memory controllers.

# Selecting the Type of Interleaving

Determining which type of interleaving will provide the best performance is achieved by examining the specific application under the available interleaving types and letting the performance results point to the best type.

- AN3939 "DDR Interleaving for PowerQUICC and QorIQ Processors"

- http://cache.freescale.com/files/32bit/doc/app\_note/AN3939.pdf?fpsp= 1&WT\_TYPE=Application Notes&WT\_VENDOR=FREESCALE&WT\_FILE\_FORMAT=pdf&WT\_ ASSET=Documentation

### **Memory Space Organization**

Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, C-Ware, mobileGT, PowerdUIICC, StarCore, and Symphony are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. BeeKit, BeeStack, CoreNet, the Energy Efficient Solutions logo, Flexis, MXC, Platform in a Package, Processor Expert, QorlQ, QUICC Engine, SMARTMOS, TurboLink and VortiQa are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. @ 2010 Freescale Semiconductor, Inc.