**AN11545** BGA3023 - 1.2 GHz 20 dB gain CATV amplifier Rev. 1 — 16 September 2014

**Application note**

#### **Document information**

| Info     | Content                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| Keywords | BGA3023, Evaluation board, CATV, Medium Power                                                                                 |

| Abstract | This application note describes the schematic and layout requirements for using the BGA3023 as a CATV medium power amplifier. |

#### **Revision history**

| Rev | Date     | Description       |

|-----|----------|-------------------|

| 1   | 20140916 | First publication |

# **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN11545

All information provided in this document is subject to legal disclaimers.

### 1. Introduction

The BGA3023 customer evaluation board enables the user to evaluate the performance of the medium power wideband CATV MMIC amplifier BGA3023.

The BGA3023 performance information is available in the BGA3023 datasheet.

This application note describes the evaluation board schematic and layout requirements for using the BGA3023 as a CATV medium power amplifier between 40 MHz and 1200 MHz. The BGA3023 is fabricated in the BiCMOS process and packaged in a lead-free 8-pin SOT786-2 package. The BGA3023 is surface-mounted on an evaluation board with element matching and DC decoupling circuitry. The amplifier MMIC comprises a push-pull amplifier with internal bias network and operates over a frequency range of 40 MHz to 1200 MHz with a supply voltage between 5 V and 8 V.

### 2. System features

- 20 dB gain

- Internally biased and internal integrated feedback

- Frequency range of 40 MHz to 1200 MHz

- High linearity with an IP3o of 47 dBm and IP2o of 85 dBm

- Operating from 5 V to 8 V supply

- High gain output 1 dB compression point of 30 dBm

- 75  $\Omega$  input and output impedance

- Unconditionally stable

- Icc(tot) can be controlled between 175 mA and 350 mA

### 3. Customer evaluation kit contents

The evaluation kit contains the following items:

- ESD safe casing

- BGA3023 evaluation board

### 4. Application Information

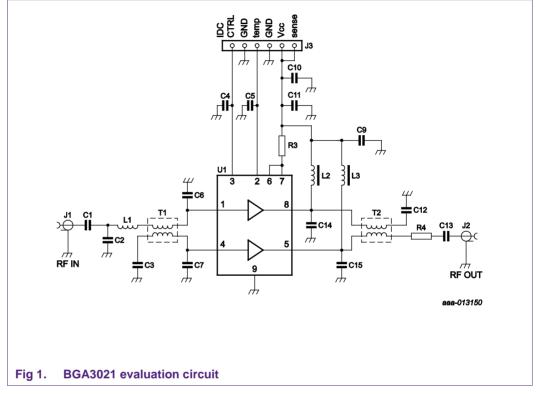

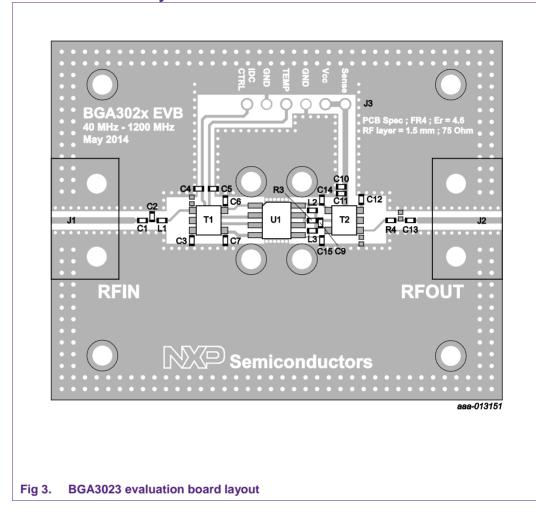

For evaluation purposes an evaluation board is available. The evaluation circuit can be seen in figure 1 and the corresponding PCB is shown in figure 2. Table 1 shows the bill of materials.

### 4.1 Evaluation board circuit

The power supply is applied on the Vcc pin of connector J3 and is applied to the BGA3023 via chokes L2 and L3 which provides RF blocking to the supply line. Capacitors C9, C10 and C11 are supply decoupling capacitors, where C4 and C5 are decoupling capacitors for the control lines.

At the F-connector J1 the RF input signal is applied where capacitor C1 provides DCblocking, followed by C2 and L1 for input matching (Z = 75  $\Omega$ ). The single ended unbalanced 75  $\Omega$  signal is converted into a balanced signal for push pull configuration. The balanced signal is applied to the input of BGA3023 at pin 1 and pin 4. Capacitor C3 provides DC-blocking. Capacitors C6 and C7 add extra capacitance to the output of balun T1, which results in improved input matching.

At the output the amplified balanced signal are converted back into one 75  $\Omega$  single ended signal by balun T2. Capacitors C14 and C15 add extra capacitance to the balun for improved impedance matching. Capacitors C12 and C13 are DC-blocking capacitors. Resistor R4 is a 0  $\Omega$  jumper and has no function other than passing the RF signal.

Resistor R3 provides a protection against damaging the internal crowbar due to overshoot of the supply during switch on or switch off. This resistors needs to be in the circuit to guarantee resistance against electrical overstress.

AN11545

The lcc can be controlled via the IDC CTRL pin of connector J3. The high current mode (350 mA) can be selected by leaving the IDC CTRL pin open or by applying 3.3V.The low current mode can be selected by applying 0 V to the IDC CTRL pin.

The Temp pin on connector J3 gives access to an internal temperature sense diode which can be used to verify proper thermal connection of the exposed die pad. The use of this function is described in chapter 4.3

### 4.2 Choice of balun

The choice of balun is important when the maximum performance needs to be achieved, especially on input and output return loss. Investigation showed that to get the best output performance, balun type MABA-010245 should be used. This balun gives a good output return loss and because of its low losses also give maximum P1dB, IP2 and IP3 levels.

However, balun type MABA-010245 does not give the best input return loss. Balun type MABA-007159 with slightly more losses gives a much better input return loss. The extra losses do not have any impact on the distortion values as it is placed at the input of the device. The noise figure will slightly increase but is not a problem as the BGA3023 will be used as final amplifier. For a system solution with low noise and more total gain the BGA3018 can be used in front of the BGA3023.

Baluns also play a big role in the frequency coverage range. For frequencies lower than 40 MHz the BGA3023 can be made to work with the use of MABA-007532. Lab samples show functionality between 5 MHz and 200 MHz with the use of MABA-007532 at the input and output.

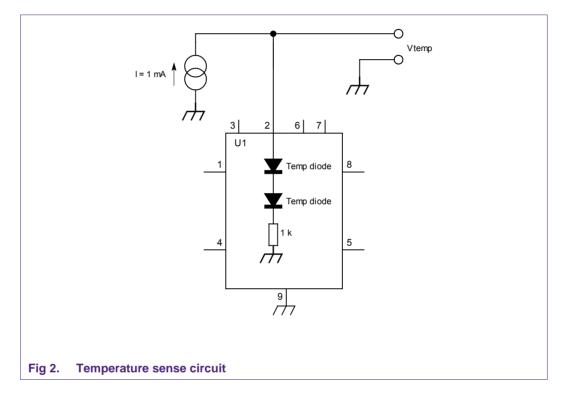

### 4.3 Temperature sense

Pin 2 of the BGA3023 gives access to a thermal diode which can be used to measure the temperature increase between power-off state and power-on state. This can be very helpful to check if the exposed die-pad has a good solder connection to the circuit board. In case the solder connection has thermal voids a rapid increase in temperature can be noticed.

A proposed circuit can be seen in fig 2.

During the whole test procedure a 1 mA current should be applied at pin 2. The Voltage level Vtemp will represent the actual die temperature.

To check for any thermal solder voids the following procedure need to be followed:

Step 1: At power-off state and in room temperature measure Vtemp

Step 2: Power on the device

Step 3: Wait 1 second to let the device heat up.

Step 4: Measure Vtemp again

Step 5: Switch off power

The Vtemp Voltage difference between power-off and power-on will be about 200mV for a device without thermal voids. When the Voltage difference is higher the thermal connection is not good and performance cannot be guaranteed.

AN11545

#### For optimum distortion performance it is important to have enough ground vias underneath and around the MMICs ground pins. This lowers the inductance to the ground plane. The evaluation board is made with two layer FR4 material.

### 4.4 Evaluation board layout

### 4.5 Bill of materials

| Table 1. Evaluation board BOM           |                      |     |         |                     |          |                          |

|-----------------------------------------|----------------------|-----|---------|---------------------|----------|--------------------------|

| Circuit<br>Reference                    | Description          | Qty | Mfr     | Manufacturer number | Supplier | Supplier part number     |

| C1, C3, C4,<br>C5, C9, C11,<br>C12, C13 | 10 nF                | 8   | Murata  | GRM155R71E103KA01D  | Digikey  | 490-1312-1-ND            |

| C2                                      | 0.47 pF              | 1   | Phycomp | 2238 869 14477      | Phycomp  | 2238 869 14477           |

| C8, C10                                 | 100 nF               | 2   | Murata  | GRM155R61A104KA01D  | Digikey  | 490-1318-2-ND            |

| C6, C7, C14,<br>C15                     | 1 pF                 | 4   | Murata  | GRM1555C1H1R0CA01D  | Digikey  | 490-3199-1-ND            |

| L1                                      | 1.0 nH               | 1   | Murata  | LQG15HS1N0S02D      | Digikey  | 490-2610-1-ND            |

| L2, L3                                  | Choke                | 2   | Murata  | BLM15HD182SN1D      | Digikey  | 490-5196-1-ND            |

| R1                                      | 3300 Ω               | 1   | Yageo   | RC0402FR-073K3L     | Digikey  | 311-3.30KLRTR-ND         |

| R2                                      | 4700 Ω               | 1   | Yageo   | RC0402FR-074K7L     | Digikey  | 311-4.7KLRTR-ND          |

| R3                                      | 15 Ω                 | 1   | Yageo   | RC0402FR-0715RL     | Digikey  | 311-15LRCT-ND            |

| R4                                      | $0 \ \Omega$ Jumper  | 1   | Murata  | RC0402JR-070RL      | Digikey  | 311-0.0JRTR-ND           |

| J1, J2                                  | 75 Ω F-<br>connector | 2   | Bomar   | 861V509ER6          | Mouser   | 678-861V509ER6           |

| J3                                      | Header 6-pin         | 1   | Molex   |                     | Digikey  | WM2748-ND                |

| T1                                      | Balun<br>transformer | 1   | MACOM   | MABA-007159-000000  | Mouser   | 937-<br>MABA007159000000 |

| T2                                      | Balun<br>transformer | 1   | MACOM   | MABA-010245-CT1160  | Mouser   | 937-<br>MABA010245CT1160 |

| U1                                      | BGA3023              | 1   | NXP     | BGA3023             | NXP      | BGA3023                  |

### 5. Measurement results

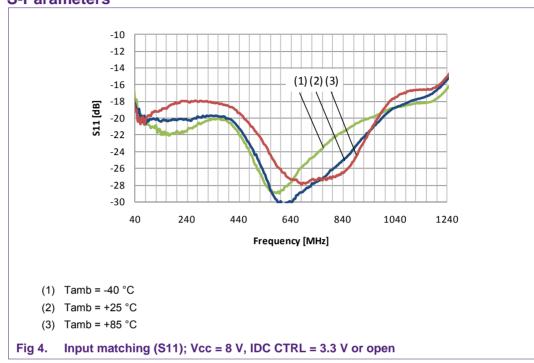

### 5.1 S-Parameters

AN11545

11 of 29

AN11545

AN11545

AN11545

AN11545

AN11545

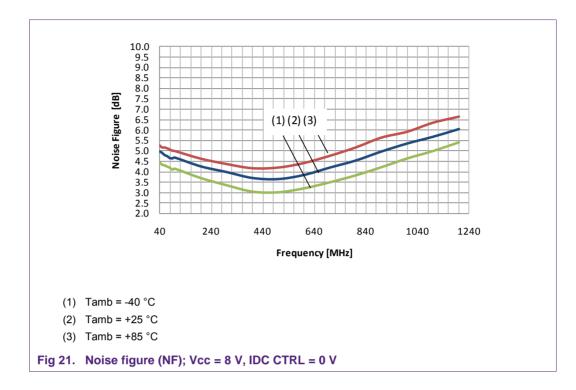

### 5.3 Noise figure

AN11545

AN11545

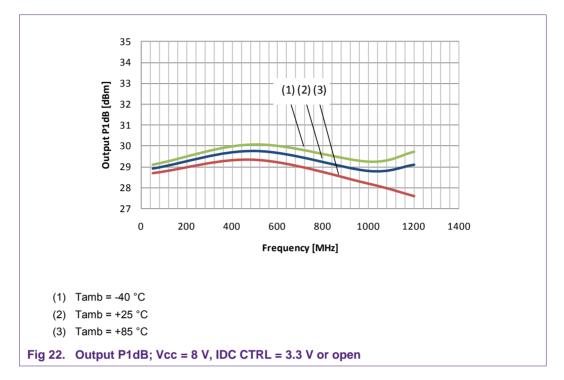

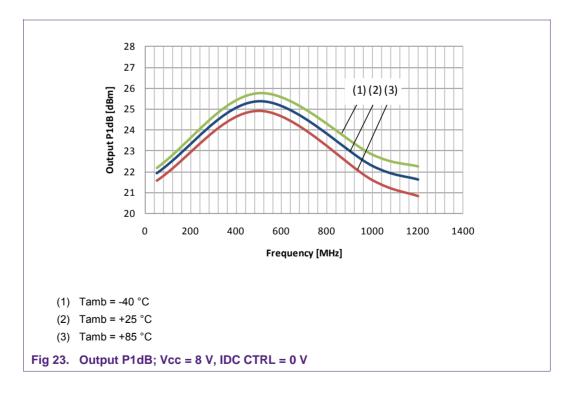

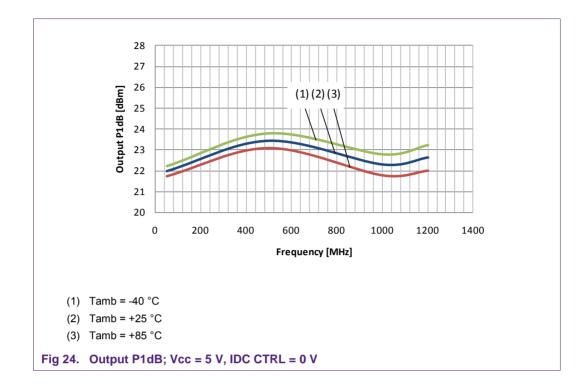

### 5.4 Output P1dB

AN11545

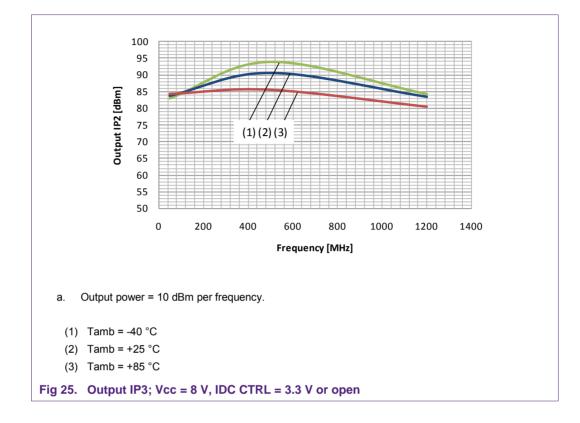

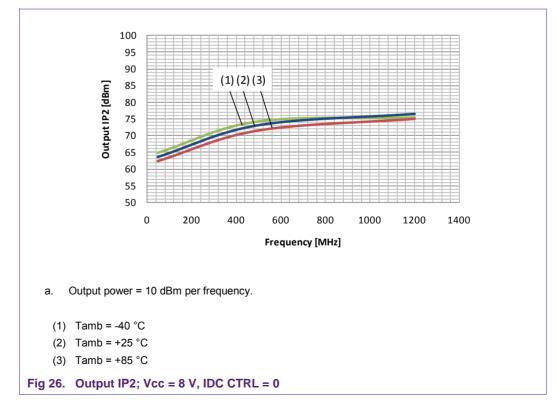

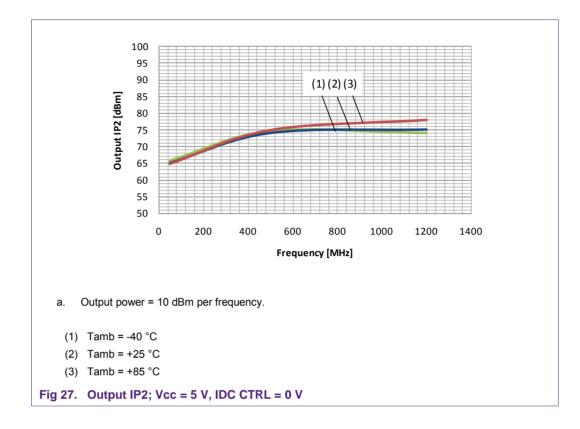

### 5.5 Output IP2

AN11545

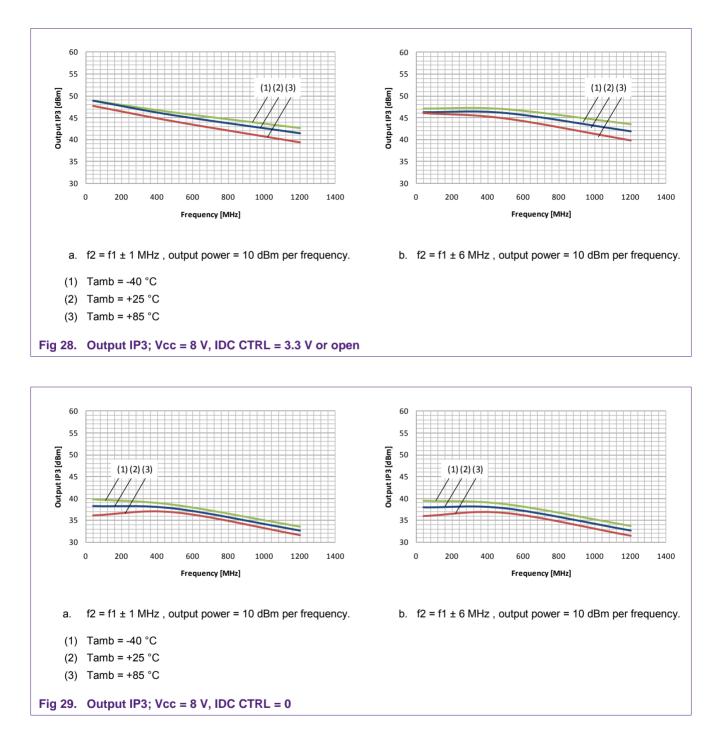

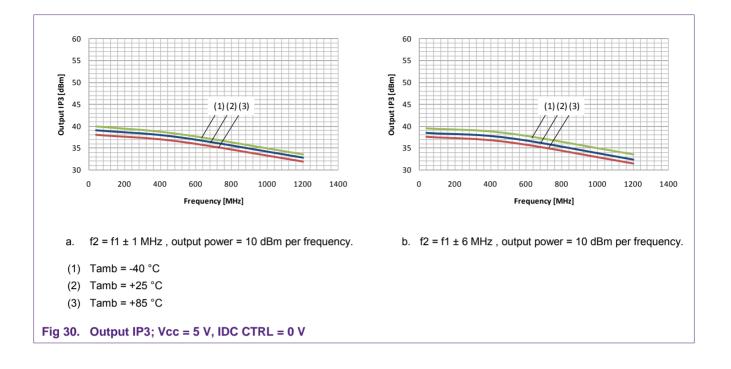

5.6 Output IP3

AN11545

# 6. Abbreviations

| Table 2. | Abbreviations                           |

|----------|-----------------------------------------|

| Acronym  | Description                             |

| AC       | Alternating Current                     |

| CATV     | Community Antenna TeleVision            |

| DC       | Direct Current                          |

| ESD      | Electro Static Discharge                |

| MMIC     | Monolithic Microwave Integrated Circuit |

| NTSC     | National Television Standards Committee |

| PCB      | Printed Circuit Board                   |

| RF       | Radio Frequency                         |

| SMD      | Surface Mounted Device                  |

# 7. Legal information

### 7.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 7.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP

Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

### 7.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

# 8. List of figures

| Fig 1.  | BGA3021 evaluation circuit                                 | 1 |

|---------|------------------------------------------------------------|---|

| Fig 2.  | Temperature sense circuit6                                 | 3 |

| Fig 3.  | BGA3023 evaluation board layout                            | 7 |

| Fig 4.  | Input matching (S11); Vcc = 8 V, IDC CTRL = 3.3 V or open  | 9 |

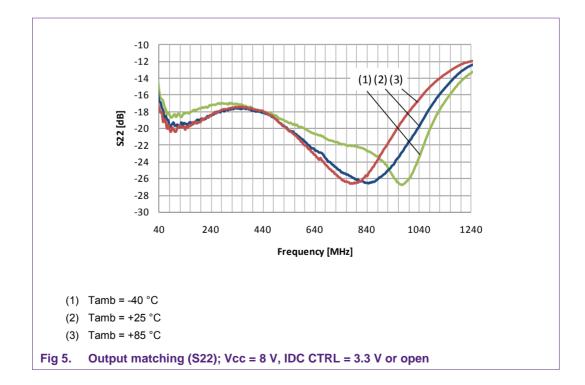

| Fig 5.  | Output matching (S22); Vcc = 8 V, IDC CTRL = 3.3 V or open |   |

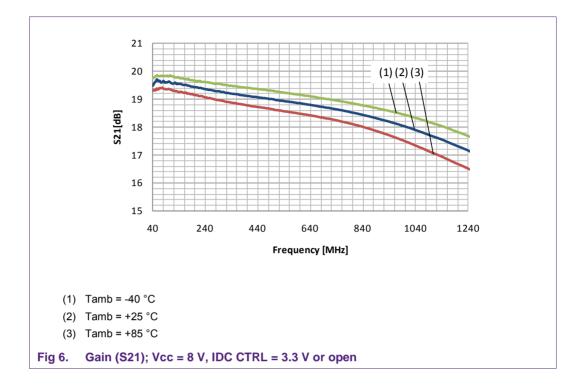

| Fig 6.  | Gain (S21); Vcc = 8 V, IDC CTRL = 3.3 V or<br>open         | ) |

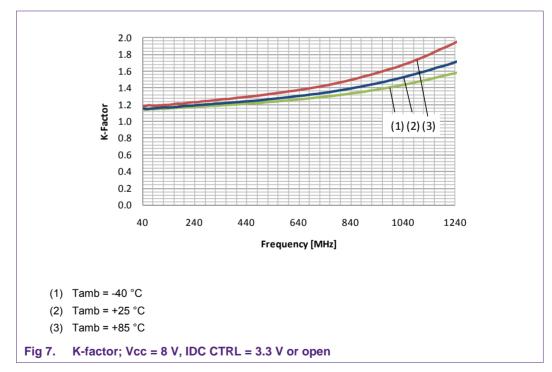

| Fig 7.  | K-factor; Vcc = 8 V, IDC CTRL = 3.3 V or open              | כ |

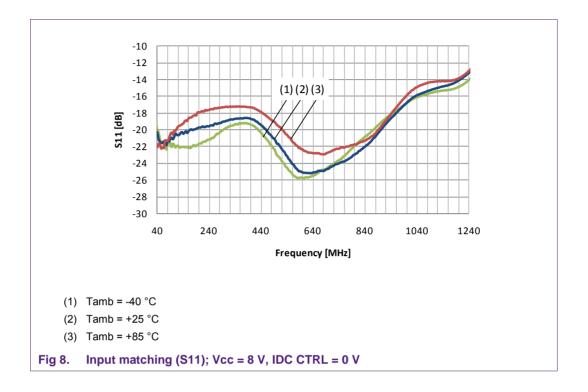

| Fig 8.  | Input matching (S11); Vcc = 8 V, IDC CTRL = 0<br>V1        |   |

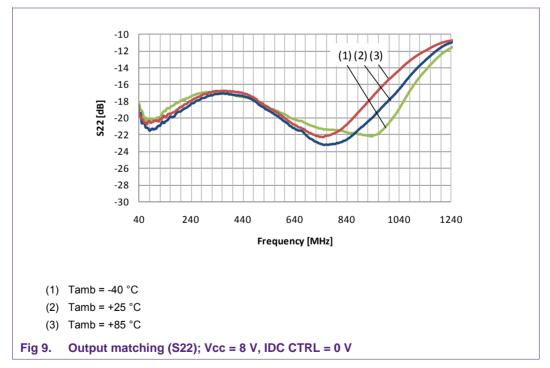

| Fig 9.  | Output matching (S22); Vcc = 8 V, IDC CTRL = 0 V           |   |

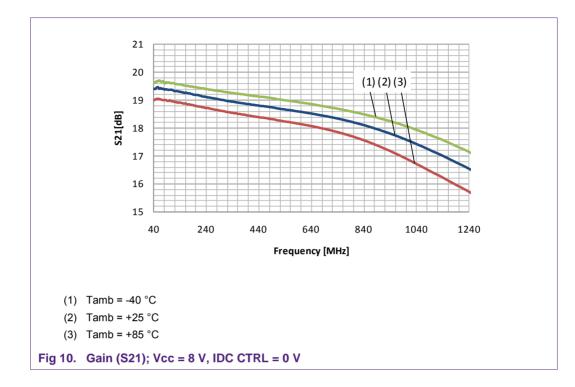

| Fig 10. | Gain (S21); Vcc = 8 V, IDC CTRL = 0 V                      | 2 |

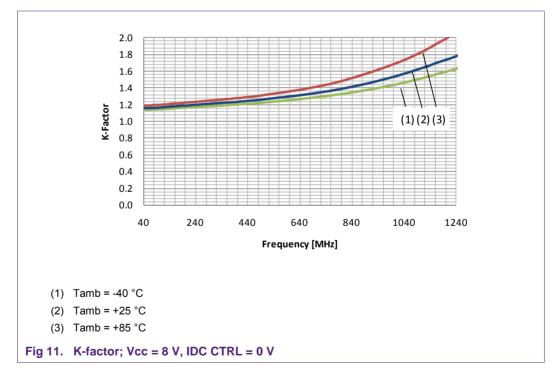

| Fig 11. | K-factor; Vcc = 8 V, IDC CTRL = 0 V12                      | 2 |

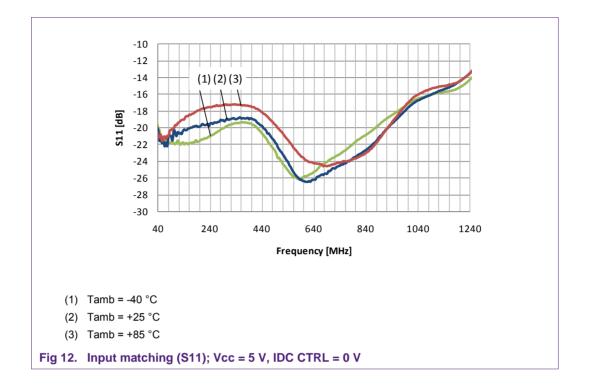

| Fig 12. | Input matching (S11); Vcc = 5 V, IDC CTRL = 0<br>V13       |   |

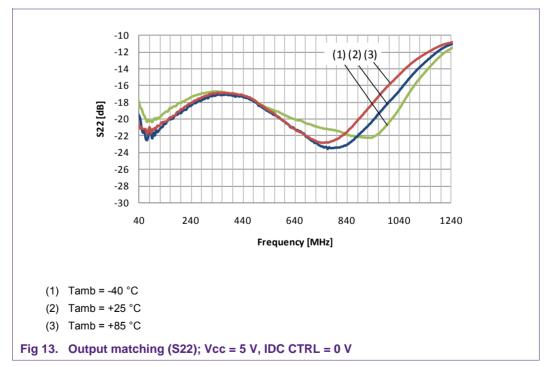

| Fig 13. | Output matching (S22); Vcc = 5 V, IDC CTRL =<br>0 V        |   |

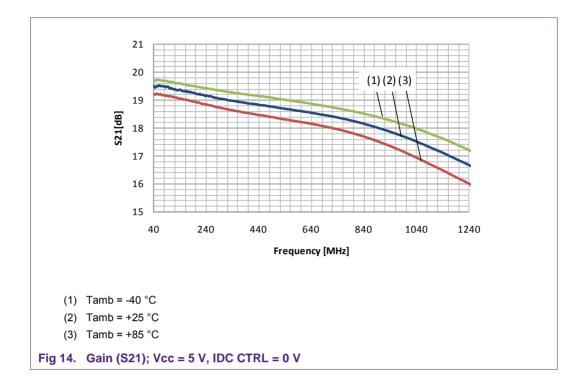

| Fig 14. | Gain (S21); Vcc = 5 V, IDC CTRL = 0 V14                    | 1 |

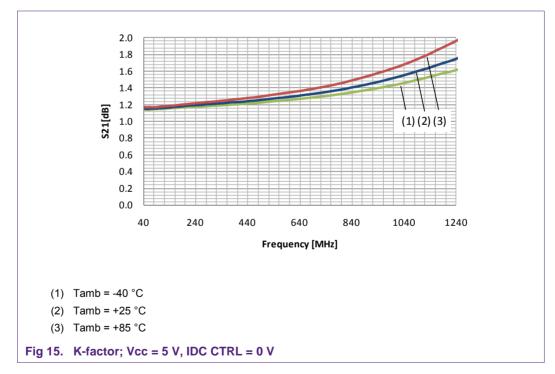

| Fig 15. | K-factor; Vcc = 5 V, IDC CTRL = 0 V14                      | 1 |

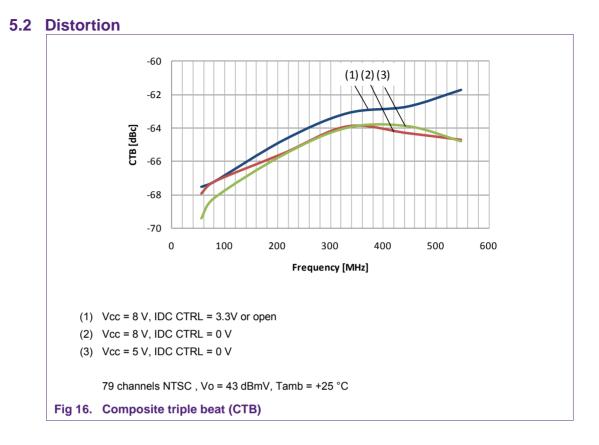

| Fig 16. | Composite triple beat (CTB)15                              | 5 |

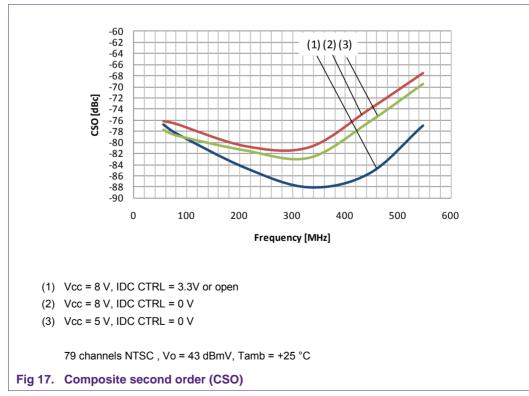

| Fig 17. | Composite second order (CSO)15                             |   |

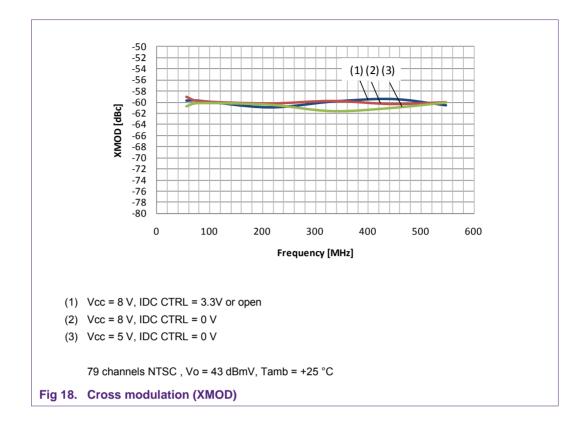

| Fig 18. | Cross modulation (XMOD)16                                  |   |

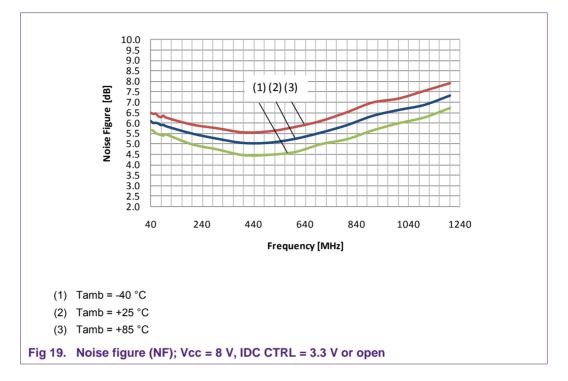

| Fig 19. | Noise figure (NF); Vcc = 8 V, IDC CTRL = 3.3 V<br>or open  |   |

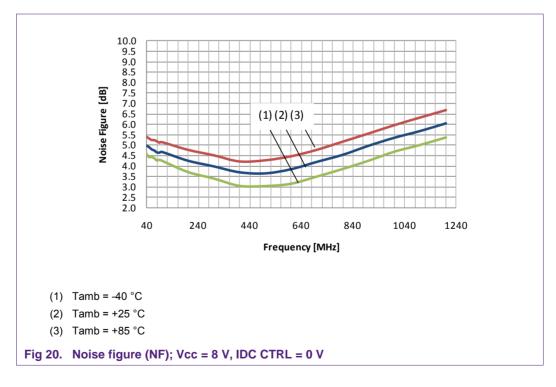

| Fig 20. | Noise figure (NF); Vcc = 8 V, IDC CTRL = 0 V17             | 7 |

| Fig 21. | Noise figure (NF); Vcc = 8 V, IDC CTRL = 0 V18             | 3 |

| Fig 22. | Output P1dB; Vcc = 8 V, IDC CTRL = 3.3 V or<br>open        | 9 |

| Fig 23. | Output P1dB; Vcc = 8 V, IDC CTRL = 0 V 19                  | 9 |

| Fig 24. | Output P1dB; Vcc = 5 V, IDC CTRL = 0 V20                   | ) |

| Fig 25. | Output IP3; Vcc = 8 V, IDC CTRL = 3.3 V or open            | 1 |

| Fig 26. | Output IP2; Vcc = 8 V, IDC CTRL = 027                      |   |

| Fig 27. | Output IP2; Vcc = 5 V, IDC CTRL = 0 V22                    | 2 |

| Fig 28. | Output IP3; Vcc = 8 V, IDC CTRL = 3.3 V or                 |   |

|         | open                                                       |   |

| Fig 29. | Output IP3; Vcc = 8 V, IDC CTRL = 023                      |   |

| Fig 30. | Output IP3; Vcc = 5 V, IDC CTRL = 0 V24                    | 1 |

# 9. List of tables

| Table 1. | Evaluation board BOM8 |

|----------|-----------------------|

| Table 2. | Abbreviations25       |

# 10. Contents

| 1.  | Introduction                     | 3  |

|-----|----------------------------------|----|

| 2.  | System features                  | 3  |

| 3.  | Customer evaluation kit contents | 3  |

| 4.  | Application Information          | 4  |

| 4.1 | Evaluation board circuit         | 4  |

| 4.2 | Choice of balun                  | 5  |

| 4.3 | Temperature sense                | 6  |

| 4.4 | Evaluation board layout          | 7  |

| 4.5 | Bill of materials                | 8  |

| 5.  | Measurement results              | 9  |

| 5.1 | S-Parameters                     | 9  |

| 5.2 | Distortion                       | 15 |

| 5.3 | Noise figure                     | 17 |

| 5.4 | Output P1dB                      | 19 |

| 5.5 | Output IP2                       | 21 |

| 5.6 | Output IP3                       | 23 |

| 6.  | Abbreviations                    | 25 |

| 7.  | Legal information                | 26 |

| 7.1 | Definitions                      | 26 |

| 7.2 | Disclaimers                      | 26 |

| 7.3 | Trademarks                       |    |

| 8.  | List of figures                  | 27 |

| 9.  | List of tables                   | 28 |

| 10. | Contents                         | 29 |

|     |                                  |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. 2014.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 16 September 2014 Document identifier: AN11545