# LS1012A silicon changes from revision 1.0 to revision 2.0

## 1 About this document

This document is intended for customers using LS1012A processor revision 1.0 based designs and need to migrate their designs to revision 2.0.

## 2 System and Processor version

This table provides a cross-reference to match the LS1012A revision level to the system version register (SVR). Software that uses the SVR, must take into account the changes in these values with LS1012A revision 1.0

#### Contents

| 1 | All a statistical and state                          | 1   |

|---|------------------------------------------------------|-----|

| 1 | About this document                                  | 1   |

| 2 | System and Processor version                         | . 1 |

| 3 | Errata fixed in LS1012A revision 2.0                 | .2  |

| 4 | SGMII clocking scheme change                         | . 2 |

| 5 | Functional changes in revision 2.0 from revision 1.0 | .3  |

| 6 | Additional Part of 1000MHz CPU core frequency        | .5  |

| 7 | DC power supply tolerance changes                    | .5  |

| 8 | Power up sequencing change                           | .5  |

| 9 | Revision history                                     | 6   |

|   |                                                      |     |

#### Errata fixed in LS1012A revision 2.0

| Part     | Revision | System Version Register<br>Value | Note               |

|----------|----------|----------------------------------|--------------------|

| LS1012A  | 1.0      | 0x8704_0110                      | Without Encryption |

| LS1012AE | 1.0      | 0x8704_0010                      | With Encryption    |

| LS1012A  | 2.0      | 0x8704_0120                      | Without Encryption |

| LS1012AE | 2.0      | 0x8704_0020                      | With Encryption    |

Table 1. Revision Level to Part Marking Cross-Reference

Software needs to accommodate SVR update.

# 3 Errata fixed in LS1012A revision 2.0

This section describes the errata fixed in LS1012A revision 2.0

#### Table 2. Errata fixed in LS1012A revision 2.0

| Errata             | Title                                                                             | SW Impact | HW Impact                                                 |

|--------------------|-----------------------------------------------------------------------------------|-----------|-----------------------------------------------------------|

| Ethernet A-010336  | SGMII operation requires<br>common clock between PHY/<br>link partner and LS1012A |           | Yes<br>For details, refer SGMII<br>clocking scheme change |

| Ethnernet A-010904 | 2.5 SGMII is not supported.                                                       | No        | No                                                        |

| Ethernet A-010897  | Jumbo frame not supported.                                                        | No        | No                                                        |

#### NOTE

For complete list of LS1012A errata, refer LS1012ACE document.

Errata fixes have no impact on software implementation.

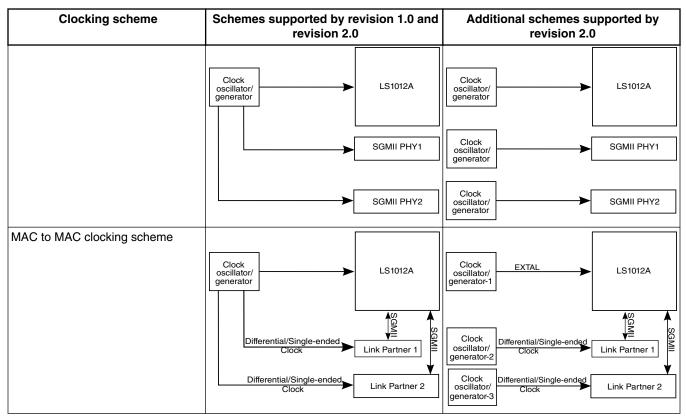

# 4 SGMII clocking scheme change

LS1012A revision 1.0 requires common clock for LS1012A and its link partner for proper operation of SGMII (10/100/1000/2500 Mbps). Refer erratum Ethernet A-010336.

Ethernet A-010336 is fixed in LS1012A revision 2.0.

Changes in clocking requirement are shown below:

### Table 3. MAC to PHY and MAC to MAC clocking scheme

| Clocking scheme            | Schemes supported by revision 1.0 and revision 2.0 | Additional schemes supported by revision 2.0 |

|----------------------------|----------------------------------------------------|----------------------------------------------|

| MAC to PHY clocking scheme |                                                    |                                              |

Table continues on the next page ...

#### LS1012A silicon changes from revision 1.0 to revision 2.0, Rev. 0, 01/2018

## Table 3. MAC to PHY and MAC to MAC clocking scheme (continued)

# 5 Functional changes in revision 2.0 from revision 1.0

This section describes the major functional changes applicable to LS1012A revision 2.0 from LS1012A revision 1.0.

# 5.1 RESET\_REQ\_B additionally multiplexed to CLK\_OUT

This section describes additional multiplexing of RESET\_REQ\_B with CLK\_OUT.

In LS1012A revision 1.0, RESET\_REQ\_B is multiplexed with QSPI\_A\_DAT3 signal hence limiting 4 bit QSPI mode with RESET\_REQ\_B.

In LS1012A revision 2.0, RESET\_REQ\_B is additionally multiplexed with CLK\_OUT signal thus providing flexibility to support 4 bit QSPI along with RESET\_REQ\_B.

| RCW Bit | Field Name                        | Revision 1.0                | Revision 2.0   |

|---------|-----------------------------------|-----------------------------|----------------|

| 382     | Reserved                          | Reserved. Must be set to 0. | Options:       |

| 383     | CLK_OUT_BASE                      | Options:                    | 00 GPIO1[31]   |

|         |                                   | 0 GPIO1[31]                 | 01 CLK_OUT     |

|         | functionality of the CLK_OUT pin. | 1 CLK_OUT                   | 10 RESET_REQ_B |

#### LS1012A silicon changes from revision 1.0 to revision 2.0, Rev. 0, 01/2018

| Functional cl | hanges in | revision | 2.0 from | revision | 1.0 |

|---------------|-----------|----------|----------|----------|-----|

|---------------|-----------|----------|----------|----------|-----|

| RCW Bit | Field Name | Revision 1.0 | Revision 2.0                                                                                                                                                 |

|---------|------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |            |              | 11 Reserved                                                                                                                                                  |

|         |            |              | Note:Select RESET_REQ_B<br>through either RCW[382:383] or<br>RCW[QSPI_IIC2]. Selection of<br>RESET_REQ_B in both RCW fields<br>simultaneously is prohibited. |

Impact:

Higher QSPI bandwidth is available with RESET\_REQ\_B.

## 5.2 Dependence of RESET\_REQ\_B selection on the ITS fuse

In revision 1.0, when ITS=1, RESET\_REQ\_B get mapped on QSPI\_A\_DATA3 pin. Hence LS1012A device cannot support 4-bit QSPI in secure mode.

The LS1012A revision 2.0 supports 4-bit QSPI in secure mode. In secure mode (ITS=1), user can choose to have RESET\_REQ\_B signal on CLK\_OUT or choose to not pinout RESET\_REQ\_B.

#### Impact

LS1012A revision 2.0 can be configured in secure mode without RESET\_REQ\_B.

## 5.3 GPIO1[13] availability

In LS1012A revision 1.0, GPIO1[13] is not available with RESET\_REQ\_B. If RCW[QSPI\_IIC2]=11, then the pin IIC2\_SCL is always tristated.

In LS1012A revision 2.0, GPIO1[13] is available with RESET\_REQ\_B. If RCW[QSPI\_IIC2]=11, then the pin IIC2\_SCL is configured as GPIO1[13]. If backwards compatibility with revision 1.0 is required when using RCW[QSPI\_IIC2]=11, then please ensure that GPIO1[13] is configured to be tristated.

| RCW Bit | Field Name                         | Revision1.0                   | Revision2.0                                                                  |

|---------|------------------------------------|-------------------------------|------------------------------------------------------------------------------|

| 424-425 | QSPI_IIC2                          | Options:                      | Options:                                                                     |

|         | Selects between                    | 00 GPIO1[13], GPIO1[14]       | 00 GPIO1[13], GPIO1[14]                                                      |

|         | GPIO's, IIC2,<br>QSPI_DAT[2:3] and | 01 IIC2_SCL, IIC2_SDA         | 01 IIC2_SCL, IIC2_SDA                                                        |

|         | RESET_REQ_B                        | 10 QSPI_A_DATA2, QSPI_A_DATA3 | 10 QSPI_A_DATA2, QSPI_A_DATA3                                                |

|         |                                    | 11 Reserved, RESET_REQ_B      | 11 GPIO1[13], RESET_REQ_B                                                    |

|         |                                    |                               | Note:Select RESET_REQ_B through<br>either RCW[382:383] or<br>RCW[QSPI_IIC2]  |

|         |                                    |                               | Selection of RESET_REQ_B in both<br>RCW fields simultaneously is prohibited. |

#### Impact:

GPIO1[13] is available when RCW[QSPI\_IIC2]= 11.

# 6 Additional Part of 1000MHz CPU core frequency

LS1012A revision 2.0 is available with additional core frequency of 1000MHz.

### Table 4. Supported CPU frequency for LS1012A revision 1.0 and 2.0

|                         | LS1012A revision 1.0 | LS1012A revision 2.0 |

|-------------------------|----------------------|----------------------|

| CPU Frequency supported | H = 800 MHz          | K = 1000 MHz         |

|                         | E = 600 MHz          | H = 800 MHz          |

|                         |                      | E = 600 MHz          |

## 7 DC power supply tolerance changes

Tolerance for DC power supply (S1V<sub>DD</sub>, USB\_SDV<sub>DD</sub>, USB\_SV<sub>DD</sub>) is changed in revision 2.0.

Table below details the changes:

#### Table 5. Recommended operating condition changes between revision 1.0 and revision 2.0

| Characteristic                                    | Symbol                | Recommended Value<br>in revision 1.0 | Recommended Value<br>in revision 2.0 | Unit |

|---------------------------------------------------|-----------------------|--------------------------------------|--------------------------------------|------|

| SerDes transceiver core and receiver power supply | S1V <sub>DD</sub>     | 0.9 ± 30 mV                          | 0.9 +50/-30 mV                       | V    |

| USB PHY Transceiver supply voltage                | USB_SDV <sub>DD</sub> | 0.9 ± 30 mV                          | 0.9 +50/-30 mV                       | V    |

| USB PHY Transceiver supply voltage                | USB_SV <sub>DD</sub>  | 0.9 ± 30 mV                          | 0.9 +50/-30 mV                       | V    |

Impact

Tolerance for  $S1V_{DD}$ , USB\_SDV<sub>DD</sub>, USB\_SV<sub>DD</sub> has been increased on positive side.

## 8 Power up sequencing change

#### Table 6. Changes in USB supplies ramp up timing

| Supply                                                                                | Revision 1.0 | Revision 2.0 |

|---------------------------------------------------------------------------------------|--------------|--------------|

| Maximum time allowed for all<br>USB supplies to ramp-up with<br>respect to each other |              | 95ms         |

# 9 Revision history

This table summarizes changes to this document.

## Table 7. Document revision history

| Revision number | Date    | Change                 |

|-----------------|---------|------------------------|

| 0               | 01/2018 | Initial public release |

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, the Freescale logo, Layerscape, QUICC Engine, CoreNet, and QorlQ are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, Arm Powered, Cortex, and TrustZone are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2018 NXP B.V.

Document Number AN11980 Revision 0, 01/2018