# AN12245 Power Consumption and Measurement of i.MX RT1060

Rev. 1 — 25 August 2019

**Application Note**

## **1** Introduction

This document discusses about the power consumption of i.MX RT1060. Mainly includes the following contents:

- i.MX RT1060 overview

- · Run mode definition and configuration

- · Low-power mode definition and configuration

- · How to measure power consumption based on MIMXRT1060 EVK board

- · Power consumption under different power modes

The development environment in this application note is IAR Embedded Workbench. Software is based on SDK 2.6.1. The hardware environment is MIMXRT1060 EVK board (Rev A1).

## 2 i.MX RT chip overview

The i.MX RT chip is a Cortex-M7 based chip that operates at speed up to 600 MHz to provide high CPU performance and best real-time response.

- Cortex-M7 based processor, which can operate at speed up to 600 MHz.

- 1 MB On-Chip SRAM up to 512 KB configurable as Tightly Coupled Memory (TCM).

- Advanced power management module with DCDC and LDO to reduce complexity of external power supply and simplifies power sequencing.

- Various memory interfaces, including SDRAM, Raw NAND FLASH, NOR flash, SD/eMMC, Quad SPI.

- A wide range of other interfaces for connecting peripherals, such as WLAN, Bluetooth<sup>™</sup>, GPS, displays, and camera sensors.

- Rich audio & video features, including LCD display, basic 2D graphics, camera interface, S/PDIF, and I2S audio interface.

- Provide rich peripheral modules, such as SPI, I<sup>2</sup>C, Can, Ethernet, Flex-Timers, and ADC.

- Target at Industrial HMI, Motor Control, and Home Appliance areas.

#### 3 Low power overview

- Power supply

- Run mode

- Low-power mode

#### 3.1 Power supply

Table 1 below shows the power supply rails of i.MX RT1060.

#### Contents

| 1 Introduction1                                                        |

|------------------------------------------------------------------------|

| 2 i.MX RT chip overview1                                               |

| 3 Low power overview                                                   |

| 4 How to measure power<br>consumption on MIMXRT1060<br>EVK             |

| 5 Power consumption results9<br>5.1 Run mode10<br>5.2 Low-power mode10 |

| 6 Conclusion11                                                         |

| 7 Revision history 11                                                  |

| 8 References11                                                         |

#### Table 1. External power supply rails

| Power Rail    | Description                                 |

|---------------|---------------------------------------------|

| DCDC_IN       | Power for DCDC.                             |

| SOC_IN        | Power for SOC.                              |

| VDD_HIGH_IN   | Power for Analog.                           |

| VDD_SNVS_IN   | Power for SNVS and RTC.                     |

| USB_OTG1_VBUS | Power for USB VBUS.                         |

| USB_OTG2_VBUS |                                             |

| VDDA_ADC_3P3  | Power for 12-bit ADC.                       |

| NVCC_SD0      | Power for GPIO in SDIO1 bank (3.3 V mode).  |

|               | Power for GPIO in SDIO1 bank (1.8 V mode).  |

| NVCC_SD1      | Power for GPIO in SDIO2 bank (3.3 V mode).  |

|               | Power for GPIO in SDIO2 bank (1.8 V mode).  |

| NVCC_GPIO     | IO Power for GPIO in GPIO bank.             |

| NVCC_EMC      | IO Power for GPIO in EMC bank. (3.3 V mode) |

|               | IO Power for GPIO in EMC bank. (1.8 V mode) |

#### 3.2 Run mode

- Run mode definition

- Run mode configuration

#### 3.2.1 Run mode definition

#### Table 2. Run mode definition

| Run Mode       | Definition                                                 |  |  |  |  |

|----------------|------------------------------------------------------------|--|--|--|--|

| Overdrive Run  | CPU runs at 600 MHz, overdrive voltage to 1.275 V          |  |  |  |  |

|                | Bus frequency at 150 MHz                                   |  |  |  |  |

|                | All the peripheral is enabled and runs at target frequency |  |  |  |  |

|                | All PLLs are enabled                                       |  |  |  |  |

| Full-Speed Run | CPU runs at 528 MHz, full loading, lower voltage to 1.15 V |  |  |  |  |

|                | Bus frequency at 132 MHz                                   |  |  |  |  |

|                | All the peripheral is enabled and runs at target frequency |  |  |  |  |

|                | All PLLs are enabled                                       |  |  |  |  |

Table continues on the next page...

| Table 2. | Run mode | definition | (continued) | ) |

|----------|----------|------------|-------------|---|

|----------|----------|------------|-------------|---|

| Low-Speed Run | CPU runs at 132 MHz, lower voltage to 1.15 V                                            |

|---------------|-----------------------------------------------------------------------------------------|

|               | Internal bus frequency at 33 MHz                                                        |

|               | <ul> <li>All PLL and PFDs are disabled except SYSPLL and<br/>SYSPLLPFD2</li> </ul>      |

|               | • 20 % peripheral are active, others are in low-power mode                              |

| Low-Power Run | CPU runs at 24 MHz, lower voltage to 0.95 V                                             |

|               | Internal bus frequency at 12 MHz                                                        |

|               | <ul> <li>All PLLs are powered down, OSC24M powered down,<br/>RCOSC24 enabled</li> </ul> |

|               | High-speed peripherals are power down                                                   |

### 3.2.2 Run mode configuration

#### Table 3. Run mode configuration

| CCM LPM Mode    | RUN     | RUN     | RUN        | RUN          |

|-----------------|---------|---------|------------|--------------|

| CPU Core        | 600 MHz | 528 MHz | 132 MHz    | 24 MHz       |

| L1 Cache        | ON      | ON      | ON         | ON           |

| IPG CLK         | 150 MHz | 132 MHz | 33 MHz     | 12 MHz       |

| PER CLK         | 75 MHz  | 66 MHz  | 33 MHz     | 12 MHz       |

| FlexRAM         | ON      | ON      | ON         | ON           |

| SOC Voltage     | 1.275 V | 1.15 V  | 1.15 V     | 0.95 V       |

| Analog LDO      | ON      | ON      | ON         | In Weak Mode |

| 24 MHz XTAL OSC | ON      | ON      | ON         | OFF          |

| 24 MHz RC OSC   | OFF     | OFF     | OFF        | ON           |

| ARM PLL         | ON      | ON      | Power Down | Power Down   |

| SYS PLL         | ON      | ON      | ON         | Power Down   |

| SYS PFD0        | ON      | ON      | Power Down | Power Down   |

| SYS PFD1        | ON      | ON      | Power Down | Power Down   |

| SYS PFD2        | ON      | ON      | ON         | Power Down   |

| SYS PFD3        | ON      | ON      | Power Down | Power Down   |

| USB1 PLL        | ON      | ON      | Power Down | Power Down   |

| USB1 PFD0       | ON      | ON      | Power Down | Power Down   |

| USB1 PFD1       | ON      | ON      | Power Down | Power Down   |

| USB1 PFD2       | ON      | ON      | Power Down | Power Down   |

| USB1 PFD3       | ON      | ON      | Power Down | Power Down   |

Table continues on the next page...

| CCM LPM Mode | RUN | RUN | RUN                   | RUN                  |

|--------------|-----|-----|-----------------------|----------------------|

| USB2 PLL     | ON  | ON  | Power Down            | Power Down           |

| Audio PLL    | ON  | ON  | Power Down            | Power Down           |

| Video PLL    | ON  | ON  | Power Down            | Power Down           |

| ENET PLL     | ON  | ON  | Power Down Power Down |                      |

| Module Clock | ON  | ON  | On as needed          | Peripheral clock off |

| RTC32K       | ON  | ON  | ON                    | ON                   |

#### Table 3. Run mode configuration (continued)

#### 3.3 Low-power mode

- Low-power mode definition

- Low-power mode configuration

- Wake-up source

#### 3.3.1 Low-power mode definition

#### Table 4. Low-power mode definition

| Low-Power Mode | Definition                                                                                                                    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| System Idle    | CPU can automatically enter this mode when no thread<br>running                                                               |

|                | All the peripherals can remain active                                                                                         |

|                | CPU only enters WFI mode, it has its state retained so the interrupt response can be very short                               |

| Low-Power Idle | Much lower power than System Idle mode, with longer exit time                                                                 |

|                | <ul> <li>All PLLs are shut off, analog modules running in low-power mode</li> </ul>                                           |

|                | <ul> <li>All high-speed peripherals are power gated, low speed<br/>peripherals can remain running at low frequency</li> </ul> |

| Suspend        | The most power-saving mode with longest exit time                                                                             |

|                | <ul> <li>All PLLs are shut off, XTAL are off, all clocks are shut off<br/>except 32 K clock</li> </ul>                        |

|                | <ul> <li>All high-speed peripherals are power gated, low speed<br/>peripherals are clock gated</li> </ul>                     |

| SNVS           | All SOC digital logic, analog modules are shut off only except SNVS domain                                                    |

|                | • 32 KHz RTC is alive                                                                                                         |

|                | VDD_HIGH_IN and VDD_DCDC_IN can be powered off                                                                                |

## 3.3.2 Low-power mode configuration

#### Table 5. Low-power mode configuration

|                    | System Idle | Low-Power Idle | Suspend    | SNVS |

|--------------------|-------------|----------------|------------|------|

| CCM LPM Mode       | WAIT        | WAIT           | STOP       | -    |

| Arm Core (PDM7)    | WFI         | WFI            | Power Down | OFF  |

| L1 Cache           | ON          | ON             | Power Down | OFF  |

| FlexRAM (PDRET)    | ON          | ON             | ON         | OFF  |

| FlexRAM (PDRAM0)   | ON          | ON             | Power Down | OFF  |

| FlexRAM (PDRAM1)   | ON/OFF      | ON/OFF         | Power Down | OFF  |

| VDD_SOC_IN Voltage | 1.15 V      | 0.95 V         | 0.925 V    | OFF  |

| ARM PLL            | Power Down  | Power Down     | Power Down | OFF  |

| SYS PLL            | ON          | Power Down     | Power Down | OFF  |

| SYS PFD0           | Power Down  | Power Down     | Power Down | OFF  |

| SYS PFD1           | Power Down  | Power Down     | Power Down | OFF  |

| SYS PFD2           | ON          | Power Down     | Power Down | OFF  |

| SYS PFD3           | Power Down  | Power Down     | Power Down | OFF  |

| USB1 PLL           | Power Down  | Power Down     | Power Down | OFF  |

| USB1 PFD0          | Power Down  | Power Down     | Power Down | OFF  |

| USB1 PFD1          | Power Down  | Power Down     | Power Down | OFF  |

| USB1 PFD2          | Power Down  | Power Down     | Power Down | OFF  |

| USB1 PFD3          | Power Down  | Power Down     | Power Down | OFF  |

| USB2 PLL           | Power Down  | Power Down     | Power Down | OFF  |

| Audio PLL          | Power Down  | Power Down     | Power Down | OFF  |

| Video PLL          | Power Down  | Power Down     | Power Down | OFF  |

| ENET PLL           | Power Down  | Power Down     | Power Down | OFF  |

| 24 MHz XTAL OSC    | ON          | OFF            | OFF        | OFF  |

| 24 MHz RC OSC      | OFF         | ON             | OFF        | OFF  |

| LDO2P5             | ON          | OFF            | OFF        | OFF  |

| LDO1P1             | ON          | OFF            | OFF        | OFF  |

| WEAK2P5            | OFF         | ON             | OFF        | OFF  |

| WEAK1P1            | OFF         | ON             | OFF        | OFF  |

| Bandgap            | ON          | OFF            | OFF        | OFF  |

| Low-Power Bandgap  | ON          | ON             | ON         | OFF  |

| AHB clock          | 33 MHz      | 12 MHz         | OFF        | OFF  |

Table continues on the next page ...

| IPG clock     | 33 MHz       | 12 MHz       | OFF | OFF |

|---------------|--------------|--------------|-----|-----|

| PER clock     | 33 MHz       | 12 MHz       | OFF | OFF |

| Module Clocks | ON as needed | ON as needed | OFF | OFF |

| RTC32K        | ON           | ON           | ON  | ON  |

#### Table 5. Low-power mode configuration (continued)

#### 3.3.3 Wake-up source

#### Table 6. Wake-up source

|                                  | System Idle           | Low Power Idle | Suspend | SNVS               |  |

|----------------------------------|-----------------------|----------------|---------|--------------------|--|

| GPIO wake-up                     | YES                   | YES            | YES     | - YES (1 PIN only) |  |

| RTC wake-up                      | YES                   | YES            | YES     | YES                |  |

| USB remote wake-up               | SB remote wake-up YES |                | YES     | NO                 |  |

| Other peripheral wake-up sources | YES                   | YES            | YES     | NO                 |  |

#### NOTE

Irrespective of whether the system is in System Idle, Low-Power Idle or Suspend modes, the wake-up interrupt should be enabled in GPC module. The only pin that can wake up the system in SNVS is IOMUXC\_SNVS\_WAKEUP\_GPI05\_I000.

NOTE

Peripheral wake-up requires that the clock for the peripheral is available in the mode

## 4 How to measure power consumption on MIMXRT1060 EVK

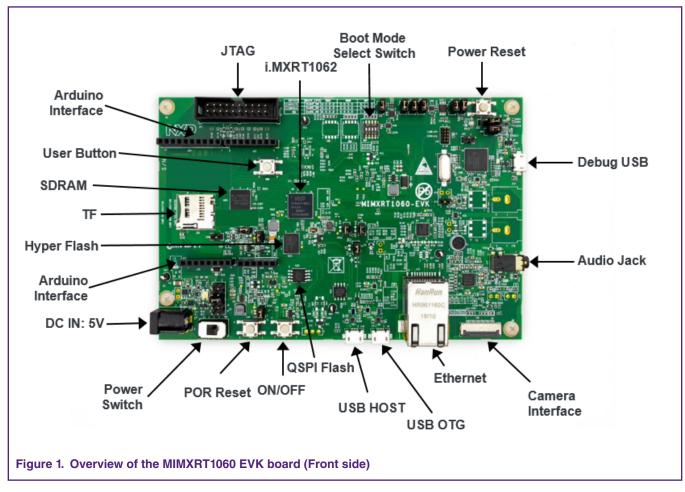

## 4.1 MIMXRT1060-EVK (REV A1) board overview

#### 4.1.1 Current measurements on EVK

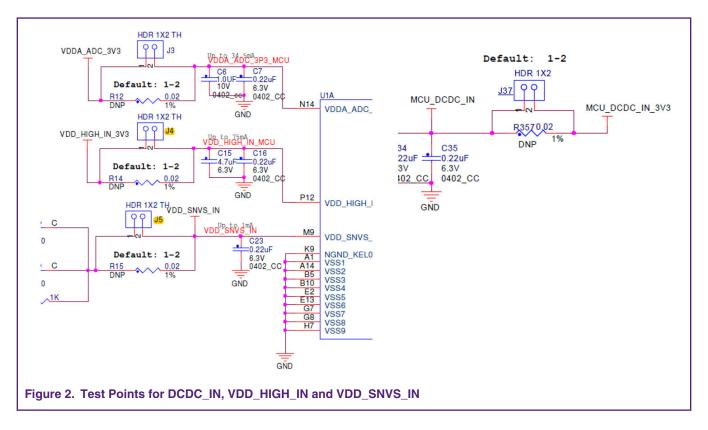

For this application note, measure the current value of DCDC\_IN (J37), VDD\_HIGH\_IN (J4), and VDD\_SNVS\_IN (J5).

#### 4.1.2 Hardware rework for the EVK

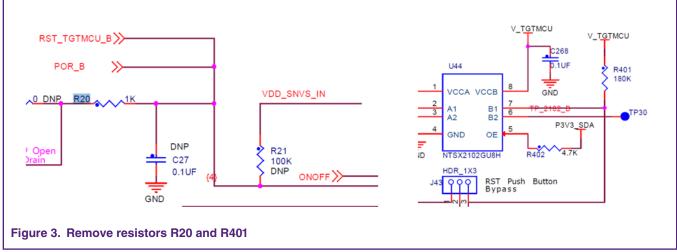

Because the POR\_B pin has an internal pullup, R401 and R20 should be removed. Leaving these resistors populated causes higher SNVS current than what is shown in this application note.

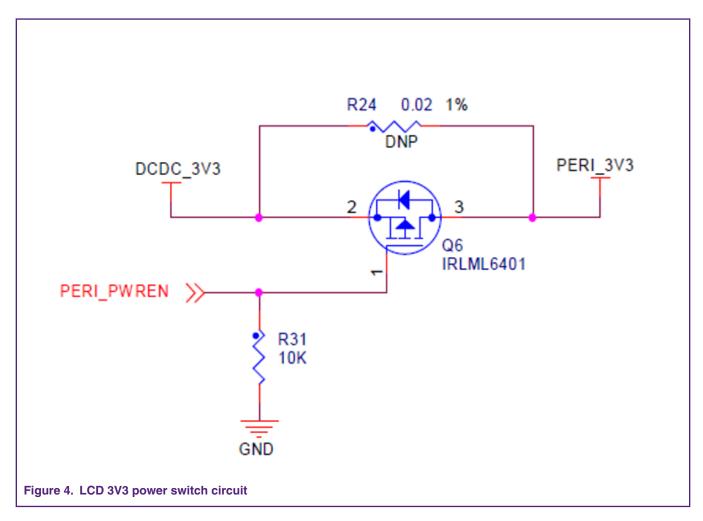

SNVS\_PMIC\_STBY\_REQ\_GPIO5\_IO02 outputs a high-level signal under Suspend Mode (Stop Mode). On the EVK board, this pin is used to control LCD Power switch and a resistor R31 is connected to this pin. When the chip is under the Suspend Mode, this resistor consumes more current. To fix this issue, SNVS\_PMIC\_STBY\_REQ is configured as a low-level output GPIO pin.

#### 4.1.3 Run IAR-based project demo example – Power mode switch

- 1. The project file is at: boards\evkbmimxrt1060\demo\_apps\power\_mode\_switch\_bm\iar\power\_mode\_switch\_bm.eww

- 2. Download the project.

- 3. Select the target power mode on the terminal.

## **5** Power consumption results

NOTE -

To reduce power consumption, VDD\_SNVS\_IN is powered by VDD\_HIGH\_IN in all power modes except the SNVS mode.

All power consumption values are typical silicon at 25 C.

Discontinuous conduction mode (DCM) increases the efficiency of DCDC in case of low current loading and is always recommended.

### 5.1 Run mode

#### Table 7. Run mode on RAM

| RT1060-EVK Overdrive (600 MHz) |                | · · ·           |               | Low-speed run (132<br>MHz) |               | Low power run (24<br>MHz) |               |                 |               |

|--------------------------------|----------------|-----------------|---------------|----------------------------|---------------|---------------------------|---------------|-----------------|---------------|

| Power<br>Rail                  | Voltage<br>(V) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA)            | Power<br>(mW) | Current<br>(mA)           | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) |

| DCDC_IN                        | 3.3            | 53.1432         | 175.3726      | 38.2423                    | 126.1996      | 12.9733                   | 42.8119       | 2.7634          | 9.1192        |

| HIGH_IN                        | 3.3            | 20.4431         | 67.4622       | 20.4244                    | 67.4005       | 5.2617                    | 17.3636       | 0.2682          | 0.8851        |

| SNVS_IN                        | 3.3            | 0.0250          | 0.0824        | 0.0234                     | 0.0771        | 0.0137                    | 0.0452        | 0.0173          | 0.0571        |

#### Table 8. Run mode XIP on Flash

| RT1060-EVK    |                | Overdrive (600 MHz) |               | Full-speed run (528<br>MHz) |               | Low-speed run (132<br>MHz) |               | Low power run (24<br>MHz) |               |

|---------------|----------------|---------------------|---------------|-----------------------------|---------------|----------------------------|---------------|---------------------------|---------------|

| Power<br>Rail | Voltage<br>(V) | Current<br>(mA)     | Power<br>(mW) | Current<br>(mA)             | Power<br>(mW) | Current<br>(mA)            | Power<br>(mW) | Current<br>(mA)           | Power<br>(mW) |

| DCDC_IN       | 3.3            | 44.5526             | 147.0236      | 32.4731                     | 107.1612      | 11.8486                    | 39.1004       | 2.4326                    | 8.0276        |

| HIGH_IN       | 3.3            | 20.4381             | 67.4457       | 20.4542                     | 67.4989       | 5.2729                     | 17.4006       | 0.2827                    | 0.9329        |

| SNVS_IN       | 3.3            | 0.0257              | 0.0847        | 0.0241                      | 0.0796        | 0.0140                     | 0.0461        | 0.0178                    | 0.0586        |

#### 5.2 Low-power mode

The power consumption in Table 9 and Table 10is measured with the power mode switch project.

#### Table 9. Power consumption results

| RT1060-EVK    |                | System Idle     |               | Low power       |               | Suspend         |               | SNVS            |               |

|---------------|----------------|-----------------|---------------|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| Power<br>Rail | Voltage<br>(V) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) |

| DCDC_IN       | 3.3            | 5.6543          | 18.6592       | 1.3263          | 4.3768        | 0.2192          | 0.7234        | 1               | /             |

| HIGH_IN       | 3.3            | 5.2542          | 17.3389       | 0.2601          | 0.8583        | 0.0223          | 0.0736        | 1               | /             |

| SNVS_IN       | 3.3            | 0.0133          | 0.0438        | 0.0171          | 0.0564        | 0.0109          | 0.0361        | 0.0157          | 0.0518        |

#### Table 10. Low power mode XIP on Flash

| RT1060-EVK    |                | System Idle     |               | Low power       |               | Suspend         |               | SNVS            |               |

|---------------|----------------|-----------------|---------------|-----------------|---------------|-----------------|---------------|-----------------|---------------|

| Power<br>Rail | Voltage<br>(V) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) | Current<br>(mA) | Power<br>(mW) |

| DCDC_IN       | 3.3            | 6.0045          | 19.8149       | 1.4586          | 4.8134        | 0.2156          | 0.7115        | /               | /             |

| HIGH_IN       | 3.3            | 5.2568          | 17.3474       | 0.2601          | 0.8583        | 0.0222          | 0.0733        | /               | /             |

| SNVS_IN       | 3.3            | 0.0136          | 0.0450        | 0.0177          | 0.0583        | 0.0114          | 0.0376        | 0.0157          | 0.0518        |

NOTE

All power consumption values are typical silicon at 25 C.

NOTE

Discontinuous conduction mode (DCM) increases the efficiency of DCDC in case of low current loading and is always recommended.

## 6 Conclusion

This document mainly describes how to measure power consumption on i.MX RT based on MIMXRT1060 EVK (Rev. A1). For more design details in designing a low-power application, see the application note How to use iMXRT Low Power Feature.

## 7 Revision history

#### Table 11. Revision history

| Revision number | Date    | Substantive changes                   |  |  |

|-----------------|---------|---------------------------------------|--|--|

| 0               | 09/2018 | Initial release                       |  |  |

| 1               | 08/2019 | Updated the power consumption results |  |  |

## 8 References

- 1. i.MX RT 1060 Reference Manual

- 2. Arm Cortex M7 Reference Manual

- 3. How to use iMXRT Low Power Feature

#### How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, UMEMS, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

#### <sup>©</sup> NXP B.V. 2018-2019.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 25 August 2019 Document identifier: AN12245

## arm