NXP Semiconductors Application Note

# Migration Guide from i.MX RT1060 to i.MX RT1064

# 1. Introduction

The i.MX RT1064 processor contains 4 MB on-chip flash and 1 MB on-chip RAM. Different from the i.MX RT1060, i.MX RT1064 is embedded with one 4 MB QSPI flash, which helps customers to save the space and simply circuit design.

This document intends to introduce how to migrate from the i.MX RT1060 to i.MX RT1064.

### Contents

| 1. | Intro | duction                  | . 1 |

|----|-------|--------------------------|-----|

| 2. | Over  | view                     | . 2 |

| 3. | How   | to migrate               | 5   |

|    |       | Linker file modification |     |

|    | 3.2.  | XIP flash boot option    | 6   |

|    | 3.3.  | FlexSPI2 pin mux changes | . 6 |

|    |       | lusion                   |     |

# 2. Overview

The i.MX RT1064 combines the i.MXRT1060 and one 4 MB QSPI flash in chip. During the migration, be aware of the following items:

- The i.MX RT1064 chip can directly replace the i.MXRT1060 chip and no hardware upgrade is required.

- The i.MX RT1064 can boot by the internal QSPI flash while the i.MXRT1060 can boot by external flash.

- The modification on the linker file is required.

The i.MX RT1060 and i.MX RT1064 take different XIP boot options, which means they boot by different FlexSPI instances. The i.MX RT1060 uses FlexSPI and i.MXRT1064 uses FlexSPI2. Please see following tables for the differences on boot pins, memory map and pin mux.

Table 1 and Table 2 describe the XIP boot pins for i.MXRT1060 and i.MXRT1064.

| Peripheral | Port (IO function) | PAD           | Description                              |

|------------|--------------------|---------------|------------------------------------------|

| FlexSPI    | FLEXSPI_B_DATA3    | GPIO_SD_B1_00 | Boot option to connect the external XIP  |

|            | FLEXSPI_B_DATA2    | GPIO_SD_B1_01 | flash, such as, QSPI flash, Octal flash  |

|            | FLEXSPI_B_DATA1    | GPIO_SD_B1_02 | and Hyper flash, and so on.              |

|            | FLEXSPI_B_DATA0    | GPIO_SD_B1_03 |                                          |

|            | FLEXSPI_B_SCLK     | GPIO_SD_B1_04 |                                          |

|            | FLEXSPI_B_DQS      | GPIO_SD_B0_05 |                                          |

|            | FLEXSPI_B_SS0_B    | GPIO_SD_B0_04 |                                          |

|            | FLEXSPI_B_SS1_B    | GPIO_SD_B0_01 |                                          |

|            | FLEXSPI_A_DQS      | GPIO_SD_B1_05 |                                          |

|            | FLEXSPI_A_SS0_B    | GPIO_SD_B1_06 |                                          |

|            | FLEXSPI_A_SS1_B    | GPIO_SD_B0_00 |                                          |

|            | FLEXSPI_A_SCLK     | GPIO_SD_B1_07 |                                          |

|            | FLEXSPI_A_DATA0    | GPIO_SD_B1_08 |                                          |

|            | FLEXSPI_A_DATA1    | GPIO_SD_B1_09 |                                          |

|            | FLEXSPI_A_DATA2    | GPIO_SD_B1_10 |                                          |

|            | FLEXSPI_A_DATA3    | GPIO_SD_B1_11 |                                          |

| FlexSPI    | FLEXSPI_A_DQS      | GPIO_AD_B1_09 | The other boot option, just available to |

|            | FLEXSPI_A_DATA3    | GPIO_AD_B1_10 | connect QSPI flash.                      |

|            | FLEXSPI_A_DATA2    | GPIO_AD_B1_11 |                                          |

|            | FLEXSPI_A_DATA1    | GPIO_AD_B1_12 |                                          |

|            | FLEXSPI_A_DATA0    | GPIO_AD_B1_13 |                                          |

|            | FLEXSPI_A_SCLK     | GPIO_AD_B1_14 |                                          |

|            | FLEXSPI_A_SS0_B    | GPIO_AD_B1_15 |                                          |

Table 1. i.MXRT1060 XIP boot options

| Peripheral | Port (IO function) | PAD            | Description                    |

|------------|--------------------|----------------|--------------------------------|

| FlexSPI2   | FLEXSPI2_A_SS0_B   | GPIO_SPI_B1_06 | Connected to the embedded QSPI |

|            | FLEXSPI2_A_ SCLK   | GPIO_SPI_B0_08 | flash for booting.             |

|            | FLEXSPI2_A_ DQS    | GPIO_SPI_B0_09 |                                |

|            | FLEXSPI2_A_DATA0   | GPIO_SPI_B0_02 |                                |

|            | FLEXSPI2_A_DATA1   | GPIO_SPI_B1_03 |                                |

|            | FLEXSPI2_A_DATA2   | GPIO_SPI_B1_02 |                                |

|            | FLEXSPI2_A_DATA3   | GPIO_SPI_B0_10 |                                |

|            | FLEXSPI2_RESET_PIN | GPIO_SPI_B0_13 |                                |

Table 2. i.MXRT1064 XIP boot options

*Table 3* shows the memory map differences between FlexSPI and FlexSPI2.

Table 3. FlexSPI/FlexSPI2 memory map

| Start address | End address | Size   | Description                  |

|---------------|-------------|--------|------------------------------|

| 7000_0000     | 7EFF_FFFF   | 240 MB | FlexSPI2/FlexSPI2 ciphertext |

| 6000_0000     | 6FFF_FFFF   | 256 MB | FlexSPI/FlexSPI ciphertext   |

During the migration from the i.MX RT1060 to i.MX RT1064, there are pin mux changes, as shown in *Table 4*.

| Peripheral | Function         | Pin muxing     |                |

|------------|------------------|----------------|----------------|

| ronphora   |                  | i.MX RT1060    | i.MX RT1064    |

|            |                  | GPIO_EMC_26    |                |

|            | FLEXSPI2_A_DATA0 | GPIO_SPI_B1_04 | GPIO_SPI_B0_02 |

|            |                  | GPIO_SPI_B0_02 |                |

|            |                  | GPIO_SPI_B0_12 |                |

|            | FLEXSPI2_A_DATA1 | GPIO_SPI_B1_03 | GPIO_SPI_B1_03 |

|            |                  | GPIO_EMC_27    |                |

|            |                  | GPIO_SPI_B0_06 |                |

|            | FLEXSPI2_A_DATA2 | GPIO_SPI_B1_02 | GPIO_SPI_B1_02 |

|            |                  | GPIO_EMC_28    |                |

|            |                  | GPIO_SPI_B0_10 |                |

| FlexSPI2   | FLEXSPI2_A_DATA3 | GPIO_SPI_B1_01 | GPIO_SPI_B0_10 |

|            |                  | GPIO_EMC_29    |                |

|            |                  | GPIO_SPI_B0_09 |                |

|            | FLEXSPI2_A_DQS   | GPIO_SPI_B1_00 | GPIO_SPI_B0_09 |

|            |                  | GPIO_EMC_23    |                |

|            |                  | GPIO_SPI_B0_08 |                |

|            | FLEXSPI2_A_SCLK  | GPIO_SPI_B1_05 | GPIO_SPI_B0_08 |

|            |                  | GPIO_EMC_25    |                |

|            |                  | GPIO_SPI_B0_05 |                |

|            | FLEXSPI2_A_SS0_B | GPIO_SPI_B1_06 | GPIO_SPI_B1_06 |

|            |                  | GPIO_EMC_24    |                |

Table 4.Pin mux changes

Migration Guide from i.MX RT1060 to i.MX RT1064, Application Note, Rev. 0, 10/2018

#### How to migrate

| <b>D</b>   | Function         | Pin muxing     |             |

|------------|------------------|----------------|-------------|

| Peripheral |                  | i.MX RT1060    | i.MX RT1064 |

|            | FLEXSPI2_A_SS1_B | GPIO_EMC_22    | N/A         |

| Γ          |                  | GPIO_SPI_B0_11 | N/A         |

|            | FLEXSPI2_B_DATA0 | GPIO_EMC_13    | N/A         |

|            |                  | GPIO_SPI_B0_07 | N/A         |

|            | FLEXSPI2_B_DATA1 | GPIO_EMC_14    | N/A         |

|            |                  | GPIO_SPI_B0_03 | N/A         |

|            | FLEXSPI2_B_DATA2 | GPIO_EMC_15    | N/A         |

|            |                  | GPIO_SPI_B0_04 | N/A         |

|            | FLEXSPI2_B_DATA3 | GPIO_EMC_16    | N/A         |

|            | FLEXSPI2_B_DQS   | GPIO_EMC_11    | N/A         |

|            |                  | GPIO_SPI_B0_01 | N/A         |

|            | FLEXSPI2_B_SCLK  | GPIO_EMC_12    | N/A         |

|            | FLEXSPI2_B_SS0_B | GPIO_EMC_10    | N/A         |

|            | FLEXSPI2_B_SS1_B | GPIO_EMC_09    | N/A         |

#### Table 4.Pin mux changes

## 3. How to migrate

As the i.MX RT1064 XIP boots through the FlexSPI2 interface, modifications are required on the linker file.

## 3.1. Linker file modification

As mentioned above, there are changes on the memory map during the migration from the i.MX RT1060 to i.MX RT1064.

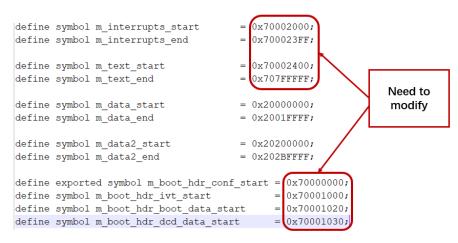

As shown in *Figure 1* and *Figure 2*, you need to update the base address of text space from 0x60000000 to 0x70000000 during the code migration from the i.MX RT1060 to i.MX RT1064.

```

define symbol m interrupts start

= 0 \times 60002000;

define symbol m interrupts end

= 0x600023FF;

define symbol m text start

= 0 \times 60002400;

define symbol m text end

= 0 \times 607 FFFFF;

define symbol m data start

= 0 \times 20000000;

define symbol m data end

= 0 \times 2001 FFFF;

define symbol m data2 start

= 0 \times 20200000;

= 0x202BFFFF;

define symbol m data2 end

define exported symbol m boot hdr conf start = 0x60000000;

define symbol m boot hdr ivt start

= 0 \times 60001000;

define symbol m_boot_hdr_boot_data_start = 0x60001020;

define symbol m_boot_hdr_dcd_data_start = 0x60001030;

```

Figure 1. Linker file in i.MXRT1060

Figure 2. Linker file in i.MXRT1064

## 3.2. XIP flash boot option

Do not try the XIP boot by FlexSPI with external XIP flash, but you can still connect the external flash through the FlexSPI interface, which can be used to save data or other functions except boot.

## 3.3. FlexSPI2 pin mux changes

i.MX RT1060 can remap the FlexSPI2 to external pins (SEMC port) and internal pad, while i.MX RT1064 can only remap to the internal pad (SPI port).

#### NOTE

DO NOT remap the FlexSPI2 to other pins except the embedded flash connection when migrating from i.MX RT1060 to i.MX RT1064. Otherwise, the embedded QSPI flash malfunctions.

# 4. Conclusion

This document introduces how to migrate from the i.MXRT1060 to the i.MXRT1064, which helps customers to move the project to i.MXRT1064 easily.

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, Freescale, and the Freescale logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm, Arm Powered, and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

© 2018 NXP B.V.

Document Number: AN12290 Rev. 0 10/2018