## AN12949 Flash Programming Tips for LPC5500 Series

Rev. 0 — 08/2020

Application Note

## 1 Introduction

#### 1.1 LPC5500 series introduction

The LPC55S00 is a family of Arm<sup>®</sup> Cortex<sup>®</sup> -M33-based MCUs for embedded applications. It features a rich peripheral set leveraging the new ARMv8M architecture. This document focuses on LPC5500's series flash operation.

Compared with legacy LPC parts, LPC4300, LPC54000, LPC1800, LPC800, the LPC5500 uses new flash IP and is enabled with ROM API driver. Lots of new features have been introduced into this new series. At the same time, it might be a little complicated for new users to operate LPC5500 series' flash. This document aimes to removing those barriers and giving some useful tips for users.

If you have already used LPC5500 series and met some issues with operating internal flash, go to Summary first to check if you follow all the rules and tips mentioned in this document.

#### 1.2 Related UM chapters

- 1. Chapter 2: LPC55S6x/LPC55S2x/LPC552x Memory Map

- 2. Chapter 5: LPC55S6x/LPC55S2x/LPC552x Flash

- 3. Chapter 9: LPC55S6x/LPC55S2x/LPC552x Flash API

- 4. Chapter 10: LPC55S6x/LPC55S2x/LPC552x Protected Flash Region

- 5. UM attached file: LPC55S6x\_LPC55S2x\_LPC552x Protected Flash Region v1.1.xls

## 2 Implementation

### 2.1 Flash memory layout

LPC5500 series have three flash configurations:

- 640 KB FLASH/320 KB RAM

- 512 KB FLASH/256 KB RAM

- 256 KB FLASH/144 KB RAM

In some configurations, users cannot use all flash memory to store code and data. Because LPC5500 series use last few pages as Protected Flash Region (PFR) to store important information and some internal manufacture settings.

### 2.1.1 Page size and sector size

The sector size of the LPC5500 series internal flash memory is 32 KB and the page size is 512 bytes.

#### Contents

| 1   | Introduction1                      |

|-----|------------------------------------|

| 1.1 | LPC5500 series introduction1       |

| 1.2 | Related UM chapters1               |

| 2   | Implementation1                    |

| 2.1 | Flash memory layout1               |

| 2.2 | Flash operation2                   |

| 3   | Summary5                           |

| 3.1 | Make sure core clock under 100     |

|     | MHz when operating flash5          |

| 3.2 | Caution on PFR region5             |

| 3.3 | Using ROM API to erase/program     |

|     | flash5                             |

| 3.4 | Using ROM API:                     |

|     | FLASH_VerifyErase before read      |

|     | flash data to void Hardfault issue |

|     | 5                                  |

| 3.5 | Align5                             |

|     |                                    |

The minimum programming size is the page size, 512 bytes.

The minimum erase size is page size, 512 bytes.

#### 2.1.2 PFR region in last pages of flash memory

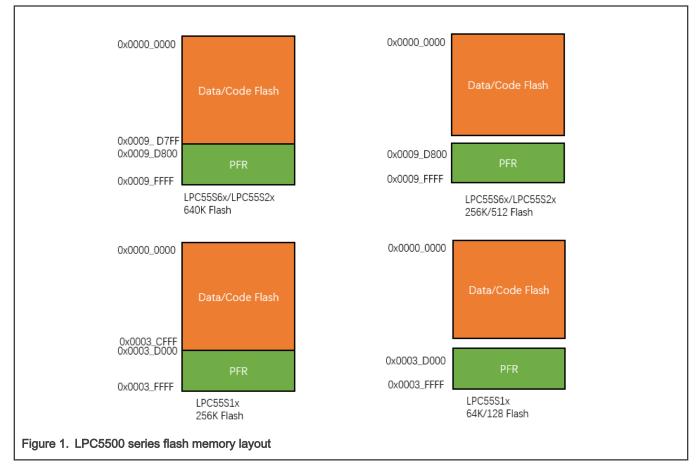

Unlike legacy LPC parts, all LPC5500 series use last few pages of flash memory as PFR. PFR is used to store some important user and manufacture configuration information. PFR cannot be used as normal flash to store data and code. Programming PFR needs special cautions, or the chip might be malfunctioned. Figure 1 shows the flash memory layout.

#### As shown in Figure 1:

The PFR size of LPC55S6x/LPC55S2x is 10 KB, located in 0x0009\_D800 - 0x0009\_FFFF.

The PFR size of LPC55S1x is 12 KB, located in 0x0003\_D000 - 0x0003\_FFFF.

- For LPC55S6x/LPC55S2x 256/512 KB part, the total flash size can be used by customer is 256/512 KB.

- For LPC55S6x/LPC55S2x 640 KB part, the total flash size can be used by customer is 630 KB.

- For LPC55S1x 64/128 KB part, the total flash size can be used by customer is 64/128 KB.

- For LPC55S1x 256 KB part, the total flash size can be used by customer is 244 KB.

#### 2.2 Flash operation

LPC5500 series' flash implement internal ECC management, including single bit correction and error correction logging. This makes flash more secure and robust than others. But this feature also brings an issue: when performing AHB read, memcpy, of an erased or corrupted flash memory, a HardFault will occur. This may happen when users try to read, AHB read, an erased while not programmed flash page.

See Notes in Block diagram in LPC55S6x/LPC55S2x/LPC552x User manual (document UM11126).

NOTE

When performing AHB reads of the flash memory contents, a hardware fault will occur if an unrecoverable error is detected. Read operations performed using flash controller commands (see **Command listing**) will not cause a hard fault.

The following section will discuss how to work around this issue.

Also, PFR region resides the last pages of flash, making it vulnerable to be erased accidently. To avoid this, we recommend using ROM API to operate flash instead of manipulating flash register directly. ROM API provide internal protection to avoid user erase PFR accidently. While the flash register gives you free access to all flash data, it is a little "dangerous".

We suggest using ROM API to access data flash and PFR. The flash register operation is not recommended.

Finally, flash erase and program can only be done when core clock <=100 MHz. if the CPU running at higher than 100 Mhz, user must lower CPU frequency first than erase and program flash.

#### 2.2.1 Flash ROM API

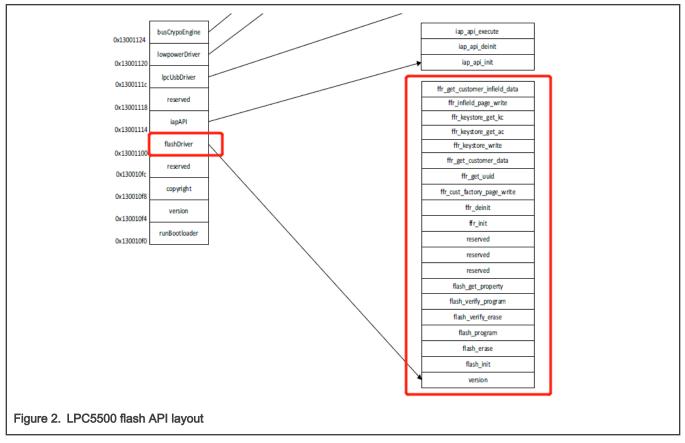

The BootROM of LPC5500 series provides a set of Flash APIs for users. ROM API table is located at the address of 0x130010f0.

Figure 2 shows the ROM API address layout.

SDK provides full examples of how to use flash driver to operate internal flash. The example is located at:

|boards||pcxpresso55s28|driver\_examples|flashiap

We suggest using ROM API to access data flash and PFR. The flash register operation is not recommended.

#### 2.2.2 Flash Init

To use Flash ROM API to operate flash, you need first initialized flash instance. The FLASH\_Init API in SDK needs to pass a flash\_config\_t structure. When calling this API, the structure returns some flash parameters, such as, FLashSecterSize, TotalFlashSize, PageSize, etc. Users should check and confirm that the parameters are correct.

```

#define ROM_API_TREE ((*uint32_t)0x130010f0)

#define FLASH_API_TREE ((flash_driver_interface_t*) ROM_API_TREE[3])

flash_config_t flashConfig;

status = FLASH_API_TREE->flash_init(&flashConfig);

```

Figure 3. Flash Init code

#### 2.2.3 Flash erase

The flash erase API is easy to use. The start and lengthinBytes filed need to be 512 bytes aligned.

```

#define ERASE_KEY 0x6b65666b

status = FLASH_API_TREE->flash_erase(&flashConfig, 0x0, 0x4000, ERASE_KEY);

```

Figure 4. Flash erase

#### 2.2.4 Flash program

Same as Flash Erase API, the start and lengthinBytes filed need to be 512 bytes aligned.

#### 2.2.5 Flash read

Accessing or reading blank flash area will hit hardfault, so before performing the access/read, check whether the flash region is blank or not.

SDK provides an API named **FLASH\_VerifyErase** for blank checking. Before accessing or reading a flash page that we don't know blank or not, use **FLASH\_VerifyErase** to confirm. If the page is blank, the content in this page is all 0xFF, and reading or accessing it directly will hit hardfault. If the page is not blank, it can be read/access as usual.

Summary

```

status = FLASH_VerifyErase(&flashInstance, flash_addr, 512);

if (status == kStatus_Success)

{

/* it's a erased flash, just return all 0xFF */

memset(read_buf, 0xFF, sizeof(read_buf));

}

else

{

/* flash not erased, AHB read */

memcpy(read_buf, (void*)flash_addr, sizeof(read_buf));

}

```

Figure 6. Flash read

### 3 Summary

#### 3.1 Make sure core clock under 100 MHz when operating flash

All flash operations must be done when the core clock is under 100 MHz.

#### 3.2 Caution on PFR region

Special caution needs to be taken when you operate last few pages near PFR. Do not perform a sector erase (erase 32 KB) of the last flash sector.

### 3.3 Using ROM API to erase/program flash

Use ROM API to access data flash and PFR. The flash register operation is not recommended because it's easy to erase PFR accidently.

#### 3.4 Using ROM API: FLASH\_VerifyErase before read flash data to void Hardfault issue

Call **FLASH\_VerifyErase** before reading flash content. To make sure it's not an erased/empty page. Otherwise, it might trigger HardFault.

#### 3.5 Align

ROM API: The start and lengthinBytes fileds of Flash\_Program and Flash\_Erase need to be page aligned.

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities on customer's applications and products, and NXP accepts no liability for any vulnerability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, eIQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2020.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 08/2020 Document identifier: AN12949

# arm