# Power Management on LPC55S3x/LPC553x

Rev. 0 — 21 February 2022 Application Note

## 1 Introduction

The LPC55S3x/LPC553x family offers a wide peripheral portfolio with focus on low power consumption. This application note describes all the important parts of power management on the LPC553 family and summarizes the main difference and additional features from the previous families.

The following chapters focus on the LPC55S3x/LPC553x power domains, power API, and power-optimization technique. This application note discusses how to use the power management in RT500. The description of the internal DC-DC and LDO regulator functionality on LPC55S3x/LPC553x is in *Using the DC-DC and LDO features* (document AN13528).

| 1 | Introduction                  |     |

|---|-------------------------------|-----|

| 2 | Power domain and distribution | '   |

| 3 | Power API                     | . 4 |

| 4 | LPC55S3x/LPC553x power modes  | 3   |

|   |                               | . 7 |

| 5 | Power-optimization techniques |     |

| 6 | Conclusion                    | 1(  |

| 7 | Revision history              | 1(  |

|   | Legal information0            |     |

Legal information......11

Contents

## 2 Power domain and distribution

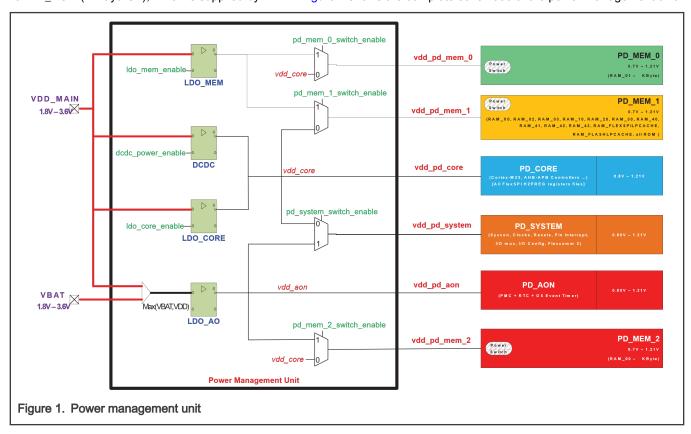

The LPC55S3x/LPC553x family has 6 power domains. All power domains are powered via the VDD\_MAIN power supply, except for PD\_AON (Always-On), which is supplied by VBAT. Figure 1 shows the complete schematic of the power management unit:

The power domains on LPC553 are the following:

## 2.1 Always-On Power Domain (PD\_AON)

The Always-On Power Domain consists of:

- · A set of digital units: Power Management Controller (PMC), RTC, and OS Event Timer.

- Several analog modules located in the Power Management Unit (PMU): FRO32K, XTAL32K, FRO1M, and Analog Comparator.

- · 5 wake-up GPIOs.

This power domain has power when VBAT or VDDMAIN are available with a sufficient voltage [1.8 V - 3.6 V].

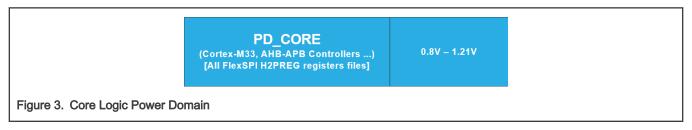

## 2.2 Core Logic Power Domain (PD\_CORE)

The Core Logic Power Domain consists of nearly all digital components, such as the Cortex-M33 CPU, system DMA, and almost the whole Flexcom. All digital units not located in the PD\_AO or PD\_SYSTEM power domains are part of the Core Logic Power Domain.

The Core Logic Power Domain is supplied by:

- The LDO\_CORE (configured in the high-power mode) or the DC-DC in ACTIVE.

- The LDO\_CORE (configured in the low-power mode) during DEEP-SLEEP.

The Core Logic Power Domain is shut down in the POWER-DOWN and DEEP-POWER-DOWN low-power modes.

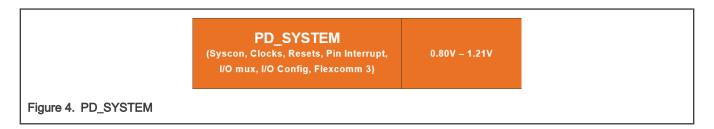

## 2.3 System Power Domain (PD\_SYSTEM)

The System Power Domain consists of:

- System-critical digital components: Reset and Clock controllers, System Configuration (SYSCON).

- All GPIOs with their associated configuration and multiplexing (IOCON).

- The Flexcomm3 (UART, SPI, and I2C) and both Group GPIO Input Interrupts (GINT0, GINT1).

- · The PUF Keys Store.

The System Power Domain is supplied by:

- The LDO\_CORE (configured in the High-Power Mode) or the DC-DC in ACTIVE.

- The LDO\_CORE (configured in the Low-Power Mode) during DEEP SLEEP.

- The LDO\_AO during POWER DOWN.

The System Power Domain is shut down during the DEEP POWER DOWN low-power mode.

3 / 13

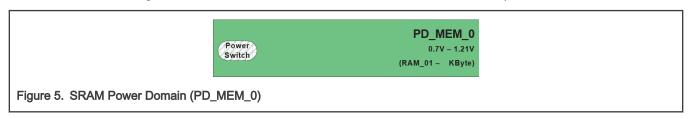

## 2.4 First SRAM Power Domain (PD\_MEM\_0)

The first SRAM Power Domain (PD\_MEM0) consists in a single SRAM instance: RAM\_01 (4 kB). PD\_MEM0 is supplied by:

- The LDO\_CORE (configured in the high-power mode) or the DC-DC in ACTIVE.

- The LDO\_MEM during DEEP-SLEEP, POWER-DOWN, and DEEP-POWER-DOWN low-power modes.

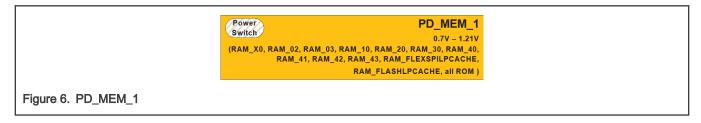

## 2.5 Second SRAM Memories Power Domain (PD\_MEM\_1)

The second SRAM Power Domain (PD\_MEM1) consists of these SRAM instances: RAM\_X0 (16 kB), RAM\_02 (4 kB), RAM\_03 (4 kB), RAM\_10 (32 kB), RAM\_20 (32 kB), RAM\_30 (16 kB), RAM\_40 (4 kB), RAM\_41 (4 kB), RAM\_42 (4 kB), RAM\_43 (4 kB). PD MEM1 is supplied by:

- The LDO\_CORE (configured in the high-power mode) or the DC-DC in ACTIVE.

- The LDO MEM during DEEP-SLEEP, POWER-DOWN, and DEEP-POWER-DOWN low-power modes.

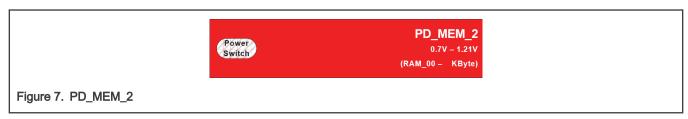

### 2.6 Third SRAM Memories Power Domain (PD\_MEM\_2)

The third SRAM Memories Power Domain (PD\_MEM2) consists of a single SRAM instance: RAM\_00 (4 kB).

PD\_MEM2 is supplied by:

- The LDO\_CORE (configured in the High-Power Mode) or the DC-DC in ACTIVE.

- The LDO\_AO during the DEEP SLEEP, POWER DOWN, and DEEP POWER DOWN low-power modes.

Table 1 summarizes the power state of the different power domains according to the power modes.

Table 1. Power modes vs power domains

| MODE               | PD_CORE | PD_SYSTEM | PD_AON | PD_MEM_0     | PD_MEM_1     | PD_MEM_2     |

|--------------------|---------|-----------|--------|--------------|--------------|--------------|

| ACTIVE             | ON      | ON        | ON     | ON           | ON           | ON           |

| SLEEP              | ON      | ON        | ON     | ON           | ON           | ON           |

| DEEP SLEEP         | ON      | ON        | ON     | Configurable | Configurable | Configurable |

| POWER DOWN         | OFF     | ON        | ON     | Configurable | Configurable | Configurable |

| DEEP<br>POWER DOWN | OFF     | OFF       | ON     | Configurable | Configurable | Configurable |

## 3 Power API

The power API serves as a control of device power consumption. The entry to low-power modes can be configured through simple calls to the low-power profile API. The power API functions are available in the SDK software package at LPC553x-LPC55S3x| ARM Cortex-M33 32-bit Microcontrollers (MCUs)|NXP.

## 3.1 Power API categories

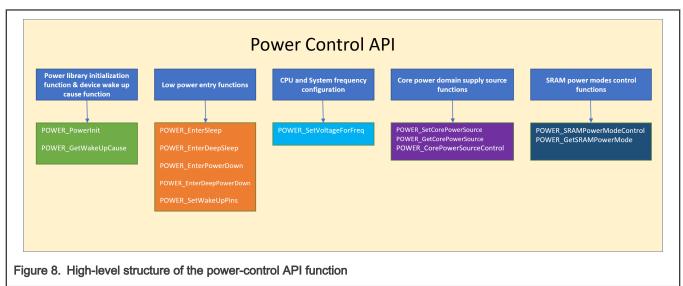

The power API on LPC55S3x/LPC553x is divided into 5 categories:

- · Power-library-initialization function and device wake-up cause function.

- · Low-power entry functions prepare the device to enter low-power modes.

- · Core power domain supply source functions.

- · CPU and system frequency configuration.

- · Manages power consumption of device SRAM instances.

- Figure 8 shows the high-level structure of the power-control API function.

The following part shortly summarizes the power library API. For detailed information, see the LPC55S3x/LPC553x reference manual or *Low-Power Modes and Wake-Up Time* (document AN13056).

Application Note 4/13

## 3.2 Power library initialization function and device wake-up cause function

#### API function POWER\_PowerInit:

```

power status POWER PowerInit (void);

```

This routine checks the status of the hardware boot sequence and performs a power-related initialization of the system (such as configuring internal voltage regulators).

#### API function POWER GetWakeUpCause:

```

void POWER GetWakeUpCause (power reset cause t * reset cause,

power boot mode t * boot mode

power wakeup pin t * wakeup pin cause)

```

This routine returns key information related to device events, such as the most recent reset cause, the most recent low-power mode, and the most recent wake-up pin events.

## 3.3 Low-power entry functions

#### API Function POWER\_EnterSleep:

```

void POWER EnterSleep (void)

```

The SLEEP mode saves power by stopping the Cortex-M33 execution without affecting peripherals or requiring significant wake-up time.

The part wakes up from the SLEEP mode after:

- Any interrupt enabled in the CORTEX-M33 Nested Vector Interrupt Controller (NVIC) arrives at the processor.

- Any chip reset occurs (Power-on Reset, Brownout detector reset, pin reset, and so on).

#### API function POWER\_EnterDeepSleep:

```

void POWER EnterDeepSleep ( uint32 t exclude from pd[2] uint32 t sram retention ctrl uint32 t

wakeup_interrupts[4] uint32_t hardware_wake_ctrl)

```

This routine prepares the part and then enters the DEEP-SLEEP low-power mode. The API function configures which analog/ digital components remain running, so that an interrupt from one of these analog/digital peripherals can wake up the part.

### API function POWER\_Enterpower down:

```

void POWER EnterPowerDown ( uint32 t exclude from pd[1] uint32 t sram retention ctrl uint32 t

wakeup_interrupts[2] uint32_t cpu_retention_addr)

```

This routine configures the POWER-DOWN low-power mode. It allows controlling which peripherals are powered up and which SRAM instances are in a retention state during POWER-DOWN.

#### API function POWER\_EnterDeepPowerDown:

```

void POWER EnterDeepPowerDown ( uint32 t exclude from pd[1] uint32 t sram retention ctrl uint32 t

wakeup interrupts[2] uint32 t wakeup io ctrl)

```

This routine prepares the part and then enters the DEEP-POWER-DOWN low-power mode. The API function configures which analog/digital components remain running, so that an interrupt from one of these analog/digital peripherals can wake up the part.

#### API function POWER SetWakeUpPins:

```

void POWER SetWakeUpPins ( uint32 t wakeup io cfg sr uint32 t wakeup io ctrl)

```

Power Management on LPC55S3x/LPC553x, Rev. 0, 21 February 2022 5 / 13 This routine configures the 5 wake-up pins before entering the DEEP-SLEEP or POWER-DOWN modes. It is expected to be called before calling "POWER\_EnterDeepSleep" or "POWER\_EnterPowerDown". The API function configures which wake-up pins can wake up the device from a low-power mode and sets up some other pin parameters, such as the internal pull-up/pull-down and the rising or falling edge detections.

## 3.4 CPU and system frequency configuration

API function POWER SetVoltageForFreq:

```

void POWER_SetVoltageForFreq (uint32_t system_freq_hz)

```

The "POWER\_SetVoltageForFreq" API configures the device's internal power-control settings according to the calling arguments. The goal is to prepare on-chip power regulators (DC-DC converter/core and always-on low-drop-out regulators) to deliver the amount of power needed for the requested performance level, as defined by the CPU operating frequency.

## 3.5 Core power domain supply source functions

API function POWER SetCorePowerSource:

```

power_status_t POWER_SetCorePowerSource (power_core_pwr_source_t pwr_source)

```

The "POWER\_SetCorePowerSource" API selects the core logic supply source from the DC-DC buck converter and the core logic low drop-out regulator (LDO\_CORE, in both the high-power and low-power modes). When a supply source is selected, the other internal sources are disabled. For example, if you select the DC-DC buck converter, the LDO\_CORE (for both the high-power and low-power modes) will be disabled.

API function POWER\_GetCorePowerSource:

```

power_core_pwr_source_t POWER_GetCorePowerSource (void)

```

The "POWER\_GetCorePowerSource" API returns the current core logic supply source.

API function POWER CorePowerSourceControl:

```

power_status_t POWER_CorePowerSourceControl (power_core_pwr_source_t pwr_source

power_core_pwr_state_t pwr_state)

```

The "POWER\_GetCorePowerSource" API allows controlling the state (enabled or disabled) of the core logic internal regulators (DC-DC and LDO\_CORE).

## 3.6 SRAM power modes control functions

API function POWER\_SRAMPowerModeControl:

```

power_status_t POWER_SRAMPowerModeControl (power_sram_bit_t sram_inst

power_sram_pwr_mode_t pwr_mode)

```

The "POWER\_SRAMPowerModeControl" API allows to configure the SRAM instances' (low) power modes when the part is in the ACTIVE mode.

API function POWER GetSRAMPowerMode:

```

power_status_t POWER_GetSRAMPowerMode (power_sram_index_t sram_index)

```

The "POWER\_GetSRAMPowerMode" API allows to determine the power mode of a single SRAM instance when the part is in the ACTIVE mode.

Application Note 6/13

## 4 LPC55S3x/LPC553x power modes

The LPC55S3x/LPC553x includes the following power-saving modes and wake-ups:

- Integrated PMU (Power Management Unit) to minimize power consumption.

- · Configurable wake-up options form peripheral interrupts.

- The Micro-Tick Timer running from the watchdog oscillator can be used to wake-up the device from all low-power modes.

- The Real-Time Clock (RTC), running from the 32.768 kHz clock, can be used to wake up the device from all low-power modes.

- · Power-On Reset (POR).

- Brownout Detector (BOD) for VBAT\_DC-DC with separate thresholds for forced reset.

The LPC55S3x/LPC553x module implements 4 basic power modes: Active, Sleep, Deep Sleep, Power down, and Deep Power down. The following section explains the difference between the power modes using the following decoding bullets:

- ↑ ON

- ↓ OFF

- Software selection: ON, OFF, or low power

#### 4.1 Active

This is the default mode after RESET.

• ↑ The clocks to the CPU, memories, and peripherals are enabled.

#### 4.2 Sleep

- ↓ Stops the clock to the CPU (the system clock).

- ↓ Suspends the instruction execution until RESET or an interrupt occurs.

- \( \subseteq \text{The peripherals can be clocked and continue to operate.} \)

- \( \subseteq \text{The peripherals may generate interrupts to resume the CPU operation.} \)

- > The SRAM that was not shut down maintains its content.

- ↑ The CPU state registers and peripheral registers are maintained.

- ↑ The pins' logic levels remain static.

### 4.3 Deep sleep

This mode is configurable and can potentially turn off almost the whole on-chip power consumption, resulting in longer wake-up times.

- ↓ The CPU clock is shut down.

- 1 The power consumed by the analog peripherals and the dynamic power used by the processor.

- \( \subseteq \text{The peripherals (if not configured) receive no internal clocks.} \)

- \( \subseteq \text{The individual blocks may be in the on, low-power, or off states; as defined in the software.

- > The device features can be automatically disabled.

- > The SRAM that was not shut down maintains its content.

- \( \square\) This runs the selectable peripherals.

- \( \subseteq \text{The analog blocks are powered down by default, but they can be configured by software.

Application Note 7/13

• ↑ The device registers maintain their content.

#### 4.4 Power Down

- 1 Turns off nearly all on-chip power consumption by eliminating power.

- All registers lose their internal states, except for those located in the PD\_SYSTEM and PD\_AO power domains.

- \(\sim \) The SRAM and register content is retained (software-configurable via power API).

- ↓ All registers lose their internal states, except for those located in the PD\_SYSTEM and PD\_AO power domains.

- \(\sim \) The GPIO group interrupts (GINT0 and GINT1), selected serial peripherals in Flexcomm3 (SPI, I2C, USART), RTC, OS, Event Timers, and Analog Comparator can be left running to wake up the device.

### 4.5 Deep power down

- \quad The entire chip's clock and power are shut down.

- \$\rightarrow\$ Registers are not retained (except for the PMC, RTC, and OS timer).

- \(\simega\) The SRAM and register content is retained (software-configurable via the power API).

- ↓ All functional pins are tri-stated, except for the 5 wake-up pins and the RESET pin.

- ↑ The RTC is on through VDD\_AON.

## 5 Power-optimization techniques

The following tables show various clocks and peripherals that can be software-configured in reduced-power modes, such as Sleep, Deep Sleep, Power Down, and Deep Power Down.

Table 2. Clocks in reduced power modes

|         | Clocks                                |                         | Device Low-Power Modes |               |                 |  |

|---------|---------------------------------------|-------------------------|------------------------|---------------|-----------------|--|

| Clock   | Description                           | Sleep                   | Deep Sleep             | Power Down    | Deep Power Down |  |

| FRO1MHz | 1-MHz Free<br>Running Oscillator      | ON                      | SW configured          | SW configured | SW configured   |  |

| FRO192M | High-Speed Free<br>Running Oscillator | ON                      | SW configured          | OFF           | OFF             |  |

| FRO32K  | 32-kHz Free<br>Running Oscillator     | Same state as in ACTIVE | SW configured          | SW configured | SW configured   |  |

| XTAL32K | 32-kHz<br>Crystal Oscillator          | Same state as in ACTIVE | SW configured          | SW configured | SW configured   |  |

| XTALHF  | High-Frequency<br>Crystal Oscillator  | Same state as in ACTIVE | SW configured          | OFF           | OFF             |  |

| PLL0    | Phase-Locked Loop<br>Module 0         | Same state as in ACTIVE | SW configured          | OFF           | OFF             |  |

| PLL1    | Phase-Locked Loop<br>Module 1         | Same state as in ACTIVE | SW configured          | OFF           | OFF             |  |

Application Note 8 / 13

Table 3. Peripherals in reduced power modes

| Peripl        | nerals                                                             | Device Low-Power Modes  |               |               |                    |

|---------------|--------------------------------------------------------------------|-------------------------|---------------|---------------|--------------------|

| Peripheral    | Description                                                        | Sleep                   | Deep Sleep    | Power Down    | Deep Power<br>Down |

| DC-DC         | Bulk DC-<br>DC Converter                                           | Same state as in ACTIVE | OFF           | OFF           | OFF                |

| BIAS          | Analog References                                                  | ON                      | ON            | SW configured | OFF                |

| BODCORE       | Core Logic Supply<br>Brownout Detector                             | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| BODVDDMAIN    | VDD_MAIN supply Brownout Detector                                  | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| USBFSPHY      | USB Full-Speed<br>Physical Interface                               | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| COMP          | Analog Comparator                                                  | Same state as in ACTIVE | SW configured | SW configured |                    |

| LDOEFUSEPROG  | eFUSE Programming<br>Low Drop-<br>Out Regulator                    | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| LDOXTALHF     | High-Frequency<br>Crystal Oscillator<br>Low Drop-<br>Out Regulator | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| LDOFLASHNV    | Non-Volatile Flash  Macro Low Drop- Out Regulator                  | ON                      | OFF           | OFF           | OFF                |

| PLL0_SSCG     | PLL0 Spread<br>Spectrum<br>Clock Generator                         | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| HSCMP 0, 1, 2 | High-<br>Speed Comparator                                          | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| OPAMP 0, 1, 2 | Operational Amplifier                                              | Same state as in ACTIVE | SW configured | OFF           | OFF                |

| VREF          | ADCs/DACs Analog<br>Reference Module                               | Same state as in ACTIVE | SW configured | SW configured | OFF                |

| CMPBIAS       | High-Speed<br>Comparators Biasing                                  | Same state as in ACTIVE | SW configured | OFF           | OFF                |

Table continues on the next page...

Table 3. Peripherals in reduced power modes (continued)

| Periph             | erals                           | Device Low-Power Modes  |               |            |                    |

|--------------------|---------------------------------|-------------------------|---------------|------------|--------------------|

| Peripheral         | Description                     | Sleep                   | Deep Sleep    | Power Down | Deep Power<br>Down |

| HSCMPx_DAC (0,1,2) | HSCMP1<br>(Internal) DAC        | Same state as in ACTIVE | SW configured | OFF        | OFF                |

| DAC 0, 1, 2        | Digital-to-<br>Analog Converter | Same state as in ACTIVE | SW configured | OFF        | OFF                |

| STOP_DAC 0, 1, 2   | DAC Stop Mode                   | Same state as in ACTIVE | SW configured | OFF        | OFF                |

## 6 Conclusion

The LPC55S3x/LPC553x family opens the way for a wide range of low-power applications. Including the internal LDO regulator allows using the MCU in more complex systems with their own power domain. The complete description of DC-DC and internal LDO usage is described in *Using the DC-DC and LDO features* (document AN13528).

## 7 Revision history

Table 4. Revision history

| Revision number | Date             | Substantive changes |

|-----------------|------------------|---------------------|

| 0               | 21 February 2022 | Initial release     |

Application Note 10 / 13

## Legal information

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

Application Note 11/13

12 / 13

Translations — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately.

Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamlQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile — are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved.

Airfast — is a trademark of NXP B.V.

Bluetooth — the Bluetooth wordmark and logos are registered trademarks owned by Bluetooth SIG, Inc. and any use of such marks by NXP Semiconductors is under license.

Cadence — the Cadence logo, and the other Cadence marks found at www.cadence.com/go/trademarks are trademarks or registered trademarks of Cadence Design Systems, Inc. All rights reserved worldwide.

CodeWarrior — is a trademark of NXP B.V.

ColdFire — is a trademark of NXP B.V.

ColdFire+ — is a trademark of NXP B.V.

EdgeLock — is a trademark of NXP B.V.

EdgeScale — is a trademark of NXP B.V.

EdgeVerse — is a trademark of NXP B.V.

**Application Note**

elQ — is a trademark of NXP B.V.

FeliCa — is a trademark of Sony Corporation.

Freescale — is a trademark of NXP B.V.

HITAG — is a trademark of NXP B.V.

ICODE and I-CODE — are trademarks of NXP B.V.

Immersiv3D — is a trademark of NXP B.V.

12C-bus - logo is a trademark of NXP B.V.

Kinetis — is a trademark of NXP B.V.

Layerscape — is a trademark of NXP B.V.

Mantis — is a trademark of NXP B.V.

MIFARE — is a trademark of NXP B.V.

NTAG — is a trademark of NXP B.V.

Processor Expert — is a trademark of NXP B.V.

QorlQ — is a trademark of NXP B.V.

SafeAssure — is a trademark of NXP B.V.

SafeAssure — logo is a trademark of NXP B.V.

Synopsys — Portions Copyright © 2021 Synopsys, Inc. Used with permission. All rights reserved.

Tower — is a trademark of NXP B.V.

UCODE - is a trademark of NXP B.V.

VortiQa — is a trademark of NXP B.V.

Power Management on LPC55S3x/LPC553x, Rev. 0, 21 February 2022

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP B.V. 2022.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 21 February 2022 Document identifier: AN13575