# AN13818 LPC86x Low-power and Wake-up Optimization Rev. 0 — 8 May 2023

**Application note**

#### **Document Information**

| Information | Content                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------|

| Keywords    | LPC86x, low power                                                                                                   |

| Abstract    | This application note introduces how to optimize the power consumption and wake-up time with the low-power feature. |

#### Introduction 1

The low-power feature is an important demand in most of consumer applications. To reduce the power consumption and wake-up time, set the chip into different power modes and turn off these unused modules or reduce the system clock. This application note introduces how to optimize the power consumption and wake-up time with the low-power feature.

#### LPC86x overview 2

The LPC86x is an Arm Cortex-M0+ based, low-cost 32-bit MCU operating at CPU frequencies of up to 60 MHz in LPC series. It supports up to 64 kB of flash memory and 8 kB of SRAM.

The peripheral complements of the LPC86x include a CRC engine, one I3C bus interface, one I2C bus interface, up to three USARTs, up to two SPI interfaces, one multirate timer, self-wake-up timer, two FlexTimers, one general-purpose 32-bit counter/timer, a DMA, one 12-bit ADC, one analog comparator, functionconfigurable I/O ports through a switch matrix, an input pattern match engine, and up to 54 general-purpose I/O pins.

Features relevant to power include:

- · Reduced power modes and wake-up:

- Integrated Power Management Unit (PMU) to minimize power consumption.

- Reduced power modes: Sleep mode, Deep sleep mode, Power-down mode, and Deep power-down mode.

- Wake-up from Deep sleep mode and Power-down mode on activity on USART, SPI, I2C, and I3C peripherals.

- Timer-controlled self-wake-up from Deep power-down mode.

- Power-On Reset (POR)

- Brownout detect (BOD)

- Single power supply 1.8 3.3 v

#### 3 Power management

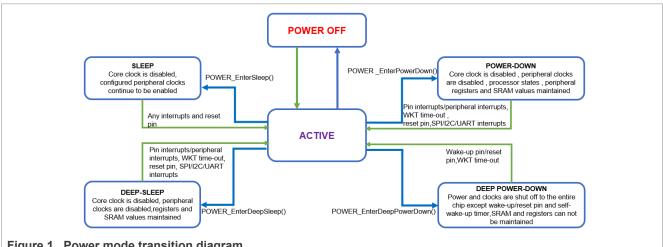

Figure 1 shows the four low-power modes. And in different power modes, the peripherals can be software configurable or power on/off automatic. When the low-power feature is used, only FRO or low-power oscillator can afford the system clock.

Figure 1. Power mode transition diagram

AN13818

**Note:** When the chip enters Deep sleep mode, Power-down mode, or Deep power-down mode, FRO provides the system clock and the FRO output (FRO divider) is disabled. The system can only set to FRO18M/FRO24/FRO30/FRO36M/FRO48M/FRO60M before entering the Deep sleep mode or Power-down mode.

| Peripheral                   | Sleep mode            | Deep sleep mode       | Power-down mode       | Deep power-down mode  |

|------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| FRO                          | Software configurable | ON                    | OFF                   | OFF                   |

| FRO output                   | Software configurable | OFF                   | OFF                   | OFF                   |

| Flash                        | Software configurable | ON                    | OFF                   | OFF                   |

| BOD                          | Software configurable | Software configurable | Software configurable | OFF                   |

| PLL                          | Software configurable | OFF                   | OFF                   | OFF                   |

| SysOsc                       | Software configurable | OFF                   | OFF                   | OFF                   |

| WDosc/WWDT                   | Software configurable | Software configurable | Software configurable | OFF                   |

| Digital peripherals          | Software configurable | OFF                   | OFF                   | OFF                   |

| WKT/Low-<br>power oscillator | Software configurable | Software configurable | Software configurable | Software configurable |

| ADC                          | Software configurable | OFF                   | OFF                   | OFF                   |

| Comparator                   | Software configurable | OFF                   | OFF                   | OFF                   |

Table 1. Peripheral configuration in reduced power modes

## 3.1 Power modes

There are five power modes on LPC86x listed as below, from highest to lowest:

1. Active mode:

The part is in active mode when it is fully powered and operational after booting.

2. Sleep mode:

This mode can only affect the Arm Cortex-M0+ core. Peripherals and memories are active.

- 3. Deep sleep mode and Power-down mode:

- Deep sleep mode and Power-down mode cannot only affect the core. These two modes can also affect memories and peripherals.

- In the Deep sleep mode, the peripherals receive no internal clocks. The flash is in standby mode. The SRAM memory and all peripheral registers as well as the processor maintain their internal states. The WWDT, WKT, and BOD can remain active to wake up the system on an interrupt.

• In the Power-down mode, different from the Deep sleep mode, the flash memory is powered down.

4. Deep power-down mode:

In the Deep power-down mode, the entire system is shut down. Only the general-purpose registers in the PMU register maintain internal states and the self-wake-up timer is not shut down. The WAKEUP pin or chip RESET can wake it up.

# 3.2 Wake-up process

Wake-up sources can wake up chip in different power modes, such as, peripherals interrupts, Self-wake-up timer, reset pin. <u>Table 2</u> describes the wake-up sources for different power modes.

| Table 2. | Wake-up | sources | for | power | modes |

|----------|---------|---------|-----|-------|-------|

|----------|---------|---------|-----|-------|-------|

| Power mode                    | Wake-up source                                | Conditions                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep                         | Any interrupt                                 | Enable interrupt in NVIC.                                                                                                                                                                                                                                                                                                                                                  |

|                               | RESET pin PICO_5                              | Enable the reset function in the PINENABLE0 register via switch matrix.                                                                                                                                                                                                                                                                                                    |

| Deep-sleep and Power-<br>down | Pin interrupts                                | Enable pin interrupts in NVIC and STARTERP0 register via switch matrix                                                                                                                                                                                                                                                                                                     |

|                               | BOD interrupts                                | <ul> <li>Enable interrupt in NVIC and STARTERP1 registers.</li> <li>Enable interrupt in BODCTRL register.</li> <li>BOD powered in PDSLEEPCFG register.</li> </ul>                                                                                                                                                                                                          |

|                               | BOD reset                                     | <ul> <li>Enable interrupt in BODCTRL register.</li> <li>BOD powered in PDSLEEPCFG register</li> </ul>                                                                                                                                                                                                                                                                      |

|                               | WWDT interrupts                               | <ul> <li>Enable interrupt in NVIC and STARTERP1 registers.</li> <li>WWDT running. Enable WWDT in WWDT MOD register and feed.</li> <li>Enable reset in WWDT MOD register.</li> <li>WDOsc powered in PDSLEEPCFG register.</li> </ul>                                                                                                                                         |

|                               | WWDT reset                                    | <ul> <li>WWDT running.</li> <li>Enable reset in WWDT MOD register.</li> <li>WDOsc powered in PDSLEEPCFG register.</li> </ul>                                                                                                                                                                                                                                               |

|                               | Self-wake-up Timer<br>(WKT) time-out          | <ul> <li>Enable interrupt in NVIC and STARTERP1 registers.</li> <li>Enable ultra low-power oscillator in the DPDCTRL register in the PCON block.</li> <li>Select low-power clock for WKT clock in the WKT CTRL register.</li> <li>Start the WKT by writing a time-out value to the WKT COUNT register.</li> </ul>                                                          |

|                               | Interrupt from<br>USART/SPI/I2C<br>peripheral | <ul> <li>Enable interrupt in NVIC and STARTERP1 registers.</li> <li>Enable USART/SPI/I2C interrupts.</li> <li>Provide an external clock signal to the peripheral.</li> <li>Configure the USART in synchronous slave mode and I2C and SPI in slave mode.</li> </ul>                                                                                                         |

|                               | Interrupt from peripheral                     | <ul> <li>Enable interrupt in NVIC and STARTERP1 registers.</li> <li>Switch FCLK clock source to the WDOsc.</li> </ul>                                                                                                                                                                                                                                                      |

|                               | RESET pin PIO0-5                              | Enable the reset function in the PINENABLE0 register via switch matrix.                                                                                                                                                                                                                                                                                                    |

| Deep power-down               | WAKEUP pin<br>PIO0-4                          | Enable the WAKEUP function in the DPDCTRL register in the PMU.                                                                                                                                                                                                                                                                                                             |

|                               | RESET pin PIO0_5                              | Enable the reset function in the DPDCTRL register in the PMU to allow wake-up in the Deep power-down mode.                                                                                                                                                                                                                                                                 |

|                               | WKT time-out                                  | <ul> <li>Enable the ultra low-power oscillator in the DPDCTRL register in the PMU.</li> <li>Enable the ultra low-power oscillator to keep running in deep power-down mode in the DPDCTRL register in the PMU.</li> <li>Select low-power clock for WKT clock in the WKT CTRL register.</li> <li>Start WKT by writing a time-out value to the WKT COUNT register.</li> </ul> |

# 4 **Power configurations**

The LPC86x supports a variety of power control features. In the active mode, when the chip is running, to optimize power and clocks to selected peripherals for power consumption, configure registers. In the four reduced power modes (sleep, deep-sleep, power-down, and deep power-down), to optimize the power consumption and to select the wake-up source, set the registers to different modes.

## 4.1 Active mode

In the active mode, clock the Arm Cortex-M0+ core, memories, and peripherals with the system clock or main clock.

The chip runs in active mode after reset. The default power configuration is determined by the reset values of the PDRUNCFG and SYSAHBCLKCTRL registers. The power configuration can be changed during the runtime.

## 4.2 Sleep mode

In sleep mode, the core clock stops and execute the instructions when a reset or interrupt occurs.

To configure power consumption in sleep mode, perform the same settings as in the active mode:

- The clock remains running.

- The system clock frequency remains the same as in the active mode, but the processor is not clocked.

- Analog and digital peripherals are selected as in the active mode.

#### 4.3 Deep sleep mode

In the Deep sleep mode, the system clock remains, but it is not clocked to the processor. All analog blocks are powered down, except for the BOD circuit and the low-power oscillator, which can be selected or deselected during the Deep sleep mode in the PDSLEEPCFG register.

As shown in <u>Figure 1</u>, the Deep sleep mode powers off all the analog peripherals and eliminates all dynamic power used by the processor itself, memory systems and related controllers, and internal buses. The processor state and registers, peripheral registers, and internal SRAM values are maintained, and the logic levels of the pins remain static.

Power consumption in Deep sleep mode is determined by the deep-sleep power configuration setting in the PDSLEEPCFG register:

- The low-power oscillator can be left running in the Deep sleep mode if required for the WWDT.

- The BOD circuit can be left running in the Deep sleep mode if required by the application.

### 4.4 Power-down mode

In the Power-down mode, the system clock to the processor and analog blocks power configuration are same as the Deep sleep mode. If the low-power oscillator is selected. The main clock and therefore all peripheral clocks are disabled except for the clock to the watchdog timer. FRO and flash are powered down Compared to the Deep sleep mode, the power consumption decreases.

Peripheral configurations in the Power-down mode are same as the Deep sleep mode Compared to the Deep sleep mode, its wake-up time is longer.

Configure the power consumption the in the Power-down mode with the power configuration setting in the PDSLEEPCFG register, same as for the Deep sleep mode.

AN13818 Application note

#### 4.5 Deep power-down mode

As shown in Table 1, the Deep power-down mode has no configuration options. All clocks, the core, and all peripherals are powered down. Only the WAKEUP pin, RESET pin, and the self-wake-up timer are powered.

During the Deep power-down mode, the contents of the SRAM and registers are not retained except for a small amount of data which can be stored in the general-purpose registers of the PMU blocks.

#### Example to achieve typical data on data sheet 5

#### 5.1 Hardware environment

- LPCXpresso860-MAX EVK

- · Personal computer

- USB cable

- Digital multimeter for current measure

- · Oscillograph for wake-up time measure

### 5.2 Hardware setup

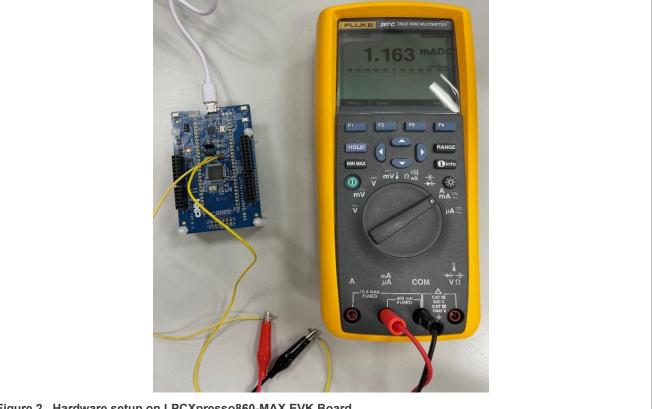

To measure the power consumption, remove R51 and connect the multimeter to JP2.

Figure 2. Hardware setup on LPCXpresso860-MAX EVK Board

### 5.3 Software environment setup

MCUXpresso IDE v11.5.1\_7266

- · Serial terminal program, for example TeraTerm or Putty

- SDK\_2\_11\_1\_LPCXpresso860MAX

#### 5.4 Reference software and hardware implementation

During the power consumption and wake-up time test, uart0 is used to communicate with PC for test function select. In the test code, turn off the clock for uart0 and any other unused peripherals after the test function is selected. It does not affect the power consumption.

To make the power consumption as little as possible, configure the test code and EVK as below:

- Code configuration:

- Drive all the GPIO pin to low and output except the wake-up pin PIO0\_4, reset pin PIO0\_5 and the pin used for wake-up time test.

- Set the optimization level to highest for the wake-up time test

- Set the Sleep mode/Deep sleep mode/Power-down mode wakeup test pin to output low in PIN INTO IRQHandler() and locate the ISR into RAM for wake-up time test

- Set the Deep power-down mode wakeup test pin PIO1 5 to output high in ResetISR().

- Disable BOD reset and power down BOD.

- Power down the unused analog blocks.

- Attach the clock of these unused peripherals to none.

- EVK modification:

- Remove the R38, R39, R52, R60 to disconnect the on-board debugger to decrease the sink current.

- Remove the R5, R6, R8 to disconnect the LED.

- Remove the C20 for the Deep power-down mode wakeup time test when the wakeup source is reset pin.

### 5.5 Running and measure results

```

/* Copyright 2023 NXP. NXP Confidential. This software is owned or controlled by

NXP and may only be

* used strictly in accordance with the applicable license terms found at

* https://www.nxp.com/LA_OPT_NXP_SW. The "production use license" in Section 2.3

in the NXP SOFTWARE

```

\* LICENSE AGREEMENT is expressly granted for this software.

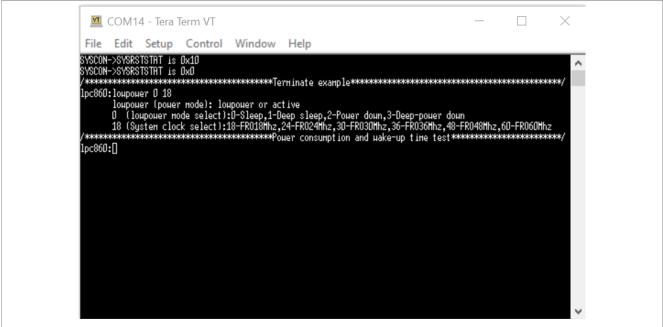

Figure 3. Power consumption test terminal

**Note:** To use the USB to UART module to communicate with the device, disconnect the module when testing the power consumption. It may take some sink current to the device. And set the transmit format to CR+LF in terminate tool.

| System clock<br>in power mode | Sleep (mA)<br>VDD = 3.3 V | Deep sleep (mA)<br>VDD = 3.3 V | Power-down (uA)<br>VDD = 3.3 V | Deep power-<br>down (uA)<br>VDD = 3.3 V |

|-------------------------------|---------------------------|--------------------------------|--------------------------------|-----------------------------------------|

| 18 MHz                        | 1.372                     | 0.254                          | 3.03                           | 0.39                                    |

| 24 MHz                        | 1.749                     | 0.284                          | 2.95                           | 0.40                                    |

| 30 MHz                        | 2.126                     | 0.306                          | 2.97                           | 0.40                                    |

| 36 MHz                        | 2.404                     | 0.257                          | 2.96                           | 0.40                                    |

| 48 MHz                        | 3.110                     | 0.293                          | 2.99                           | 0.40                                    |

| 60 MHz                        | 3.810                     | 0.306                          | 2.97                           | 0.40                                    |

#### Table 3. Power consumption

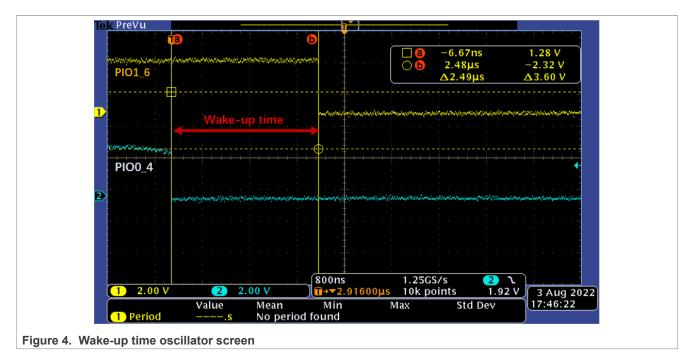

When testing the wake-up time, use the  $PIOO_4$  as the wake-up source for Sleep mode/Deep sleep mode/ Power-down mode and the  $PIOI_6$  to detect whether the chip is woken up. As shown in Figure 4, the wake-up time is from when the  $PIOO_4$  is triggered from high to low level to wake up the chip to when the  $PIOI_6$  is set to low. The channel 1 is  $PIOI_6$  and channel 2 is  $PIOO_4$ .

# AN13818

LPC86x Low-power and Wake-up Optimization

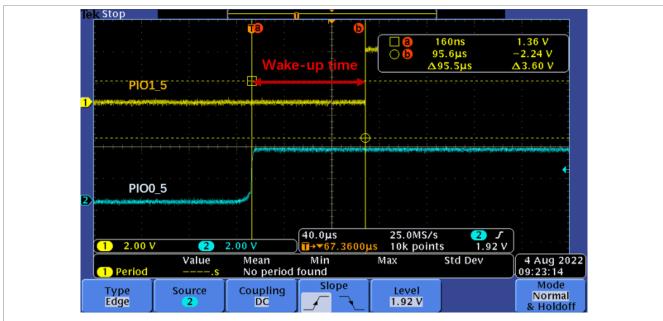

When testing the wakeup time in the Deep power-down mode, use the reset pin PIO0\_5 as the wake up source and the PIO1\_5 to detect whether the chip is woken up in reset handler. As shown in Figure 5, wakeup time in the Deep power-down mode is measured from when the reset pin PIO0\_5 is triggered to from low to high level to wake up the chip, to when the PIO1\_5 is set to high. The channel 1 is PIO1\_5 and channel 2 is PIO0\_5.

Figure 5. Wake-up time oscillator screen

#### Table 4. Wake-up time

| Power mode<br>System clock | Sleep (us)<br>VDD = 3.3 V | Deep-sleep (us)<br>VDD = 3.3 V | Power-down (us)<br>VDD = 3.3 V | Deep Power-<br>down (us)<br>VDD = 3.3 V |

|----------------------------|---------------------------|--------------------------------|--------------------------------|-----------------------------------------|

| 18 MHz                     | 2.49                      | 3.39                           | 49.07                          | 97.3                                    |

AN13818 Application note © 2023 NXP B.V. All rights reserved.

| Power mode<br>System clock | Sleep (us)<br>VDD = 3.3 V | Deep-sleep (us)<br>VDD = 3.3 V | Power-down (us)<br>VDD = 3.3 V | Deep Power-<br>down (us)<br>VDD = 3.3 V |

|----------------------------|---------------------------|--------------------------------|--------------------------------|-----------------------------------------|

| 24 MHz                     | 1.86                      | 2.57                           | 46.4                           | 96.5                                    |

| 30 MHz                     | 1.50                      | 2.05                           | 44.8                           | 96.0                                    |

| 36 MHz                     | 1.27                      | 1.73                           | 46.9                           | 95.5                                    |

| 48 MHz                     | 0.95                      | 1.31                           | 44.8                           | 95.5                                    |

| 60 MHz                     | 0.77                      | 1.06                           | 44.3                           | 95.5                                    |

#### Table 4. Wake-up time...continued

# 6 Revision history

#### Table 5 summarizes the revisions to this document.

#### Table 5. Revision history

| Revision number | Date        | Substantive changes |

|-----------------|-------------|---------------------|

| 0               | 08 May 2023 | Initial release     |

# AN13818

#### LPC86x Low-power and Wake-up Optimization

#### Legal information 7

## 7.1 Definitions

Draft - A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

# 7.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use - NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale - NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

Export control — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products - Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

Translations — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security - Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP B.V. - NXP B.V. is not an operating company and it does not distribute or sell products

# 7.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

# AN13818

# LPC86x Low-power and Wake-up Optimization

# Contents

| 1   | Introduction                            | 2  |

|-----|-----------------------------------------|----|

| 2   | LPC86x overview                         | 2  |

| 3   | Power management                        | 2  |

| 3.1 | Power modes                             |    |

| 3.2 | Wake-up process                         | 4  |

| 4   | Power configurations                    | 5  |

| 4.1 | Active mode                             | 5  |

| 4.2 | Sleep mode                              | 5  |

| 4.3 | Deep sleep mode                         |    |

| 4.4 | Power-down mode                         |    |

| 4.5 | Deep power-down mode                    | 6  |

| 5   | Example to achieve typical data on data |    |

|     | sheet                                   | 6  |

| 5.1 | Hardware environment                    | 6  |

| 5.2 | Hardware setup                          | 6  |

| 5.3 | Software environment setup              | 6  |

| 5.4 | Reference software and hardware         |    |

|     | implementation                          | 7  |

| 5.5 | Running and measure results             |    |

| 6   | Revision history                        | 10 |

| 7   | Legal information                       |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com

Date of release: 8 May 2023 Document identifier: AN13818