### AN14024 LPC86x FlexTimer Module Feature Rev. 1.0 — 29 September 2023

**Application note**

#### **Document information**

| Information | Content                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14024, FlexTimer, LPC86x, PWM, motor control, power energy                                                                                        |

| Abstract    | This document introduces the FlexTimer module feature, which is an enhanced version of CTimer used for motor control and power energy applications. |

### 1 Introduction

The FlexTimer module (FTM) is an enhanced timer module when compared with the Timer/PWM module (TPM). The FTM is commonly used in the Kinetis series MCUs and for motor control, lighting, and power-conversion application. This document introduces the features of the FTM module in LPC86x.

The key features of the FTM module are as follows:

- Each channel can be configured for Input capture, Output compare, or Edge-aligned or Center-aligned PWM mode.

- Each pair of channels can be combined to generate PWM signals with equal outputs, pairs with complementary outputs, or independent outputs.

- The dead time insertion is available for each complementary pair.

- Quadrature decoder with input filters, relative position counting, and interrupt on position count or capture of position count on external event.

- Software control of PWM outputs, fault inputs for global fault control.

The masking, inverting, polarity and fault control, and hardware dead time insertion are the main features of the FTM module dedicated for motor-control applications. They provide greater flexibility and significantly reduce the CPU load. If the FTM module is not used for motor control, it retains standard timer functions such as the Input capture or Output compare modes.

### 2 Acronyms

Table 1 lists the acronyms used in this document.

| Table 1. Acronyms |

|-------------------|

|-------------------|

| Acronym | Meaning            |

|---------|--------------------|

| FTM     | FlexTimer module   |

| EPWM    | Edge-aligned PWM   |

| СРѠМ    | Center-aligned PWM |

| DCAP    | Dual-edge capture  |

| GTB     | Global time base   |

### **3** FlexTimer overview

The LPC86x FTM is a six-to-four-channel timer that supports the following features:

- Input capture

- Output compare

- Generation of PWM signals to control electric motor

- Power management applications

The FTM time reference is a 16-bit counter that can be used as an unsigned or signed counter.

The LPC86x device has two FlexTimers as follows:

- FTM0: FTM0 provides six channels and includes support for motor control including fault control.

- *FTM1*: FTM1 provides four channels. This timer does not include fault control but includes a quadrature decoder.

#### LPC86x FlexTimer Module Feature

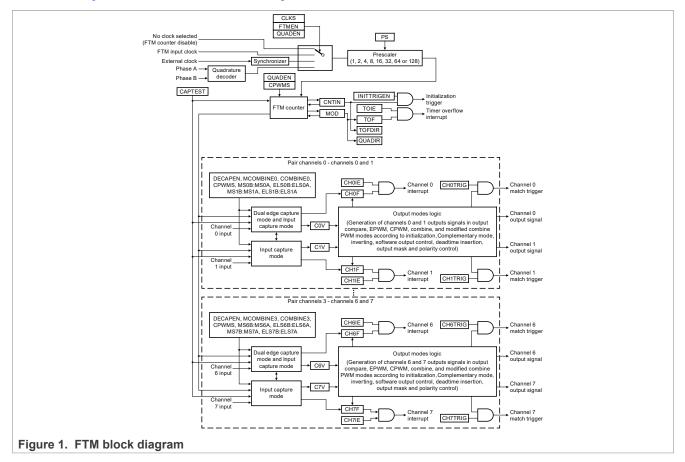

Both the FlexTimers can be clocked up to 60 MHz. When the FlexTimers are operated at a rate higher than the CPU, they must be exactly two times the CPU/AHB frequency. Otherwise, they can use the same clock as the CPU/AHB. Figure 1 shows the FTM block diagram.

Figure 2 shows the FTM module channel modes setting and the capture edge level.

|                      | DECAPEN | COMBINE | CPWMS | MSnB:MSnA | ELSnB:ELSnA | Mode                  | Configuration                                            |

|----------------------|---------|---------|-------|-----------|-------------|-----------------------|----------------------------------------------------------|

|                      | 0       | 0       | 0     | 0         | 1           | Input capture         | Capture on rising edge only                              |

|                      |         |         |       |           | 10          |                       | Capture on falling edge only                             |

|                      |         |         |       |           | 11          |                       | Capture on rising or falling edge                        |

|                      |         |         |       | 1         | 1           | Output                | Toggle output on match                                   |

|                      |         |         |       |           | 10          | compare               | Clear output on match                                    |

|                      |         |         |       |           | 11          |                       | Set output on match                                      |

|                      |         |         |       | 1X        | 10          | Edge-aligned          | High-true pulses                                         |

|                      |         |         |       |           |             | PWM                   | (clear output on match)                                  |

|                      |         |         |       |           | X1          |                       | Low-true pulses                                          |

|                      |         |         |       |           |             |                       | (set output on match)                                    |

|                      |         |         | 1     | XX        | 10          | Center-aligned<br>PWM | High-true pulses                                         |

|                      |         |         |       |           |             |                       | (clear output on match-up)                               |

|                      |         |         |       |           | X1          |                       | Low-true pulses<br>(set output on match-up)              |

|                      |         | 1       | 0     | ХХ        | 10          | Combine               |                                                          |

|                      |         | '       | Ů     | ~~        | 10          | PWM                   | High-true pulses<br>(set on channel (n) match, and clear |

|                      |         |         |       |           |             |                       | on channel (n+1) match)                                  |

|                      |         |         |       |           | X1          |                       | Low-true pulses                                          |

|                      |         |         |       |           |             |                       | (clear on channel (n) match, and set                     |

|                      |         |         |       |           |             |                       | on channel (n+1) match)                                  |

|                      | 1       | 0       | 0     | X0        |             | Dual-edge             | One-shot capture mode                                    |

|                      |         |         |       | X1        |             | capture<br>mode       | Continuous capture mode                                  |

|                      |         |         |       | -         |             |                       |                                                          |

| Figure 2. FTM channe | l mode  | settin  | g     |           |             |                       |                                                          |

143

### **4** FlexTimer features

The FTM features are discussed in detail in further sections.

#### 4.1 Edge-aligned PWM mode

For Edge-aligned PWM (EPWM) mode, the FTM counter counts from the FTM\_CNTIN value to the FTM\_MOD value. All FTM channel signals align at the edge when the FTM counter changes from the MOD value to the CNTIN value.

The Edge-aligned mode is selected when:

- QUADEN = 0

- DECAPEN = 0

- COMBINE = 0

- CPWMS = 0

- MSnB = 1

The edge-aligned PWM period can be determined from Equation 1:

$$[MOD - CNTIN + 0 \times 0001]$$

(1)

The pulse width or the duty cycle can be determined from Equation 2 or Equation 3, depending on the ELSnB:ELSnA bits setting.

$$(CnV - CNTIN)$$

<sup>(2)</sup>

$$(MOD - NTIN - CnV) \tag{3}$$

The Edge-aligned mode PWM code example is as follows:

```

void FTM EdgeAlignedMode Output(void)

(void)CLOCK_EnableClock(kCLOCK Ftm0);

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* Set Modulo in initialization stage (10kHz PWM frequency @60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(6000-1);

/* Set CNTIN in initialization stage */

FTM0->CNTIN = FTM CNTIN INIT(0);

/* Enable high-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSB_MASK;

/* Set channel value in initialization stage */

FTM0->CONTROLS[0].CnV=FTM_CnV_VAL(3000); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(3000); // 50% duty cycle

/* Reset FTM counter */

FTMO -> CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC = FTM SC CLKS(1) | FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK;

}

```

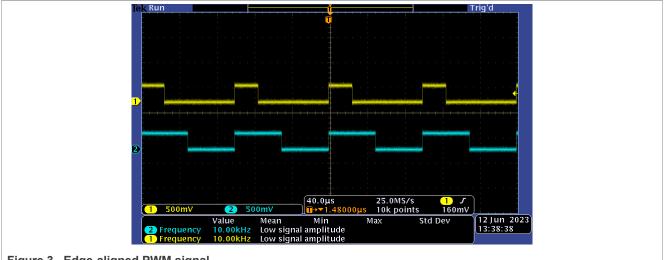

Figure 3 shows that the CH1 and CH2 channel signals on the oscilloscope are the FTM0\_CH0 and FTM0\_CH1 signals. The FTM0\_CH0 and FTM0\_CH1 are aligned in the raising edge.

#### LPC86x FlexTimer Module Feature

Figure 3. Edge-aligned PWM signal

### 4.2 Center-aligned PWM mode

In Center-aligned PWM (CPWM) mode, the FTM counter counts up from FTM CNTIN to FTM MOD and then counts down from FTM MOD to FTM CTNIN. All FTM channel signals align at the point when the FTM counter reaches up to FTM MOD value.

The Center-aligned mode is selected when:

- QUADEN = 0

- DECAPEN = 0

- COMBINE= 0

- CPWMS = 1

The center-aligned PWM period can be determined from Equation 4:

$$2 \times (MOD - CNTIN + 0 \times 0001) \tag{4}$$

The pulse width or the duty cycle can be determined from Equation 5 or Equation 6, depending on the ELSnB:ELSnA bits setting.

$$2 \times (CnV - CNTIN) \tag{5}$$

$$2 \times (MOD - CNTIN - CnV) \tag{6}$$

The Center-aligned mode PWM code example is as follows:

```

void FTM CenterAlignedMode Output(void)

(void)CLOCK EnableClock(kCLOCK_Ftm0);

FTMO ->SC = \overline{F}TM SC CPWMS MASK;

/* Enable registers updating from write buffers */

FTM0->MODE = FTM MODE FTMEN MASK | FTM MODE WPDIS MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM MOD MOD(3000-1);

/* Set CNTIN in initialization stage */

FTMO->CNTIN = FTM CNTIN INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

/* Set Channel Value */

FTMO->CONTROLS[0].CnV=FTM_CnV_VAL(1500); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(750); // 25% duty cycle

AN14024

All information provided in this document is subject to legal disclaimers

© 2023 NXP B.V. All rights reserved

```

LPC86x FlexTimer Module Feature

```

/* FTM counter reset */

FTMO -> CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM SC CLKS(1) | FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK;

}

```

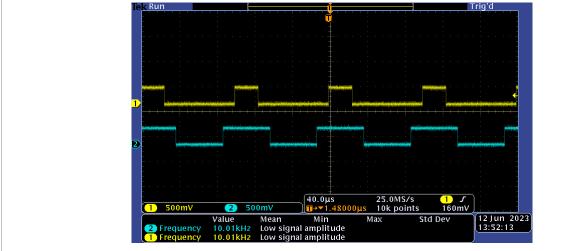

Figure 4 shows that the CH1 and CH2 channel signals on the oscilloscope are the FTM0 CH0 and FTM0 CH1 signals. The FTM0 CH0 and FTM0 CH1 are aligned in the center.

Figure 4. Center-aligned PWM signal

#### 4.3 Complementary mode and dead time insertion

The FTM module supports the Complementary mode. If the COMP bit enables the Complementary mode in the FTM COMBINE register, the even FTM channel generates the output signal. The complementary logic generates the odd output signal as a complement to the even FTM channel. The complementary signal generation can be set individually for each pair of the FTM outputs.

To avoid short-circuit, the dead time must be inserted into the complementary signals. The dead time insertion is provided by the dead time logic, following the complementary logic. The DTEN bit enables this feature in the FTM COMBINE register. The dead time logic delays every rising edge by a time set in the FTM DEADTIME register.

The dead time consists of two parts as follows:

- The first two most significant bits DTPS[1:0] define the pre-scaler of the system clock.

- The bits DTVAL[5:0] define the dead time value using the pre-scaled clock.

The Complementary mode and dead time insertion are applied to both the Edge-aligned PWM and Centeraligned PWM modes, described in Section 4.1 and Section 4.2.

The Complementary mode and dead time insertion PWM code example is as follows:

| <pre>void FTM_CompMode_Output(void) {   (void)CLOCK_EnableClock(kCLOCK_Ft: FTM0-&gt;SC = FTM_SC_CPWMS_MASK;   /* Enable combine, complementary: FTM0-&gt;COMBINE = FTM_COMBINE_COMPO     FTM_COMBINE_COMP1_MASK   FTM_CO   /* Enable registers updating from FTM0-&gt;MODE = FTM_MODE_FTMEN_MASK   /* Select up-down counter for Cen   /* Set Modulo (10kHz PWM frequenc FTM0-&gt;MOD = FTM_MOD_MOD(6000-1); </pre> | <pre>mode and dead-time for channel pair CH0/CH1*/ _MASK   FTM COMBINE_DTEN0_MASK MBINE_DTEN1_MASK; write buffers */   FTM_MODE_WPDIS_MASK; ter-Align PWM */</pre> |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| AN14024                                                                                                                                                                                                                                                                                                                                                                                                             | All information provided in this document is subject to legal disclaimers.                                                                                         | © 2023 NXP B.V. All rights reserved. |

#### LPC86x FlexTimer Module Feature

```

/* Set CNTIN */

FTM0->CNTIN = FTM_CNTIN_INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[2].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[3].CnSC = FTM_CnSC_ELSB_MASK;

/* Set Channel Value */

FTM0->CONTROLS[0].CnV=FTM_CnV_VAL(3000); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(3000); // 50% duty cycle

FTM0->CONTROLS[2].CnV=FTM_CnV_VAL(1500); // 25% duty cycle

FTM0->CONTROLS[3].CnV=FTM_CnV_VAL(1500); // 25% duty cycle

FTM0->CONTROLS[3].CnV=FTM_CnV_VAL(1500); // 25% duty cycle

FTM0->CONTROLS[3].CnV=FTM_CnV_VAL(10) | FTM_DEADTIME_DTPS(1);

/* FTM counter reset */

FTM0->CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM_SC_CLKS(1) | FTM_SC_PWMEN0_MASK | FTM_SC_PWMEN1_MASK

}

```

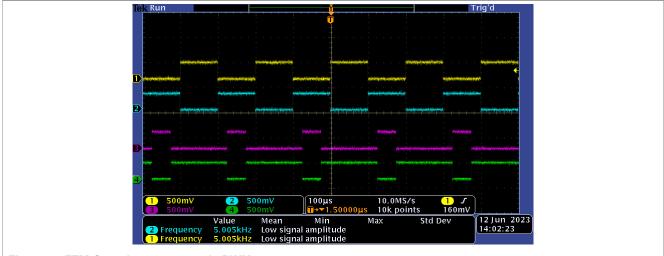

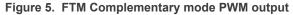

Figure 5 shows the following parameters:

- CH1 and CH2 in the oscilloscope are FTM0\_CH0 and FTM0\_CH1.

- CH3 and CH4 are FTM0 CH2 and FTM0 CH3.

- The FTM0\_CH0 and FTM0\_CH1 and FTM0\_CH2 and FTM\_CH3 are all in Complementary mode.

- The FTM0\_CH0 and FTM0\_CH1 PWM duty cycles are 50 %.

- The FTM0\_CH2 and FTM0\_CH3 PWM duty cycles are 25 %.

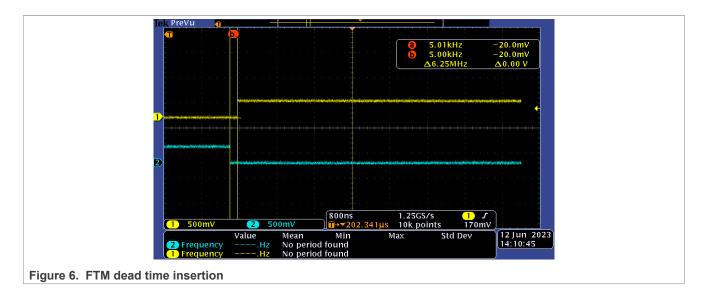

<u>Figure 6</u> shows the dead time value between FTM0\_CH0 and FTM0\_CH1. The oscilloscope can get the dead time value of 0.16 µs. This value is equal to the value, which has been set in the code example.

LPC86x FlexTimer Module Feature

#### 4.4 Combine mode

The Combine mode provides a higher flexibility because the PWM channel (n) output is generated by combining the even channel (n) and the adjacent odd channel (n+1). This implies that the even and odd channels must work in the Complementary mode.

The Combine mode enables generating the EPWM and CPWM using only the up counter, the asymmetrical PWM, or the phase-shifted PWM. The phase-shifted PWM generation is commonly used in phase-shifted fullbridge converters and motor-control applications. Here, the 3-phase stator currents are reconstructed from the current sensed by a single shunt resistor placed in the DC-link and the actual combination of the power supply inverter switches.

The Combine mode is selected when:

- QUADEN = 0

- DECAPEN = 0

- MCOMBINE = 0

- COMBINE = 1

- CPWMS = 0

To generate a phase-shifted PWM with high-true pulses, set the control bits as ELSnB:ELSnA = 1:0. This code example shows the configuration of the FTM0 module used for the phase-shifted PWM generation.

Complementary mode and phase shift PWM code example is as follows:

```

void FTM CombineMode Output(void)

(void)CLOCK EnableClock(kCLOCK Ftm0);

Enable registers updating from write buffers */

FTM0->MODE = FTM MODE FTMEN MASK | FTM MODE WPDIS MASK;

/* Enable combine, complementary mode and dead-time for channel pair CH0/CH1*/

FTM0->COMBINE = FTM_COMBINE_COMBINE0_MASK | FTM_COMBINE_DTEN0_MASK

| FTM_COMBINE_COMBINE1_MASK | FTM_COMBINE_DTEN1_MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTMO ->MOD = FTM MOD MOD(6000-1);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[2].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[3].CnSC = FTM_CnSC_ELSB_MASK;

/* Set Channel Value */ ______

FTM0->CONTROLS[0].CnV=FTM_CnV_VAL(1000); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(4000); // 50% duty cycle

© 2023 NXP B.V. All rights reserved.

AN14024

All information provided in this document is subject to legal disclaimers.

```

#### LPC86x FlexTimer Module Feature

```

FTM0->CONTROLS[2].CnV=FTM_CnV_VAL(2500); // 50% duty cycle

FTM0->CONTROLS[3].CnV=FTM_CnV_VAL(5500); // 50% duty cycle

/* FTM counter reset */

FTM0->CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM_SC_CLKS(1) | FTM_SC_PWMEN0_MASK | FTM_SC_PWMEN1_MASK

| FTM_SC_PWMEN2_MASK | FTM_SC_PWMEN3_MASK;;

}

```

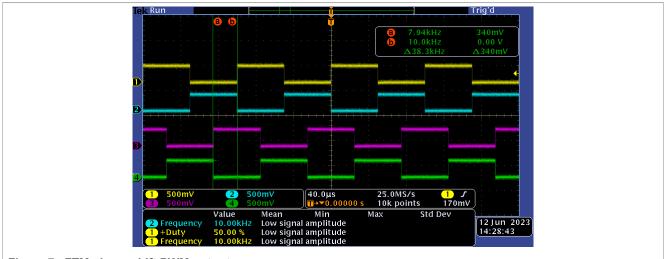

#### Figure 7 shows the following parameters:

- The scope channels CH1, CH2, CH3, and CH4 represent the FTM0 module channels FTM0\_CH0, FTM0\_CH1, FTM0\_CH2, and FTM0\_CH3, respectively.

- The first channel pair (FTM0\_CH0/FTM0\_CH1) and the second channel pair (FTM0\_CH2/FTM0\_CH3) both work in the Complementary mode with a 50 % duty cycle.

- The second channel pair (FTM0\_CH2/FTM0\_CH3) is phase-shifted by 90 degrees to the first channel pair (FTM0\_CH0/FTM0\_CH1).

Figure 7. FTM phase-shift PWM output

### 4.5 Single-edge capture mode

The FTM capture mode has the following uses:

- The FTM capture mode determines the pulse width or the period of the tested signal.

- The FTM capture mode detects the rising/falling edge of an external signal and generates an interrupt to notify that an external event has appeared.

- The FTM capture mode is used in BLDC motor-control applications. The hall sensors in these applications are used to detect the position of the rotor and compute the rotor speed, so that the speed loop can be established. The hall sensors are connected to the channels of the independent FTM (FTM\_CHx). The FTM can then detect both the falling and rising edges of the hall sensor signals and generates a capture interrupt. In the capture-interrupt routine, the duty cycles of the PWM signals are then modified according to the hall sensor logic.

The Single-edge capture mode is selected when:

- DECAPEN = 0

- MCOMBINE = 0

- COMBINE = 0

- CPWMS = 0

- MSnB:MSnA = 0:0

ELSnB:ELSnA ≠ 0:0

To measure either the pulse width or the period of the tested signal, perform the following steps:

- 1. Select the input channel of the FTM module  $FTM_CHx$  and the edge-sensitive input by the control bits ELSnB:ELSnA.

- When the selected edge occurs on the channel input, the current value of the FTM counter is captured in the CnV register. It also generates a channel interrupt (if CH(n)IE = 1).

- 3. In the interrupt routine, save the value of the CnV register into a variable.

- 4. Create a difference between the current value and the saved value from the previous interrupt routine:

- If the selected capture mode is sensitive either on the rising edge (ELSnB:ELSnA= 0:1) or the falling edge (ELSnB:ELSnA= 1:0), the difference is equal to the signal period.

- If the selected capture mode is sensitive on both edges (ELSnB:ELSnA = 1:1), the difference is equal to the pulse width of the tested signal.

The Single-edge capture mode code example is as follows:

```

void FTM_SingleEdgeInputCaptureMode(void)

{

(void)CLOCK_EnableClock(kCLOCK_Ftm0);

EnableIRQ(FTM0_IRQn);

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* Input capture mode sensitive on rising edge to measure period of tested signal */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSA_MASK | FTM_CnSC_CHIE_MASK;

/* Reset counter */

FTM0->CNT = 0;

/* Select clock */

FTM0->SC = FTM_SC_CLKS(1);

}

```

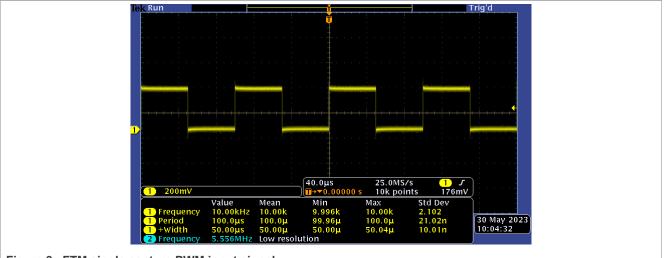

Figure 8 shows the PWM signal attached to the FTM0 used for single edge capture. The PWM signal frequency is 10 kHz.

#### LPC86x FlexTimer Module Feature

Figure 8. FTM single capture PWM input signal

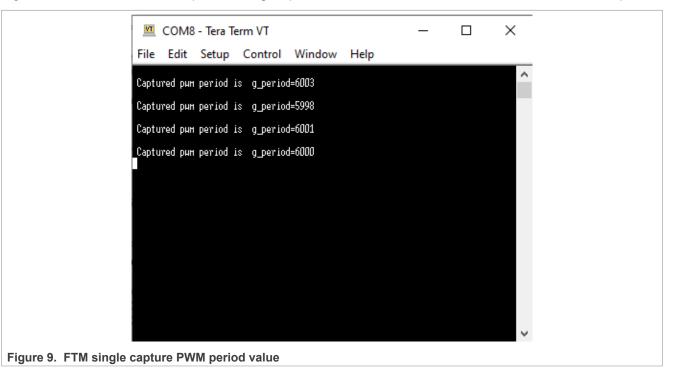

Figure 9 shows the calculated input PWM signal period MOD value. This value also determines its PWM period.

### 4.6 Dual-edge capture mode

The Dual-edge capture mode uses two FTM channels that enable measuring the positive-polarity or negativepolarity pulse width of the signals. In this mode, input the signals through the even FTM channels and ignore the odd channels.

The Dual-edge capture mode is selected when DECAPEN = 1. The Dual-edge capture mode of the FTM can work either in the One-shot capture mode or the Continuous capture mode. The One-shot capture mode is selected when MS(n)A = 0. If the DECAP bit is enabled, the edges are captured. For every new measurement, clear the CH(n)F and CH(n+1)F and set the DECAP bit again. The Continuous capture mode is selected

#### LPC86x FlexTimer Module Feature

when MS(n)A = 1. In this mode, if the DECAP bit is set, the edges are captured continuously. For each new measurement, it is necessary to clear the CH(n)F and CH(n+1)F bits.

To measure the positive-polarity pulse width of the tested signal (either in the One-shot mode or in the Continuous mode), configure the channels as follows:

- To capture the rising edge (ELS(n)B:ELS(n)A = 1:0), configure channel (n).

- To capture the falling edge (ELS(n+1)B:ELS(n+1)A = 0:1), configure channel (n+1).

When a second falling edge of the tested signal is detected, set CH(n+1)F, clear the DECAP bit, and if CH(n+1)IE=1, generate an interrupt. In the interrupt routine, subtract the values saved in the C(n+1)V and C(n)V registers. The subtraction determines the positive-polarity pulse width of the tested signal and clears the CH(n+1)F bit.

If the application requires to measure the negative-polarity pulse width of the tested signal, configure the channels as follows:

- To capture the falling edge (ELS(n)B:ELS(n)A = 0:1), configure channel (n).

- To capture the rising edge (ELS(n+1)B:ELS(n+1)A = 1:0), configure channel (n+1).

To determine the period of the tested signal, channel (n) and channel (n+1) must be sensitive on the same edges.

Dual-edge capture mode code example is as follows:

```

void FTM0 IRQHandler(void)

if ((FTM GetStatusFlags(FTM0) & kFTM TimeOverflowFlag) == kFTM TimeOverflowFlag)

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_TimeOverflowFlag);

g timerOverflowInterruptCount++;

else if (((FTM GetStatusFlags(FTM0) & kFTM Chnl0Flag) == kFTM Chnl0Flag) &&

(ftmFirstChannelInterruptFlag == false))

{

/* Disable first channel interrupt.*/

FTM_DisableInterrupts(FTM0, kFTM_Chnl0InterruptEnable);

g_firstChannelOverflowCount = g_timerOverflowInterruptCount;

ftmFirstChannelInterruptFlag = true;

else if ((FTM GetStatusFlags(FTM0) & kFTM Chnl1Flag) == kFTM Chnl1Flag)

/* Clear second channel interrupt flag.*/

FTM ClearStatusFlags(FTM0, kFTM_ChnllFlag);

/* Disable second channel interrupt.*/

FTM_DisableInterrupts(FTM0, kFTM_ChnllInterruptEnable);

g_secondChannelOverflowCount = g_timerOverflowInterruptCount;

ftmSecondChannelInterruptFlag = true;

else

{ }

```

void FTM\_DualEdgeInputCaptureMode(void)

{

(void)CLOCK\_EnableClock(kCLOCK\_Ftm0);

EnableIRQ(FTM0\_IRQn);

/\* Enable registers updating from write buffers \*/

FTM0->MODE = FTM\_MODE\_FTMEN\_MASK | FTM\_MODE\_WPDIS\_MASK;

/\* Enable dual-edge capture mode \*/

FTM0->COMBINE = FTM\_COMBINE\_DECAPEN0\_MASK | FTM\_COMBINE\_DECAP0\_MASK

| FTM\_COMBINE\_DECAPEN1\_MASK | FTM\_COMEINE\_DECAP1\_MASK;

/\* Select positive polarity pulse width measurement and enable continuous mode for FTM0\_CH0/CH2 \*/

FTM0->CONTROLS[0].CnSC = FTM\_CnSC\_MSA\_MASK | FTM\_CnSC\_ELSA\_MASK;

FTM0->CONTROLS[1].CnSC = FTM\_CnSC\_ELSE\_MASK | FTM\_CnSC\_ELSA\_MASK;

FTM0->CONTROLS[2].CnSC = FTM\_CnSC\_MSA\_MASK | FTM\_CnSC\_ELSA\_MASK;

FTM0->CONTROLS[3].CnSC = FTM\_CnSC\_ELSE\_MASK | FTM\_CnSC\_CHIE\_MASK;

Application note

AN14024

© 2023 NXP B.V. All rights reserved.

#### **NXP Semiconductors**

LPC86x FlexTimer Module Feature

```

/* Reset counter */

FTM0->CNT = 0;

/* Select clock */

FTM0->SC = FTM_SC_CLKS(1);

}

```

```

void FTM_PwmPulseWithCaculate(void)

{

capturelVal = FTM_GetInputCaptureValue(DEMO_FTM_BASEADDR,

(ftm_chnl_t)(BOARD_FTM_INPUT_CAPTURE_CHANNEL_PAIR * 2));

capture2Val = FTM_GetInputCaptureValue(DEMO_FTM_BASEADDR, (ftm_chnl_t)

(BOARD_FTM_INPUT_CAPTURE_CHANNEL_PAIR * 2 + 1));

/* FTM clock source is not prescaled and is divided by 1000000 as the output is printed in

microseconds*/

pulseWidth =

(float)(((g_secondChannelOverflowCount - g_firstChannelOverflowCount) * 65536 + capture2Val -

capture1Val) +

1) / ((float)FTM_SOURCE_CLOCK / 100000);

}

}

```

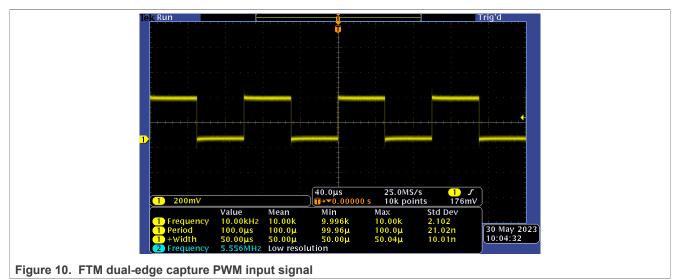

Figure 10 shows the PWM signal attached to the FTM0 used for dual edge capture. The PWM signal frequency is 10 kHz.

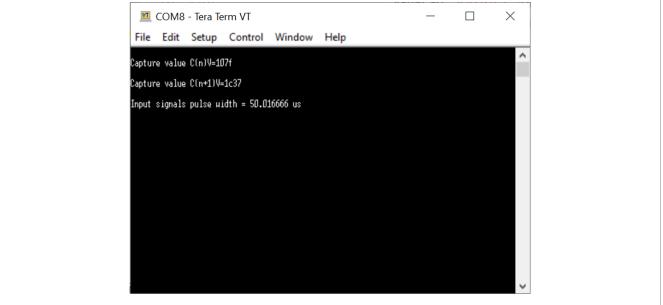

Figure 11 shows the captured input PWM signal C(n)V and C(n+1)V value. This value also determines its PWM period.

LPC86x FlexTimer Module Feature

Figure 11. FTM dual-edge capture PWM value

### 4.7 Quadrature decoder mode

For the motor control use case, the encoder sensor is used to detect the motor position. The Quadrature decoder mode of the FTM module can be used to decode the signals and get the position information of the motor. There are three output signals. The phase A and phase B signals consist of a series of pulses, which are phase-shifted by 90 degrees. The third signal provides the absolute position information. In the motion control, it is used to check the pulse-counting consistency. After each revolution, the value of the counted pulses is captured and compared to the defined value. If a difference is detected, the control algorithm must perform the position-offset compensation.

The LPC86x FTM module only provides the Quadrature encoder mode in the FTM1 module. The Quadrature decoder mode is enabled if QUADEN = 1. The Quadrature decoder mode uses the input signals phase A and phase B to control the FTM counter increment and decrement.

Two sub-modes can be used in the Quadrature encoder mode, which are as follows:

- Count and direction encoding mode

- Phase A and phase B encoding mode

The Count and direction encoding mode is enabled when QUADMODE = 1. In this mode, the phase A and phase B inputs imply the counting rate and the counting direction.

To process the phase A and phase B signals from the encoder sensor, enable the Phase A and phase B encoding mode (QUADMODE = 0).

- In this mode, the phase A and phase B signals indicate the counting direction and the counting rate.

- If the phase B signal lags the phase A signal, the FTM counter increments after every detected rising/falling edge of both signals.

- If the phase B signal leads the phase A signal, the FTM counter decrements after every detected rising/falling edge of both signals. The QUADIR bit in the FTM QDCTRL register indicates the counting direction.

The Quadrature decoder mode code example is as follows:

void FTM\_QuadratureDecoderMode(void)

```

(void)CLOCK_EnableClock(kCLOCK_Ftm1);

```

| <pre>EnableIRQ(FTM1_IRQn); /* Enable registers updating from write buffers */ FTM1-&gt;MODE = FTM_MODE_FTMEN_MASK   FTM_MODE_WPDIS_MASK; /* Encoder simulation with totally 10 rising/falling edges</pre> | */ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| FTM1->MOD = FTM MOD MOD(10);                                                                                                                                                                              |    |

| <pre>FTM1 &gt; MOD</pre>                                                                                                                                                                                  |    |

|                                                                                                                                                                                                           |    |

| FTM1->QDCTRL= FTM_QDCTRL_QUADEN_MASK;                                                                                                                                                                     |    |

| FTM1 -> CNT = 0;                                                                                                                                                                                          |    |

| /* Select clock */                                                                                                                                                                                        |    |

| FTM1->SC = FTM SC CLKS(1)   FTM SC TOIE MASK;                                                                                                                                                             |    |

| }                                                                                                                                                                                                         |    |

|                                                                                                                                                                                                           |    |

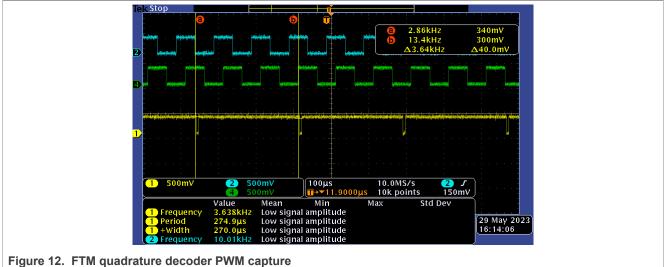

Figure 12 shows the following parameters:

- CH2 and CH4 in the scope represent the encoded phase A and phase B PWM signals attached to the FTM1 QD PHA and FTM1 QD PHB.

- CH1 in the scope represents the FTM1 counter overflow interrupt generated every time the FTM counter reaches the value of the MOD register.

### 4.8 Updating the FTM registers

This section describes the flow on how to update the FTM register using the reload points, software, and hardware.

#### 4.8.1 Update FTM registers by reload points (half cycle reload points)

The following sections describe how to update the FTM registers using the reload points.

#### 4.8.1.1 Edge-aligned PWM register update

To change the PWM duty cycle or time period while the FTM counter is running, the half and full cycle reload strategies can be applied. This feature enables updating the FTM registers with the content of their buffers, depending on the chosen reload opportunity, by setting the LDOK bit in the FTM PWMLOAD register. When a reload opportunity occurs, the RF bit in the FTM SC register is set and the reload-opportunity interrupt is generated if RIE = 1. In the interrupt routine, the FTM registers can be changed and updated simultaneously.

If the Up-counting mode is selected to generate the edge-align PWM, the half and full cycle reload opportunities can update the FTM registers according to the following steps:

LPC86x FlexTimer Module Feature

- 1. To generate the edge-align PWM and enable the FTMEN bit in the FTM\_MODE register and the RIE bit in the FTM\_SC register, initialize FTM0.

- 2. Enable the HCSEL bit in the FTM PWMLOAD register.

- 3. For the half-cycle reload opportunity, adjust the value in the FTM HCR register to MOD/2

- 4. For the full-cycle reload opportunity, HCSEL = 0.

- 5. In the interrupt routine, change the value of the FTM registers to update the values from their buffers and clear the RF bit in the FTM SC register.

Edge-aligned PWM register update code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

if(g_flag)

{

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(3000-1);

}

else

{

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(6000-1);

}

g_flag = ! g_flag;

GFL0 = frm_MOD_MOD(6000-1);

}

g_flag = ! g_flag;

GFL0 = frm_PWMLOAD_LDOK_MASK;

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

```

```

void FTM EdgeAlignedUpdatePwmMode(void)

(void)CLOCK EnableClock(kCLOCK Ftm0);

EnableIRQ(FTM0 IRQn);

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

* Set Modulo in initialization stage (10kHz PWM frequency @60MHz system clock) */

FTMO ->MOD = FTM_MOD_MOD(6000-1);

/* Set CNTIN in initialization stage */

FTM0->CNTIN = FTM CNTIN INIT(0);

/* Enable high-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_MSB_MASK | FTM_CnSC_ELSB_MASK;

/* Enable high-true pulses of PWM signals */

FTM0->CONTROLS[1].CnSC = FTM CnSC MSB MASK | FTM CnSC ELSB MASK;

/* Set channel value in initialization stage *

FTM0->CONTROLS[0].CnV=FTM CnV VAL(1500); // 50% duty cycle

/* Set channel value in initialization stage */

FTM0->CONTROLS[1].CnV=FTM CnV VAL(1500); // 50% duty cycle

/*enable HalfCycle reload*/

FTM0->PWMLOAD = FTM_PWMLOAD_HCSEL_MASK;

/*Set the halfcycle value*,

FTM0->HCR = FTM HCR HCVAL(3000);

/* Reset FTM counter */

FTMO -> CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC = FTM SC CLKS(1) | FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK | FTM SC RIE MASK;

```

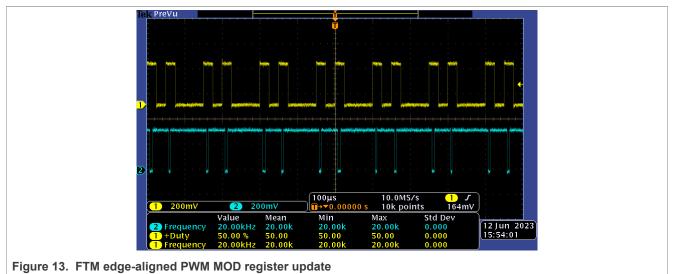

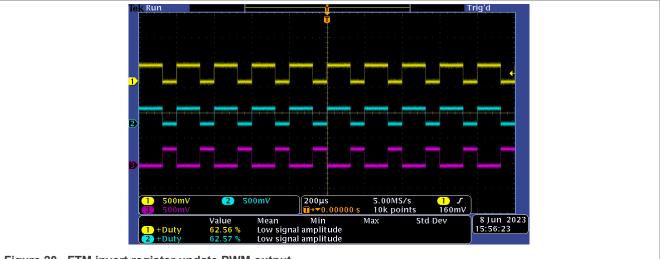

Figure 13 shows the Edge-aligned PWM mode update MOD register with the following parameters:

- The CH1 in the scope represents the FTM0 CH0.

- The FTM0\_CH0 updates the MOD value each half PWM cycle.

- The CH2 in scope represents the FTM0 reload interrupt when the FTM counter C(n)V reaches MOD/2.

LPC86x FlexTimer Module Feature

#### 4.8.1.2 Center-aligned PWM register update

A different scenario must be considered when the Up/Down-counting mode is selected to generate the centeraligned PWM as described in the following steps:

- 1. To generate the center-aligned PWM, initialize FTM0.

- 2. Enable the FTMEN bit in the FTM MODE register and the RIE bit in the FTM SC register.

- 3. Enable the CNTMIN and CNTMAX bits in the FTM SYNC register for the half-cycle reload opportunity.

- 4. Enable the CNTMIN = CNTMAX = 0 for the full-cycle reload opportunity.

- 5. In the interrupt routine, change the value of the FTM registers to update the values from their buffers and clear the RF bit in the FTM SC register.

Center-aligned PWM register update code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

FTM0->CONTROLS[0].CnV = FTM_CnV_VAL(4500);

FTM0->CONTROLS[1].CnV = FTM_CnV_VAL(4500);

GPI0_PinInit (GPI0, 1, 20, &gpioPinConfig_1);//set P101_20 to Low

FTM0->PWMLOAD = FTM_PWMLOAD_LDOK_MASK;

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

}

```

```

void FTM_CenterAlignedUpdatePwmMode(void)

{

(void)CLOCK_EnableClock(kCLOCK_Ftm0);

EnableIRQ(FTM0_IRQn);

FTM0->SC = FTM_SC_CPWMS_MASK;

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(6000-1);

/* Set CNTIN */

FTM0->CNTIN = FTM_CNTIN_INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[2].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[3].CnSC = FTM_CnSC_ELSB_MASK;

```

AN14024 Application note All information provided in this document is subject to legal disclaimers.

/\* Set Channel Value \*/

FTM0->CONTROLS[0].CnV=FTM\_CnV\_VAL(3000); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM\_CnV\_VAL(1500); // 25% duty cycle

FTM0->CONTROLS[2].CnV=FTM\_CnV\_VAL(3000); // 50% duty cycle

FTM0->CONTROLS[3].CnV=FTM\_CnV\_VAL(1500); // 25% duty cycle

FTM0->SYNC = FTM\_SYNC\_CNTMAX\_MASK | FTM\_SYNC\_CNTMIN\_MASK;

/\* FTM counter reset \*/

FTM0->CNT = 0;

/\* Clock selection and enabling PWM generation \*/

FTM0->SC |= FTM\_SC\_CLKS(1) | FTM\_SC\_PWMEN0\_MASK | FTM\_SC\_PWMEN1\_MASK

| FTM\_SC\_PWMEN2\_MASK | FTM\_SC\_PWMEN3\_MASK | FTM\_SC\_RIE\_MASK;

}

<u>Figure 14</u> shows the Center-aligned PWM mode update for the C(n)V and C(n+1)V register with the following parameters:

- The CH2 in the scope represents the FTM0 CH0.

- The FTM0 CH0 updates the C(n)V value after the half PWM cycle.

- The CH4 in the scope represents the FTM0\_CH3, which does not update the C(n)V value used to compare with the FTM0\_CH0.

- The CH1 in scope represents the FTM0 reload interrupt when the FTM counter C(n)V reaches MOD/2.

Figure 14. FTM center-aligned PWM CnV register update

#### 4.8.2 Update FTM registers by software

The following sections describe how to update the FTM registers using the software.

#### 4.8.2.1 Update MOD register value

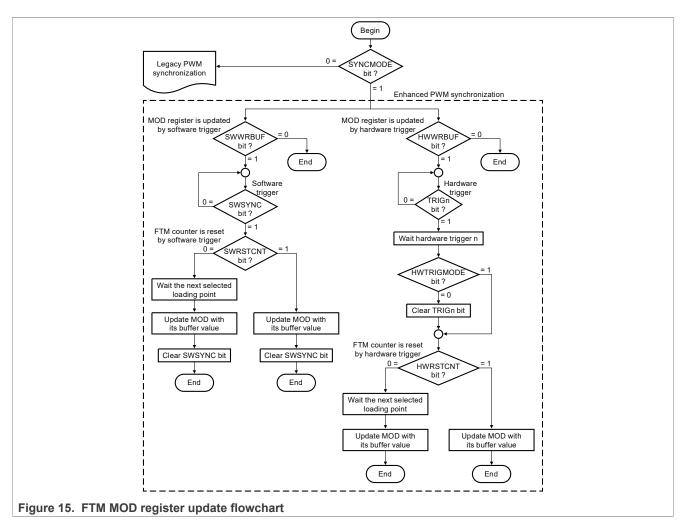

The MOD register synchronization updates the MOD register with its buffer value. This synchronization is enabled if FTMEN = 1.

The MOD register synchronization is done either by the enhanced PWM synchronization (SYNCMODE = 1) or the legacy PWM synchronization (SYNCMODE = 0). However, it is expected that the MOD register is synchronized only by the enhanced PWM synchronization.

In the case of enhanced PWM synchronization, the MOD register synchronization depends on SWWRBUF, SWRSTCNT, HWWRBUF, and HWRSTCNT bits.

Figure 15 shows the MOD register update flowchart.

### **NXP Semiconductors**

### AN14024

#### LPC86x FlexTimer Module Feature

The software MOD register updated code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

if(FTM0->MOD != FTM_MOD_MOD(3000-1))

{

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(3000-1);

GPI0_PinInit (GPI0, 1, 20, &gpioPinConfig);//set P101_20 to Low

/* enable software sync */

FTM0->SYNC = FTM_SYNC_SWSYNC_MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(6000-1);

}

else

{

GPI0_PinInit (GPI0, 1, 20, &gpioPinConfig);//set P101_20 to Low

FTM0->SYNC = FTM_SYNC_SWSYNC_MASK;

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

```

void FTM\_CenterAlignedSwTiggerMODSYNC(void)

© 2023 NXP B.V. All rights reserved.

```

(void)CLOCK EnableClock(kCLOCK Ftm0);

EnableIRQ(FTM0_IRQn);

FTM0->SC = FTM SC CPWMS MASK;

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK| FTM_MODE_WPDIS_MASK;

/* Set Modulo (5kHz PWM frequency at 60MHz system clock) */

FTMO -> MOD = FTM MOD MOD(6000-1);

/* Set CNTIN */

FTM0->CNTIN = FTM CNTIN INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM CnSC ELSB MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

/* Set Channel Value */

FTMO->CONTROLS[0].CnV=FTM_CnV_VAL(1500); // 50% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(1500); // 50% duty cycle

FTM0->CONF = FTM CONF LDFQ(3);

FTM0->SYNCONF = FTM_SYNCONF_SYNCMODE_MASK | FTM_SYNCONF_SWWRBUF_MASK | FTM_SYNCONF_SWRSTCNT_MASK;

FTM0->SYNC = FTM_SYNC_CNTMAX_MASK | FTM_SYNC_CNTMIN_MASK;

/* FTM counter reset */

FTMO -> CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM SC CLKS(1) | FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK | FTM SC RIE MASK;

```

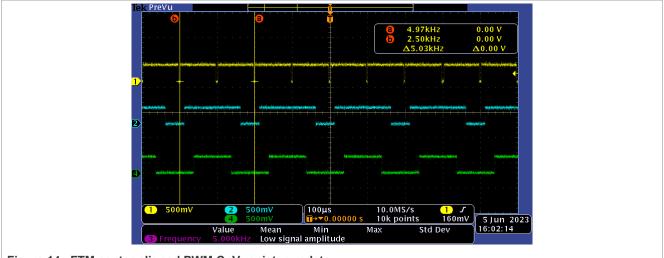

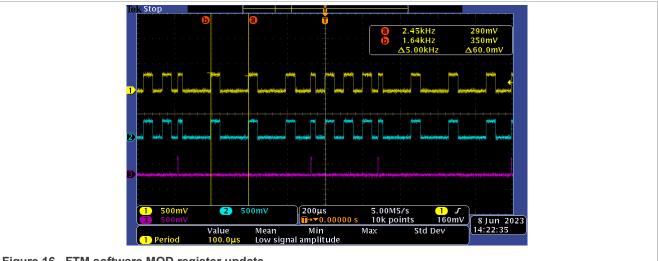

Figure 16 shows the result for the software MOD register update with the following parameters:

- The CH1 and CH2 in the scope represent the FTM0 CH0, FTM0 CH1.

- The CH3 represents the reload point interrupt after every three periods.

- After four periods, the reload point interrupt is generated and the MOD register can be updated in the IRQ.

- The frequency changes between 5 kHz and 10 kHz.

Figure 16. FTM software MOD register update

#### 4.8.2.2 Update output mask register value

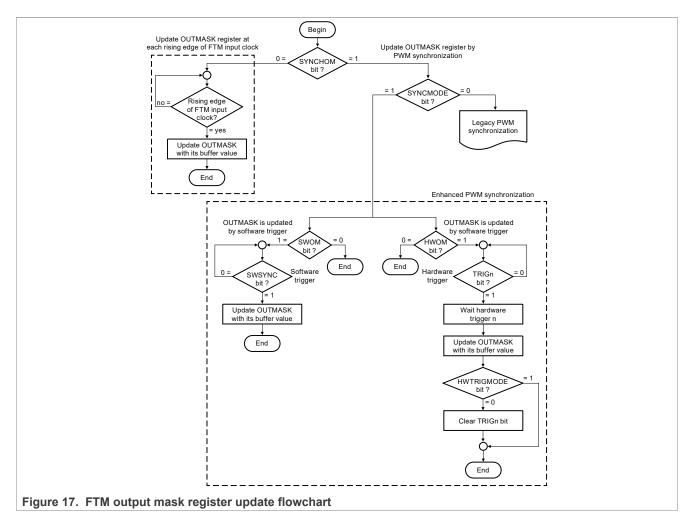

The OUTMASK register synchronization updates the OUTMASK register with its buffer value. The OUTMASK register can be updated at each rising edge of the FTM input clock (SYNCHOM = 0), by one of the following synchronizations:

- The enhanced PWM synchronization, where SYNCHOM = 1 and SYNCMODE = 1.

- The legacy PWM synchronization, where SYNCHOM = 1 and SYNCMODE = 0. However, it is expected that the OUTMASK register is synchronized only by the enhanced PWM synchronization.

Figure 17 shows the output mask register update flowchart.

#### LPC86x FlexTimer Module Feature

The output mask register update code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

if(!(FTM0->OUTMASK & FTM_OUTMASK_CH0OM_MASK))

{

FTM0->OUTMASK = FTM_OUTMASK_CH0OM_MASK;

GPI0_PinInit (GPI0, 1, 20, &gpioPinConfig);//set P101_20 to High

FTM0->SYNC = FTM_SYNC_SWSYNC_MASK;

}

else

{

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->OUTMASK &= ~(FTM_OUTMASK_CH0OM_MASK);

}

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

}

```

```

void FTM_CenterAlignedSwTiggerOMSYNC(void)

{

(void)CLOCK_EnableClock(kCLOCK_Ftm0);

EnableIRQ(FTM0_IRQn);

FTM0->SC = FTM_SC_CPWMS_MASK;

/* Enable registers updating from write buffers */

```

AN14024

© 2023 NXP B.V. All rights reserved.

#### LPC86x FlexTimer Module Feature

```

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->MOD = FTM_MOD_MOD(3000-1);

/* Set CNTIN */

FTM0->CNTIN = FTM_CNTIN_INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

/* Set Channel Value */

FTM0->CONTROLS[0].CnV=FTM_CnV_VAL(2250); // 75% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(2250); // 37.5% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(2250); // 37.5% duty cycle

FTM0->SYNC = FTM_SYNC_SYNCHOM_MASK | FTM_SYNC_CNTMAX_MASK | FTM_SYNC_CNTMIN_MASK;

FTM0->CONF = FTM_CONF_LDFQ(3);

FTM0->SYNCONF = FTM_SYNCONF_SYNCMODE_MASK | FTM_SYNCONF_SWOM_MASK;

/* FTM counter reset */

FTM0->CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM_SC_CLKS(1) | FTM_SC_PWMEN0_MASK | FTM_SC_PWMEN1_MASK |FTM_SC_RIE_MASK;

}

```

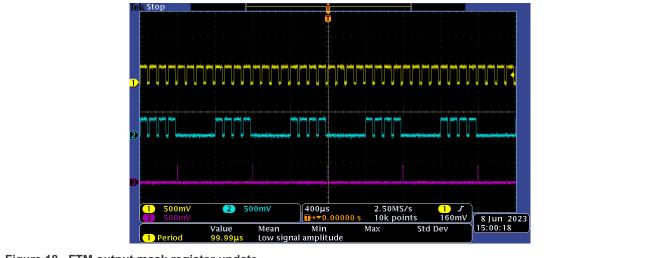

Figure 18 shows the output mask register update for PWM output with the following parameters:

- CH1 and CH2 in the scope represent the FTM0 CH1 and FTM0 CH0.

- CH3 represents the reload point interrupt every four periods.

- As the scope shows, the FTM0\_CH0 output mask register is updated every four periods and FTM0\_CH0 is masked after every four periods.

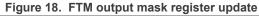

#### 4.8.2.3 Update invert register value

The INVCTRL register synchronization updates the INVCTRL register with its buffer value. The INVCTRL register can be updated at each rising edge of the FTM input clock (INVC = 0). The enhanced PWM synchronization (INVC = 1 and SYNCMODE = 1) can also update the INVCTRL register, as shown in the flowchart in Figure 19.

In the case of enhanced PWM synchronization, the INVCTRL register synchronization depends on SWINVC and HWINVC bits.

Figure 19 shows the invert register update flowchart.

### **NXP Semiconductors**

### AN14024

#### LPC86x FlexTimer Module Feature

The invert register update code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

FTM0->INVCTRL = FTM_INVCTRL_INV0EN_MASK;

FTM0->SYNC = FTM_SYNC_SWSYNC_MASK;

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

```

```

void FTM_CenterAlignedSwTiggerIVSYNC(void)

{

(void)CLOCK_EnableClock(kCLOCK_Ftm0);

EnableIRQ(FTM0_IRQn);

FTM0->SC = FTM_SC_CPWMS_MASK;

/* Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* Set Modulo (10kHz PWM frequency at 60MHz_system clock) */

FTM0->MOD = FTM_MOD_MOD(6000-1);

/* Set CNTIN */

FTM0->CNTIN = FTM_CNTIN_INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK;

FTM0->CONTROLS[1].CnSC = FTM_CNSC_ELSB_MASK;

FTM0->CONTROLS[2].CnSC = FTM_CNSC_ELSB_MASK;

/* Set Channel Value */

```

Application note

AN14024

© 2023 NXP B.V. All rights reserved.

#### LPC86x FlexTimer Module Feature

```

FTM0->CONTROLS[0].CnV=FTM_CnV_VAL(2250); // 37.5% duty cycle

FTM0->CONTROLS[1].CnV=FTM_CnV_VAL(2250); // 37.5% duty cycle

FTM0->CONTROLS[2].CnV=FTM_CnV_VAL(2250); // 37.5% duty cycle

FTM0->SYNC = FTM_SYNC_CNTMAX_MASK | FTM_SYNC_CNTMIN_MASK;

FTM0->INVCTRL &= ~FTM_INVCTRL_INVOEN_MASK;

FTM0->CONF = FTM_CONF_LDFQ(3);

FTM0->CONF = FTM_SYNCONF_SYNCMODE_MASK | FTM_SYNCONF_SWINVC_MASK | FTM_SYNCONF_INVC_MASK;

/* FTM counter reset */

FTM0->CNT = 0;

/* Clock selection and enabling PWM generation */

FTM0->SC |= FTM_SC_CLKS(1) | FTM_SC_PWMEN0_MASK | FTM_SC_PWMEN1_MASK | FTM_SC_PWMEN2_MASK |

FTM_SC_RIE_MASK;

}

```

Figure 20 shows the invert register update PWM output with the following parameters:

- CH1 and CH2 in the scope represent the FTM0\_CH0 and FTM0\_CH1.

- CH3 represents FTM0\_CH2.

- As the scope shows, FTM0 CH3 is the PWM, which has not been inverted.

- The FTM0\_CH0 and FTM0\_CH1 represent the inverted PWM compared with FTM0\_CH3.

Figure 20. FTM invert register update PWM output

#### 4.8.3 Update FTM registers by hardware

The hardware synchronization is another way of updating the FTM registers when the counter is running. For this case, the interrupt routine is not necessary because the FTM registers can be changed at any time during the code execution. Their values are updated when a hardware trigger occurs. This way the CPU load can be reduced significantly.

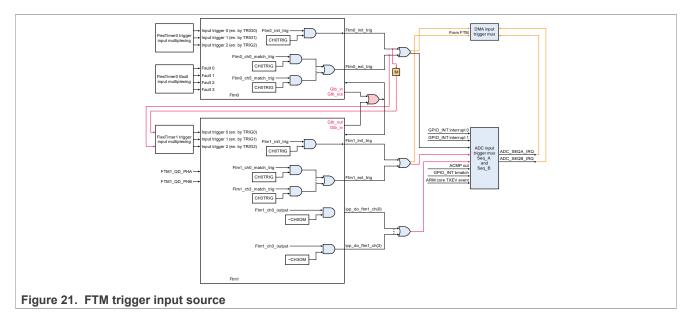

Three hardware trigger signal inputs of the FTM module can be selected depending on the enabled TRIGn bit in the FTM\_SYNC register. The FlexTimer trigger input multiplexing assigns the input trigger "n" to certain signals, as shown in Figure 21.

#### LPC86x FlexTimer Module Feature

Figure 22 shows the selection ID of the FlexTimer0 trigger input source. For more information on the FTM trigger input configuration, refer to the below code example.

| Selection | Input source                   |

|-----------|--------------------------------|

| 0         | FTM1_INIT_TRIG                 |

| 1         | FTM1_EXT_TRIG                  |

| 2         | ADC0_THCMP_IRQ                 |

| 3         | ACMP0_OUT                      |

| 4         | GPIOINT_BMATCH                 |

| 5         | ARM_TXEV                       |

| 6         | MRT_IRQ (global MRT interrupt) |

Figure 22. FTM trigger input source selection

The hardware PWM register updated code example is as follows:

```

void FTM0_IRQHandler(void)

{

if((FTM_GetStatusFlags(FTM0) & kFTM_ReloadFlag) == kFTM_ReloadFlag)

{

if(!(FTM0->OUTMASK & FTM_OUTMASK_CH0OM_MASK))

{

FTM0->OUTMASK = FTM_OUTMASK_CH0OM_MASK;

GPI0_PinInit (GPI0, 1, 20, &gpioPinConfig);//set P101_20 to High

FTM0->SYNC = FTM_SYNC_SWSYNC_MASK;

}

else

{

/* Set Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM0->OUTMASK &= ~(FTM_OUTMASK_CH0OM_MASK);

/* Clear overflow interrupt flag.*/

FTM_ClearStatusFlags(FTM0, kFTM_ReloadFlag);

}

}

```

```

void FTM_CenterAlignedHwTiggerUpdatePwmMode(void)

{

EnableIRQ(FTM0_IRQn);

/* FTM0 configuration*/

FTM0->SC = FTM_SC_CPWMS_MASK;

/* Enable registers updating from write buffers */

```

Application note

AN14024

© 2023 NXP B.V. All rights reserved.

#### LPC86x FlexTimer Module Feature

FTM0->MODE = FTM MODE FTMEN MASK | FTM MODE WPDIS MASK; /\* Set Modulo (10kHz PWM frequency at 60MHz system clock) \*/ FTMO ->MOD = FTM MOD MOD(3000-1);/\* Set CNTIN \*/ FTMO->CNTIN = FTM CNTIN INIT(0); /\* High-true pulses of PWM signals \*/ FTM0->CONTROLS[0].CnSC = FTM\_CnSC\_ELSB\_MASK; FTM0->CONTROLS[1].CnSC = FTM\_CnSC\_ELSB\_MASK; /\* Set Channel Value \*/ FTM0->CONTROLS[0].CnV=FTM\_CnV\_VAL(2250); // 62.5% duty cycle FTM0->CONTROLS[1].CnV=FTM\_CnV\_VAL(2250); // 62.5% duty cycle

/\*Connect FTM1\_INIT\_TRIG to FTM0 trigger0\*/

NDUTMUX >Emotion Trigger0\*/ /restrict in the string set / INPUTMUX->FTMO\_INMUX[0] = 0; /\*Configure the output mask synchronization and trigger input\*/ FTM0->SYNC = FTM\_SYNC\_SYNCHOM\_MASK | FTM\_SYNC\_CNTMAX\_MASK | FTM\_SYNC\_CNTMIN\_MASK | FTM SYNC TRIGO MASK; /\*enable hardware trigger pwm synchronization\*/ FTM0->SYNCONF = FTM\_SYNCONF\_SYNCMODE\_MASK | FTM\_SYNCONF\_HWOM\_MASK | FTM\_SYNCONF\_HWTRIGMODE\_MASK; /\* FTM counter reset \*/ FTMO -> CNT = 0;/\* Clock selection and enabling PWM generation \*/ FTM0->SC |= FTM\_SC\_CLKS(1) | FTM\_SC\_PWMEN0\_MASK | FTM\_SC\_PWMEN1\_MASK | FTM\_SC\_RIE\_MASK; /\* FTM1 configuration\*/ /\* Enable registers updating from write buffers \*/ FTM1->MODE = FTM\_MODE\_FTMEN\_MASK; /\* Set Modulo in initialization stage (10kHz PWM frequency @60MHz system clock) \*/  $FTM1 - MOD = FTM_MOD_MOD(6000 - 1);$ /\* Set CNTIN in initialization stage \*/ FTM1->CNTIN = FTM CNTIN INIT(0); /\* Enable high-true pulses of PWM signals \*/ FTM1->CONTROLS[0].CnSC = FTM CnSC MSB MASK | FTM CnSC ELSB MASK; /\* Set channel value in initialization stage \* FTM1->CONTROLS[0].CnV=FTM\_CnV\_VAL(3000); // 50% duty cycle /\*Enable FTM1 INIT TRIG\*/ FTM1->EXTTRIG = FTM EXTTRIG INITTRIGEN MASK; /\* Reset FTM counter \*/ FTM1 -> CNT = 0;/\* Clock selection and enabling PWM generation \*/ FTM1->SC = FTM SC CLKS(1) | FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK; }

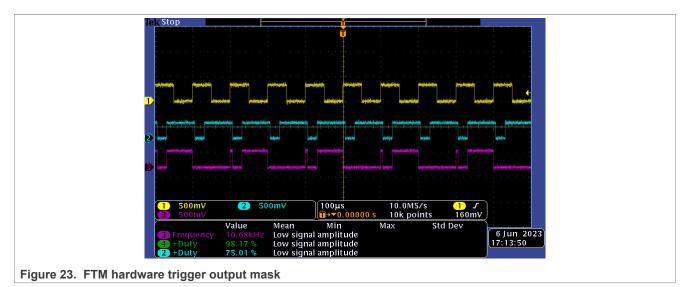

Figure 23 shows the hardware trigger invert register update for PWM output with the following parameters:

- CH1 and CH2 in the scope represent the FTM1 CH0 and FTM0 CH1.

- CH3 represents FTM0\_CH0.

- As the scope shows, FTM1\_CH0 is the hardware trigger signal.

- FTM0 CH1 is the PWM, which has not been masked.

- The FTM0 CH0 represents the masked PWM by hardware trigger compared with FTM0 CH1.

LPC86x FlexTimer Module Feature

### 4.9 Fault control and GTB feature

Fault control is an FTM feature used in motor control application.

#### 4.9.1 Fault control

The fault control of the FTM module plays an important role in motor-control applications. It protects the power devices and the whole electrical drive system in critical moments, when undesirable behaviors such as overtemperature, over-voltage, or over-current occur. In such cases, the fault signal can be generated via a sensor or a special circuit. The fault control is able to stop all PWM channels when a fault signal is detected on the input of the FTM fault pins. An interrupt can be generated after receiving the fault signal and the undesirable behavior can be mitigated.

All FTM interrupt sources (fault interrupt, FTM counter overflow and reload opportunity interrupt, channelcompare event interrupt, and capture interrupt) share the interrupt vector. When a fault signal appears, the outputs of the FTM channels are disabled and kept at a safe logic defined in the FTM POL register.

For example, if POL0 = 1 and a fault is present, FTM CH0 is disabled and forced to a high logic. On the contrary, if POL0 = 0 and a fault is present, FTM CH0 is disabled, but forced to a low logic.

FTM has multiple channels. However, FTM cannot disable the specific channels by the means of specific fault signals. One fault signal is generated as a result of the OR operation of all entering fault signals. Whether the fault signal can disable the FTM channel or not depends on the FAULTENx bit in the FTM COMBINE register. The resulting fault signal can disable all FTM channels or only the even channels (FTM CH0/CH2/CH4/CH6). The selection depends on the FAULTM bit field in the FTM MODE register.

Fault control code example is as follows:

```

void FTM FaultControlCombineMode Output (void)

(void)CLOCK EnableClock(kCLOCK Ftm0);

/* Enable registers updating from write buffers */

FTM0->MODE = FTM MODE FTMEN MASK | FTM MODE WPDIS MASK;

/* Enable combine, complementary mode and dead-time for channel pair CH0/CH1*/

FTM0->COMBINE = FTM COMBINE COMBINE0 MASK | FTM COMBINE COMP0 MASK

| FTM COMBINE DTENO MASK | FTM COMBINE FAULTENO MASK;

FTM0->CONTROLS[0].CnSC = FTM_CnSC_ELSB_MASK; // Select high-true pulses

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK; // Select high-true pulses

/* Set Modulo (20kHz PWM frequency @60MHz system clock)

FTM0->MOD = FTM MOD MOD(3000-1); // Set modulo

FTM0->CONTROLS[0].CnV = FTM CnV VAL(1000); // Set channel Value

AN14024

All information provided in this document is subject to legal disclaimers

```

#### LPC86x FlexTimer Module Feature

```

FTM0->CONTROLS[1].CnV = FTM CnV VAL(2500); // Set channel Value

FTM0->CNT = 0; // Counter reset

FTM0->FLTCTRL = FTM FLTCTRL FAULTOEN MASK;

/* Enable fault control for all channels and select automatic fault clearing mode */

FTMO->MODE |= FTM MODE FAULTM(0x3);

/* Safe value is set as a low after fault input is detected */

FTMO -> POL = 0 \times 0;

/* A 1 at the fault input indicates the fault */

FTM0->FLTPOL &= ~FTM_FLTPOL_FLTOPOL_MASK;

FTM0->SC |= FTM_SC_CLKS(1) | FTM_SC_PWMEN0_MASK | FTM_SC_PWMEN1_MASK; // Select clock and enable PWM

}

```

Figure 24 shows the fault control output with the following parameters:

- · CH1 represents the fault input signal.

- CH2 and CH3 are FTM0 CH0 and FTM0 CH1.

- As the scope shows, when the fault signal is high logic, the FTM0 CH0 and FTM0 CH1 are masked.

Figure 24. FTM fault control output

#### 4.9.2 Global time base

AN14024

**Application note**

The chip supports multiple FTMs and the multiple FTM modules are independent. If the application requires more PWM channels, multiple FTM modules can be used, but they must be synchronized. The synchronization of two (or more) FTM modules means that their counters have the same values at any instant time.

LPC86x provides the global time base (GTB) mechanism to synchronize multiple FTMs. The GTB is a synchronous signal generated by the leader FTM that launches the counter of all FTMs used.

The following two conditions must be met when using the GTB function:

- Each FTM must have the same clock source

- · Each FTM must start at the same time

To enable the GTB feature for each participating FTM module, perform the following steps:

- 1. Stop the FTM counter (write 00b to SC[CLKS]).

- 2. Program the FTM to the intended configuration. The FTM counter mode must be consistent across all participating modules.

- 3. Write 1 to CONF[GTBEEN] and write 0 to CONF[GTBEOUT] at the same time.

- 4. Select the intended FTM counter clock source in SC[CLKS]. The clock source must be consistent across all participating modules.

- 5. Reset the FTM counter (write any value to the CNT register).

LPC86x FlexTimer Module Feature

#### The GTB code example is as follows:

```

void FTM CenterAlignedPwmOutputGlobalBaseMode(void)

(void)CLOCK_EnableClock(kCLOCK_Ftm0);

(void)CLOCK EnableClock(kCLOCK Ftm1);

/* FTM0 Enable registers updating from write buffers */

FTM0->MODE = FTM_MODE_FTMEN_MASK | FTM_MODE_WPDIS_MASK;

/* FTM1 Enable registers updating from write buffers *,

FTM1->MODE = FTM MODE FTMEN MASK | FTM MODE WPDIS MASK;

/* FTM0 configuration*/

FTMO->SC = FTM SC CPWMS MASK;

/* FTM1 configuration*/

FTM1->SC = FTM SC CPWMS MASK;

/* Set FTM0 Modulo (10kHz PWM frequency at 60MHz system clock) */

FTMO - >MOD = FTM MOD MOD(3000-1);

/* Set FTM1 Modulo (10kHz PWM frequency at 60MHz system clock) */

FTM1->MOD = FTM MOD MOD(3000-1);

/* Set FTM0 CNTIN *7

FTMO->CNTIN = FTM CNTIN INIT(0);

/* Set FTM1 CNTIN */

FTM1->CNTIN = FTM CNTIN INIT(0);

/* High-true pulses of PWM signals */

FTM0->CONTROLS[0].CnSC = FTM CnSC ELSB MASK;

FTM0->CONTROLS[1].CnSC = FTM_CnSC_ELSB_MASK;

FTM1->CONTROLS[0].CnSC = FTM CnSC ELSB MASK;

/* Set Channel Value */

FTMO->CONTROLS[0].CnV = FTM_CnV_VAL(1500); // 50% duty cycle

FTM0->CONTROLS[1].CnV = FTM_CnV_VAL(1500); // 50% duty cycle

FTM1->CONTROLS[0].CnV = FTM_CnV_VAL(1500); // 50% duty cycle

/* FTM counter reset */

FTMO -> CNT = 0:

/* FTM counter reset */

FTM1 -> CNT = 0;

/* Enable global time base to control FTMO and FTM1 */

FTM0->CONF = FTM_CONF_GTBEEN_MASK;

FTM1->CONF = FTM_CONF_GTBEEN_MASK;

/* FTM0 Clock selection*/

FTM0->SC |= FTM_SC_CLKS(1);

/* FTM1 Clock selection*

FTM1->SC |= FTM SC CLKS(1);

/* Synchronization signal for FTMO and FTM1 */

FTM0->CONF |= FTM_CONF_GTBEOUT_MASK;

/* FTM0 Clock selection and enabling PWM generation */

FTM0->SC |= FTM SC PWMEN0 MASK | FTM SC PWMEN1 MASK;

/* FTM1 Clock selection and enabling PWM generation */

FTM1->SC |= FTM SC PWMEN0 MASK;

}

```

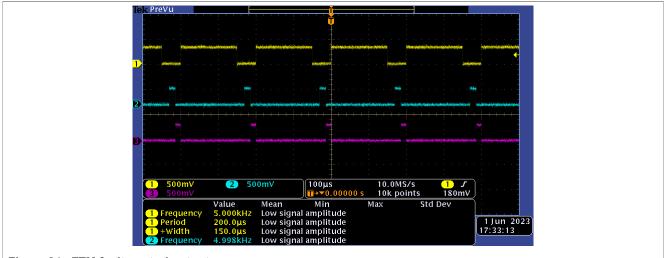

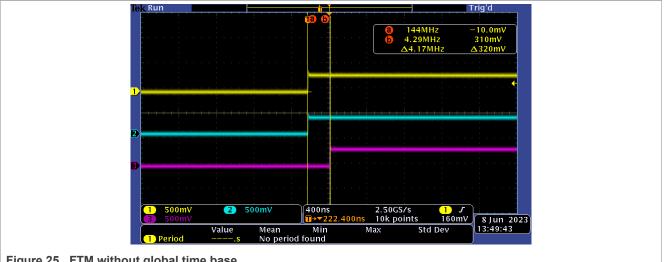

Figure 25 shows the FTM output without global time base with the following parameters:

- CH1 and CH2 in scope represent the FTM0\_CH0 and FTM0\_CH1.

- CH3 represents FTM1\_CH0. When two FTM modules do not enable GTB function, the signals are not synchronized.

#### LPC86x FlexTimer Module Feature

#### Figure 25. FTM without global time base

#### Note about the source code in the document 5

Example code shown in this document has the following copyright and BSD-3-Clause license:

Copyright 2023 NXP Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials must be provided with the distribution.

- Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT HOLDER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE

#### **Revision history** 6

Table 2 summarizes revisions to this document.

Table 2. Revision history

| Revision history | Release date      | Description            |

|------------------|-------------------|------------------------|

| 1                | 29 September 2023 | Initial public release |

#### LPC86x FlexTimer Module Feature

### 7 Legal information

### 7.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

### 7.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Suitability for use in non-automotive qualified products — Unless this document expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <u>PSIRT@nxp.com</u>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

$\ensuremath{\mathsf{NXP}}\xspace \mathsf{B.V.}$  — NXP B.V. is not an operating company and it does not distribute or sell products.

### 7.3 Trademarks

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V. Kinetis — is a trademark of NXP B.V.

#### LPC86x FlexTimer Module Feature

### Contents

| 1       | Introduction                                | 2  |

|---------|---------------------------------------------|----|

| 2       | Acronyms                                    | 2  |

| 3       | FlexTimer overview                          | 2  |

| 4       | FlexTimer features                          | 4  |

| 4.1     | Edge-aligned PWM mode                       | 4  |

| 4.2     | Center-aligned PWM mode                     | 5  |

| 4.3     | Complementary mode and dead time            |    |

|         | insertion                                   | 6  |

| 4.4     | Combine mode                                | 8  |

| 4.5     | Single-edge capture mode                    |    |

| 4.6     | Dual-edge capture mode                      | 11 |

| 4.7     | Quadrature decoder mode                     | 14 |

| 4.8     | Updating the FTM registers                  | 15 |

| 4.8.1   | Update FTM registers by reload points (half |    |

|         | cycle reload points)                        | 15 |

| 4.8.1.1 | Edge-aligned PWM register update            |    |

| 4.8.1.2 | Center-aligned PWM register update          |    |

| 4.8.2   | Update FTM registers by software            | 18 |

| 4.8.2.1 | Update MOD register value                   |    |

| 4.8.2.2 | Update output mask register value           | 20 |

| 4.8.2.3 | Update invert register value                | 22 |

| 4.8.3   | Update FTM registers by hardware            |    |

| 4.9     | Fault control and GTB feature               | 27 |

| 4.9.1   | Fault control                               | 27 |

| 4.9.2   | Global time base                            | 28 |

| 5       | Note about the source code in the           |    |

|         | document                                    | 30 |

| 6       | Revision history                            | 30 |

| 7       | Legal information                           | 31 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© 2023 NXP B.V.

All rights reserved.

For more information, please visit: http://www.nxp.com