AN1726

# Using Motorola's Fast Static RAM CAMs on a Media Independent Interface

Prepared by: Roy Bieda, FAE, Motorola Semiconductors Jim Soroka, FAE, Arrow Electronics

Not too long ago we were happy to have a 10 Mbps LAN connection on our desktop computer. However, given the growing popularity of the Internet and other services, we find ourselves needing more bandwidth. 100 Mbps Ethernet promises to deliver the bandwidth we need without the need to rewire or rewrite our existing protocol stacks.

The transition from 10Base to 100Base Ethernet does present some implementation differences. Given the relatively low data rate of 10Base Ethernet, address filtering in bridge applications was often performed by the host CPU in software. The higher data rate of 100Base Ethernet doesn't allow the host CPU in the bridge enough time to accept or reject frames. There is a need to implement a hardware method to accept or reject frames. This need can be filled by the addition of a Content Addressable Memory to the Ethernet Media Access Controller.

A bridge would simply present to the CAM a 48–bit MAC address obtained from an incoming frame. The CAMs job is to search its contents and indicate to the MAC if the incoming address was present within the CAM.

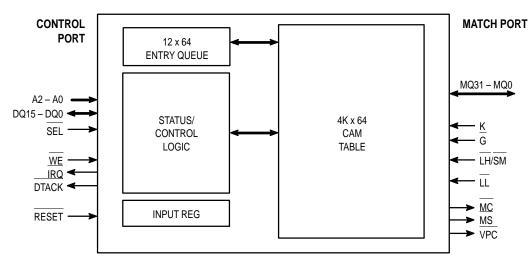

Although CAMs have been available for years, they were often too expensive to justify their use. The MCM69C232 CAM addresses this problem with a different approach to CAM technology. By combining logic with fast and dense SRAM memory cores, Motorola is able to produce cost–effective, fast, and deep CAMs. The MCM69C232 is a 4K x 64 CAM and the MCM69C432 is a 16K x 64 CAM.

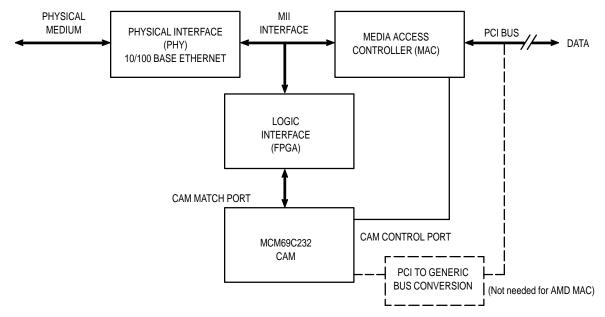

The purpose of this application note is to illustrate the connection of a CAM in a system. The CAM would exist between the Physical Interface Device (the PHY) and the MAC. The AMD79C971 MAC was chosen to illustrate. The MAC has an industry standard interface to the PHY known as a Media Independent Interface. What is needed is a single logic device that can interface the CAM to the MII/PHY connection and signal the MAC to accept or reject an incoming frame. This logic is easily implemented in a FPGA. We will discuss the operation of this FPGA in this application note.

### MEDIA INDEPENDENT INTERFACE DESCRIPTION

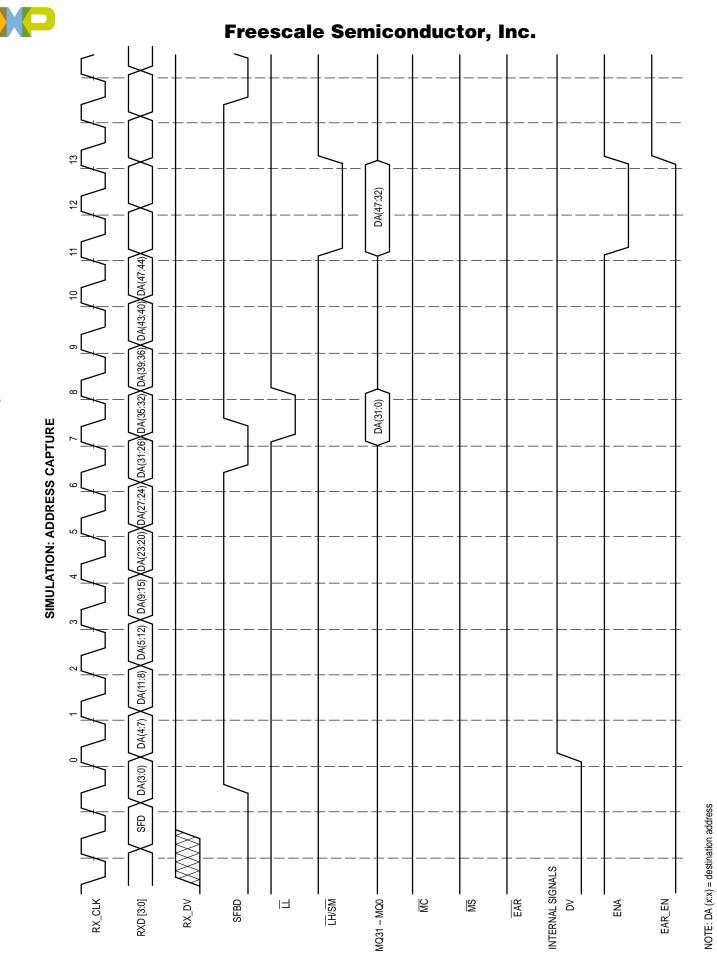

The Media Independent Interface is a standard to facilitate the transfer of data between the MAC and the physical layer interface. The MII interface is a four bit (nibble) wide data path interface that runs at 25 MHz for a 100 Mbps networks and at 2.5 MHz for 10 Mbps networks.

The MII receive clock is generated by the PHY and is sent to the MAC on the RX\_CLK pin. The data from the PHY on RXD[3:0] is presented synchronous to the rising edge of RX\_CLK. The receive process is started when RX\_DV is asserted and remains asserted for the entire receive frame length.

#### RELEVANT SIGNALS

| Pin Name  | Pin<br>Function       | Туре  | No. of<br>Pins | Comments                             |

|-----------|-----------------------|-------|----------------|--------------------------------------|

| RX_CLK    | Receive<br>Clock      | Input | 1              | Recovered receive<br>clock from PHY. |

| RXD [3:0] | Receive<br>Data       | Input | 4              | Received nibbles.                    |

| RX_DV     | Receive<br>Data Valid | Input | 1              | RXD [3:0] has valid data.            |

### **CAM DESCRIPTION**

In its basic operating mode, the MCM69C232 reads a data input word and compares it to all the <u>entr</u>ies in its CAM table. Whether a match is found or not, the MC pin is asserted after <u>the</u> comparisons have been made. If a match is found, the MS pin is asserted, and the data associated with the matching entry is output on the MQ bus. If no match is found, the MQ bus remains in a high impedance state to facilitate depth expansion via the cascading of multiple CAMs.

#### **RELEVANT SIGNALS**

| Pin Name      | Pin<br>Function                     | Туре             | No. of<br>Pins | Comments                                                               |

|---------------|-------------------------------------|------------------|----------------|------------------------------------------------------------------------|

| LH/SM         | Latch<br>High/Start<br>Match        | Input            | 1              | Initiates match<br>sequence on match<br>data present on<br>MQ31 – MQ0. |

| LL            | Latch Low                           | Input            | 1              | Latches low order<br>bits if match width is<br>greater than 32 bits.   |

| MC            | Match<br>Complete                   | Output           | 1              | Open drain, Pullups required.                                          |

| MS            | Match<br>Successful                 | Output           | 1              | Open drain, Pullups required.                                          |

| MQ31 –<br>MQ0 | 32–bit<br>Common<br>I/O CAM<br>Data | Input/<br>Output | 32             | Used for input of match compare data values.                           |

10/3/97

The CAM is prepared for match operations by writing to data and instruction registers via the control port. Since we are only interested in matching 48 bits, it will be necessary to set the global mask to ignore 16 bits of the 64–bit match field. If the MAC has an available EPROM space, the CAMs' control port may be accessed in this space.

# THE EXTERNAL ADDRESS DETECTION INTERFACE

The EADI is provided on the MAC to allow external address filtering. The EADI interface can be used in conjunction with external logic (the purpose of this application note) to capture the packets' destination address from the serial bit stream, to compare the captured address, and determine whether the MAC should accept the p<u>acket</u>. The MAC supports external CAMs via its SFBD and EAR pins.

#### **RELEVANT SIGNALS**

| Pin Name | Pin<br>Function                     | Туре                  | No. of<br>Pins | Comments                                         |

|----------|-------------------------------------|-----------------------|----------------|--------------------------------------------------|

| SFBD     | Start<br>Frame<br>Byte<br>Delimiter | Output<br>from<br>MAC | 1              | Used by FPGA to indicate start of frame.         |

| EAR      | External<br>Address<br>Reject       | Input<br>to<br>MAC    | 1              | Used to reject the<br>current incoming<br>frame. |

### MCM69C232 CAM BLOCK DIAGRAM

### SYSTEM BLOCK DIAGRAM

NOTE: The FPGA uses several signals of both the CAM, MAC, and PHY.

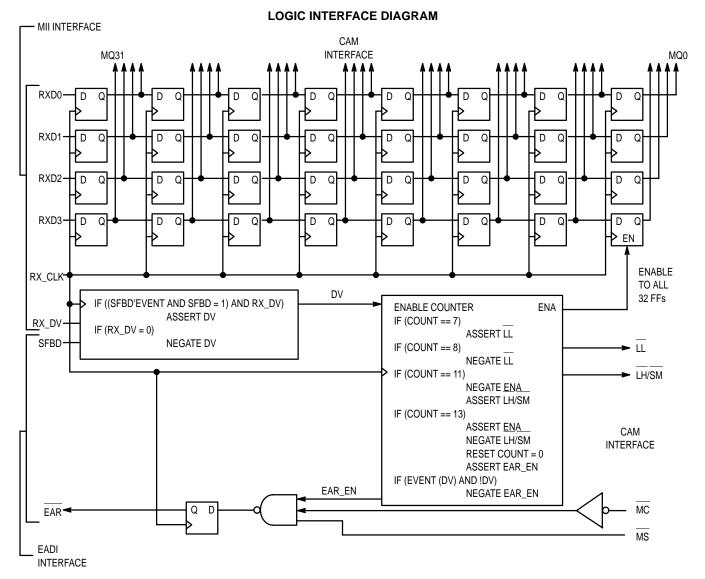

#### **OPERATION OF THE LOGIC INTERFACE**

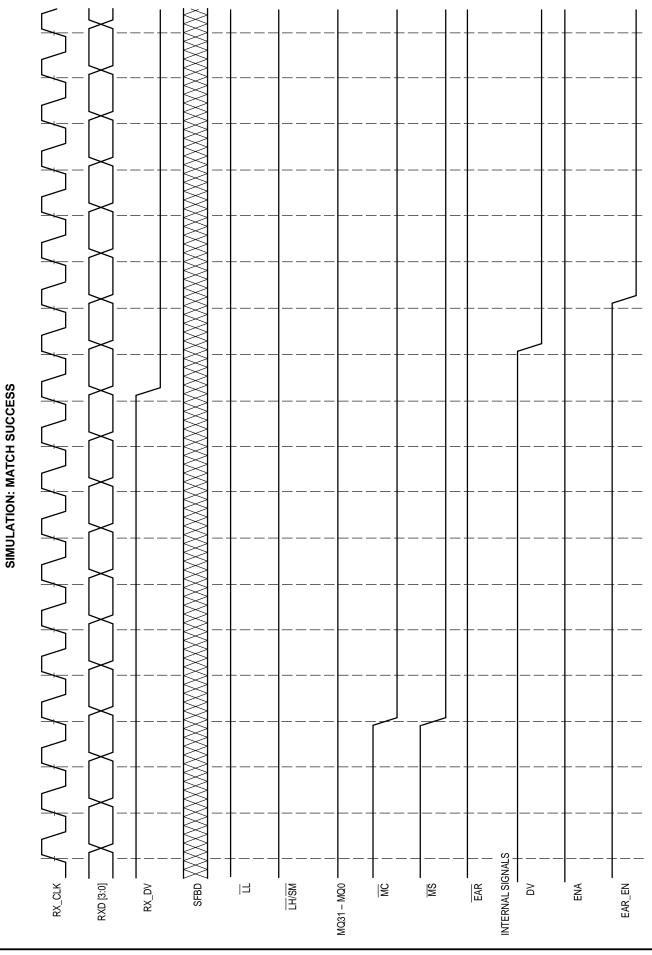

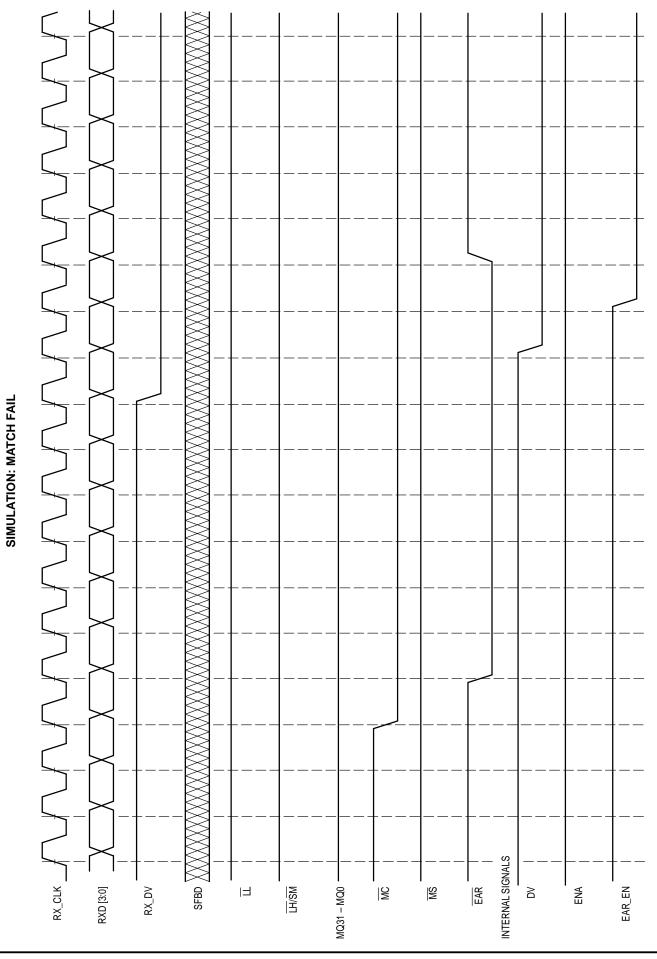

Receive data from the PHY is continuously clocked into the Logic I/F via RXD[3:0] and the RX\_CLK signals. RX\_DV is used to indicate that valid receive data is being presented on the RXD[3:0] signals. RX\_DV remains asserted until after the last nibble of the CRC is driven on RXD[3:0]. RX\_DV, when negated, resets the Logic I/F to its initial state.

An initial rising edge of the SFBD signal indicates that a start of valid data is present on the RXD[3:0] pins. The destination address, 48 bits wide, is then shifted into the Logic I/F, four bits per clock, and then presented to the CAM 32 bits at a time via the LL and LH/SM signals. The LH/SM signal then starts the match process of the CAM. The CAM will then respond with MC and if the destination address was not in

the CAM, the MS will not assert. The Logic I/F then signals rejection of the frame to the EADI via its EAR signal. **RELEVANT SIGNALS**

| EAR_EN | MC | MS | EAR | Comments                        |

|--------|----|----|-----|---------------------------------|

| 0      | Х  | Х  | 1   | Address not yet latched.        |

| 1      | 1  | Х  | 1   | Address compare in process.     |

| 1      | 0  | 0  | 1   | Match successful.<br>No Reject. |

| 1      | 0  | 1  | 0   | Match fail. Reject.             |

For More Information On This Product, Go to: www.freescale.com

#### SUMMARY

Motorola's number one global leadership position as a supplier of state of the art FSRAM devices has allowed for the advent of the cost effective CAM. With the addition of a small amount of logic it is easy to interface Motorola's MCM69C232 CAM to a MII / PHY Ethernet interface.

The addition of a CAM to a bridge will greatly increase the routing performance of a bridge at a slight increase to the cost of the bridge.

Changes to the logic can be made to facilitate any manufacturers' MII and EADI interfaces with ease. The logic can be easily implemented in a FPGA such as Motorola's MPA1016, the smallest, lowest cost member of Motorola's fine grain FPGA family.

#### REFERENCES

- 1. MCM69C232 4K x 64 CAM, Motorola Inc., 1997.

- 2. Am79C971 10/100 Mbps Ethernet Controller, AMD Inc, 1996.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights not the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and with associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and *Q* are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado, 80217. 1-303-675-2140 or 1-800-441-2447

Mfax™: RMFAX0@email.sps.mot.com

- TOUCHTONE 1-602-244-6609

Motorola Fax Back System

- US & Canada ONLY 1-800-774-1848

- http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/

Mfax is a trademark of Motorola, Inc.

JAPAN: Nippon Motorola Ltd.; SPD, Strategic Planning Office; 4-32-1, Nishi-Gotanda; Shinagawa-ku, Tokyo 141, Japan. 81-3-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; 8B Tai Ping Industrial Park, 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

CUSTOMER FOCUS CENTER: 1-800-521-6274

<sup>()</sup>For More Information On This Product, Go to: www.freescale.com