#### **Freescale Semiconductor**

Order this document by AN1776/D

**AN1776**

# Stereo Audio Transmission Over The CAN Bus Using The Motorola MC68376 With TouCAN Module

By Allan Dobbin

Transportation Systems Group

East Kilbride, Scotland

Rev 1.0, 10th July 1998

### 1 Introduction

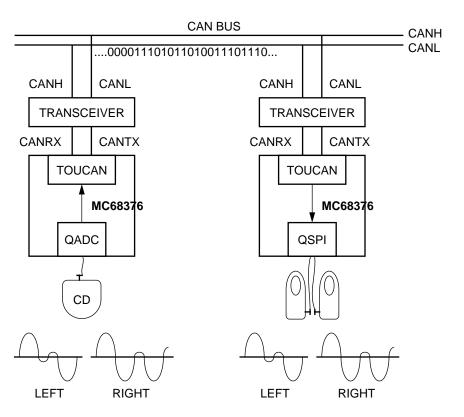

The main purpose of this application note is to provide the reader with a working knowledge of the Motorola TouCAN module. A non-typical CAN application of stereo-audio transmission is used as an example. The Motorola MC68376 microcontroller with TouCAN is used and its QADC and QSPI modules are demonstrated also. The source code for the TouCAN module and all audio transfer is provided in C.

In this example, an MC68376 MCU samples the stereo audio data using the QADC. The resultant sampled data is transmitted onto the CAN bus by the TouCAN module and is received by a second 68376 MCU also connected to the CAN bus. The receiving MCU uses a small internal RAM buffer for temporary storage before outputting the audio data on the QSPI to an external DAC for reproduction of the analogue signal. The MCUs use the queuing mechanism of the QADC and QSPI to minimize CPU overhead.

© Freescale Semiconductor, Inc., 2004. All rights reserved.

### 2 Contents

| 1     | Introduction1                 |

|-------|-------------------------------|

| 2     | Contents                      |

| 3     | Summary of CAN                |

| 3.1   | The Physical Layer            |

| 3.2   | Message Transfer              |

| 3.3   | Monitoring and Arbitration    |

| 3.4   | Errors and Fault Confinement  |

| 3.5   | Bit Timing                    |

| 3.6   | Motorola CAN Modules          |

| 4     | MC68376 Overview              |

| 4.1   | CPU3213                       |

| 4.2   | QADC                          |

| 4.3   | QSM                           |

| 4.4   | 7.5K SRAM                     |

| 4.5   | 8K ROM14                      |

| 4.6   | TPU14                         |

| 4.7   | CTM14                         |

| 4.8   | SIM                           |

| 4.9   | TouCAN14                      |

| 4.9.1 | Message Buffers               |

| 4.9.2 | TouCAN Bit Timing             |

| 4.9.3 | Pin Configuration             |

| 4.9.4 | Interrupts                    |

| 4.9.5 | Message Filters               |

| 4.9.6 | Error Counters                |

| 4.9.7 | TouCAN Initialization         |

| 5     | Audio Transfer                |

| 5.1   | Audio Input                   |

| 5.1.1 | Digital Audio Sampling23      |

| 5.1.2 | QADC to TouCAN Transfer 27    |

| 5.2   | Audio Output                  |

| 5.2.1 | Digital to Analogue Converter |

| 5.2.2 | QSPI Operation                |

| 5.2.3 | QSPI Data Output Timing       |

| 5.2.4 | QSPI Data Updating Mechanism  |

### **Application Note**

| 5.2.5 | Receiving Data from CAN                   | 35 |

|-------|-------------------------------------------|----|

| 5.2.6 | Synchronizing Audio Output to Input       | 36 |

| 5.2.7 | Altering QSPI Output Rate and Buffer Size | 39 |

| 6     | Hardware Design                           | 42 |

| 6.1   | Audio Input Hardware                      | 43 |

| 6.2   | Audio Output Hardware                     | 45 |

| 6.2.1 | Digital Signals                           | 45 |

| 6.2.2 | Analogue Signals                          | 46 |

| 6.3   | CAN Hardware                              | 47 |

| 7     | Software                                  | 48 |

| 7.1   | File Summary                              | 48 |

| 7.2   | Generic TouCAN Routines – file 'toucan.c' | 48 |

| 7.2.1 | toucan_init_global                        | 48 |

| 7.2.2 | toucan_MB_off                             | 49 |

| 7.2.3 | toucan_bus_on                             | 49 |

| 7.2.4 | set_ip                                    | 49 |

| 7.3   | Audio Input – file 'ain.c'                | 49 |

| 7.3.1 | ain_toucan_ init                          | 49 |

| 7.3.2 | ain_QADC_ init                            |    |

| 7.3.3 | ain_Q2_ISR                                |    |

| 7.3.4 | ain_MB4_ISR                               |    |

| 7.3.5 | Audio-in main routine                     |    |

| 7.4   | Audio Output – file 'aout.c'              |    |

| 7.4.1 | aout_toucan_init                          |    |

| 7.4.2 | aout_SPI_init                             |    |

| 7.4.3 | testSPIspeed                              |    |

| 7.4.4 | aout_MB6_ ISR                             |    |

| 7.4.5 | Audio-out main routine                    |    |

| 7.5   | Source Listings                           |    |

| 7.5.1 | ain.c                                     |    |

| 7.5.2 | aout.c                                    |    |

| 7.5.3 | toucan.c                                  |    |

| 7.5.4 | audio.h                                   |    |

| 7.5.5 | regs.h                                    |    |

| 7.5.6 | toucan1.h                                 | /1 |

| 0     | Poforonoco                                | 72 |

Summary of CAN The Physical Layer

### 3 Summary of CAN

The Controller Area Network (CAN) was originally developed by BOSCH Gmbh as a serial communications protocol to pass information between controllers on an automotive network and thus reduce the growing complexity of the wiring harness on modern car design. The protocol had to include prioritization of messages, flexible configuration, multicast reception, multiple bus masters, error detection, fault confinement and automatic retransmission.

Over recent years there has been a steady growth in the number of applications using the CAN interface. It is already widely used in the Automotive industry in Europe and increasingly in the USA. In automotive electronics, engine control units, anti-lock braking and sensors may be connected using a high-speed CAN bus with bit-rates up to 1 Mbit/s whereas electric windows and vehicle lighting may be connected to a low speed bus with data transmission rates of between 10 to 100 kbit/s. Other applications include industrial and nautical equipment, medical apparatus, elevator controls and even entire manufacturing plants may interface intelligent control systems communicating in real time using CAN networks.

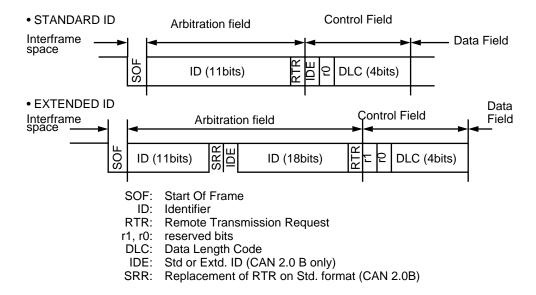

The original CAN specification provided 11 identifier (ID) bits. The updated CAN specification provides for either 11 ID bits or for a larger identifier range using 29 bits. The 11-bit ID format is referred to as the *standard* format and is governed by the CAN standard 1.2/2.0A, whilst the 29-bit ID is referred to as the *extended* format. CAN standard 2.0B caters for both 11 and 29-bit ID's. The majority of current applications use the standard 11-bit identifier as it has greater throughput i.e. the smaller ID field is less of an overhead than a 29-bit field. See reference #1 for the full CAN specification.

# 3.1 The Physical Layer

The physical layer covers the transfer of the data between the different nodes on the CAN network and all electrical properties. The actual physical interface is not described within the CAN specification but usually consists of a two-wire differential bus with each signal designated CANL and CANH. The 'off' state of the bus is called *recessive* and the 'on' state is *dominant*. The physical interface is designed so that more than one node may drive the bus at any one instant without damage. If both dominant and recessive bits are transmitted onto the bus together, the resulting bus state will be dominant. Using a wired-AND implementation as an example, logic "0" would be dominant and logic "1" would be recessive and the bus state would be 0 if any input was 0.

### Application Note

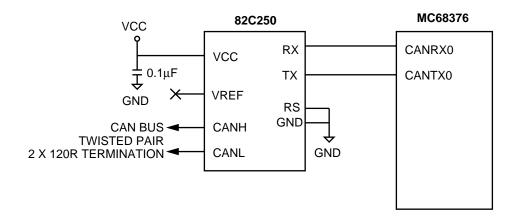

The actual voltage levels that appear on the CAN bus are not defined in the Bosch specification and several different transmission mediums may be used. Although twisted pair is common, others may be used including optical and single wire implementations. Most controller ICs implementing the CAN protocol do not include the physical layer drivers, but have CMOS transmit and receive pins instead. A common interface IC is the Philips 82C250 transceiver which implements the physical layer as defined by ISO 11898 (CAN standard for high speed communications). This IC is used in the hardware described later in this application.

The 82C250 outputs nominal voltage levels of 3.5V on CANH and 1.5V on CANL for the dominant state i.e. 2V differential. The pins do not drive during the recessive state and are tied together using termination resistors to produce a zero differential. The transceiver interprets an input differential greater than 1V as dominant.

The TouCAN module has one receive input, CANRx0 and two transmit outputs, CANTx0 and CANTx1. The transmit outputs may be configured as full CMOS with positive or negative polarity or as open drain. The receive input may be configured as 0 or 1 dominant. On the 68376 device, only CANTx0 and CANRx0 are bonded out to pins. The TouCAN module is described in detail in the next section.

The maximum speed of a CAN bus, according to the standard, is 1 Mbit/s. Since the arbitration scheme requires that the data propagates to the most remote node and back, the maximum cable length at this transmission rate is limited (by the speed of propagation) to 40 meters. The cable length may be increased at lower transmission rates i.e. up to 500 meters at 125 kbit/s. This transmission speed limitation is due to the propagation delay and is described in Section 3.5 Bit Timing.

# 3.2 Message Transfer

Four different frame types are possible in CAN.

A **remote frame** is transmitted from a node acting as a receiver and is a request for data. This remote frame contains no data, but does contain the ID of the type of data it is requesting.

An **error frame** is transmitted by any node on the bus which detects a bus error. This error frame consists mainly of dominant bits which override the current message and break the CAN bit stuffing rule (described in Section 3.3). This forces the transmitter to abort transmission of the current message and ensures that all nodes on the bus are aware of the error.

An **overload frame** is used when a node requires a delay between reception of successive data frames.

Summary of CAN Message Transfer

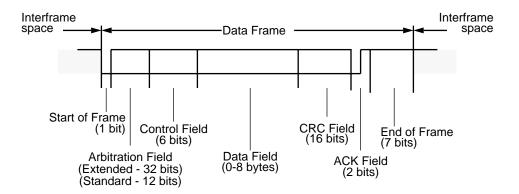

A **data frame** is a regular message frame that carries data from the transmitter to the receivers. Under normal operating conditions, the data frame is the predominant, or only, frame on the bus and is described in more detail. A data frame consists of several fields as shown below.

issued automatically by the CAN controller independently of the CPU.

**NOTE:** Data and remote frames are issued by the CAN controller after instruction by the CPU whereas error and overload frames are usually

Figure 1 CAN Data Frame

**start of frame** — a single dominant start bit indicates the start of a message from one or more nodes.

arbitration field — this contains the message ID plus the RTR bit. An 11-bit ID is used for standard format and 29 bits for extended format as shown in Figure 2. The extended format additionally contains the SRR and IDE bits. The ID is usually used to assign the message type i.e. air temperature, engine speed, audio left, etc. and not the destination address, however this is specified by the system designer. The ID is also used to assign priority to messages – priority is discussed in more detail in the section on arbitration. The RTR bit (Remote Transmission Request) specifies whether the frame is a data frame or a remote frame. The IDE bit (Identifier Extension indicates 11-bit or 29-bit identifier) and SRR (Substitute Remote Request) are transmitted recessive for an extended format frame.

**control field** — this field contains a 4-bit data length code (DLC) plus two reserved bits. The DLC specifies how many bytes of data are contained within the data frame and 0 to 8 bytes are allowed. Codes for 9 to 15 are not permitted.

**data field** — the data consists of between 0 to 8 bytes and can vary in length i.e. air temperature may consist of two data bytes, whereas audio

### **Application Note**

may consist of eight. A zero byte message does have its uses and could be used as a wake-up command, a synchronization command or a request for data (in the case of a remote frame where RTR would be recessive).

**CRC field** — this consists of a 15-bit cyclic redundancy sequence which allows all nodes to perform a frame security check for detecting bit errors, plus a single recessive bit used as a CRC delimiter. The CRC sequence is derived from all preceding fields.

ack field — this consists of two bits – the ACK slot and the ACK delimiter. The transmitting node sends two recessive bits but any other active node on the network which receives the frame correctly will force the first bit to dominant. This acts as an acknowledgment to the transmitter that the message has been successfully transmitted on the bus. This does not necessarily mean that the node(s) which the message was intended for has received it, but only that at least one node has received it – all active nodes will acknowledge the frame whether or not they have been programmed to filter that particular ID. If the transmitting node does not detect a dominant acknowledge bit, it will repeat transmission of the frame.

**End of frame** — the end of message is indicated by the "end of frame" field which consists of seven recessive bits.

**Interframe space** — this normally consists of an intermission period of 3-bit times plus the bus idle period. Nodes cannot transmit data frames or remote frames during the intermission period and the bus will be recessive during this 3-bit period. The bus idle period is of arbitrary length and all nodes will recognize the bus as being free during this recessive state.

The arbitration fields for standard and extended formats is shown in Figure 2.

Summary of CAN Monitoring and Arbitration

Figure 2 Standard vs Extended Arbitration Fields

## 3.3 Monitoring and Arbitration

There are certain rules that all nodes must adhere to in keeping with the CAN protocol standard. These include bit stuffing, cyclic redundancy check, frame checks and the acknowledgment process. Bit stuffing ensures that sufficient edges are generated for synchronization since NRZ (non-return-to-zero) coding is used – after five consecutive equal bits, an additional complementary bit is added, or stuffed, by the transmitter. To enforce these rules all nodes must monitor the bus. This means that all active nodes on the network, receivers and transmitters alike, will monitor every bit of each message for proper conformance to the CAN protocol. As soon as violation is detected by any node then those nodes will transmit an error frame which consists of six consecutive dominant bits (except in the case of error passive nodes which transmit a recessive error frame – see Section 3.4 Errors and Fault Confinement). Since this violates the law of bit stuffing, it acts as a message to all other nodes that the current message is corrupt and transmission should be aborted.

This monitoring of bits by the transmitter serves another purpose i.e. arbitration. Since several nodes may commence transmission at the same time, each message's unique ID within the arbitration field is used to determine who wins control of the bus. The process is as follows: two or more nodes transmit a dominant start bit at the same time and both successfully monitor the correct state on the bus. They then commence transmission of the 12 (or 32) arbitration bits until at some point one node transmits a dominant and the other transmits a recessive. Due to the nature of the physical interface, the dominant bit prevails and so the

### **Application Note**

unsuccessful node detects this and simply backs off its own transmission and waits for the current message to end before trying for bus arbitration again, but participates as a receiver on the current transmission. The successful node continues transmission and is unaware that there was ever any conflict, or arbitration, for the bus.

The arbitration process allows assignment of priority by giving highest priority messages a low numerical ID (in a 0 dominant system). Generally, high priority is assigned to rapidly changing data. All CAN nodes receiving a message must check the ID to determine whether or not there is any useful data in the message for its use. On highly integrated CAN controllers (such as the TouCAN), the hardware will provide ID filtering where a mask permits only certain ID combinations to filter through to the internal receive buffers. Less integrated controllers will not provide hardware filtering thus the application software will have to burden the CPU with the additional task of testing the message ID of every message received on the bus.

# 3.4 Errors and Fault Confinement

Fault confinement on the bus is possible as CAN nodes are able to distinguish between short disturbances and permanent failures. This is accomplished by the use of two 8-bit error counters within each node – a transmit error counter and a receive error counter. In summary, the node will increase its receive or transmit counter when it detects any of the five possible error types (bit error, stuff error, CRC error, form error or acknowledgment error) and will decrement when it completes a successful reception or transmission. This means that any temporary disturbances result in small counts that recover back to zero, whereas permanent failures result in large counts.

The Rx error counter increases by 1 if an error is detected during reception. However if the first bit after transmission of an error flag is dominant, which suggests that another node did not detect this same error, the Rx error counter is increased by 8. The Tx error counter is always increased by 8 if an error is detected while the node is transmitting. The Rx error counter is decreased by 1 after a successful reception and the Tx error counter is decreased by 1 after a successful transmission. This method of incrementing the counters ensures that if the fault is local to a node then only its own error counters will increment rapidly.

A node will take on one of three states depending on the value within its error counters as follows:

**error active** — this is the regular operational state of the node and occurs when both counts are less than 128. In this state the node can participate in usual communication. If it detects any errors during

Summary of CAN Bit Timing

communication, it indicates this by transmitting an ERROR ACTIVE FLAG which consists of 6 dominant bits and therefor blocks the current transmission.

error passive — this state occurs when either of the counters increment past 127 and indicates that there is an abnormal level of errors at this node. The node still participates in transmission and reception, but is forced to wait slightly longer after a message transmission before it can initiate a new message transfer of its own. This extra delay for the error passive node is known as *suspend transmission* and is accomplished by having the node send an additional 8 recessive bits at the end of its frame. This means that an error passive node loses arbitration to any error active node regardless of the priority of their IDs. When an error passive node detects an error during communication it indicates this by transmitting an ERROR PASSIVE FLAG. This consists of 6 recessive bits which will not disrupt the current transmission (assuming another node is the transmitter) if the error turns out to be local to the error passive node.

**bus off** — this state occurs when the transmit error count reaches 256. This indicates that the node has experienced consistent errors whilst transmitting. In this state, the node switches off its bus drivers and no longer influences the bus. The node will eventually be re-enabled for transmission and become error-active after it has detected 128 occurrences of 11 consecutive recessive bits on the bus which indicate periods of bus inactivity.

### 3.5 Bit Timing

Nodes connected to the CAN bus use a high frequency clock and a prescaler of at least 5 bits which allows division of this clock by a range of at least 1 to 32. The period of this resulting lower frequency clock is a *time quantum* and this is the basic unit of measurement for the CAN bit timing. The transmission period of the node will be a multiple of these time quanta.

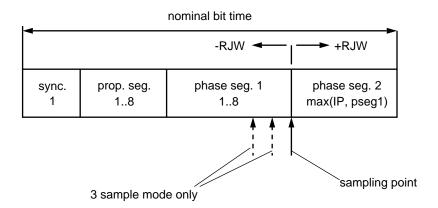

Referring to Figure 3, each bit on the CAN bus is composed of four time segments as follows:

**synchronisation segment** — this has a fixed size of one time quanta and the bit edge is expected to lie within this segment. Each node synchronizes to the transmitting node by ensuring that the first edge of a message lies within this segment. Further resynchronizations are performed on subsequent edges within the message.

**propagation segment** — this is programmable between 1 and 8 time quanta and compensates for delays on the CAN network. Its value must be at least twice the maximum time the signal takes to propagate between any two nodes on the system, i.e.

### **Application Note**

prop > 2 • (output driver delay + bus line delay + input comparator delay)

The output driver and input comparator delays are dependent on the bus interface hardware and the bus line delay is the total bus length multiplied by the speed of propagation (approx. 2 x 10<sup>8</sup> m/s but depends on cable used).

phase segment 1 and 2 – pseg1 is programmable between 1 and 8 time quanta and pseg2 will be of at least equal length, usually down to a minimum of 2. The minimum value of pseg2 is required to allow the node time to process the bit value since it is sampled at the end of pseg1. This minimum process time is called the information processing time or IP. The CAN node will automatically lengthen pseg1 or shorten pseg2 upon detecting edges within the message to allow resynchronization with the transmitting node. The amount of time quanta these segments may be altered by must not be greater than the *resynchronization jump width*, RJW, which is limited in size to that of pseg1 up to a maximum of 4 time quanta.

The automatic adjusting of pseg1 and 2 by the CAN controller is required to allow each node to resynchronise with the current transmitter during each recessive to dominant transmission. If the transmitter has an internal clock that is slightly slower than the receiver then the transition will be 'late' and will occur after the sync. seg. within either the prop or pseg1 segments. In this case, pseg1 is lengthened to compensate. Conversely, if the transmitter is fast then the transition will be received 'early' i.e. before the sync. seg, within pseg2 of the previous bit time. In this case, pseg2 is shortened to compensate.

The values assigned to segments are dependent on the CAN bit rate required plus the oscillator tolerance of each node. Generally, the propagation segment is set to the minimum amount of time quanta that allow for twice the worst case signal propagation delay. If maximum bit rates are required, then set pseg1 and 2 small with respect to prop. seg. If maximum resynchronization is required to allow the use of low tolerance clock oscillators then set pseg1 and 2 large in relation to prop. seg. up to a value of 4. Usually RJW is set to maximum value i.e. equal to pseg1 (up to a maximum of 4).

Refer to Section 4.9.2 for an example of TouCAN bit timing set-up.

Summary of CAN Motorola CAN Modules

Figure 3 Can Bit Timing

## 3.6 Motorola CAN Modules

Motorola currently offer three different CAN modules to support CAN on each of their 8, 16 and 32-bit microcontroller families i.e. MCAN, MSCAN and TouCAN.

MCAN provides the lowest performance / highest CPU overhead of the three and is available on the HC05 family. One Tx and two Rx buffers are provided.

MSCAN has a higher level of integration and provides three Tx buffers and two Rx buffers. This module is available as two slightly different versions for the HC08 and HC12 families. The MSCAN12 version has 2 x 32-bit filtering which is double that of the MSCAN08.

TouCAN offers the highest performance and is currently available on the HC16, 683xx and PowerPC MPC500 families. It provides 16 message buffers each configurable as Rx or Tx and 3 x 32-bit filter masks. The TouCAN operation is covered in more detail in Section 4.9.

### **Application Note**

#### 4 MC68376 Overview

The Motorola MC68376 is a member of the highly integrated 683xx modular family of microcontrollers where modular building blocks are shared throughout the family and connected internally via the inter-module bus (IMB). The 68376 comes in 160 QFP package and consists of several modules as described in the following sections. All modules are described briefly with the emphasis on the TouCAN module. For a full description refer to reference #2.

### 4.1 CPU32

32-bit architecture based on the 68020 processor. May operate on 8-bit, 16-bit and 32-bit operands, however only a 16-bit data bus exists outside the CPU. Contains eight 32-bit data registers, eight 32-bit address registers, 32-bit stack and program counters plus an 8-bit condition code register. Features a built-in background debugging mode (BDM) which was used in the debugging and testing of this application. The CPU32 provides seven levels of interrupt priority and 256 exception vectors.

#### **4.2 QADC**

10-bit analogue to digital converter with 16 direct input channels expandable to 44 in multiplexed mode and conversion time around 8 micro-seconds. The distinctive feature on this ADC is its queuing mechanism. The CPU does not have to intervene after every analogue conversion, instead a queue of up to 40 conversion commands may be utilized. Each conversion command has a corresponding result word register which stores the resulting 10-bit digital conversion. Our system makes extensive use of this queuing mechanism and interrupts so that there is minimal overhead on the CPU during audio sampling.

#### 4.3 QSM

The Queued Serial Module consists of two independent ports – an SCI (Serial Communications Interface) and QSPI (Queued Serial Peripheral Interface). The SCI is a standard asynchronous serial interface, or a UART and is not used in our system. The QSPI is a synchronous interface similar to the Motorola SPI used on 8-bit micros, but with two important additions. The first of these is a sixteen word queue offering similar advantages as the queuing mechanism on the QADC. A table of up to sixteen serial transfer commands may be used which act on a corresponding table of sixteen receive and transmit data registers. The use of this queue allows reduction on the CPU overhead since up to sixteen transfers without CPU intervention are possible. The second addition is a port of four PCS (Programmable Chip Selects). Each of the sixteen queued command words activates the required PCS for one of the serial transfers. Our audio system makes use of both the queue and the PCS as will be described in the audio section.

### 4.4 7.5K SRAM

There are two RAM blocks – a 4K byte block of SRAM for general purpose use plus a 3.5K byte block for either general use or TPU microcode emulation. The internal SRAM is sufficient for our application, so no additional external memory is required.

#### 4.5 8K ROM

8K bytes of masked ROM available for high volume users. In most applications this is used for initialization and start up routines.

#### 4.6 TPU

The TPU is essentially an internal co-processor with sixteen dedicated input/output channels for control of timer based functions. This module is very useful in engine management and motor control applications but can be put to many other general purpose uses i.e. additional SCI (UART) ports or PWM channels. The TPU is not required in our application.

#### 4.7 CTM

The configurable timer module with two 16-bit modulus counters, 16-bit free running counter, four double action submodules and four pulse width modulation submodules provides additional timer / counter functionality. The CTM is not required in our application.

### 4.8 SIM

The System Integration Module includes the external bus interface, 12 chip selects, system protection block with software watchdog, periodic interrupt timer, bus monitor and the PLL generated system clock.

### 4.9 TouCAN

The TouCAN module is a communication controller that implements the CAN protocol up to maximum possible CAN transfer rates of 1Mbit/s. Both standard (11-bit identifier) and extended (29-bit identifier) message formats are supported as specified in CAN protocol specification 2.0B. The TouCAN module includes the following features:

- 16 message buffers for receiving or transmitting data frames.

- Programmable bit rate up to 1Mbit/s.

- 2 serial message buffers for double buffering of both received and transmitted data.

- 16-bit free-running timer provides time-stamp.

- Supports CAN 2.0B both standard and extended ID formats.

- CPU overhead reduced by implementing local ID fields within each message buffer plus ID bit masking using one of three 32-bit mask registers.

- Automatic reply mechanism available for remote request frames.

- 19 maskable interrupt sources.

- Low power sleep mode with wake-up mechanism.

### **Application Note**

#### 4.9.1 Message Buffers

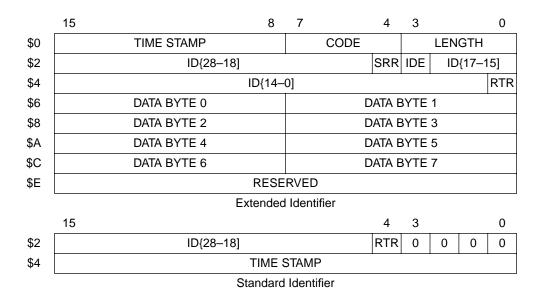

The TouCAN provides sixteen message buffers (MBs), each of which can be assigned either as a transmit or receive buffer and each may optionally generate an interrupt after successful completion of data transfer. Each buffer contains eight 16-bit registers which take two slightly different formats depending on whether standard or extended format is selected as shown.

Figure 4 TouCAN Message Buffer Structures

The **code** field is initially written by the CPU to define the operation of the MB i.e. inactive, receiver, transmitter, remote request, etc. and is updated by the TouCAN after bus activity to indicate whether a successful operation has occurred. The **time stamp** is copied from the free-running timer to the MB by the TouCAN to indicate when reception or transmission occurred. On MBs configured for transmission, the CPU writes the **length** and **data** fields to be transmitted on the bus within a data frame, whereas on receive MBs, the TouCAN writes these two fields as they were received from the bus. The ID field is written by the CPU including the **IDE** bit to select either standard or extended format for both transmission and reception. On a Tx MB, the ID field is transmitted as written, whereas on a Rx MB, the ID field is combined with one of the receive mask registers and the resulting filter is used to check for a comparison on any received frames. If a match is made on a received frame, its ID will then be copied into the MB's ID field, regardless of the contents of the mask register.

The code field is not initialized after power-up or reset and must manually be set to an inactive receiver (0000) or inactive transmitter

MC68376 Overview TouCAN

(1000) by the CPU. Once all TouCAN registers have been initialized and the message buffers have their data and ID fields configured, the code may be set to active receiver (0100) or active transmitter (1100 and RTR = 0) or alternatively one of the remote modes may be selected for transmission. The remote modes are remote transmission request (1100 and RTR = 1) which means the buffer transmits an ID only as a request for data, and remote response (1010) which is the code to transmit data only on reception of a matching ID from an RTR frame. After transmission or reception of data on the CAN bus, the TouCAN will update the MBs code field and its corresponding bit in the IFLAG register will be set.

Reading the control/status word on a receive MB will lock that MB so that its entire contents may be read without a serial message buffer overwriting any of the data. The MB is unlocked by reading the control/status word of another MB or by reading the 16-bit timer. When polling a MB for completion of data transfer, the IFLAG register should be used and not the code field within the MBs CONTROL/STATUS register as this could lock the MB and prevent a message from being transferred.

The length field specifies how many data bytes are contained within the message – zero to eight. On transmit buffers the CPU writes this value, whereas on receive buffers the TouCAN copies this field from the DLC field within the CAN message.

During reception or transmission of data, the time stamp is captured when the ID field appears on the CAN bus. The captured time stamp value is transferred from the TouCAN's free-running counter to the relevant MB only when the entire message frame has been successfully transferred. If standard format is used, all 16-bits of the time stamp are used, but for extended format only the upper 8-bits of the timer are used.

The ID\_HIGH and ID\_LOW registers contain the arbitration field just as it appears on the CAN bus, i.e. the SRR, IDE and RTR bits are embedded within the 11 or 29-bit ID. This is why the layout of the bits is slightly different for the standard and extended formats. The user must be careful when writing these registers that the ID value is as intended. The RTR, IDE and SRR bits are as specified in the CAN specification i.e. RTR is set to 1 for remote frame request, IDE is set to 1 for extended format and SRR in extended format should always be set to 1.

The MBs data registers contain up to eight bytes of data as specified by the length field. As with the length field, these registers are written by the CPU and transferred by the TouCAN on transmit buffers, but are written as received from the CAN bus in receive buffers.

### **Application Note**

The TouCAN uses a double buffering scheme where one of two shadow serial message buffers are employed for temporary buffering of data. This allows the TouCAN to buffer all CAN messages before transferring them to a matching message buffer. These two message buffers are not accessible by the CPU.

### 4.9.2 TouCAN Bit Timing

The TouCAN bit timing follows the rules defined in Section 3.5. An 8-bit prescaler is used to divide the system clock by up to 256 to obtain a serial clock for TouCAN use. The PRESDIV register is used to select this divide ratio and the resulting clock is called the S-clock, whose period is one time quanta.

The propagation, phase 1 and phase 2 segment values are set by programming the PROPSEG[2:0], PSEG1[2:1] and PSEG2[2:0] bits within CANCTRL1 and CANCTRL2 registers. Since the synchronous segment size is always 1 and the other segments are one more than the value programmed in the register bit field, the bit time length will be:

bit time =

$$1 + (PROPSEG + 1) + (PSEG1 + 1) + (PSEG2 + 1)$$

time quanta

i.e.

bit rate =

$$\frac{F_{SYS}}{(PRESDIV + 1) \bullet (4 + PROPSEG + PWSEG1 + PSEG2)}$$

bits/s

The resynchronization jump width is set by programming the RJW[1:0] field in CANCTRL2 and should not be greater than PSEG1.

For example, if the system clock frequency is 20MHz and the maximum bit rate of 1Mbit/s is required then one possible set-up is as follows:

PRESDIV = 1, i.e. prescaler divide rate is 2 and S-clock is 10MHz, time quanta = 100ns.

PROPSEG[2:0] = 4, so propagation segment is 5 time quanta.

PSEG1[2:0] = 1, so phase 1 segment is 2 time quanta.

PSEG2[2:0] = 1, so phase 2 segment is 2 time quanta.

RJW[2:0] = 1, i.e. resynchronization up to 2 time quanta.

This allows for a propagation time of 5 • 100ns i.e. 500ns which is sufficient for most transmission circuits. RJW cannot be bigger than PSEG1, so is limited to 200ns. On many systems, for instance those with bus lengths less than say 10m, PROPSEG could be made smaller, allowing PSEG1 and PSEG2 and thus RJW to be increased. Larger RJW will compensate for less accurate oscillators or for PLL systems.

MC68376 Overview TouCAN

There are some restrictions that must be observed when setting the TouCAN bit timing. If the S-clock is equal to Fsys, i.e. PRESDIV = 0, then PSEG2[2:0] must be set to at least 2, otherwise PSEG2[2:0] must be at least 1. The bit time should be at least 9 system clocks in length to guarantee correct operation. This should not pose any problems as in most cases the system clock will be at least 16MHz which means there will always be more than 9 system clocks per bit time since maximum bit rate is 1Mbit/s.

### 4.9.3 Pin Configuration

RXMODE[1:0] and TXMODE[1:0] in the CANCTRL0 register allow the receive and transmit pins to be configured independently of each other. On the 68376, only the CANRX0 pin is available so the RXMODE1 bit is not used. Clearing RXMODE0 defines a logic '0' on the CANRX0 pin as dominant, which will be the case when using most CAN transceiver ICs. However, on custom designed CAN bus interface circuits, either setting is possible.

On the 68376, only the CANTX0 pin is available and the following settings are possible for TXMODE[1:0]:

00 - drives '0' for dominant and '1' for recessive.

01 – drives '1' for dominant and '0' for recessive.

1X - drives '1' for dominant and open drain for recessive.

The usual setting when using standard transceiver ICs is 00.

#### 4.9.4 Interrupts

The TouCAN has 19 sources of interrupt, one for each of the 16 MBs, bus off, error and wake up interrupts, and are enabled by setting the relevant bits in the CANMCR (WAKEMSK), CANCTRLO (BOFFMSK and ERRMSK) and IMASK registers. Each of these sources have individual enable bits and status flags but share common interrupt arbitration and request levels.

The interrupt mechanism for the TouCAN is similar to other IMB modules on the 683xx family. The interrupt arbitration field (IARB[3:0] within CANMCR) may take on values 0 through 15 and is reset to 0. A non-zero value must be assigned otherwise the CPU will process a spurious interrupt.

The interrupt priority level is set using ILCAN[2:0]. 0 disables all TouCAN interrupts, while 7 is the highest priority. The IP field within the CPU status register must be set to a value lower than the ILCAN to enable interrupts of this level. The CPU32 allows nested interrupts – the current

### **Application Note**

interrupt increases the CPU IP field to a level equal to its own interrupt priority level. This means that any subsequent interrupts of higher level will override the current interrupt whereas lower or equal requests are disabled until afterwards.

Finally, the vector base address is defined for MB0 by writing IVBA[2:0] and the other interrupts will occupy the preceding 18 vector entries in the vector table. The location of the interrupt vectors are calculated by shifting the IVBA value twice, adding the VBR offset and then adding an offset of 4 times the buffer number as shown in the following examples:

```

IVBA = $40 (vector # 64), VBR = $0000,

MB0 vector address = (IVBA[7:0] << 2) + VBR + (4 x MB#)

= $100 + $0000 + $00 = $0100

IVBA = $60 (vector # 96), VBR = $1000,

MB2 vector address = (IVBA[7:0] << 2) + VBR + (4 x MB#)

= $180 + $1000 + $08 = $1188

```

### 4.9.5 Message Filters

There are three 32-bit mask filter registers on the TouCAN which are used to make some of the ID bits within the message buffers 'don't care' bits. The masks are relevant for receive buffers only. RXGMSK provides a global mask for MB0-13. RX14MSK and RX15MSK are used as unique masks for MB14 and MB15. The default state of these registers after reset is all '1's which means that the ID bits within a message must match all the bits in an active receive message buffer before the message is accepted. The user may write any or all of these bits to a '0' to allow any of the ID bits in a message to be ignored. If all the bits in a mask register are set to '0' then an active receive buffer will accept all messages of the correct format (i.e. standard or extended) from the CAN bus. Bit 19 of the mask register corresponds to the IDE bit within the arbitration field and is always a '1', thus a receive buffer cannot be configured to filter both standard and extended formats. If a node has to accept all messages on a bus then a minimum of two message buffers must be used – one for extended and the other for standard frames.

Bits 20 and 0 in the mask register correspond to the SRR and RTR bits in a message. These bits are always '0' and are never compared to the corresponding bit with the received frame.

Although the mask filters allow reception of a data frame with a different ID field to that originally written into the MB's ID field, the actual ID received on the bus will be copied into the MB. This means the ID within the MB may be altered by a reception

Mask filters are used only for data frames – any remote frames must match the MB's ID field exactly.

Semiconductor, Inc.

### Freescale Semiconductor, Inc.

MC68376 Overview TouCAN

### 4.9.6 Error Counters

As described in Section 3.4, fault confinement on the CAN bus is achieved using two 8-bit error counters. On the TouCAN, these are the RXECTR and the TXECTR registers. These error counters are automatically increased by the TouCAN by 1 or 8 on detection of Rx or Tx errors and decrement by 1 on completion of successful reception or transmission. As described in Section 3, the node status changes from error active to error passive if either counter exceeds 127 and changes to bus off status if the Tx error counter reaches 256. The status of the node is indicated in the FCS[1:0] bits in the ESTAT register and generation of interrupts may be enabled after detection of an error or a transition to bus off state. The ESTAT register also sets either of two warning flags, TXWARN or RXWARN, if either of the error counters exceed 96 as this indicates a heavily disturbed bus.

### 4.9.7 TouCAN Initialization

After the TouCAN is reset (power-up, hard reset or soft reset), all of its control registers default to their reset state but the message buffers are not initialized. The TouCAN module will not attempt to communicate with the CAN bus at this stage as its HALT bit within the CANMCR register is set allowing the CPU access to all TouCAN registers. A typical initialization procedure is as follows:

- 1. Initialize pin configuration and bit timings using the following registers:

- CANCTRL0: RXMODE [1:0], TXMODE[1:0] define dominant and recessive levels and select CMOS or open drain drive. CANCTRL1: SAMP, PROPSEG[2:0] select 1 or 3 samples per bit and a propagation delay of between 1 & 8 time quanta. PRESDIV select how many CPU clocks (1–256) make up one TouCAN time quanta.

- CANCTRL2: RJW[1:0], PSEG1[2:0], PSEG2[2:0] select phase segment delays between 1 & 8 time quanta and re-synchronize with up to 4 time quanta. Adhere to rules in bit timing section.

- 2. Make all 16 message buffers inactive by writing their control field to 0000. The MBs may be activated for Rx/Tx now so they will begin the arbitration process immediately the TouCAN has synchronized with the CAN bus (after step 6) or can be left inactive until the CPU is ready for communication. In either case, the following steps are taken to activate the MB for communication when required: Initialize the ID fields of required MBs by writing the ID\_HIGH and ID\_LOW registers to the necessary values, taking care to embed the SRR, IDE and RTR bits within the 11 or 29-bit identifier. If the MB is to be used for transmit, write the data bytes and length field. Finally, rewrite the control field to make the MBs active Rx (0100) or active Tx (1100), or use one of the remote codes for remote frame set-up.

### **Application Note**

- 3. Write the 32-bit ID mask filter registers RXGMSK, RX14MSK and RX15MSK to filter messages with the required ID. As with the ID field in the MB, take care to embed the three non-ID bits within the ID filter. These registers default to '1's in each if the 29 ID bit fields which mean that every ID bit is compared with the ID field in the message buffer. Also, the bit corresponding to the IDE bit (bit 20) is always a '1' which means that IDE cannot be masked and therefor any one MB cannot be configured to receive both standard and extended format frames.

- Refer to the section on interrupts for a description on interrupt operation. The following registers effect interrupts: CANMCR: IARB[3:0] – set interrupt arbitration value to non-zero if interrupts enabled.

CANICR: ILCAN[2:0] – set between 0 (interrupts disabled) and 7 (highest priority).

CANICR: IVBA[2:0] – indicates the location of the interrupt vector. Finally, select which of the 19 TouCAN interrupt sources are required

IMASK – write a '1' to each bit corresponding to MBs 0–15 where an interrupt is required on completion of transmission / reception. CANMCR: WAKEMSK – set bit if wake-up interrupts are required. CANCTRL0: BOFFMSK, ERRMSK – set bits for bus off or error interrupts.

- 5. Read free running timer to ensure all Rx MBs are unlocked.

- 6. Finally clear the HALT flag in CANMCR to enable the TouCAN to synchronize with the CAN bus and allow participation in communication.

Example TouCAN software initialization is listed in functions ain\_toucan\_init and aout\_toucan\_init in Section 7.

Audio Transfer TouCAN

### 5 Audio Transfer

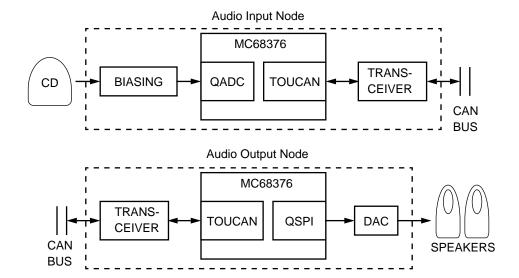

A system for transmitting stereo audio over the CAN bus using TouCAN is described. The system makes extensive use of the Motorola 68376 microcontroller which combines TouCAN, QADC, QSPI, 7.5K bytes SRAM, CPU32, SIM and other additional modules which are not used in this system i.e. ROM and timers.

The audio input node consists of a stereo input jack for audio input, typically from a personal CD player which connects to two of the QADC analogue input pins. The QADC samples at approximately 60kHz i.e. 30kHz per channel, and the data is passed to the TouCAN which transmits it over the CAN bus via an external transceiver IC.

The audio output node also uses a 68376 with TouCAN receiving the audio data via the CAN bus. The 68376 uses internal SRAM to buffer the incoming data before outputting it on the QSPI to an external serial DAC. The DAC provides two low power output audio signals which are capable of driving a pair of amplified speakers. The hardware design is described in full in Section 6.

Figure 5 Input and Output Nodes Connected to CAN Bus

### **Application Note**

### 5.1 Audio Input

### 5.1.1 Digital Audio Sampling

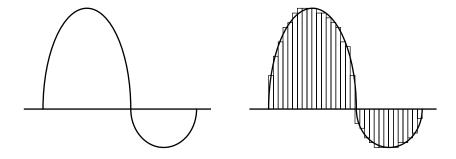

The basic task is to take a pair of analogue audio wave-forms and sample them with regular sampling and adequate resolution, or quantization, to allow them to be represented numerically. The numerical digital data will then be reproduced with the minimal acceptable amounts of noise and distortion.

Figure 6 Analogue Wave-Form and Digitized Version

Typical hearing bandwidth starts at around 20Hz and goes up to between 15 or 20kHz. This range narrows with age as the eardrum becomes less flexible. Nyquist's sampling theory states that a signal must be sampled at least twice the rate of it's maximum frequency component if no information is to be lost. This means that for good audio reproduction, we have to sample at a frequency greater than 40kHz, but even down to 30kHz would still capture the audible range detectable by most of us. As a comparison, CD uses a sampling rate of 44.1kHz with 16-bit accuracy (96dB SNR) for audio reproduction up to 20kHz, whilst FM stereo broadcasting and NICAM 728 stereo TV sound system both use a sampling rate of 32kHz with 14-bit accuracy (84dB SNR) for audio up to 15kHz. Voice reproduction on GSM handsets uses a bandwidth of 300Hz to 3.4kHz with 8-bit accuracy (48dB SNR).

Sampling frequencies in this range are well within the capabilities of the 68376's QADC, which can operate at sampling rates above 100kHz with typical conversion times as low as  $8.6\mu s$ . The main limitation is the CAN bandwidth. Running CAN at 1Mbit/s yields approx. 530kbit/s of data using standard ID format and 460kbit/s using extended ID format due to non-data fields within the message. In our system we will use standard format for higher data bandwidth and assume that most of this is available for audio, but that some additional non-audio messages are present on the bus. In addition, some messages may have to be

Audio Transfer Audio Input

retransmitted in the event of an error. Because of these reasons, we will reserve 90% of the available bandwidth for audio transmission. A simple calculation yields maximum sampling rate for each audio channel as follows:

max. sampling frequency =

$$\frac{\text{available CAN bandwidth}}{(2 \text{ channels}) \bullet (\# \text{ bits in sample})}$$

$\frac{\text{using 10-bit QADC}}{\text{resolution (60dB SNR)}} = \frac{530000 \bullet 0.90}{2 \bullet 10} = 24 \text{kHz}$

A sampling rate of 24kHz will capture audio frequencies up to a maximum of 12kHz and is insufficient for good quality playback. We can consider several options which would allow us to increase the sampling rate:

- i) combine the stereo inputs into a single mono signal,

- ii) use data compression techniques to mathematically compress the data, or

- iii) reduce the resolution of the analogue samples.

Option i) is not suitable since our original requirement was for quality *stereo* reproduction. Option ii) is a viable solution but would put additional loading on the CPU. In our system where the transfer of audio data is the sole task of the CPU, this would probably be acceptable, but on other systems where additional tasks may be running, the loading on the CPU may not be acceptable. Besides, digital data compression techniques are out-with the scope of this note. Option iii) is possible – the noise levels introduced using 8-bit sampling still give acceptable audio reproduction. Also, 8-bit data is more suited to the data byte orientation of CAN.

Re-applying our sampling rate calculation with 8-bit quantization gives:

max. sampling freq. using 8-bit resolution (48dB SNR) =

$$\frac{530000 \bullet 0.90}{2 \bullet 8}$$

= 29.8kHz

Our system frequency is not critical and 20MHz has been selected for simplicity. The 68376 is currently available up to 25MHz but this is not required as CAN bandwidth is our limitation, not processing power. The QADC conversion times are based on the QCLK which in turn is derived from the system clock. The minimum QADC conversion time of 18 QCLKs will be used. The prescaler for our QADC clock can now be calculated to give the 29.8kHz sampling rate:

QADC prescalar =

$$\frac{F_{SYS}}{(Samp. freq. \bullet 2) \bullet Conversion clocks}$$

### **Application Note**

$$\frac{20000000}{29800 \bullet 2 \bullet 18} = 18.5$$

A prescaler value of 19 will be used, resulting in a sampling frequency of 29.2kHz, or 342 (19 • 18) system clocks. This results in CAN bandwidth usage of 88%.

To test audio sampling parameters, a non CAN system was developed using a single 68376 with the same QADC input circuitry and QSPI output circuitry as is used on our final system (hardware described in Section 6). This system was used to test hardware, sampling rates and quantization levels before moving onto a more complicated two-node system with CAN. Simple software was used which sampled the audio input and immediately output the data on the QSPI. This system was used to digitally sample a single audio channel from the analogue 'line-out' socket on a personal CD player and playback using an external DAC and amplified speakers. Experimentation on sampling rates and quantization levels demonstrated that 8-bit resolution gave reasonable results with little loss of quality when compared to 10-bit sampling. The improvement gained with 30kHz sampling when compared with 24kHz was much more noticeable and so the final specification of our system shall be as follows:

sampling rate – 29.2kHz

sampling resolution – 8 bits

no. of audio channels – 2

CAN rate – 1Mbit/s

CAN bandwidth – 88%

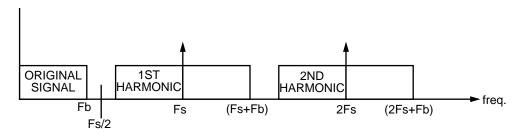

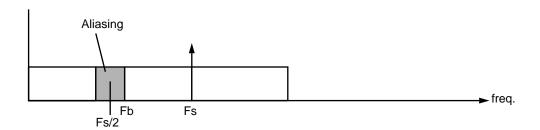

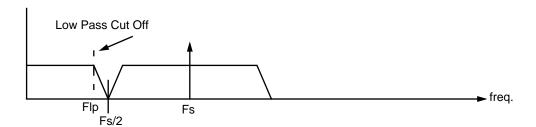

One last subject on digital audio sampling – aliasing. Again, referring to Nyquist's sampling theory and avoiding the detailed mathematics, the sampled baseband signal, Fb, will be reproduced at all harmonics of the sampling rate, Fs, as shown in Figure 6. The original data can be reproduced without loss of data if the sampling frequency is at least twice its highest component.

Audio Transfer Audio Input

Figure 7a Sampled Signal and Harmonics

Figure 7b

Figure 7c

If the sampling frequency is less than double, as shown in Figure 7b, the reproduced signal at the first harmonic will overlap the original signal and the resulting distortion is called aliasing. To avoid aliasing, the sampling frequency should be increased. If this is not possible, a low pass filter must be used to remove some of the high frequency data within the input signal, as shown in Figure 7c. An expensive LP filter with sharp roll-off allows cut-off frequencies at half Fs. Inexpensive LP filters with gentle roll-off requires the cut-off frequency to be lower, thus even more of the original signal is lost. A trade off between price and quality must be made.

In our system, the input signal from a CD will have 20kHz bandwidth. Sampling at 29.2kHz means that aliasing will exist without the use of an

### **Application Note**

LP filter. Brief testing on our non-CAN test system using sinusoidal inputs showed that aliasing was indeed present above 15kHz. However, with audio input, the reproduced signal quality was reasonable since audio content above 15kHz is low. Adding a fourth-order LP filter with cut-off frequency around 14kHz in series with the input produced little or no audible difference. For these reasons, and since LP filter design is not a goal of this note, we shall avoid the use of one in our system.

### 5.1.2 QADC to TouCAN Transfer

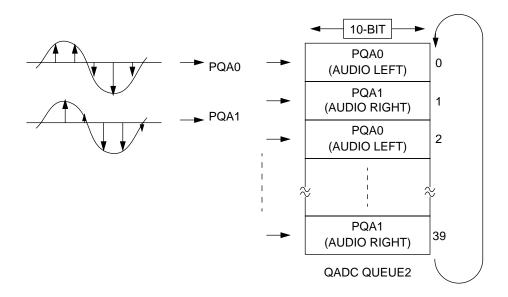

The main objective of the microcontroller on the audio input side of the CAN bus is to sample the analogue input using a fixed sampling rate and then transfer the data onto the CAN bus. The QADC will be used in 'software triggered continuous-scan mode' which allows the QADC itself to control the sampling rate to 29.2kHz per channel i.e. 58,400 samples per second. A single queue, queue 2, with maximum length of 40 conversions will be used to reduce the CPU overhead to a minimum. This queue will be configured to sample left audio channel on PQA0 and then right audio channel on PQA1 alternatively. Once all 40 conversions are complete and the queue is full, the QADC will generate an interrupt to request the CPU to empty the conversion result queue and transfer the data to the TouCAN module.

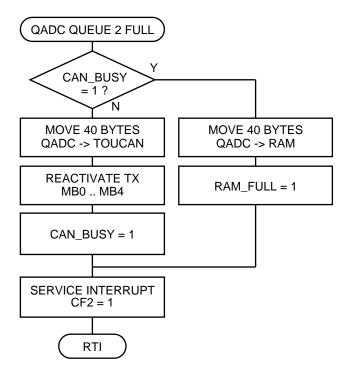

The QADC ISR (interrupt service routine) must move the 40 conversion results immediately as the QADC will loop back to the start of the queue and overwrite the previous results. In particular, the first conversion result must be recovered within 17.1µs i.e. the sampling period, as it is the first to be overwritten during the next iteration of the queue. This process is summarized in Figure 8.

Audio Transfer Audio Input

Figure 8 QADC Continuous Sampling Operation

By assigning five of the available sixteen TouCAN message buffers to transmit audio, each with eight data bytes, we can match the 40 bytes from the QADC to the TouCAN data buffer size. The first eight bytes of data will be transmitted from message buffer 0 and the last eight from message buffer 4. Setting the TouCAN to transmit lowest numbered buffer first, rather than lowest ID first (LBUF bit in CANCTRL1), we are assured proper ordering of our sampled data. Once the QADC has completed the conversion queue, all 40 bytes will be transferred to the TouCAN and the five message buffers enabled together. The TouCAN will then commence arbitration for the bus for each of the five messages in turn and requires no further action from the CPU until all five messages, i.e. 40 bytes, have been transferred. The TouCAN setup is detailed in the software section.

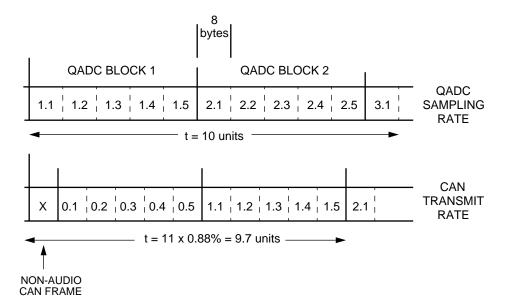

As discussed previously, not all of the available CAN bandwidth will be used. This means that on average the CAN will transmit the data faster than the QADC can deliver it. In theory this means that the TouCAN message buffers will always be empty by the time the QADC has completed its queue, allowing the QADC ISR to transfer all 40 data bytes directly from its result queue to the TouCAN. In practice, there may be brief periods of heavy CAN bus activity, either from additional CAN transmitter nodes or due to retransmission of an error-induced message from our own transmitter.

To compensate for brief periods of additional activity, we shall use a small buffer in RAM which may be used as a temporary store for data

### **Application Note**

from the QADC in the event the TouCAN has not completed its own transfer. A temporary buffer large enough to take the 40 bytes of data from the QADC i.e. five CAN message lengths of eight data bytes each will be sufficient to ensure no audio data is lost as long as there is no more than one additional non-audio CAN message in every ten audio messages. As is shown in Figure 9, when running at 88% bandwidth, one additional non-audio message in every ten will keep us within the available bandwidth limit. Our small buffer will require only simple software control and will protect against data loss when additional but infrequent CAN messages are present on the bus. This mechanism is not suitable when additional data of two or more consecutive messages with high priority appear on the bus. In this situation, all 40 bytes in the buffer would be overwritten by the QADC ISR before the TouCAN could retrieve them and therefor all 40 bytes would be lost. This situation could be avoided by assigning highest priority identifier to the audio data. In our system, the audio data shall be assigned a high priority ID for this reason. In addition, each of the five audio messages from the five message buffers shall be assigned different identifiers. This will give us better visibility in a debug environment and also allows demonstration of the receiver filter mask on the audio output node. The 11-bit ID for message buffer 0 shall be set at 000 i.e. highest possible priority, through to an ID of 004 for message buffer 4. A receive mask shall be used on the receiving side of the bus to filter off the three least significant bits of the ID, thus all five audio message may be received using a single receive ID plus one of the three available 32-bit filter registers. See Section 5.2.5 for explanation of receive filter.

Audio Transfer

Audio Input

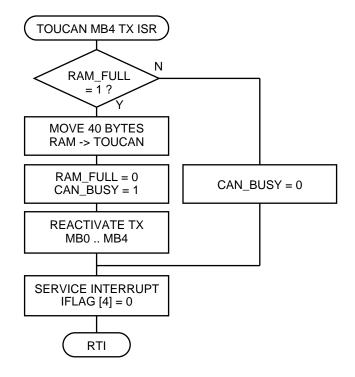

Figure 9 Additional Loading on the CAN Bus

The flowcharts for the QADC and TouCAN ISRs are shown in Figure 10 and Figure 11 respectively. The control of data flow from QADC into either TouCAN or RAM buffer is handled by two flags – CAN\_BUSY and RAM\_FULL as shown. These two routines must be mutually exclusive and this is easily accomplished by assigning both ISRs the same interrupt request level. The TouCAN interrupt should be triggered when all five message buffers are empty, so only the last message buffer, MB4 will be used for interrupt generation.

### **Application Note**

Figure 10 QADC ISR Flowchart

Figure 11 TouCAN Tx ISR Flowchart

Audio Transfer Audio Output

These two ISRs, along with the QADC's queued mechanism and the TouCAN's multiple message buffer structure, completely handle the audio input function of sampling the dual analogue audio wave-forms to transmitting the numerical representation onto the CAN bus. This means that this function is fully interrupt driven and in our system, the main audio input routine becomes a 'do-nothing' loop after performing initialization. In other systems this is significant if audio transfer has to be performed as a background task.

# 5.2 Audio Output

The node at the audio output has to receive all data on the CAN bus and filter off non-audio information. It must then separate left and right channel information and reproduce the original stereo audio signals.

### 5.2.1 Digital to Analogue Converter

To generate the analogue wave-form, an external DAC (Digital to Analogue Converter) IC will be interfaced to the 68376. Serial input DACs are abundant and are less expensive and come in smaller pin packages than a corresponding parallel input DAC. The QSPI offers an ideal interface for a serial DAC and may be configured for most, if not all available. Our selection criteria for a DAC is as follows:

- serial interface for QSPI connection

- dual channel to reproduce left and right stereo

- minimum 8-bit resolution our system currently uses 8-bit sampling, but all 10-bits of the QADC resolution may be implemented in a future revision if CAN bandwidth is better utilized, i.e. by making use of data compression techniques.

- single +5 volt supply

- voltage output drive capable of driving a pair of amplified multimedia speakers

The MAX549 DAC was considered. This is a low cost, dual 8-bit, voltage output, serial input device in 8-pin DIP package. The drawback with this device is its high output impedance and limited 8-bit resolution.

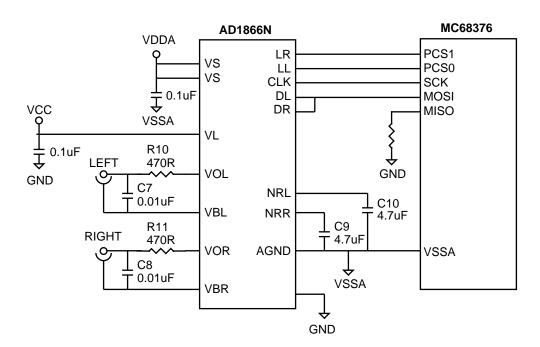

The AD1866 DAC is a more expensive device and comes in a 16-pin package but offers all the features required. It is a dual 16-bit, voltage output, serial input device running from a single +5 volt supply. In addition, this DAC is intended for audio applications and has the advantage of offering audio compatible outputs i.e.  $\pm$  1 volt up to  $\pm$  1mA. This DAC is the one chosen for our application and is examined in more detail in the hardware sections later.

This device requires the serial input to be supplied as a 16-bit serial stream with two's compliment, MSB first format. The QADC offers the digital conversions in three formats – the Left Justified, Signed Result

### **Application Note**

Register or 'LJSRR' is the format suitable in this case and will be used on the audio input node.

### 5.2.2 QSPI Operation

The queuing mechanism on the QSPI will be fully utilized on the output node just as it was on the QADC at the input node. The QSPI will initiate all serial transfers to the DAC, thus will operate in master mode. All 16 command queue entries will be used to perform 16 serial transfers without CPU intervention. In addition, wrap-around mode will be enabled to allow continuous execution of the queued commands. The QSPI output timing will be set to match the input sampling rate of the QADC. This greatly reduces the overhead on the CPU as it does not have to generate the continuous output of data at approximately 58,400 bytes per second – this will be a task for the QSPI. The CPU merely has to ensure that there is always updated audio data within the 16 word queue.

### 5.2.3 QSPI Data Output Timing

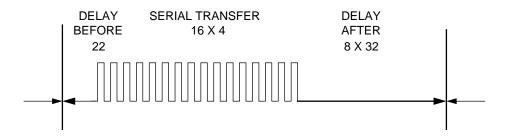

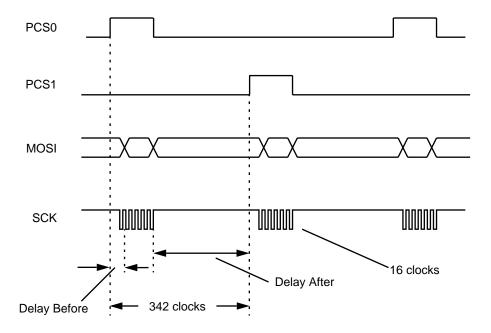

Data has to be serially shifted out at the same continuous rate as the QADC sampling frequency, i.e. 58.4kHz (29.2kHz per channel) i.e. every 342 system clocks. Each serial transfer from the QSPI consists of three components – delay before transfer, the serial transfer itself and a delay after transfer, as shown in Figure 12.

Since the AD1866 DAC requires a fixed 16-bit transfer, the 8-bit digital word must be zero extended. Maximum QSPI operating shift rate of Fsys/4 will be used, thus the number of system clocks for the actual 16-bit shift will be 4 • 16 i.e. 64 system clocks. The delay before transfer is adjustable by single system clocks in the range 1 to 127. The delay after transfer is adjustable in steps of 32 system clocks from 32 to 8192. Choosing delay before of 22 and delay after of 256 results in a total transfer time of 342 system clocks which matches the sampling rate of the QADC.

word serial transfer time = delay before + transfer time + delay after

= 22 + 16 • 4 + 256 = 342 system clocks

transfer frequency = 20MHz / 342 = 58.2 kHz

Audio Transfer Audio Output

Figure 12 QSPI Serial Data Transfer

This setup is performed in function aout\_SPI\_init in file aout.c in the software section.

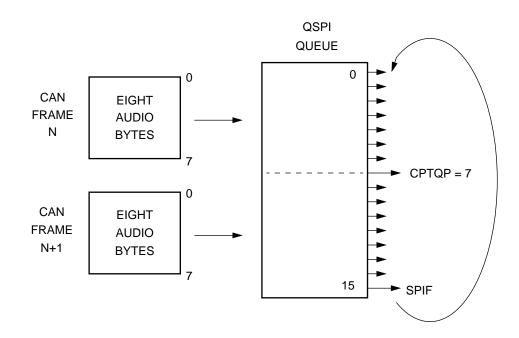

5.2.4 QSPI Data Updating Mechanism Once all 16 command entries in the queue have been executed, the QSPI Finished Flag, SPIF, is asserted. In wrap-around mode, the next data word at the start of the queue is latched into the shift register for transmission almost immediately after the SPIF flag is asserted. For this reason, we cannot simply wait for SPIF then reload 16 new data entries as the QSPI would already have latched old data for transmission from the first word in the queue. The SPIF flag is more suited to serial reception of data when used in wrap-around mode rather than transmission.

To get around this issue, we will load data into the queue in two halves. Referring to Figure 13, when the queue pointer passes the mid-point of the table, i.e. the first eight queued words have been transmitted (CPTQP = 7), the CPU will load eight new data words to the top of the queue. When the QSPI transmits the last word in the queue and SPIF triggers, the CPU will load eight new data words to the bottom of the queue. This two stage loading mechanism allows the QSPI to run continuously since data will be loaded into the queue approximately eight transmit periods before they are due to be transmitted. The CPU latency time after CPTQP = 7 and SPIF is eight transmit times at 58.4kHz per word i.e.

CPU latency for QSPI load =

$$\frac{8}{58400}$$

= 137µs

Since only SPIF can generate an interrupt and not CPTQP = 7, we shall not use interrupts for the QSPI. Instead we shall poll for both of these conditions before loading new data into the QSPI transmit data queue. In another system where polling was not possible, SPIF interrupts could

### **Application Note**

be used to capture the end of queue condition and a timer interrupt could be used to interrupt just after the mid-queue condition.

Figure 13 QSPI Queue Mechanism

The QSPI updating mechanism is shown in Figure 16.

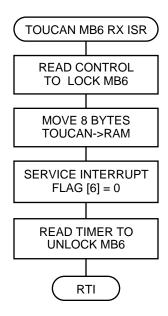

### 5.2.5 Receiving Data from CAN

Receiving the audio data from the CAN bus will be a relatively straight forward process. Although five message buffers are used to transmit audio onto the CAN, this was required only to match the data buffer size of 40 bytes to that of the QADC result buffer. Only one message buffer is required to receive the data from the CAN. This message buffer will use one of the three available mask filter registers to exclude non-audio messages.

Any one of the sixteen available message buffers may be chosen. For our system we will use MB6 which shares the RXGMSK (Receive Global Mask Register) with MB0 – MB13. This shall be set to 0xFF0FFFE i.e. mask out the three bits (MD18–20 correspond to the first three ID bits in standard format) that differ in the five audio IDs so that all five will pass the filter process.

Receive interrupt will be enabled for MB6 by setting bit-6 in the IMASK register. The resulting ISR must take the eight data bytes from MB6 and make them available for the QSPI. As explained previously, we cannot write directly to the QSPI data queue as this can only be done at certain

instances. For this reason, MB6 ISR must move the eight data bytes into a temporary RAM buffer. The source code for this ISR is listed in aout\_MB6\_ISR in file aout.c and is further explained in the software section.

Figure 14 TouCAN Rx ISR Flowchart

5.2.6 Synchronizing Audio Output to Input Since two micro-processors using separate crystal oscillators are used, it is unavoidable that the data output rate will differ slightly from the input sampling rate. Although this slight difference in speed cannot be detected by ear, it will result in gaps in the audio sound that will be audible. If the output rate is slower than the input, then the RAM buffer between TouCAN and QSPI will eventually fill. When this happens, the newly received data must be discarded as there is nowhere to store it. Since the CAN message consists of eight data bytes, data will be lost in blocks of eight bytes at a time. This is equivalent to an audio transmission of 137  $\mu$ s. By discarding this data, the output buffer will recover for a short period then overflow again. Similarly, if the output rate is faster than the input, there will be periods when the QSPI data queue has not been updated with fresh data. Since the QSPI is running in wrap-around mode, it will continue to output data regardless and so will repeat previously transmitted data.

Typical crystal accuracy's are in the region of  $\pm$  30 ppm. In addition, many 68376 systems make use of the internal PLL (phase-locked loop). The long term clock jitter of the resulting clock generated by the 68376 PLL is listed as 0.0625% with 'long term' defined as 500  $\mu$ s. In practice the resulting clock will be much more accurate than this figure, but we

# **Application Note**

shall use these figures for calculating the worst case rate of data loss as follows

worst case data loss rate =  $2 \bullet (PLL \text{ variation} + \text{crystal variation})$

$$= 2 \bullet \left( \frac{0.0625}{100} + 30 \bullet 10^{-6} \right) = 1310 \text{ppm or } 0.131\%$$

At a data rate of 58.4kHz, this equates to a maximum loss of 76 bytes per second.

This loss of data will produce small gaps in the output transmission and would certainly be detected by ear. The effect will depend on how large the variation between the two clock rates actually is, but would manifest itself as noise on the audio signal and must be avoided. The question is how do we synchronize output to input and thus avoid any loss of data? One answer may be to avoid the use of the PLL and select a highly accurate crystal oscillator. This would add cost to the system and would still result in slight differences between the two clock rates.

Another suggestion may be to use one external oscillator and share the clock between both processors. In most systems using CAN bus to communicate between remote nodes, transmission of a 20 MHz clock signal would not be practical.

A final suggestion may be to have the audio output node dynamically adjust the output rate of the QSPI so that there is always new data available within its RAM buffer. This may be achieved without any additional hardware cost other than that of the RAM used to buffer the data at the output node. Our system already has 7.5K bytes of SRAM internal to the 68376 and so we will make use of this technique.

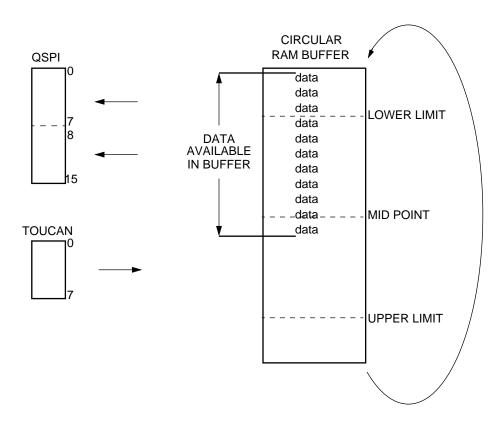

The RAM buffer used is shown in Figure 15. This buffer must be a circular buffer i.e. there is no beginning or end, but instead is a loop where data is continuously pushed in at the top and pulled from the bottom. The TouCAN ISR routine as discussed in the previous section, will take eight data bytes from the receive message buffer MB6 and place them onto the circular RAM buffer at a position defined by a

'data-in' pointer. The CPU will then transfer them into the top or bottom half of the QSPI data queue.

Figure 15 Audio Output Data Buffer

The function of the QSPI control loop is to move data from the RAM buffer to the QSPI and monitor the amount of data within the circular buffer i.e. the distance between the data-in and data-out pointer. The QSPI output rate will then be adjusted so that the amount of data in the buffer is less than an upper limit to avoid having to discard data from the TouCAN, but greater than a lower limit to avoid QSPI being starved of data. An algorithm will be used where three possible QSPI data rates may be selected as follows:

NORMAL – the nominal QSPI speed will be that previously calculated i.e. 342 system clock periods. This will be selected when the circular buffer data size reaches mid-way.

FAST – the fast speed will be selected when the circular buffer data size is greater than the upper limit to allow the QSPI to empty the data at a more rapid rate and will be 341 system clocks.

# **Application Note**

SLOW – the slow speed will be selected when the circular buffer data size is less than the lower limit to allow the TouCAN to build the data stack upwards and avoid a zero data situation and will be 343 system clocks.

These small variations are approximately 0.3% of NORMAL and will do little to effect the quality of our audio output.

The operation of the QSPI on the circular buffer can now be analyzed. After system reset, data size will be zero i.e. less than the lower limit and the QSPI SLOW rate will come into effect. The SLOW speed will be such that the QSPI removes data at a slower rate than the TouCAN places incoming data onto the buffer. The data size will slowly increase until it reaches the mid-point. Now the QSPI NORMAL rate will be selected to restrict the increase of data in the buffer. If the two nodes have identical clock rates, the buffer will remain centered at the mid-point and the NORMAL rate will remain. However, if the input clock is faster than the output, the buffer content will continue to increase, although at a slower rate than before. Eventually the upper limit will be reached and the FAST rate will be selected which will lead to a reduction in buffer content until once again the mid-point is reached. This will result in a continual switching of QSPI output rate between NORMAL and FAST and the buffer size fluctuating between mid-way and the upper limit. This adjustment on audio output rate is very small and will not be audible.

A similar description may be applied when the input clock is slower than the output. Here the QSPI will toggle between NORMAL and SLOW and the buffer size will fluctuate between midway and the lower limit.

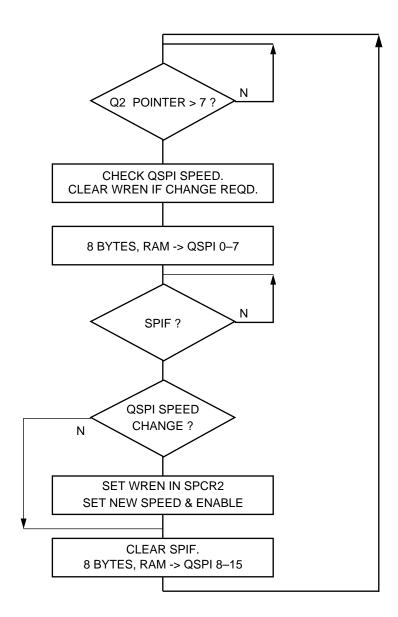

5.2.7 Altering QSPI Output Rate and Buffer Size The minimum adjustment of QSPI output rate is one system clock and can be achieved by adjusting the DSCKL field i.e. the delay before transfer. Since nominal speed is 342 system clocks, adjustment by one clock period to either 341 or 343 gives a QSPI output frequency variation of approximately 0.3%. This is sufficient to override the maximum possible clock difference between the input and output nodes which was shown to be 0.131%.

Choosing a buffer size of 800 bytes will allow us to buffer up to 100 CAN messages of eight data bytes each. As explained previously, the 'data-in' pointer will traverse between either lower limit and mid-point or mid-point and upper limit i.e. QSPI speed will alter after approximately 400 data bytes have accumulated. Since the output node may be running the QSPI at up to 0.3% variation from the input sampling rate, the minimum time for speed alteration may be calculated:

min. QSPI output rate adjustment period =  $\frac{\text{buffer size}}{\text{max. data accumulation rate}}$

Audio Transfer Audio Output

$$\frac{0.5 \bullet 800 \text{ bytes}}{58.4 \text{K bytes/s} \bullet 0.3\%} = 2.3 \text{ seconds}$$

Therefor choosing a buffer size of 800 bytes can cause the QSPI output rate to alter as often as every 2.3 seconds. A smaller buffer may be used i.e. a buffer of 96 bytes would still allow buffering of up to  $\pm$  6 data frames of 8 bytes each. On our system using a 68376 with 7.5K bytes of RAM, 800 bytes is not a problem.

It is not possible to adjust the QSPI output rate at any time. The DSCKL field is within the SPCR1 register which cannot be altered while the QSPI is running or operation will be disrupted. Our algorithm for altering speed will involve the following steps:

- i) clear WREN bit in SPCR2 to disable wrap-around mode so that QSPI output ceases once last word in queue is sent

- ii) wait for transmission of last word by monitoring SPIF in the SPSR (QSPI status register).

- iii) re-enable wrap around mode by setting WREN bit.

- iv) write new value to DSCKL and start continuous transmission by setting SPE, both within SPCR1 register.

These steps must be completed as quickly as possible so that no interruption in audio output is detected. In our software the QSPI is paused only for two or three instructions i.e. approximately one micro-second thus the change over is almost unobservable.

The QSPI updating mechanism is shown in Figure 16 and is coded in file aout.c.

# **Application Note**

**Figure 16 Audio Output Main Routine**

Hardware Design Audio Output

# 6 Hardware Design

The audio hardware consists of biasing and filtering of the analogue audio signal from the audio input (i.e. CD) to the QADC and on the output node, a DAC interface from the QSPI to a set of amplified speakers. The CAN hardware consists of a CAN transceiver IC on both nodes and bus termination resistors at either end of the transmission line.

Figure 17 Hardware Circuitry

# **Application Note**

# 6.1 Audio Input Hardware

Figure 18 Audio In Hardware

The audio output signal from the line out jack on a personal CD player is typically  $\pm$  0.7V maximum. The open-circuit output voltage from the headphone socket may be as high as  $\pm$  1 volt. In both cases, the voltage is centered around 0 volts.

Referring to Figure 18, C1, R1 and R2 provide dc biasing for the audio input signal and center it around Vdd/2 i.e. 2.5V. This circuit is also a high pass filter with cutoff frequency of  $1/2\pi RC$  where R = R1 in parallel with R2. Choosing large values for R1 and R2 prevents the lower audible frequencies being cut off. The cutoff frequency for our component values (C =  $0.1\mu F$ , R =  $235k\Omega$ ) is 7Hz, allowing the audible frequency of 20Hz to pass.

Hardware Design Audio Input Hardware

The second stage of the audio input circuit comprising R3 and C2 is a low pass circuit as recommended for the QADC analogue pins. This low pass filter is designed to filter out any high frequency noise from external digital circuitry or clocks. This particular circuit uses smaller values for R and C than is usually recommended so that cutoff frequency is high enough to prevent attenuation in the audio frequency band. Using R3 =  $100\Omega$  and C2 =  $0.01\mu$ F results in a cutoff frequency of 160 kHz which is high enough to pass upper audio band of 20kHz, yet low enough to filter most of the digital noise which on our system will be around 20 MHz from the system clock.