### **AN1827**

## Programming and Erasing FLASH Memory on the MC68HC908AS60

By Kim Keating, Adeela Gill, and Kazue Kikuchi Body Electronics and Occupant Safety Matt Rutledge Non-Volatile Memory Technology Center

### Introduction

Freescale has released an innovative type of FLASH non-volatile memory (NVM) for its 8-bit M68HC08 Family of microcontrollers. This FLASH technology allows in-circuit reprogrammability over the entire automotive specification range.

In-circuit reprogrammability offers these advantages:

- In-system code revision

- EPROM (erasable programmable read-only memory) replacement as a reusable code development platform

- Quick time to market with one chip for code development and production

- No obsolete inventory as with ROM parts

- Allows for last-minute code changes without waiting for new ROM code lots

### **Application Note**

This application note explains how to use the FLASH on the MC68HC908AS60 and provides example software for program and erase operations. The reprogramming algorithms are written in both M68HC08 assembly code and in C code.

This code is available for download from Motorola's Semiconductor Product Sector's Web site at http://mot-sps.com.

The FLASH topics covered in this application note include:

- Features

- Implementation on Motorola's M68HC08 microcontrollers

- Functional description

- Control and block protect registers

- Charge pump

- Block protection

- Erase operation

- Page program/margin read algorithm

- Frequently asked questions

- Hardware schematic

- Assembly source code

- C source code

### **Features**

The benefits of FLASH on the MC68HC908AS60 include:

Single V<sub>DD</sub> power supply is utilized for program/erase.

This feature simplifies program and erase with respect to EPROM (no high voltage power supply or UV (ultraviolet) oven required), reduces program and erase cycle time, and enables in-circuit reprogrammability.

Application Note Implementation on Motorola's M68HC08 Microcontrollers

- The FLASH manufacturing process is fully compatible with the EEPROM (electrically erasable, programmable read-only memory) process.

- This process compatibility allows the functionality of both FLASH and EEPROM non-volatile memories on the same chip.

- Meets automotive specifications

Unlike many competing microcontrollers with FLASH, this FLASH can operate and meet reliability requirements for the automotive space. The FLASH on the MC68HC908AS60 will read, program, and erase over the -40°C to 125°C temperature range. The specified program/erase endurance and data retention lifetime are valid over the entire temperature range.

- Multiple arrays

Multiple arrays on the MC68HC908AS60 allow code execution out of one array while programming or erasing the other array.

- Smart programming algorithm

Use of the smart programming algorithm ensures minimum program time while still guaranteeing automotive environment operation and data retention.

### Implementation on Motorola's M68HC08 Microcontrollers

The specific FLASH technology found on the MC68HC908AS60 is known as FLASH 2TS, in reference to its 2-transistor source-select bit cell. FLASH 2TS is commonly found on Motorola's M68HC08 Family of microcontrollers, but it is not the exclusive FLASH technology for the HC08 core. The FLASH 2TS technology discussed in this application note is referred to generically as FLASH.

This FLASH technology is available in array sizes between 2 Kbytes and 32 Kbytes. For parts requiring more than 32 Kbytes, multiple arrays of any size between 2 Kbytes and 32 Kbytes, with 2-Kbyte boundaries, can be placed on a chip. Typically, only one charge pump is used on parts with multiple arrays. This constrains program or erase operations to one array at a time, but conserves die area.

### **Application Note**

The FLASH bit cell consists of two transistors in series, referred to as the select-gate and control-gate transistors. The floating gate is associated with the control gate transistor and stores charges which represent the two different data states of the memory. The high threshold condition of the bit cell is the erased state and the low threshold condition is the programmed state. The select gate prevents bit cell leakage of unselected wordlines during read operations when the floating gate is programmed.

Although the size and shape of the array is mostly transparent to the user, it does help when determining the "cared addresses" during the erase algorithm. The term and function of "cared addresses" are explained in the **Erase Operation** of this application note. For now, it is important to know that the cared addresses determine exactly which block will erase during the erase operation.

More importantly, the size and shape of the memory array may alter the size of the programming page. The term page refers to the number of consecutive bytes that are programmed during a page program/margin read operation. On larger memory arrays, like the two arrays found on the MC68HC908AS60, one page equals eight bytes. As the array is scaled down, the page is proportionally scaled to either four, two, or one byte(s). This will affect the programming algorithm that appears later in this application note.

The only other obvious difference in implementation of the FLASH array is the size of the blocks that can be protected against an undesired program or erase operation. Again, this depends on the size of the memory on the microcontroller. Check the appropriate documentation for each specific microcontroller to determine the size of the memory array, the page program size, and the erase block sizes.

Application Note Functional Description

### **Functional Description**

The FLASH memory on the MC68HC908AS60 physically consists of two independent arrays with two bytes of block protection and additional bytes of user vectors. An erased bit reads as a logic 0 and a programmed bit reads as a logic 1. Program and erase operations are facilitated through control bits in memory mapped registers. Details for these operations appear later in this application note.

Memory in the FLASH array is organized into pages within rows. There are eight pages of memory per row with eight bytes per page. The minimum erase block size is a single row, 64 bytes. Programming is performed on a per-page basis, eight bytes at a time. The address ranges for the user memory, control registers, block protect registers, and vectors are listed here.

The FLASH memory map on the MC68HC908AS60 consists of:

- \$0450-\$05FF, FLASH-2 array, 432 bytes

- \$0E00-\$7FFF, FLASH-2 array, 29,184 bytes

- \$8000–\$FDFF, FLASH-1 array, 32,256 bytes

- \$FE0B, FLASH-1 control register, FLCR1

- \$FE11, FLASH-2 control register, FLCR2

- \$FF80, FLASH-1 block protect register, FLBPR1

- \$FF81, FLASH-2 block protect register, FLBPR2

- \$FFDA-\$FFFF, FLASH-1 vector space, 38 bytes

To program the FLASH, each page must be erased before it is programmed. The erase block sizes are found in **Erase Operation**.

The four 64-byte row address boundaries for the MC68HC908AS60 are:

- \$xx00-\$xx3F

- \$xx40-\$xx7F

- \$xx80-\$xxBF

- \$xxC0-\$xxFF

### Application Note

When programming the FLASH, exact program time must be used to program a page. Excessive program time can result in a program disturb condition, in which case an erased bit on the row being programmed becomes unintentionally programmed. Program disturb is avoided by using an iterative program and margin read technique known as the smart programming algorithm. The smart programming algorithm is required whenever programming the FLASH. See Page Program/Margin Read Algorithm.

**NOTE:** A security feature prevents viewing of the FLASH contents.<sup>1</sup>

Programming tools are available from Freescale. Contact a local Freescale representative for more information.

### Control and Block Protect Registers

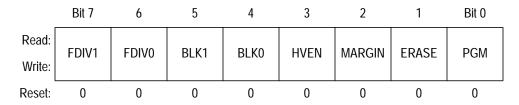

Each FLASH array has two registers that control its operation, the FLASH control register (FLCR) and the FLASH block protect register (FLBPR). See **Figure 1** and **Figure 2**.

Figure 1. FLASH Control Register (FLCR)

There are two FLASH control registers, FLCR1 and FLCR2, for FLASH-1 and FLASH-2 arrays, respectively.

- \$FE0B FLASH-1 control register (FLCR1)

- \$FE11 FLASH-2 control register (FLCR2)

<sup>1.</sup> No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

Application Note Control and Block Protect Registers

### FDIV1 — Frequency Divide Control Bit

This read/write bit together with FDIV0 selects the factor by which the charge pump clock is divided from the bus clock. See **Charge Pump**.

### FDIV0 — Frequency Divide Control Bit

This read/write bit together with FDIV1 selects the factor by which the charge pump clock is divided from the bus clock. See **Charge Pump**.

### BLK1 — Block Erase Control Bit

This read/write bit together with BLK0 allows erasing of blocks of varying sizes. See **Erase Operation** for a description of available block sizes.

### BLK0 — Block Erase Control Bit

This read/write bit together with BLK1 allows erasing of blocks of varying sizes. See **Erase Operation** for a description of available block sizes.

### HVEN — High-Voltage Enable Bit

This read/write bit enables the charge pump to drive high voltages for program and erase operations in the array. HVEN can be set only if either PGM = 1 or ERASE = 1 and the proper sequence for erase or page program/margin read is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

### MARGIN — Margin Read Control Bit

This read/write bit configures the memory for the margin read operation. MARGIN cannot be set if HVEN = 1. MARGIN will automatically clear (MARGIN = 0) if asserted when HVEN = 1.

- 1 = Margin read operation selected

- 0 = Margin read operation unselected

### **Application Note**

ERASE — Erase Control Bit

This read/write bit configures the memory for the erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be set at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

### PGM — Program Control Bit

This read/write bit configures the memory for the program operation. PGM is interlocked with the ERASE bit such that both bits cannot be set at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

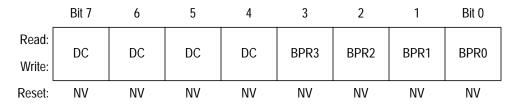

NV — Non-volatile, 1 if programmed, 0 if erased DC — Don't care

Figure 2. FLASH Block Protect Register (FLBPR)

There are two FLASH block protect registers, FLBPR1 and FLBPR2, for FLASH-1 and FLASH-2 arrays, respectively.

- \$FF80 FLASH-1 block protect register (FLBPR1)

- \$FF81 FLASH-2 block protect register (FLBPR2)

BPR3 — Block Protect Register Bit 3

This bit protects the memory contents in the address range:

FLASH-1 \$C000 to \$FFFF or FLASH-2 \$4000 to \$7FFF.

- 1 = Address range protected from erase or program

- 0 = Address range open to erase or program

Semiconductor, Inc

### Freescale Semiconductor, Inc.

Application Note Charge Pump

BPR2 — Block Protect Register Bit 2

This bit protects the memory contents in the address range: FLASH-1 \$A000 to \$FFFF or FLASH-2 \$2000 to \$7FFF.

- 1 = Address range protected from erase or program

- 0 = Address range open to erase or program

BPR1 — Block Protect Register Bit 1

This bit protects the memory contents in the address range: FLASH-1 \$9000 to \$FFFF or FLASH-2 \$1000 to \$7FFF.

- 1 = Address range protected from erase or program

- 0 = Address range open to erase or program

BPR0 — Block Protect Register Bit 0

This bit protects the memory contents in the address range: FLASH-1 \$8000 to \$FFFF or FLASH-2 \$0450 to \$7FFF.

- 1 = Address range protected from erase or program

- 0 = Address range open to erase or program

### **Charge Pump**

The internal charge pump is required for program, margin read, and erase operations of the FLASH.

The charge pump is a dynamic circuit that uses a specific clocking sequence of capacitors and switches to generate voltages higher in magnitude than  $V_{DD}$ . This charge pump design requires a clock frequency range between 1.8 MHz and 2.5 MHz to operate the FLASH correctly. The charge pump clock is derived from the bus clock. The FDIV1 and FDIV0 bits in the FLASH control register are able to divide the internal bus clock by 1, 2, or 4 to generate the charge pump clock. These divide ratios allow enough tolerance for several commonly available crystal frequencies.

See **Table 1** for common divide ratios based upon internal bus frequency.

### **Application Note**

**NOTE:**

When FLASH memory is programmed/erased with the PLL on or in monitor mode, bus frequency is not always the same as the external clock frequency divided by four. Since the charge pump frequency is derived from the bus frequency, confirm the bus frequency being used.

**Table 1. Bus Frequency Divide Ratios for Charge Pump Clock**

| f <sub>Bus</sub> (MHz) | FDIV1 | FDIV0 | Division | f <sub>Pump</sub> (MHz) |

|------------------------|-------|-------|----------|-------------------------|

| 2.000                  | 0     | 0     | 1        | 2.000                   |

| 2.4576                 | 0     | 0     | 1        | 2.4576                  |

| 4.000                  | 0     | 1     | 2        | 2.000                   |

| 4.9152                 | 0     | 1     | 2        | 2.4576                  |

| 8.000                  | 1     | 1     | 4        | 2.000                   |

| 8.400                  | 1     | 1     | 4        | 2.100                   |

NOTE:

If the charge pump frequency is not between 1.8 MHz and 2.5 MHz, Freescale does not guarantee the operation, electrical, or reliability specifications of the FLASH.

The HVEN bit in the FLASH control register enables the charge pump to generate high voltages for program and erase modes. The charge pump also generates a regulated voltage for the margin read mode in the smart programming algorithm. During programming, the HVEN bit should be asserted only for 1 ms to 1.2 ms at a time. (See Figure 8.) Asserting HVEN for longer than 1.2 ms at a time risks program disturb, where an erased bit on the same row becomes unintentionally programmed. Program disturb is a common soft fault and can be recovered by erasing the row and reprogramming using the smart programming algorithm.

Application Note Block Protection

### **Block Protection**

To protect the contents in the FLASH array from being inadvertently programmed or erased by run-away code in the user application, the FLASH block protect register option was implemented. This register is composed of two non-volatile bytes within the FLASH-1 array, with one byte per FLASH array. Once the block protect bits are set in the FLBPR registers, the defined address ranges are protected from being programmed or erased. See **Control and Block Protect Registers** for a description of address ranges.

The FLBPR register itself can be erased or programmed only with an external voltage  $V_{HI}$  on the IRQ pin.  $V_{HI}$  is defined as a voltage between  $V_{DD}$  + 2 V and  $V_{DD}$  + 4 V. Use of the block protect register is an additional measure to prevent inadvertent programming or erasing of FLASH contents in an application.

**NOTE:**

To implement in-system program or erase for a protected area of FLASH, a high voltage signal must be routed to the IRQ pin.

### **Erase Operation**

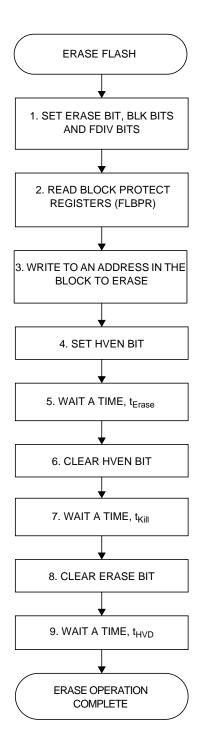

To erase a FLASH array, follow this 9-step procedure. **Figure 3** shows a flowchart of this procedure.

1. Set ERASE = 1, and set the BLK bits and FDIV bits.

ERASE = 1 configures the FLASH memory for an erase operation. The BLK bits determine the erase block size: whole array, half array, 512 bytes or 64 bytes. The FDIV bits determine the charge pump frequency. The frequency should be selected within the range between 1.8 MHz and 2.5 MHz. Refer to **Charge Pump**.

Read the FLASH block protect register.

The block protect registers must be read before high voltage can be enabled. If the desired address set in step 3 is in a protected block, erase will fail.

### **Application Note**

3. Write to any FLASH address within the block address range desired.

The "cared" bits for the FLASH address are latched and used to determine the address range that will be erased. The details are discussed later in this section.

- 4. Set HVEN = 1.

- a. Internal high voltage is applied for erasing.

- 5. Wait for a time, t<sub>Erase</sub>.

t<sub>Frase</sub> is the block erase time.

6. Set HVEN = 0.

Internal high voltage is disabled.

Wait for a time, t<sub>Kill</sub>.

This allows the high voltage to be discharged completely.

8. Set ERASE = 0.

Disable the erase operation.

9. Wait for a time, t<sub>HVD</sub>.

After a time,  $t_{HVD}$ , the memory can be accessed in normal read mode.

**NOTE:** If bulk erase is attempted on a FLASH array where either part or all of the array is block protected, then none of the FLASH memory in that array is erased.

Application Note Erase Operation

Figure 3. FLASH Erase Operation Flowchart

### **Application Note**

Although the overall procedure is relatively simple, step 3 could use some clarification. Since the specified address is any address within the block to erase, the microcontroller must somehow know exactly which memory range to erase. This is where the "cared address" becomes important.

In step 2, the size of the block to erase is set by writing to the BLK bits in the FLCR. **Table 2** shows the various block sizes which can be erased in one erase operation.

Table 2. Erase Block Sizes

| BLK1 | BLK0 | Block Size                | Cared Addresses |

|------|------|---------------------------|-----------------|

| 0    | 0    | Full array: 32 Kbytes     | A15             |

| 0    | 1    | One-half array: 16 Kbytes | A15–A14         |

| 1    | 0    | Eight rows: 512 bytes     | A15–A9          |

| 1    | 1    | Single row: 64 bytes      | A15–A6          |

When an address is specified in step 3, certain address lines are latched pertaining to this block size, and they establish the start and end addresses of the block. The larger the erase block, the smaller the size of the cared address.

For example, if the BLK bits are set such that the erase block size is a single row (BLK0 = BLK1 = 1), and the address \$9AF0 is specified in step 3, then bits 15–6 of \$9AF0 are the "cared addresses." Therefore, the values of these address bits are fixed.

| Hex     |    | 9 A F |    |    |    |    |   |   |   | 0 |   |   |   |   |   |   |

|---------|----|-------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit No. | 15 | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Binary  | 1  | 0     | 0  | 1  | 1  | 0  | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

Cared Addresses

Figure 4. Cared Address Example \$9AF0

As a result, the beginning address of the block which will be erased is:

| Hex     |    | (  | )  |    | A  |    |   |   |   | ( | ) |   | 0 |   |   |   |  |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| Bit No. | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Binary  | 1  | 0  | 0  | 1  | 1  | 0  | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |  |

Cared Addresses

Figure 5. Erase Beginning Address for Example

The end address of the block which will be erased is:

| Hex     |    | Ç  | 9  | A  |    |    |   |   |   | F | = |   | F |   |   |   |  |

|---------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|--|

| Bit No. | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

| Binary  | 1  | 0  | 0  | 1  | 1  | 0  | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

Cared Addresses

Figure 6. Erase End Address for Example

This results in erasing 64 bytes from address \$9AC0 to \$9AFF.

**NOTE:**

All memory arrays are shaped differently, so one row may not equal 64 bytes like on the MC68HC908AS60. Refer to the appropriate documentation for the pertinent device and apply these same principles.

### **Application Note**

### Page Program/Margin Read Algorithm

In the MC68HC908AS60, programming of the FLASH memory is done on a page-by-page basis. A page consists of eight bytes, from addresses \$XXX0 to \$XXX7 or from \$XXX8 to \$XXXF. Therefore, the addresses of the first byte in a page must be \$XXX0 or \$XXX8.

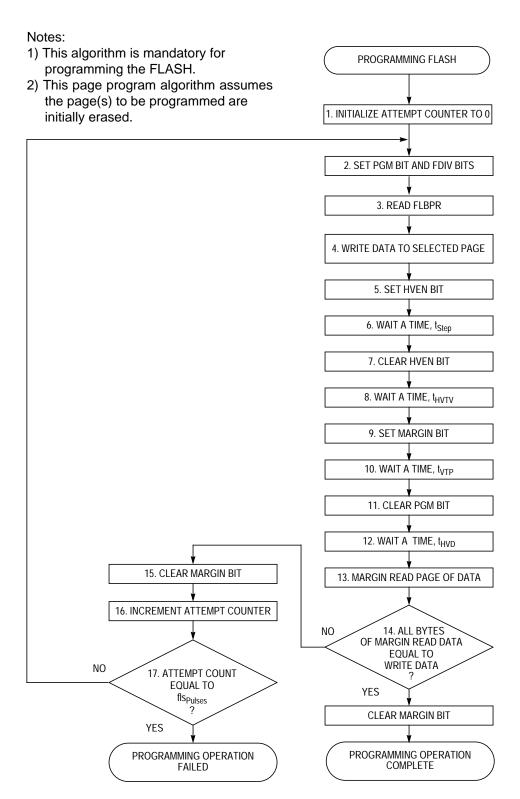

This FLASH memory requires the smart programming algorithm. The smart programming algorithm is defined as an iterative program and margin read sequence. Every page program operation is followed by a margin read until the data is programmed successfully. The margin read step of the smart programming algorithm is used to ensure programmed bits are programmed to sufficient margin for data retention over the device's lifetime.

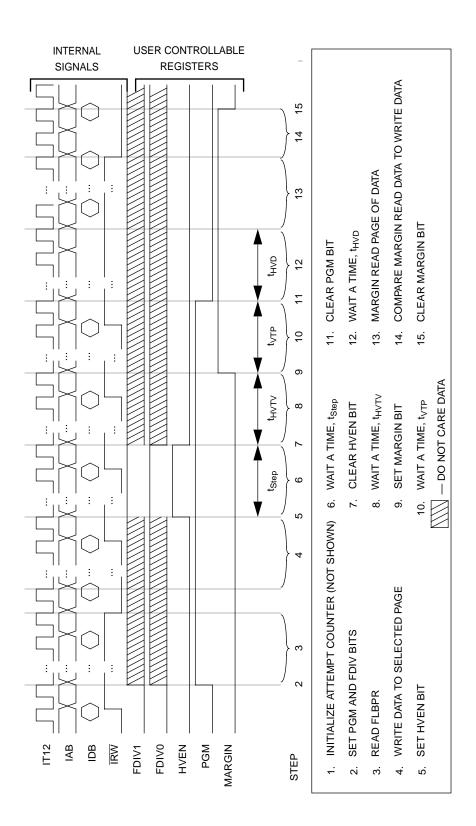

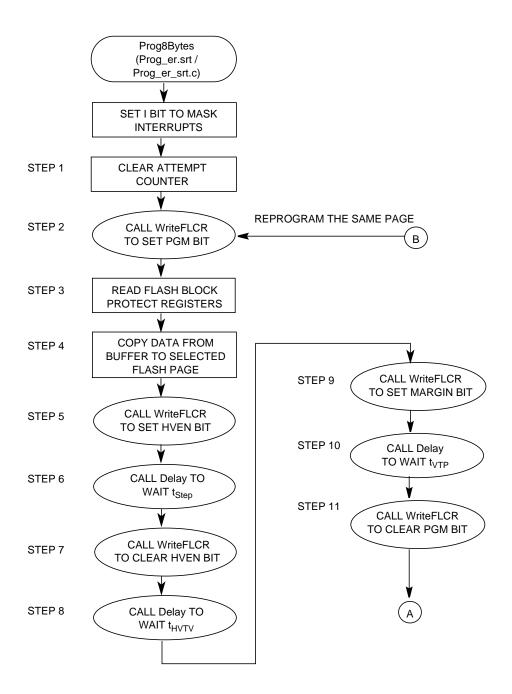

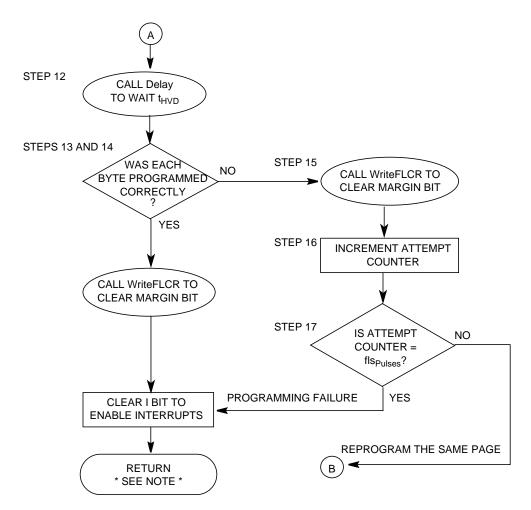

The smart programming algorithm steps are shown here and in the **Figure 7** flowchart.

1. Initialize attempt counter.

The sequence will be attempted until the count reaches fls<sub>Pulses</sub>.

Set PGM = 1 and set FDIV bits.

PGM = 1 configures the FLASH memory for a program operation and enables the latching of the address and data for programming. The FDIV bits determine the charge pump frequency. The frequency should be selected within the range between 1.8 MHz and 2.5 MHz. Refer to **Charge Pump**.

Read the FLASH block protect register.

The block protect register must be read before high voltage can be enabled. If the desired address is in a protected block, the programming will fail.

4. Write data to the page being programmed (typically 8 bytes).

This requires separate write operations for each byte and the addresses of the page must be \$XXX0 to \$XXX7, or \$XXX8 to \$XXXF.

Application Note Page Program/Margin Read Algorithm

Set HVEN = 1.

Internal high voltage is applied for programming.

Wait for a time, t<sub>Step</sub>.

t<sub>Step</sub> is the time high voltage is applied for every program pulse.

7. Set HVEN = 0.

Internal high voltage is disabled.

Wait for a time, t<sub>HVTV</sub>.

Wait for programming voltages to dissipate before margin reading.

9. Set MARGIN = 1.

This configures the FLASH memory for margin read operation.

10. Wait for a time,  $t_{VTP}$ .

Time to discharge the margin read voltage.

11. Set PGM = 0.

This step disables the programming operation.

12. Wait for a time, t<sub>HVD</sub>.

After a time, t<sub>HVD</sub>, the memory can be accessed in normal read mode.

13. Read programmed data (margin read process).

This requires separate read operations for each byte.

14. Compare margin read data with data written in Step 4.

This requires separate read operations for each byte.

15. Clear the MARGIN bit.

Disable the margin read operation.

- 16. Increment attempt counter since programming was not successful.

- 17. If any byte of programmed data does not match the margin read data, then there are two options. If the count is less than the maximum (fls<sub>Pulses</sub>(); return to step 2 to repeat programming of the same page. If the attempt to program count has reached fls<sub>Pulses</sub>, the programming operation has failed.

### **Application Note**

Figure 7. FLASH Smart Programming Algorithm Flowchart

Application Note Page Program/Margin Read Algorithm

Figure 8. Timing Diagram of One Page Program-Margin Read Step in the Smart Programming Algorithm

### **Application Note**

The smart programming algorithm ensures programming data retention and minimum program time and reduces the possibility of program disturb. The margin read operation imposes a more stringent read condition on the bit cell so that long-term data retention is ensured. The operation is the same as the ordinary read operation except the margin bit is set (MARGIN = 1). However, when the margin read operation is executed, data is read automatically with seven additional bus cycles per byte. This additional settling time allows sensing of the lower bit cell current.

The smart programming algorithm also uses multiple short program pulses instead of using one long program pulse. Therefore, whenever the margin read is successful, the page programming is completed even if the program pulses do not reach the maximum. If the program pulses reach the maximum, it means that programming operation has failed.

**NOTE:**

When the COP is enabled, the seven additional cycles of the margin read operation must be considered. Since the COP counter continues to run during the additional cycles, the additional cycles need to be added to the COP feed loop.

**NOTE:**

When the block protect bits in the FLASH block protect register are set, a portion of the memory will be locked so that no further erase or program operation may be performed. However, when high voltage is applied on the IRQ pin, the whole FLASH memory is unprotected. The details are described in the **Control and Block Protect Registers**.

Application Note Frequently Asked Questions

# Freescale Semiconductor, Inc.

### **Frequently Asked Questions**

These questions and answers are designed to help the user with frequent concerns.

Question 1 I cannot program/erase FLASH memory at all. What should I consider to make my program/erase code work?

### Answer 1 Check the following:

- Did you use the smart programming algorithm in your programming code?

The smart programming algorithm ensures that the FLASH is programmed for sufficient data retention and in minimum program time. Furthermore, not following this algorithm can lead to overprogramming, which risks program disturb. The use of the smart programming algorithm is highly recommended. (Refer to Page Program/Margin Read Algorithm.)

- Is each step of the smart programming algorithm (or erase algorithm) performed in the right order?

The sequence of the program and erase operations are interlocked in hardware so only the prescribed order of these operations can occur. However, other non-FLASH operations may occur between the steps shown.

- Is the memory block where you want to program/erase unprotected?

The block protect feature of the FLASH is present to prevent unintentional programming or erasing. The block protect bits must be set such that the memory to be erased or programmed is unprotected. The only way to override the block protect bits is to apply voltage V<sub>HI</sub> on IRQ during the erase and program algorithms. (Refer to Block Protection.)

- Are delay times such as t<sub>Step</sub>, t<sub>Erase</sub>, t<sub>HVD</sub>, etc., within the specification?

Timing is critical to ensure proper FLASH operation. Delay times that are too long or too short can alter the FLASH performance to the point where it does not work or is not reliable. Freescale does

### **Application Note**

not guarantee FLASH performance if the wrong delay times are used.

- Is the correct FLASH register being written to enable erase or program?

- The MC68HC908AS60 has two FLASH arrays with two separate sets of control and block protect registers. Make sure the appropriate register is being addressed. Refer to **Control and Block Protect Registers**.

- Is the maximum pulse value (fls<sub>Pulses</sub>) set correctly according to specification?

Usually, the FLASH will program in fewer than the maximum specified number of program pulses allowed. However, the specification is chosen to ensure that even the worst-case (slowest) bits program by allowing enough programming time. Setting this value lower than the specification may not work all the time. Refer to the electrical specifications in MC68HC908AS60 Advance Information, Freescale document order number

- Is the charge pump frequency correct? The charge pump frequency has to be set between 1.8 MHz and 2.5 MHz. If the bus speed is not between 1.8 MHz and 2.5 MHz, you must set FDIV bits to generate a suitable charge pump frequency. Refer to Charge Pump.

- Is the COP enabled?

If the COP is enabled, make sure that the COP bit is cleared before the COP reset occurs. Remember that in margin read mode, every byte requires seven additional cycles for sensing.

Refer to the Page Program/Margin Read Algorithm.

### Question 2 What is the FLASH charge pump?

MC68HC908AS60/D.

Answer 2 The charge pump is a dynamic (clocked) circuit which generates high voltages internally in the FLASH to program and erase the non-volatile memory.

Application Note Frequently Asked Questions

Question 3 The MC68HC908AS60 FLASH programs one page (eight bytes) at a time. Do I always have to program the entire page?

Answer 3 No, it is not necessary to program the entire page. Addresses which are not programmed are left as they were before the page programming was started. If one page includes reserved bytes, these bytes should not be programmed.

Question 4 Do I have to use the smart programming algorithm?

Answer 4 The use of smart programming algorithm is required. Freescale does not guarantee the performance of the FLASH if this algorithm is not followed. Refer to Page Program/Margin Read Algorithm.

Question 5 During a program/erase process, can I execute an interrupt service or include additional steps?

Answer 5 Unrelated (non-FLASH) steps may be included between steps of the program/erase algorithms as long as the sequence of the steps remains consistent. However, interrupt service routines can cause errors in the program or erase timing and lead to corrupt or missing data in the FLASH. Freescale does not guarantee performance of the FLASH if interrupts are not masked during the program or erase operations.

Question 6 I am executing program/erase code out of one of the memory arrays. Can the same array be programmed/erased?

Answer 6 No.

Question 7 In running the program/erase code in one of the memory arrays, can the other memory array be programmed/erased?

Answer 7 Yes. The MC68HC908AS60 has two FLASH memory arrays. One array can be used for executing code while programming/erasing the other.

### **Application Note**

Question 8 Can I program/erase both FLASH arrays at the same time?

Answer 8 No. The charge pump is shared between both arrays to minimize silicon area and cost. Therefore, only one high voltage FLASH operation (either program or erase) can occur at a time on the MC68HC908AS60.

Question 9 The FLASH specification states that a maximum of eight page program cycles can be done per row between erase cycles. What does this mean?

Answer 9 This specification states that a row (64 bytes of eight pages) should not be programmed more than eight times before erasing. Programming the row in excess of eight times risks inadvertent programming of erased bits. (This type of fault is known as program disturb.) Programming is done on a per-page basis where eight smart programming cycles are used typically to program eight pages, programming the entire row of 64 bytes. If further programming is required on a row after eight program cycles, the row must be erased first before it is programmed again.

- Question 10 When writing eight bytes of data to one page of FLASH memory for programming, does the order of written data matter?

- Answer 10 No, as long as the bytes are written within a page, the data is latched for the programming operation.

- Question 11 I cannot program/erase the FLASH block protect register (FLBPR).

- Answer 11 To program or erase the FLBPR, you must apply V<sub>Hi</sub> on the IRQ pin. Refer to Control and Block Protect Registers.

- Question 12 Does bus frequency affect the programming time? For example, is programming time using 8-MHz bus frequency shorter than using 2-MHz bus frequency?

- Answer 12 FLASH program times using an 8-MHz bus verses a 2-MHz bus have minimal difference.

Application Note Frequently Asked Questions

- Question 13 I'm sending external data serially into the MC68HC908AS60 for programming. How can I speed up this process?

- Answer 13 If you run the MC68HC908AS60 at a higher bus speed, you can improve the non-FLASH overhead during programming.

- Question 14 If I program FLASH with 2-MHz bus frequency, can I read the FLASH with 8-MHz bus frequency without any problems?

- Answer 14 Yes. The FLASH will meet all specifications, including data retention performance, if the FLASH is programmed/erased and used within specification limits.

- Question 15 Why is the maximum number of program attempts (fls<sub>Pulses</sub>) so high?

- Answer 15 This limit is set high to account for the worst case manufacturing process variations, ensuring that the slowest FLASH bit will still program. On average, the page program times are much faster than this worst case limit.

- Question 16 The program/erase operation is not successful in the monitor mode.

- Answer 16 The FLASH memory is protected in the monitor mode to make it difficult for unauthorized users to view the memory contents. Before programming/erasing FLASH, the security feature on the part must be "broken" to view the FLASH contents. When an attempt to break security fails, the FLASH is not addressed during reads and invalid data will be observed. Refer to the monitor ROM section, which describes how to break security, in the MC68HC908AS60 Advance Information, Freescale document order number MC68HC908AS60/D.

- Question 17 I have failed to break security in monitor mode. Can I execute a bulk erase?

- Answer 17 Yes. Bulk erase is the only FLASH operation to attempt when failing to break security in monitor mode. Make sure the block protect feature is not asserted or override it to bulk erase the device.

### **Application Note**

Question 18 In the monitor mode, how I can tell if the break security has been successful?

Answer 18 If the security check was unsuccessful, memory reads will return the same data for every byte read instead of the code or data expected.

Question 19 Do I need to confirm the memory contents after programming the FLASH?

Answer 19 It is recommended that the code used to program the FLASH also include a verification step to ensure the integrity of the data programmed into the FLASH. Some sort of error flag should be set if the data in the FLASH does not agree with what was programmed.

Question 20 A block of memory in the FLASH array is protected by programming the block protect register. When I execute bulk erase without applying high voltage on the IRQ pin, will all of the array, except for the protected block, be erased?

Answer 20 No. If any part of the array being bulk erased is protected, the bulk erase operation is defeated unless high voltage is placed on IRQ.

Question 21 What is the expected lifetime of FLASH memory?

Answer 21 The minimum program/erase endurance and data retention lifetime of the FLASH memory for all conditions is found in *MC68HC908AS60*Advance Information, Freescale document order number MC68HC908AS60/D.

Question 22 What steps can I take to prolong the life of the FLASH memory?

Answer 22 The FLASH memory has a finite program/erase and data retention lifetime. However, the specification shows the minimum lifetime considering the worst case set of conditions applied to the part. In general, the FLASH will last longer if it is used at temperatures much lower than the maximum specified, such as 25°C. The program/erase endurance and data retention of this FLASH memory is worst at 125°C.

Application Note Schematic

Question 23 Can I program/erase/read the FLASH at the maximum temperature

limits continuously for the specified lifetime of the part?

Answer 23 Yes.

Question 24 What modes of operation cause the most noise?

Answer 24 Program and erase modes cause a significant amount of EMI

(electromagnetic interference) and power supply noise due to the high transient current demand of the charge pump. High accuracy ADC (analog-to-digital) conversions may not be possible while the FLASH is

programming or erasing.

### **Schematic**

Figure 9 shows the hardware schematic for the FLASH 2TS.

**Application Note**

## the FLASH block protect registers, high voltage (V<sub>Hi</sub>) must be applied to IRQ. Note: $V_{\rm DD}$ should be applied to IRQ at all times, except when programming the FLASH block protect registers. When programming

Figure 9. Hardware Schematic for Programming and Erasing FLASH 2TS on the MC68HC908AS60

Application Note Assembly Source Code

### **Assembly Source Code**

Sample assembly source code for FLASH programming and erasing are included in this section.

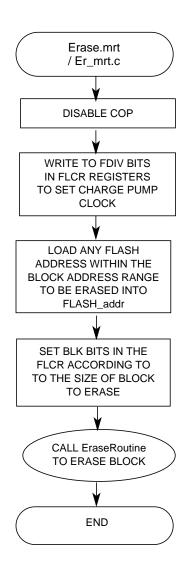

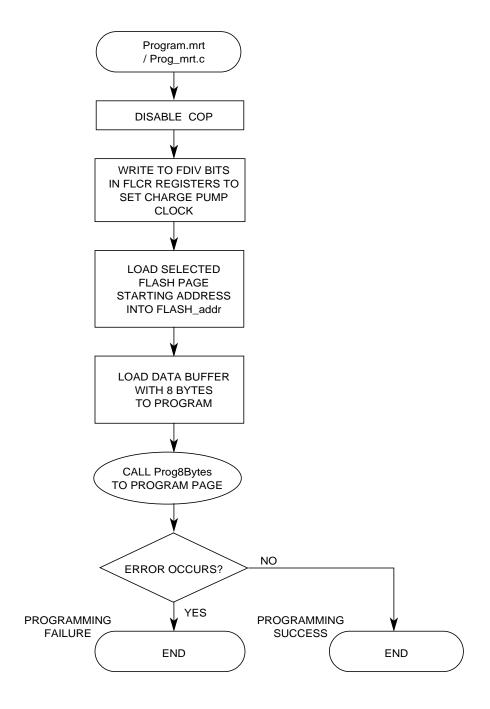

The routines <code>Erase.mrt</code> and <code>Program.mrt</code> are the respective main routines for erasing and programming. Both disable the COP and initialize the charge pump clocks. The main routines also set up the parameters required by the subroutines such as <code>FLASH\_addr</code> and the size of the erase block or the data bytes to be programmed. <code>Erase.mrt</code> can erase a 64-byte, 512-byte, 16-Kbyte, or a 32-Kbyte block of FLASH. <code>Program.mrt</code> programs one page (eight bytes) of FLASH with the data 01, 02, 03, 04, 05, 06, 07, 08. <code>Figure 10</code> and <code>Figure 11</code> are the flowcharts for <code>Erase.mrt</code> and <code>Program.mrt</code>.

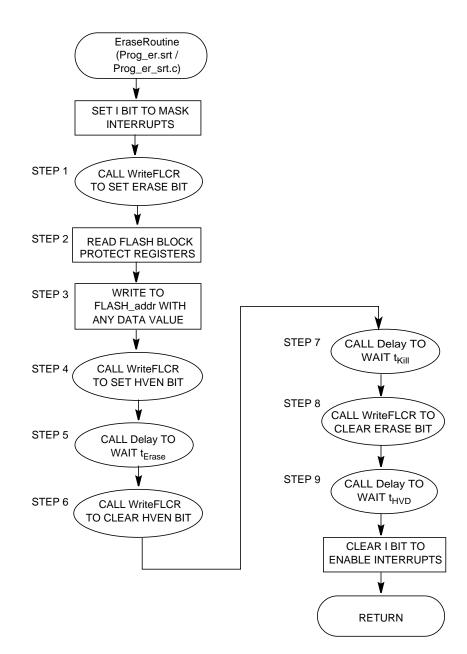

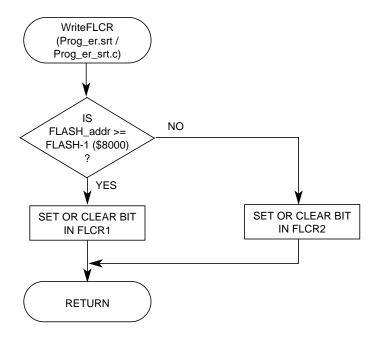

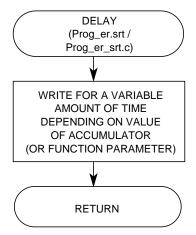

The subroutine <code>EraseRoutine</code> includes the erasing flowchart and is called from <code>Erase.mrt</code>. It calls subroutine <code>WriteFLCR</code> to set or clear various bits in the FLCR register and subroutine <code>Delay</code> to generate the required delays between steps.

Prog8Bytes is the smart programming algorithm subroutine called from Program.mrt. It also uses the WriteFLCR and Delay subroutines. Note that Prog8Bytes can make multiple attempts (up to the value set in fls<sub>Pulses</sub>) to program one page.

The flowcharts for EraseRoutine, Prog8Bytes, WriteFLCR and Delay are Figure 12, Figure 13, Figure 14, and Figure 15, respectively.

NOTE:

$V_{DD}$  should be applied to IRQ at all times, except when programming the FLASH block protect registers. When programming the FLASH block protect registers, flip the switch such that high voltage is applied to IRQ.

### **Application Note**

Figure 10. Erasing Main Routine Flowchart

Application Note Assembly Source Code

Figure 11. Programming Main Routine Flowchart

### **Application Note**

Figure 12. Subroutine EraseRoutine Flowchart

Application Note Assembly Source Code

Figure 13. Subroutine Prog8Bytes Flowchart

### **Application Note**

Note: ACCUMULATOR VALUE (OR RETURNED VALUE) INDICATES THE PROGRAMMING RESULT.

ZERO VALUE = PROGRAMMING SUCCESS

NON-ZERO VALUE = PROGRAMMING FAILURE

Figure 13. Subroutine Prog8Bytes Flowchart (Continued)

Application Note Assembly Source Code

Figure 14. Subroutine WriteFLCR Flowchart

Figure 15. Subroutine Delay Flowchart

### **Application Note**

### **Assembly Source Code**

```

Erase FLASH 2TS Memory on the MC68HC908AS60

Copyright (c)

File Name: Erase.mrt

Current Revision: 1.0

Current Release Level: RP

Current Revision Release Date: 9/6/99

Current Release Written By: Kim Sparks

Freescale Systems Engineering - Austin, TX

Assembled Under: CASM08 (P&E Micro Inc.)

Ver.: 3.06 SLD

Project Folder Name: FLASH_2TS

Part Family Software Routine Works With: HC08

Part Module(s) Software Routine Works With: fls32k_a01

* Routine Size (Bytes):

270

Stack Space Used (Bytes):

* RAM Used (Bytes):

* Global Variables Used:

FLASH_addr

* Subroutine Called:

EraseRoutine, WriteFLCR

* Full Functional Description Of Routine Design:

Erase.mrt is the main routine that demonstrates how to erase different

size blocks of FLASH 2TS memory on the MC68HC908AS60.

*************************

* Freescale reserves the right to make changes without further notice to

any product herein. Freescale makes no warranty, representation or

* guarantee regarding the suitability of its products for any particular

* purpose, nor does Freescale assume any liability arising out of the

* application or use of any product, circuit, and specifically disclaims

* any and all liability, including without limitation consequential or

* incidental damages. "Typical" parameters can and do vary in different

* applications. All operating parameters, including "Typicals" must be

* validated for each customer application by customer's technical experts.

* Freescale does not convey any license under its patent rights nor the

* rights of others. Freescale products are not designed, intended, or

* authorized for use as components in systems intended for surgical

* implant into the body, or other applications intended to support or

* sustain life, or for any other application in which the failure of the

```

Application Note Assembly Source Code

| * may occur. Shoul<br>* intended or unau<br>* Freescale and it<br>* distributors had<br>* and reasonable a<br>* claim of persona<br>* unauthorized use<br>* regarding the de<br>* Freescale symbol<br>* Freescale is an<br>************************************ | Id Buyer protection of the second of the sec | archase or use application, Bus, employees, sinst all claims ees arising out or death associated the such claim alless and anufacture of the stered trademare ortunity/Affirm ex************************************ | on where personal injury or death Freescale products for any such yer shall indemnify and hold ubsidiaries, affiliates, and , costs, damages, and expenses, of, directly or indirectly, any ated with such unintended or eges that Freescale was negligent he part. Freescale and the ks of Freescale Semiconductor, Inc. hative Action Employer.  *********************************** | *****            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|

| NOLIST                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                        |                  |  |  |

| \$INCLUDE                                                                                                                                                                                                                                                       | "H908as6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.frk"                                                                                                                                                                                                               | Equates for all registers and bit; the MC68HC908AS60                                                                                                                                                                                                                                                                                                                                   | s in             |  |  |

| *****                                                                                                                                                                                                                                                           | *****                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | *****                                                                                                                                                                                                                | **********                                                                                                                                                                                                                                                                                                                                                                             | *****            |  |  |

| ****                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Program Speci                                                                                                                                                                                                        | fic Equates                                                                                                                                                                                                                                                                                                                                                                            | ****             |  |  |

| ******                                                                                                                                                                                                                                                          | ******                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | *****                                                                                                                                                                                                                | **********                                                                                                                                                                                                                                                                                                                                                                             | *****            |  |  |

| eraseallrows.                                                                                                                                                                                                                                                   | equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | %0000000                                                                                                                                                                                                             | ;Full array: 32 Kbytes (A15)                                                                                                                                                                                                                                                                                                                                                           |                  |  |  |

| erasehalfrows.                                                                                                                                                                                                                                                  | equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | %00010000                                                                                                                                                                                                            | ;One-half array: 16 Kbytes<br>; (A15 & A14)                                                                                                                                                                                                                                                                                                                                            |                  |  |  |

| erase8rows.                                                                                                                                                                                                                                                     | equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | %00100000                                                                                                                                                                                                            | Eight rows: 512 bytes (A15-A9)                                                                                                                                                                                                                                                                                                                                                         |                  |  |  |

| eraselrow.                                                                                                                                                                                                                                                      | equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | %00110000                                                                                                                                                                                                            | ;Single row: 64 bytes (A15-A6)                                                                                                                                                                                                                                                                                                                                                         |                  |  |  |

|                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                      | * * * * * * * * * * * * * * * * * * * *                                                                                                                                                                                                                                                                                                                                                |                  |  |  |

| ****                                                                                                                                                                                                                                                            | *****                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RAM Variable De                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                        | ****             |  |  |