# AN1906

## MC92600 WarpLink Quad Configuring Unused Channels to Minimize Power

Prepared by: Bob Garvey Design Engineer

#### INTRODUCTION

This application note details how to configure an unused WarpLink Channel to minimize power consumption of this device. Warning: WarpLink is designed to allow word synchronization (32 bit alignment) for all 4 channels. If a channel is not used then word synchronization is not supported for the remaining channels.

#### **1.1 Configuration Requirements**

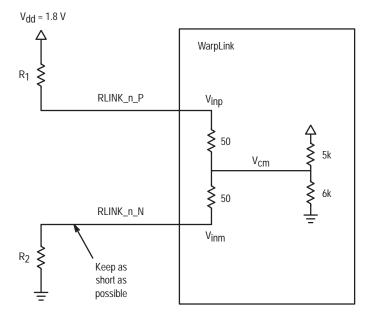

When configuring unused channels for minimizing power consumption, all outputs associated with an unused channel should be left unconnected. All inputs (other than Receiver Link Inputs) should be tied to ground. The Receiver Link Inputs (RLINK\_n\_N and RLINK\_n\_P) should be terminated as shown in Figure 1.

Lower values of R<sub>1</sub> and R<sub>2</sub> improve noise margin (AC power) at the expense of DC power. Higher values of R<sub>1</sub> and R<sub>2</sub> reduce noise margin but save DC power. R1 and R2 must be selected such that  $V_{inp} - V_{inm} \ge 35 \text{mV}$ . This is the minimum voltage difference necessary to maintain adequate noise margins. The best values for R<sub>1</sub> and R<sub>2</sub> are: R<sub>1</sub> = R<sub>2</sub> = 2.2k ohms. This achieves  $V_{inp} - V_{inm} = 38 \text{mV}$ .

Other values will work with slightly more power being drawn as long as the following relationships are met:

$$\frac{V_{dd}}{2} \le V_{cm} \le \frac{2 \cdot V_{dd}}{3}$$

$$\frac{R_2}{2} \le R_1 \le R_2$$

$$R_1 + R_2 \le 4.4k$$

It does not matter which signal is pulled down. The important point is that the other should be pulled up. RLINK\_n\_P may be pulled down and RLINK\_n\_N pulled up. RLINK\_n\_N may be pulled down and RLINK\_n\_P pulled up.

Multiple links may share the same  $R_1$  and  $R_2$  (in parallel) by adjusting  $R_1$  and  $R_2$  according to:

$$R_{1new} = \frac{R_1}{x}$$

$R_{2new} = \frac{R_2}{x}$

where "x" is the number of links sharing  $R_1$  and  $R_2$ .

Figure 1. Unused RLINK Termination

## Freescale Semiconductor, Inc.

Table 1 lists the connections for the inputs and outputs of each unused channel to minimize power. All unused channels must be connected as shown.

| WarpLink Pinout * | Input/Output | Disposition  |  |

|-------------------|--------------|--------------|--|

| XMIT_n_0          | I            | GND          |  |

| XMIT_n_1          | I            | GND          |  |

| XMIT_n_2          | I            | GND          |  |

| XMIT_n_3          | I            | GND          |  |

| XMIT_n_4          | I            | GND          |  |

| XMIT_n_5          | I            | GND          |  |

| XMIT_n_6          | I            | GND          |  |

| XMIT_n_7          | Ι            | GND          |  |

| XMIT_n_K          | I            | GND          |  |

| XMIT_n_IDLE_B     | I            | GND          |  |

| XLINK_n_P         | O (link)     | N/C          |  |

| XLINK_n_N         | O (link)     | N/C          |  |

| RECV_n_0          | 0            | N/C          |  |

| RECV_n_1          | 0            | N/C          |  |

| RECV_n_2          | 0            | N/C          |  |

| RECV_n_3          | 0            | N/C          |  |

| RECV_n_4          | 0            | N/C          |  |

| RECV_n_5          | 0            | N/C          |  |

| RECV_n_6          | 0            | N/C          |  |

| RECV_n_7          | 0            | N/C          |  |

| RECV_n_K          | 0            | N/C          |  |

| RECV_n_9          | 0            | N/C          |  |

| RECV_n_IDLE       | 0            | N/C          |  |

| RECV_n_ERR        | 0            | N/C          |  |

| RECV_n_RCLK       | 0            | N/C          |  |

| RLINK_n_P         | l (link)     | See Figure 1 |  |

| RLINK_n_N         | l (link)     | See Figure 1 |  |

### Table 1: WarpLink Pinout and Termination

\* "n" is a placeholder for the channel identifier "A" through "D".

### Freescale Semiconductor, Inc.

### **1.2 Power Consumption Estimates**

Tables 2 and 3 contain estimated power consumption for various WarpLink configurations assuming the guidelines defined in Section 1.1 of this document are followed.

| Supply | Condition* | 1 active channel | 2 active channels | 3 active channels | 4 active channels |

|--------|------------|------------------|-------------------|-------------------|-------------------|

| 3.3V   | Typical    | 41               | 82                | 123               | 164               |

| 1.8V   | Typical    | 391              | 519               | 648               | 777               |

| Total  | Typical    | 432              | 601               | 771               | 941               |

|        |            |                  |                   |                   |                   |

| 3.3V   | Worst Case | 49               | 98                | 147               | 196               |

| 1.8V   | Worst Case | 453              | 603               | 753               | 902               |

| Total  | Worst Case | 502              | 701               | 900               | 1098              |

### Table 3: Power Estimates (mW) for 10 bit Mode

| Supply | Condition* | 1 active channel | 2 active channels | 3 active channels | 4 active channels |

|--------|------------|------------------|-------------------|-------------------|-------------------|

| 3.3V   | Typical    | 48               | 96                | 144               | 192               |

| 1.8V   | Typical    | 391              | 519               | 648               | 777               |

| Total  | Typical    | 439              | 615               | 792               | 969               |

|        |            |                  |                   |                   |                   |

| 3.3V   | Worst Case | 57               | 114               | 171               | 228               |

| 1.8V   | Worst Case | 453              | 603               | 753               | 902               |

| Total  | Worst Case | 510              | 737               | 924               | 1130              |

$^{\ast}$  Typical power conditions for 3.3V logic is 3.3V, 40°C, and typical process

Typical power conditions for 1.8V logic is 1.8V, 40°C, and typical process

Worst Case power conditions for 3.3V logic is 3.6V, 105°C, and best case process

Worst Case power conditions for 1.8V logic is 1.95V, 105°C, and best case process

**Freescale Semiconductor, Inc.**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

Technical Information Center: 1-800-521-6274

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan. 81–3–3440–3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

HOME PAGE: http://www.motorola.com/semiconductors/

For More Information On This Product, Go to: www.freescale.com