# Interfacing the MSC8101 UPM to an External Dual-Port SRAM

By lantha Scheiwe

The MSC8101 is a powerful DSP that integrates the StarCore<sup>TM</sup> SC140 DSP core, a communications processor module (CPM) for network interfacing, and a system interface unit (SIU). The SIU memory controller includes three user-programmable machines (UPMs). Each UPM controls access to a wide array of memory types, including both synchronous and asynchronous SRAM and DRAM memories.

This application note describes the interface between the MSC8101 UPM and the Cypress CY7C028V dual-port asynchronous SRAM (DPRAM). After a review of UPM and DPRAM basics, it considers the signals interfacing between the two devices as well as the timing diagrams for the interface. The section on the UPM programming model includes programming specifics for the DPRAM interface. After you program the memory controller, you can access the memory in multiple ways from the MSC8101.

#### **CONTENTS**

| 1     | UPM and DPRAM Basics                    |     |

|-------|-----------------------------------------|-----|

| 2     | UPM Programming Model                   |     |

| 2.1   | UPM RAM Array                           |     |

| 2.2   | Timing Interface Diagrams               |     |

| 2.2.1 | MSC8101 to DPRAM Single Read Timing     |     |

| 2.2.2 | MSC8101 to DPRAM Single Write Timing    |     |

| 2.2.3 | DPRAM Semaphore Read After Write Timing | ′   |

| 2.2.4 | Timing Diagram of Read with BUSY        | . 8 |

| 2.3   | RAM Words                               | 1(  |

| 2.3.1 | Read                                    | 1.  |

| 2.3.2 | Write                                   | 14  |

| 2.3.3 | Exception                               | 14  |

| 2.4   | UPM Registers                           | 14  |

| 2.5   | RAM Array Programming                   | 10  |

| 2.6   | Memory Controller Bank Registers        |     |

| 2.6.1 | BRx Register                            |     |

| 2.6.2 | ORx Register                            |     |

| 3     | UPM Programming Steps                   |     |

| 4     | Memory Access                           |     |

| 5     | Conclusions                             |     |

| 6     | References                              | 2   |

|       |                                         |     |

## 1 UPM and DPRAM Basics

The UPM allows the system designer to program the memory controller signal activity to each 1/2 or 1/4 PowerPC system bus clock cycle so that the UPM can interface to any number of different types of memories. The MSC8101 has three UPMs: UPMA, UPMB, UPMC. UPMC is used on the internal PowerPC local bus to control the interface to internal SRAM from the PowerPC local bus. UPMC is initialized at boot-up so that non-core resources can access the internal SRAM. UPMC is not available for use with external devices. However, UPMA and UPMB are available for access to external devices on the PowerPC system bus.

The Cypress CY7C028V Dual-Port RAM (DPRAM) is an asynchronous SRAM that allows two independent devices to gain access to the SRAM simultaneously through its dual ports. The memory device has two independent sets of address, data, and control lines that allow two devices to access a memory cell. Because the two accessing devices are independent, each can have a unique hardware interface and timing requirement. DPRAM devices include extra functions not found in a standard SRAM that allow one accessing device to lock out a memory cell from the other accessing device if required.

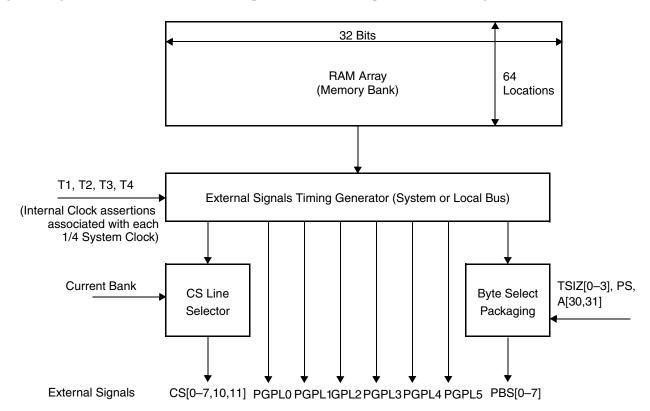

The UPM has six unique signals, PGPL[0–5]. The UPM can use other signals associated with memory accesses as well, including chip selects and byte selects. **Figure 1** shows the UPM signals. The PGPL4 signal requires special programming because it can function as an input when it is not required as a PGPL signal.

Figure 1. UPM Signals

The MSC8101 UPM signal actions are highly programmable. The chip select ( $\overline{CS}$ ) and byte select ( $\overline{PBS}$ ) signals shown in **Figure 1** are programmable to a PowerPC bus 1/4 clock cycle. The General-Purpose Line (PGPL[0–5]) signals are programmable to the 1/2 clock cycle.

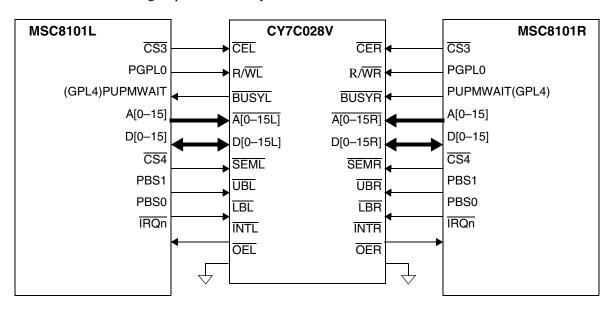

Because the CY7C028V is a dual-ported SRAM, **Figure 2** shows how two MSC8101 devices can connect to the SRAM device. The DPRAM uses standard SRAM signals such as chip-select (chip enable), read/write, address, and data lines to define the interface as well as some signals that are required to service the dual ports. Chip-select 4 (<del>CS4</del>) connects to the semaphore (<del>SEM</del>) signal from the DPRAM. Through this signal, the DPRAM controls which device accesses a semaphore latch at a given time. The semaphore latches are memory-mapped separately via the <del>CS4</del> signal, and the DPRAM device handles semaphore priority. Therefore, the semaphore can keep two DSP devices from over-writing a specific memory location.

Figure 2. Dual MSC8101 UPM to CY7C028V DPRAM Signal Interface

The PUPMWAIT signal is the UPM PGPL4 signal that allows an external device to freeze the external signals until the PUPMWAIT signal is released (or the system bus reaches a time-out condition). Therefore, the DPRAM can assert its  $\overline{\text{BUSY}}$  signal and hold the MSC8101 transaction until the memory location is released and the MSC8101 writes to the desired location. Upper byte ( $\overline{\text{UB}}$ ) and Lower byte ( $\overline{\text{LB}}$ ) signals on the DPRAM connect to the MSC8101 byte select (PBS[0–1]) signals. Therefore, both 8-bit and 16-bit accesses are possible. The DPRAM can generate an interrupt to the MSC8101 via the  $\overline{\text{IRQ}}$  signal.

## 2 UPM Programming Model

This section discusses the various modules within the UPM and registers that must be programmed to implement a UPM transaction. **Section 3**, *UPM Programming Steps*, on page 19 lists the UPM programming steps.

## 2.1 UPM RAM Array

Each UPM has a memory bank designated for programming it. This memory bank is called the UPM RAM array and is not memory-mapped but is instead programmed through a sequence of register writes. Six types of memory accesses can be programmed: single read, burst read, single write, burst write, refresh, and exception. Each access is allotted a designated amount of space within the RAM array. **Table 1** lists the starting addresses in the RAM array for each access type. These addresses are used in programming the Machine Mode Register, which is discussed later.

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

| Table 1  | UPM Routine   | Ctart   | Addrocene |

|----------|---------------|---------|-----------|

| Table L. | UPIVI BOUIINE | e Start | Addresses |

| UPM Routine               | Routine Start Address |

|---------------------------|-----------------------|

| Read single-beat (RSS)    | 0x00                  |

| Read burst (RBS)          | 0x08                  |

| Write single-beat (WSS)   | 0x18                  |

| Write burst (WBS)         | 0x20                  |

| Refresh timer (PTS)       | 0x30                  |

| Exception condition (EXS) | 0x3C                  |

Because the DPRAM is an SRAM without burst capabilities, the burst read and burst write access types do not require programming. Also, the refresh access is not required. **Section 2.3**, *RAM Words*, on page 10 describes the steps for programming the applicable access types in the RAM array. The RAM array is programmed with RAM words that define signal interface timing at each 1/4 bus clock. Examples of this are given in **Section 3**, *UPM Programming Steps*, on page 19.

## 2.2 Timing Interface Diagrams

Creating timing diagrams of the memory interface access types makes the UPM programming procedure easier. Since the UPM signals are programmable to 1/2 and 1/4 clock cycles, it helps to refer to the completed timing diagrams when determining the programming for the access types. Therefore, creating the timing diagrams is the first step in programming the UPM RAM array. The MSC8101 PowerPC system bus operates at a maximum speed of 100 MHz. A 15 ns access time DPRAM is specified for this timing analysis. The following diagrams are discussed here:

- Single Read Timing

- Single Write Timing

- Semaphore Read after Write Timing

- Read with BUSY

## 2.2.1 MSC8101 to DPRAM Single Read Timing

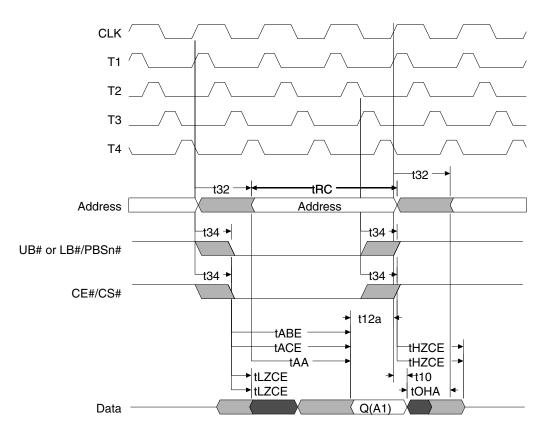

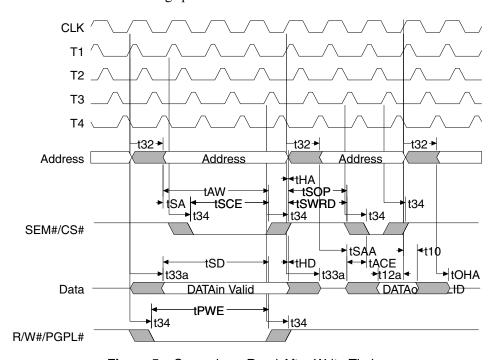

Figure 3 shows the timing diagram for the read cycle. Table 2 shows the parameters related to these timing specifications. Notice that the UPM allows programming of the PGPLn, PBSn, and CSn lines for each 1/4 or 1/2 clock cycle. Because of this, derived clocks for each 1/4 clock cycle are shown (Tn). Also, MSC8101 output timings are rated for 50 pf. Timings based on a 50 pf load are appropriate for a single DPRAM device on the PowerPC system bus. However, if a multi-device system is sharing the PowerPC system bus, it is important to analyze capacitive loading on the bus and choose the timings appropriately.

In the following timing diagrams all timings with numerical names are MSC8101 timings derived from information in the MSC8101 data sheet. Timings with alphabetical names are specified timings for the Cypress DPRAM and can be found in the data sheet for this device. The diagrams should be developed with these data sheets in hand. The "#" notation used with the signal names to the left of the diagram is a convention used to show

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

<sup>1.</sup> An application note entitled *Using DSP56300 Interactive Timing Diagrams* (AN1834) is available on the Freescale website. This application note describes using TimingDesigner from Chronology to evaluate interface timings. Refer to this application note if you are unfamiliar with timing analysis or the TimingDesigner tool.

low assertion. Therefore, UB# is the same as  $\overline{\text{UB}}$ . TimingDesigner does not support overlines on their text, so the "#" notation is used instead. Signal names to the left of the "/" are the DPRAM signal names. Signal names to the right are the associated MSC8101 signal names.

Figure 3. Single Read Cycle Timing

Table 2. Single Read Cycle Timing Parameters

| Ro | w | Name             | Min | Max | Comment                                             |

|----|---|------------------|-----|-----|-----------------------------------------------------|

| 1  | V | DSP_Name         |     |     | Freescale MSC8101 Digital Signal Processor          |

| 2  | ٧ | MEMORY_Name      |     |     | Cypress CY7C028V Dual-Port Static RAM 64kx16, 15ns  |

| 3  | V | Doc_Reference1   |     |     | MSC8101 Advance Information, Rev 0.5                |

| 4  | ٧ | Doc_Reference2   |     |     | Preliminary CY7C027V/028V Data Sheet                |

| 5  | ٧ | Mode_Description |     |     | UPM Single Read to Dual-Port SRAM, 15ns access time |

| 12 | С | tRC              | 15  |     | Read Cycle Time                                     |

| 13 | D | tLZCE            | 3   |     | CE low to low Z                                     |

| 14 | D | tLZCE            | 3   |     | CE low to low Z                                     |

| 15 | G | tOHA             | 3   |     | Output hold from address change                     |

| 16 | D | tAA              |     | 15  | Address to data valid                               |

| 17 | D | tACE             |     | 15  | CE low to data valid                                |

| 18 | D | tABE             |     | 15  | Byte enable access time                             |

| 19 | D | tHZCE            |     | 10  | CE high to high Z                                   |

| 20 | D | tHZCE            |     | 10  | CE high to high Z                                   |

#### Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

| Table 2. Single Re | ead Cycle Timing | Parameters ( | (Continued) |

|--------------------|------------------|--------------|-------------|

|--------------------|------------------|--------------|-------------|

| Ro | Row Name Min Max |         | Max      | Comment |                                             |  |  |  |  |

|----|------------------|---------|----------|---------|---------------------------------------------|--|--|--|--|

| 21 | С                | t10 0.5 |          |         | SIU hold                                    |  |  |  |  |

| 22 | С                | t12a    | 12a 4.55 |         | Data bus in normal mode, input_DLLin, setup |  |  |  |  |

| 23 | D                | t32     | 0.5      | 8.5     | ADD/ADD_atr/CI/GBL/WT/output_DLLin          |  |  |  |  |

| 24 | D                | t34     | 0.5      | 5.5     | memc_signals/DLE,V_CKL                      |  |  |  |  |

| 25 | D                | t34     | 0.5      | 5.5     | memc_signals/DLE,V_CKL                      |  |  |  |  |

| 26 | D                | t34     | 0.5      | 5.5     | memc_signals/DLE,V_CKL                      |  |  |  |  |

| 27 | D                | t34     | 0.5      | 5.5     | memc_signals/DLE,V_CKL                      |  |  |  |  |

## 2.2.2 MSC8101 to DPRAM Single Write Timing

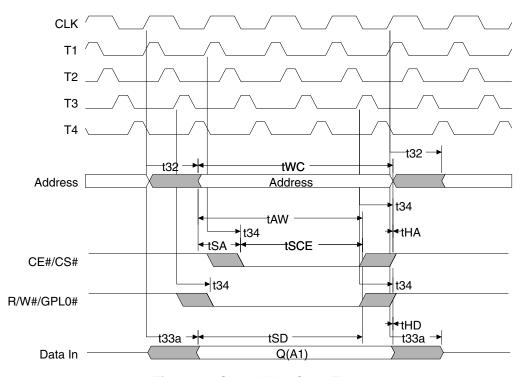

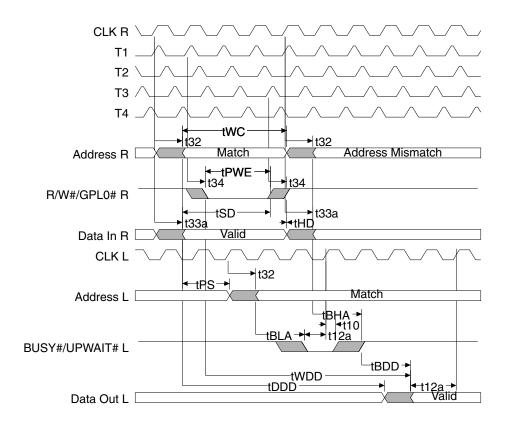

**Figure 4** shows the timing diagram for the write cycle. Following the diagram, **Table 3** shows the parameters related to these timing specifications.

Figure 4. Single Write Cycle Timing

Table 3. Single Write Cycle Timing Parameters

| Ro | Row Name Min Max Margin |                  | Margin | Comment |                                                      |  |  |  |

|----|-------------------------|------------------|--------|---------|------------------------------------------------------|--|--|--|

| 1  | V                       | DSP_Name         |        |         | Freescale MSC8101 Digital Signal Processor           |  |  |  |

| 2  | V                       | MEMORY_Name      |        |         | Cypress CY7C028V Dual-Port Static RAM 64kx16, 15ns   |  |  |  |

| 3  | V                       | Doc_Reference1   |        |         | MSC8101 Advance Information, Rev 0.5                 |  |  |  |

| 4  | V                       | Doc_Reference2   |        |         | Preliminary CY7C027V/028V Data Sheet                 |  |  |  |

| 5  | ٧                       | Mode_Description |        |         | UPM Single Write to Dual-Port SRAM, 15ns access time |  |  |  |

| 6  | ٧                       | Aliases          | ·      |         |                                                      |  |  |  |

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

| Ro | ow | Name | Min | Max | Margin | Comment                            |

|----|----|------|-----|-----|--------|------------------------------------|

| 12 | С  | tWC  | 15  |     | <17,>  | Write Cycle Time                   |

| 13 | С  | tAW  | 12  |     | <15,>  | Address valid to write end         |

| 14 | С  | tSCE | 12  |     | <8,>   | Write pulse width                  |

| 15 | С  | tSA  | 0   |     | <2,>   | Address set-up to write start      |

| 16 | С  | tSD  | 10  |     | <17,>  | Data set-up to write end           |

| 17 | С  | tHD  | 0   |     | <0,>   | Data hold from write end           |

| 18 | С  | tHA  | 0   |     | <0,>   | Address hold from write end        |

| 19 | D  | t32  | 0.5 | 8.5 |        | ADD/ADD_atr/CI/GBL/WT/output_DLLin |

| 20 | D  | t34  | 0.5 | 5.5 |        | memc_signals/DLE,V_CKL             |

| 21 | D  | t33a | 0.5 | 8.5 |        | Data bu, output_DLLin s            |

| 22 | D  | t34  | 0.5 | 5.5 |        | memc_signals/DLE,V_CKL             |

| 23 | D  | t34  | 0.5 | 5.5 |        | memc_signals/DLE,V_CKL             |

Table 3.

Single Write Cycle Timing Parameters (Continued)

## 2.2.3 DPRAM Semaphore Read After Write Timing

**Figure 5** shows the timing diagram for the semaphore read after write cycle. Following the diagram, **Table 4** shows the parameters related to these timing specifications.

Figure 5. Semaphore Read After Write Timing

Notice that this is a chip-select controlled write so it varies slightly from the associated diagram shown in the CY7C028V data sheet.

Table 4. Semaphore Read After Write Timing Parameters

| Ro | w | Name             | Min  | Max | Margin  | Comment                                                  |

|----|---|------------------|------|-----|---------|----------------------------------------------------------|

| 1  | ٧ | DSP_Name         |      |     |         | Freescale MSC8101 Digital Signal Processor               |

| 2  | ٧ | MEMORY_Name      |      |     |         | Cypress CY7C028V Dual-Port Static RAM 64kx16, 15ns       |

| 3  | ٧ | Doc_Reference1   |      |     |         | MSC8101 Advance Information, Rev 0.5                     |

| 4  | ٧ | Doc_Reference2   |      |     |         | Preliminary CY7C027V/028V Data Sheet                     |

| 5  | ٧ | Mode_Description |      |     |         | UPM, Semaphore Read after Write timing, 15ns access time |

| 12 | С | tAW              | 12   |     | <15,>   | Address valid to write end                               |

| 13 | С | tSCE             | 12   |     | <8,>    | CE# low to write end                                     |

| 14 | С | tSD              | 10   |     | <17,>   | Data set-up to write end                                 |

| 15 | С | tHA              | 0    |     | <0,>    | Address hold from write end                              |

| 16 | С | tPWE             | 12   |     | <18,>   | Write pulse width                                        |

| 17 | С | tHD              | 0    |     | <0,>    | Data hold from write end                                 |

| 18 | С | tSOP             | 10   |     | <5,>    | SEM flag update pulse (OE or SEM)                        |

| 19 | С | tSWRD            | 5    |     | <10,>   | SEM flag write to read time                              |

| 20 | С | tACE             |      | 15  | <,7>    | CE low to data valid                                     |

| 21 | С | tSA              | 0    |     | <2,>    | Address set-up to write start                            |

| 22 | D | tOHA             | 3    |     |         | Output hold from address change                          |

| 23 | D | tSAA             |      | 15  |         | SEM address access time                                  |

| 24 | С | t10              | 0.5  |     | <3,>    | SIU hold                                                 |

| 25 | С | t12a             | 4.55 |     | <1.95,> | Data bus in normal mode, input_DLLin, setup              |

| 26 | D | t32              | 0.5  | 8.5 |         | ADD/ADD_atr/CI/GBL/WT/output_DLLin                       |

| 27 | D | t33a             | 0.5  | 8.5 |         | Data bu, output_DLLin s                                  |

| 28 | D | t34              | 0.5  | 5.5 |         | memc_signals/DLE,V_CKL                                   |

| 29 | D | t34              | 0.5  | 5.5 |         | memc_signals/DLE,V_CKL                                   |

| 30 | D | t34              | 0.5  | 5.5 |         | memc_signals/DLE,V_CKL                                   |

| 31 | D | t34              | 0.5  | 5.5 |         | memc_signals/DLE,V_CKL                                   |

| 32 | D | t34              | 0.5  | 5.5 |         | memc_signals/DLE,V_CKL                                   |

## 2.2.4 Timing Diagram of Read with BUSY

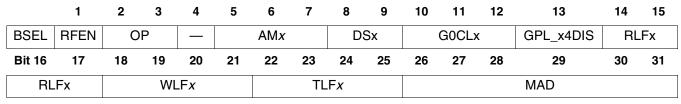

The DPRAM BUSY signal connects to the MSC8101 PUPMWAIT signal, which is sampled on the falling edge of the MSC8101 bus clock signal. To enable PUPMWAIT, set the Machine Mode Register bit 13, MxMR[13] and set UPM RAM words, bits 18 and 19, to 1. Setting bit 18 directs the MSC8101 to sample the data bus at the rising edge of T3. Setting bit 19 directs the MSC8101 to freeze an external signal logical value if the PUPMWAIT signal is detected. **Figure 6** shows the timing diagram for the read cycle with BUSY. **Table 5** shows the parameters related to these timing specifications.

Figure 6. Timing Diagram of Read with BUSY

Table 5. Timing Parameters of Read with BUSY

| Ro | w | Name             | Min  | Max | Margin                               | Comment                                           |  |  |  |  |

|----|---|------------------|------|-----|--------------------------------------|---------------------------------------------------|--|--|--|--|

| 1  | ٧ | DSP_Name         |      |     |                                      | Freescale MSC8101 Digital Signal Processor        |  |  |  |  |

| 2  | ٧ | MEMORY_Name      |      |     |                                      | Cypress CY7C028V Dual-Port Static RAM 64kx16, 15r |  |  |  |  |

| 3  | ٧ | Doc_Reference1   |      |     |                                      | MSC8101 Advance Information, Rev 0.5              |  |  |  |  |

| 4  | ٧ | Doc_Reference2   |      |     | Preliminary CY7C027V/028V Data Sheet |                                                   |  |  |  |  |

| 5  | ٧ | Mode_Description |      |     |                                      | UPM, Timing of Read with BUSY, 15ns access time   |  |  |  |  |

| 12 | С | tWC              | 15   |     | <17,>                                | Write Cycle Time                                  |  |  |  |  |

| 13 | С | tPWE             | 12   |     | <8,>                                 | Write pulse width                                 |  |  |  |  |

| 14 | С | tSD              | 10   |     | <17,>                                | Data set-up to write end                          |  |  |  |  |

| 15 | С | tHD              | 0    |     | <0,>                                 | Data hold from write end                          |  |  |  |  |

| 16 | С | tPS              | 5    |     | <9.5,>                               | Port set-up for priority                          |  |  |  |  |

| 17 | D | tBLA             |      | 15  |                                      | BUSY low from address match                       |  |  |  |  |

| 18 | D | tBHA             |      | 15  |                                      | BUSY high from address mismatch                   |  |  |  |  |

| 19 | D | tBDD             |      | 15  |                                      | BUSY high to data valid                           |  |  |  |  |

| 20 | D | tDDD             |      | 25  |                                      | Write data valid to read data valid               |  |  |  |  |

| 21 | D | tWDD             |      | 30  |                                      | Write pulse to data delay                         |  |  |  |  |

| 22 | С | t10              | 0.5  |     | <2.5,>                               | SIU hold                                          |  |  |  |  |

| 23 | С | t12a             | 4.55 |     | <9.45,>                              | Data bus in normal mode, input_DLLin, setup       |  |  |  |  |

| 24 | С | t12a             | 4.55 |     | <1.95,>                              | All other pins, input_DLLin, setup                |  |  |  |  |

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

Table 5. Timing Parameters of Read with BUSY (Continued)

| Ro | Row Name |                                               | Min | Max | Margin                             | Comment                            |

|----|----------|-----------------------------------------------|-----|-----|------------------------------------|------------------------------------|

| 25 | D        | 0.5 8.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0 |     |     | ADD/ADD_atr/CI/GBL/WT/output_DLLin |                                    |

| 26 | D        | 0.5 8.5                                       |     | 8.5 |                                    | ADD/ADD_atr/CI/GBL/WT/output_DLLin |

| 27 | D        | t33a                                          | 0.5 | 8.5 |                                    | Data bu, output_DLLin s            |

| 28 | D        | t34                                           | 0.5 | 5.5 |                                    | memc_signals/DLE,V_CKL             |

| 29 | D        | t34                                           | 0.5 | 5.5 |                                    | memc_signals/DLE,V_CKL             |

## 2.3 RAM Words

Once the timing diagrams for each access type are defined, the UPM signals can be programmed based on those diagrams. The timing for each signal is defined by the RAM word for each cycle of the access. The RAM word, shown in **Figure 7**, is a 32-bit microinstruction stored in one of 64 locations in the RAM array. It specifies timing for signals controlled by the UPM.

|           | 1    | 2     | 3     | 4    | 5    | 6    | 7    | 8  | 9  | 10 11 | 12   | 13   | 14   | 15   |

|-----------|------|-------|-------|------|------|------|------|----|----|-------|------|------|------|------|

| CST1      | CST2 | CST3  | CST4  | BST1 | BST2 | BST3 | BST4 | G  | DL | G0H   | G1T1 | G1T3 | G2T1 | G2T3 |

| Bit<br>16 | 17   | 18    | 19    | 20   | 21   | 22   | 23   | 24 | 25 | 26 27 | 28   | 29   | 30   | 31   |

| G3T1      |      | G4T1/ | G4T3/ | 1    |      |      |      |    |    |       |      |      |      | LAST |

Figure 7. RAM Word

**Table 6** describes the RAM word fields.

Table 6. RAM Word Bit Descriptions

|               |                                                                                                                                                                                     |          | •                                                                                                                   |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name          | Description                                                                                                                                                                         | Settings |                                                                                                                     |  |  |  |  |

| <b>CST1</b> 0 | Chip-Select Timing 1 Defines the state of CS during clock phase 1.                                                                                                                  | 0        | At the rising edge of T1 $\overline{\text{CS}}$ is zero.  At the rising edge of T1 $\overline{\text{CS}}$ is one.   |  |  |  |  |

| CST2          | Chip-Select Timing 2 Defines the state of CS during clock phase 2.                                                                                                                  | 0        | At the rising edge of T2 $\overline{\text{CS}}$ is zero.  At the rising edge of T2 $\overline{\text{CS}}$ is one.   |  |  |  |  |

| <b>CST3</b> 2 | Chip-Select Timing 3 Defines the state of CS during clock phase 3.                                                                                                                  | 0<br>1   | At the rising edge of T3 $\overline{\text{CS}}$ is zero.  At the rising edge of T3 $\overline{\text{CS}}$ is one.   |  |  |  |  |

| <b>CST4</b> 3 | Chip-Select Timing 4 Defines the state of CS during clock phase 4.                                                                                                                  | 0        | At the rising edge of T4 $\overline{\text{CS}}$ is zero.<br>At the rising edge of T4 $\overline{\text{CS}}$ is one. |  |  |  |  |

| BST1<br>4     | Byte-Select Timing 1 Defines the state of PBS during clock phase 1. The final value of the PBS lines depends on the values of BRx[PS], the TSIZ lines, and A[30–31] for the access. | 0        | At the rising edge of T1 PBS is zero.  At the rising edge of T1 PBS is one.                                         |  |  |  |  |

| <b>BST2</b> 5 | Byte-Select Timing 2 Defines the state of PBS during clock phase 2. The final value of the PBS lines depends on the values of BRx[PS], TSIZx, and A[30–31] for the access.          | 0        | At the rising edge of T2 PBS is zero.  At the rising edge of T2 PBS is one.                                         |  |  |  |  |

| <b>BST3</b> 6 | Byte-Select Timing 3 Defines the state of PBS during clock phase 3. The final value of the PBS lines depends on the values of BRx[PS], TSIZx, and A[30–31] for the access.          | 0        | At the rising edge of T3 PBS is zero. At the rising edge of T3 PBS is one.                                          |  |  |  |  |

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

Table 6. RAM Word Bit Descriptions (Continued)

| Name                | Description                                                                                                                                                                | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>BST4</b> 7       | Byte-Select Timing 4 Defines the state of PBS during clock phase 4. The final value of the PBS lines depends on the values of BRx[PS], TSIZx, and A[30–31] for the access. | O At the rising edge of T4 PBS is zero.  At the rising edge of T4 PBS is one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>G0L</b><br>8–9   | General-Purpose Line 0 Lower Defines the state of PGPL0 during phases 1–2.                                                                                                 | <ul> <li>The value of PGPL0 at the rising edge of T1 is as defined in MxMR[G0CL].</li> <li>The value of the PGPL0 line at the rising edge of T1 is zero.</li> <li>The value of the PGPL0 line at the rising edge of T1 is one.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>G0H</b><br>10–11 | General-Purpose Line 0 Higher Defines the state of PGPL0 during phase 3–4.                                                                                                 | <ul> <li>The value of PGPL0 at the rising edge of T3 is as defined in MxMR[G0CL].</li> <li>The value of the PGPL0 line at the rising edge of T3 is zero.</li> <li>The value of the PGPL0 line at the rising edge of T3 is one.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>G1T1</b> 12      | General-Purpose Line 1 Timing 1 Defines the state of PGPL1 during phase 1–2.                                                                                               | O At the rising edge of T1 PGPL1 is zero.  At the rising edge of T1 PGPL1 is one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>G1T3</b><br>13   | General-Purpose Line 1 Timing 3 Defines the state of PGPL1 during phase 3–4.                                                                                               | <ul><li>0 At the rising edge of T3 PGPL1 is zero.</li><li>1 At the rising edge of T3 PGPL1 is one.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>G2T1</b> 14      | General-Purpose Line 2 Timing 1 Defines the state of PGPL2 during phase 1–2.                                                                                               | <ul><li>0 At the rising edge of T1 PGPL2 is zero.</li><li>1 At the rising edge of T1 PGPL2 is one.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>G2T3</b><br>15   | General-Purpose Line 2 Timing 3 Defines the state of PGPL2 during phase 3–4.                                                                                               | <ul><li>0 At the rising edge of T3 PGPL2 is zero.</li><li>1 At the rising edge of T3 PGPL2 is one.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>G3T1</b> 16      | General-Purpose Line 3 Timing 1 Defines the state of PGPL3 during phase 1–2.                                                                                               | O At the rising edge of T1 PGPL3 is zero.  At the rising edge of T1 PGPL3 is one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>G3T3</b> 17      | General-Purpose Line 3 Timing 3 Defines the state of PGPL3 during phase 3–4.                                                                                               | O At the rising edge of T3 PGPL3 is zero.  At the rising edge of T3 PGPL3 is one.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G4T1/<br>DLT3<br>18 | General-Purpose Line 4 Timing 1/Delay Time 2 Function is determined by MxMR[PGPLx4DIS].                                                                                    | If MxMR defines PUPMWAITx/PGPL_x4 as an output (PGPL_x4), this bit functions as <b>G4T1</b> :  0 The value of the PGPL4 line at the rising edge of T1 is zero.  1 The value of the PGPL4 line at the rising edge of T1 is one.  If MxMR[PGPLx4DIS] = 1, PUPMWAITx is chosen and this bit functions as <b>DLT3</b> .  0 In the current word, indicates that the data bus should be sampled at the rising edge of T1 (if a read burst or a single read service is executed).  1 In the current word, indicates that the data bus should be sampled at the rising edge of T3 (if a read burst or a single read service is executed). |

Table 6. RAM Word Bit Descriptions (Continued)

| Name                 | Description                                                                                                                                                                                                                                                                                                                    | Settings                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>G4T3/ WAEN</b> 19 | General-Purpose Line 4 Timing 3/Wait Enable Function depends on the value of MxMR[PGPLx4DIS].                                                                                                                                                                                                                                  | If MxMR[PGPLx4DIS] = 0, <b>G4T3</b> is selected.  O The value of the PGPL4 line at the rising edge of T3 is zero.  1 The value of the PGPL4 line at the rising edge of T3 is one.  If MxMR[PGPLx4DIS] = 1, <b>WAEN</b> is selected.  O The PUPMWAITx function is disabled.  1 A freeze in the external signals logical value occurs if the external WAIT signal is asserted. This condition lasts until WAIT is deasserted. |

| <b>G5T1</b> 20       | General-Purpose Line 5 Timing 1 Defines the state of PGPL5 during phase 1–2.                                                                                                                                                                                                                                                   | O At the rising edge of T1 PGPL5 is zero.  At the rising edge of T1 PGPL5 is one.                                                                                                                                                                                                                                                                                                                                           |

| <b>G5T3</b> 21       | General-Purpose Line 5 Timing 3 Defines the state of PGPL5 during phase 3–4.                                                                                                                                                                                                                                                   | <ul><li>0 At the rising edge of T3 PGPL5 is zero.</li><li>1 At the rising edge of T3 PGPL5 is one.</li></ul>                                                                                                                                                                                                                                                                                                                |

| <b>REDO</b> 22–23    | Redo Current RAM Word                                                                                                                                                                                                                                                                                                          | <ul> <li>Normal operation.</li> <li>The current RAM word is executed twice.</li> <li>The current RAM word is executed three times.</li> <li>The current RAM word is executed four times.</li> </ul>                                                                                                                                                                                                                         |

| <b>LOOP</b> 24       | Loop The first RAM word in the RAM array where LOOP is one is recognized as the loop start word. The next RAM word where LOOP is one is the loop end word. RAM words between the start and end are defined as the loop. The number of times the UPM executes this loop is defined in the corresponding loop field of the MxMR. | <ul> <li>The current RAM word is not the loop start word or loop end word.</li> <li>The current RAM word is the start or end of a loop.</li> </ul>                                                                                                                                                                                                                                                                          |

| <b>EXEN</b> 25       | Exception Enable                                                                                                                                                                                                                                                                                                               | <ul> <li>The UPM continues executing the remaining RAM words.</li> <li>The current RAM word allows a branch to the exception pattern after the current cycle if an exception condition is detected.</li> </ul>                                                                                                                                                                                                              |

| AMX<br>26–27         | Address Multiplexing Determines the source of A[0–31] at the rising edge of T1 (single-MCS8101 mode only).                                                                                                                                                                                                                     | <ul> <li>A[0–31] is the non-multiplexed address. For example, column address.</li> <li>Reserved.</li> <li>A[0–31] is the address requested by the internal master multiplexed according to MxMR[AMx]. For example, row address.</li> <li>A[0–31] is the contents of MAR. Used, for example, during SDRAM mode initialization.</li> </ul>                                                                                    |

| <b>NA</b><br>28      | Next Address  Determines when the address is incremented during a burst access. The value of NA is relevant only when the UPM serves a burst-read or burst-write request. NA is reserved under other patterns.                                                                                                                 | <ul> <li>The address increment function is disabled.</li> <li>The address is incremented in the next cycle.</li> </ul>                                                                                                                                                                                                                                                                                                      |

| <b>UTA</b> 29        | UPM Transfer Acknowledge Indicates assertion of PSDVAL, sampled by the bus interface in the current cycle.                                                                                                                                                                                                                     | PSDVAL is not asserted in the current cycle.     PSDVAL is asserted in the current cycle.                                                                                                                                                                                                                                                                                                                                   |

|  | Table 6. | RAM Word Bit Descriptions (Continued) |

|--|----------|---------------------------------------|

|--|----------|---------------------------------------|

| Name | Description                                                                                                                                                                                                                                                    |   | Settings                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TODT | Turn-On Disable Timer                                                                                                                                                                                                                                          | 0 | The disable timer is turned off.                                                                                                                            |

| 30   |                                                                                                                                                                                                                                                                | 1 | The disable timer for the current bank is activated preventing a new access to the same bank (when controlled by the UPMs) until the disable timer expires. |

| LAST | Last                                                                                                                                                                                                                                                           | 0 | The UPM continues executing RAM words.                                                                                                                      |

| 31   | If this bit is set, it is the last RAM word in the program.  When the LAST bit is read in a RAM word, the current  UPM pattern terminates and the highest priority pending  UPM request (if any) is serviced immediately in the  external memory transactions. | 1 | The service to the UPM request is done.                                                                                                                     |

After the RAM words for each cycle of each access type are determined, the RAM array can be programmed. The following sections give the RAM word values for each access type to DPRAM and the MSC8101 code to program the RAM words into the UPM RAM array.

**Note:** PUPMWAIT does not appear in the timing diagrams shown in **Section 2.2**, but it is programmed in the RAM words. This is because its functionality must be enabled for the PGPL4 signal, but as shown in **Figure 7**, this functionality does not have specific clock cycle timing such as is required for the other PGPL and  $\overline{CS}$  signals.

#### 2.3.1 Read

**Figure 3** shows that the single read cycle is a 3-cycle access (from the first address transition until the next address transition is three PowerPC system bus clock cycles). Therefore, three RAM words are required, one for each cycle of the memory access. For each RAM word, the programmer is accounting for signal activity at every 1/4 clock of the system bus clock (T1, T2, T3, T4). **Table 1** shows that these RAM words are programmed at offset 0x00 in the RAM array.

- Single Read Cycle RAM word 1: 0x00F03040

CS and PBS signals are asserted at the beginning of the access, and are programmed to 0 starting from

- T1. PGPL0 remains unasserted for a READ cycle. PGPL4 is programmed to operate as PUPMWAIT. Exceptions are enabled for each cycle of the READ access.

- Single Read Cycle RAM word 2: 0x00F03040

- $\overline{\text{CS}}$  and  $\overline{\text{PBS}}$  signals remain asserted during the second clock cycle of the read access, and remain programmed to 0. PGPL0 remains unasserted for the entire READ cycle. PGPL4 is programmed to operate as PUPMWAIT.

- Single Read Cycle RAM word 3: 0x33F03041

CS3 and BS3 signals are deasserted at T3. PGPL4 is programmed as PUPMWAIT. This is the last RAM word for the single read access.

#### 2.3.2 Write

**Figure 4** shows the timing interface for the single write. The single write access is a 4 cycle access, so four RAM words are required to define the write interface. **Table 1** shows that these RAM words are programmed at offset 0x18 in the RAM array.

- Single write cycle RAM word 1: 0xEEE03040

Program CS3, PBS3, and PGPL0 (R/W) signals to remain unasserted until T3. PGPL4 is programmed as PUPMWAIT.

- Single write cycle RAM word 2: 0x00A03040

Signals remain asserted throughout second cycle of access. PGPL4 still acts as PUPMWAIT.

- Single write cycle RAM word 3: 0x00A03040

Same as previous RAM word.

- Single write cycle RAM word 4: 0x33B03041

CS3, PBS3, and PGPLO become unasserted at T3. PGPL4 acts as PUPMWAIT. This is the last RAM word for the single write access.

#### 2.3.3 Exception

An exception access can be programmed, depending on the requirements for the memory interface. **Table** shows that these RAM words are programmed at offset 0x3C in the RAM array.

• Exception cycle RAM word 1: 0xFF000001. Deassert <del>CS3</del> and PBS3 signals and end access.

## 2.4 UPM Registers

Besides the RAM words programmed in the UPM RAM array and BR and OR registers, two other UPM registers, the Memory Data Register (MDR) and the Machine *x* Mode Registers (MxMR) are used when the UPM is programmed. The MDR contains data written to or read from the RAM array for UPM READ or WRITE commands. MDR must be set up before a WRITE command is issued to the UPM. The MDR is a 32-bit register that holds the memory data information. Data to be written into the RAM array when a WRITE command is supplied to the UPM should be placed in the MDR before the write access is initiated.

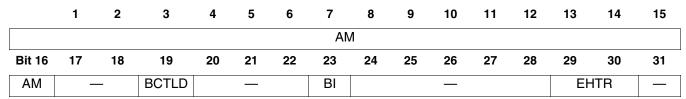

The MxMR, shown in **Figure 8**, contain the configuration for the UPMs. The configuration includes selecting the bus that the memory is assigned to, specifying whether refresh is required, and specifying the multiplex information used primarily for access to DRAMs. Also, this register defines how many times looping RAM words should be repeated. When programming the RAM array, you inform the UPM that it is being programmed at a given RAM array address by setting the Command Opcode bits (OP) to the RAM array access function and the Machine Address (MAD) bits to the address in the RAM array being accessed.

Figure 8. Machine x Mode Registers (MxMR)

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

**Table 7** describes MxMR bits.

Table 7. Machine x Mode Registers (MxMR) Bit Descriptions

| Name                  | Description                                                                                                                                                         | Bit Settings                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BSEL<br>0             | <b>Bus Select</b> Assigns banks that select UPMx to the PowerPC system or local bus.                                                                                | Banks that select UPMx are assigned to the system bus.     Banks that select UPMx are assigned to the local bus.                                                                                                                                                                                                                 |  |  |  |  |

| RFEN                  | Refresh Enable                                                                                                                                                      | 0 Refresh services are not required                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 1                     |                                                                                                                                                                     | Refresh services are required                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| <b>OP</b> 2–3         | Command Opcode  Determines the command executed by the UPMx when a memory access hit a UPM assigned bank.                                                           | <ul> <li>00 Normal operation.</li> <li>01 Write to array. On the next memory access that hits a UPM assigned bank, write the contents of the MDR into the RAM location to which MAD points. After the access, the MAD field is automatically incremented.</li> <li>10 Read from array. On the next memory access that</li> </ul> |  |  |  |  |

|                       |                                                                                                                                                                     | hits a UPM assigned bank, read the contents of the RAM location to which MAD points into the MDR. After the access, the MAD field is automatically incremented  11 Run pattern. On the next memory access that hits                                                                                                              |  |  |  |  |

|                       |                                                                                                                                                                     | a UPM assigned bank, run the pattern written in the RAM array. The pattern run starts at the location to which MAD points and continues until the LAST bit is set in the RAM.                                                                                                                                                    |  |  |  |  |

| <b>AMx</b><br>5–7     | Address Multiplex Size                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| <b>DS</b> x 8–9       | Disable Timer Period                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| <b>G0CLx</b><br>10–12 | General Line 0 Control  Determines which address line can be output to the PGPL0 pin when the UPMx is selected to control the memory access.                        | 000 A12 001 A11 010 A10 011 A9 100 A8 101 A7 110 A6 111 A5                                                                                                                                                                                                                                                                       |  |  |  |  |

| GPL_x4DI<br>S<br>13   | GPL_4 Output Line Disable Determines whether the PUPMWAIT/GTA/PGPL_4 pin behaves as an output line controlled by the corresponding bits in the UPMx array (PGPL4x). | O PUPMWAIT/GTA/PGPL_x4 behaves as PGPL_4. UPMx[G4T4/DLT3] is interpreted as G4T4. The UPMx[G4T3/WAEN] is interpreted as G4T3.  PUPMWAIT/GTA/PGPL_x4 behaves as PUPMWAIT. UPMx[G4T4/DLT3] is interpreted as DLT3. UPMx[G4T3/WAEN] is interpreted as WAEN.  Note: After a system reset, PGPL_x4DIS = 1.                            |  |  |  |  |

Table 7. Machine x Mode Registers (MxMR) Bit Descriptions (Continued)

| Name                | Description                                                                                                                                                          |      | Bit Settings                  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------|

| RLFx                | Read Loop Field                                                                                                                                                      | 0001 | The loop is executed 1 time   |

| 14–17               | Determines the number of times a loop defined in                                                                                                                     | 0010 | The loop is executed 2 times  |

|                     | the UPMx executes for a burst- or single-beat read pattern or when MxMR[OP] = 11 (RUN                                                                                |      |                               |

|                     | command)                                                                                                                                                             | 1111 | The loop is executed 15 times |

|                     |                                                                                                                                                                      | 0000 | The loop is executed 16 times |

| WLFx                | Write Loop Field                                                                                                                                                     | 0001 | The loop is executed 1 time   |

| 18–21               | · · · · · · · · · · · · · · · · · · ·                                                                                                                                |      | The loop is executed 2 times  |

|                     | the UPMx executes for a burst- or single-beat write pattern.                                                                                                         |      |                               |

|                     |                                                                                                                                                                      | 1111 | The loop is executed 15 times |

|                     |                                                                                                                                                                      | 0000 | The loop is executed 16 times |

| TLFx                | Refresh Loop Field                                                                                                                                                   | 0001 | The loop is executed 1 time   |

| 22–25               | Determines the number of times a loop defined in the UPMx executes for a refresh service pattern.                                                                    | 0010 | The loop is executed 2 times  |

|                     | the OPINIX executes for a refresh service pattern.                                                                                                                   |      |                               |

|                     |                                                                                                                                                                      | 1111 | The loop is executed 15 times |

|                     |                                                                                                                                                                      | 0000 | The loop is executed 16 times |

| <b>MAD</b><br>26–31 | Machine Address RAM address pointer for the command executed. This field is incremented by 1 each time the UPM is accessed and the OP field is set to WRITE or READ. |      |                               |

#### **RAM Array Programming** 2.5

When the MxMR register is programmed to "write to array" mode (MxMR[OP]=01), any access to the memory space defined by the Base Register (BR) and Option Register (OR) causes the data currently residing the Memory Data Register (MDR) to be placed in the UPM RAM array at the address defined by the MxMR:MAD bits. Section 3, UPM Programming Steps, on page 19 details the code required for each step of programming the MSC8101 for a UPM interface to DPRAM

#### **Memory Controller Bank Registers** 2.6

The Option Register (OR) and Base Register (BR) define the memory address in the MSC8101 memory map and general memory controller functions.

#### **BRx Register** 2.6.1

The base registers (BR0-7, 10, 11) contain the base address and address types that the memory controller uses to compare the address bus value with the current address accessed. Notice that there are no BR8 and BR9 registers. These two banks are reserved on the MSC8101. Each register also includes a memory attribute and selects the machine for memory operation handling. **Figure 9** shows the BRx register format.

|        | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11    | 12  | 13 | 14 | 15 |

|--------|----|----|----|----|----|----|----|----|----|----|-------|-----|----|----|----|

|        |    |    |    |    |    |    |    | ВА |    |    |       |     |    |    |    |

| Bit 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27    | 28  | 29 | 30 | 31 |

| BA     | _  |    | Р  | S  | DE | CC | WP |    | MS |    | EMEMC | ATC | MC | DR | V  |

Figure 9. Base Registers (BRx)

**Table 8** describes BRx fields.

Table 8. BRx Bit Descriptions

| Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                               | Settings                                                                                                                                                          |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>BA</b><br>0–16 | Base Address The upper 17 bits of each base address register are compared to the address on the address bus to determine if the bus master is accessing a memory bank controlled by the memory controller.  BRx[BA] is used with ORx[BSIZE].                                                                                                                                                                              |                                                                                                                                                                   |

| <b>PS</b> 19–20   | Port Size Specifies the port size of this memory region.                                                                                                                                                                                                                                                                                                                                                                  | 01 8-bit<br>10 16-bit<br>11 32-bit<br>00 64-bit                                                                                                                   |

| <b>DECC</b> 21–22 | Data Error Correction and Checking Specifies the method for data error checking and correction.                                                                                                                                                                                                                                                                                                                           | <ul> <li>Data errors checking disabled</li> <li>Normal parity checking</li> <li>Read-modify-write parity checking</li> <li>ECC correction and checking</li> </ul> |

| <b>WP</b> 23      | Write Protect Can restrict write accesses within the address range of a BR. An attempt to write to this address range while WP = 1 can cause TEA to be asserted by the bus monitor logic (if enabled) which terminates the cycle. When WP is set, the memory controller does not assert CSx and PSDVAL on write cycles to this memory bank. TESCR1[WP] or L_TESCR1[WP] is set if a write to this memory bank is attempted | <ul> <li>Read and write accesses are allowed</li> <li>Only read access is allowed</li> </ul>                                                                      |

| MS<br>24–26       | Machine Select Specifies machine select for the memory operations handling and assigns the bank to the PowerPC system bus if GPCM or SDRAM are selected. If UPMx is selected, the bus assignment is determined by MxMR[BSEL].                                                                                                                                                                                             | 000 GPCM— system bus 001 GPCM—local bus 010 SDRAM— system bus 011 Reserved 100 UPMA 101 UPMB 110 UPMC 111 Reserved                                                |

| <b>EMEMC</b> 27   | External MEMC Enable  Overrides MSEL and assigns the bank to the PowerPC system bus. When this bit is set, the external memory controller is expected to assert AACK, TA, and PSDVAL.                                                                                                                                                                                                                                     | Accesses are handled by the memory controller according to MSEL     Accesses are handled by an external memory controller (or other slave) on the system bus      |

Table 8. BRx Bit Descriptions (Continued)

| Name              | Description                                                                                                                                                                                                                 |    | Settings                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------|

| <b>ATOM</b> 28–29 | Atomic Operation                                                                                                                                                                                                            | 00 | The address space controlled by the memory controller bank is not used for atomic operations                   |

|                   |                                                                                                                                                                                                                             | 01 | Read-after-write-atomic (RAWA)                                                                                 |

|                   |                                                                                                                                                                                                                             | 10 | Write-after-read-atomic (WARA)                                                                                 |

|                   |                                                                                                                                                                                                                             | 11 | Reserved                                                                                                       |

| DR                | Data Pipelining                                                                                                                                                                                                             | 0  | No data pipelining is done                                                                                     |

| 30                |                                                                                                                                                                                                                             | 1  | Data beats of accesses to the address space controlled by the memory controller bank are delayed by one cycle. |

| V                 | Valid Bit                                                                                                                                                                                                                   | 0  | This bank is invalid                                                                                           |

| 31                | Indicates that the contents of the BRx and ORx pair are valid. The CS signal does not assert until V is set. An access to a region with no V bit set may cause a bus monitor time-out. After a system reset, BR0[V] is set. | 1  | This bank is valid                                                                                             |

# 2.6.2 ORx Register

The ORx registers define the sizes of memory banks and access attributes.

Figure 10. ORx in UPM Mode

**Table 9** describes the ORx fields in UPM mode.

Table 9. Option Register (ORx) in UPM Mode Bit Descriptions

| Name              | Description                                                                                                                                                                                                                                                                                                                           | Settings                                                                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>AM</b><br>0–16 | Address Mask  Masks corresponding BRx bits. Masking address bits independently allows external devices of different size address ranges to be used. Address mask bits can be set or cleared in any order in the field, allowing a resource to reside in more than one area of the address map. AM can be read or written at any time. | <ul> <li>Corresponding address bits are masked</li> <li>The corresponding address bits are used in the comparison with address pins</li> </ul> |

| BCTLD<br>19       | Data Buffer Control Disable Disables the assertion of BCTLx during access to the current memory bank.                                                                                                                                                                                                                                 | BCTLx is asserted upon access to the current memory bank     BCTLx is not asserted upon access to the current memory bank                      |

| <b>BI</b> 23      | Burst Inhibit Indicates if this memory bank supports burst accesses.                                                                                                                                                                                                                                                                  | The bank supports burst accesses     The bank does not support burst accesses The UPMx executes burst accesses as series of single accesses    |

Interfacing the MSC8101 UPM to an External Dual-Port SRAM, Rev. 3

| Table 9. | Option Register | (ORx) | in UPM M | lode Bit | Descriptions |

|----------|-----------------|-------|----------|----------|--------------|

|----------|-----------------|-------|----------|----------|--------------|

| Name              | Description                                                                                                                                 |          | Settings                                                                                                                 |