# Freescale Semiconductor Application Note

Document Number: AN2295 Rev. 13, 10/2013

# Developer's Serial Bootloader

by: Pavel Lajsner, Pavel Krenek, Petr Gargulak

# 1 Project objectives

The developer's serial bootloader offers to user easiest possible way how to update existing firmware on most of Freescale microcontrollers in-circuit. In-circuit programming is not intended to replace any of debugging and developing tool but it serves only as simple option of embedded system reprogramming via serial asynchronous port or USB. The microcontrollers supported by the developer's serial boot loader include 8-bit families HC08 and HCS08, and 32-bit families, ColdFire and Kinetis. New Kinetis families include support for K and L series.

This application note is for embedded-software developers interested in alternative reprogramming tools. Because of its ability to modify MCU memory in-circuit, the serial bootloader is a utility that may be useful in developing applications.

The developer's serial bootloader is a complementary utility for either demo purposes or applications originally developed using MMDS and requiring minor

#### **Contents**

| 1 | Project Objectives                              | 1    |

|---|-------------------------------------------------|------|

| 2 | FC Protocol Description                         | 3    |

| 3 | FC Protocol, Version 1, M68HC908 Implementation | . 12 |

| 4 | FC Protocol, Version 2, HC9S08 Implementation   | . 18 |

| 5 | FC Protocol, Version 3, Large M68HC08           |      |

|   | Implementation                                  | . 23 |

| 5 | FC protocol, version 4, ColdFire (V1)           |      |

| 3 | MCU Slave Software                              | . 23 |

| 7 | PC Bootloader Master Software                   | . 41 |

| 3 | Bootloading Procedure Demonstration             | . 46 |

| 9 | References                                      | . 51 |

|   |                                                 |      |

#### **Project objectives**

modifications to be done in-circuit. The serial bootloader offers a zero-cost solution to applications already equipped with a serial interface and SCI pins available on a connector. This document also describes other programming techniques:

- FLASH reprogramming using ROM routines

- Simple software SCI

- Software for USB (HC08JW, HCS08JM and MCF51JM MCUs)

- Use of the internal clock generator

- PLL clock programming

- EEPROM programming (AS/AZ HC08 families)

- CRC protection of serial protocol option

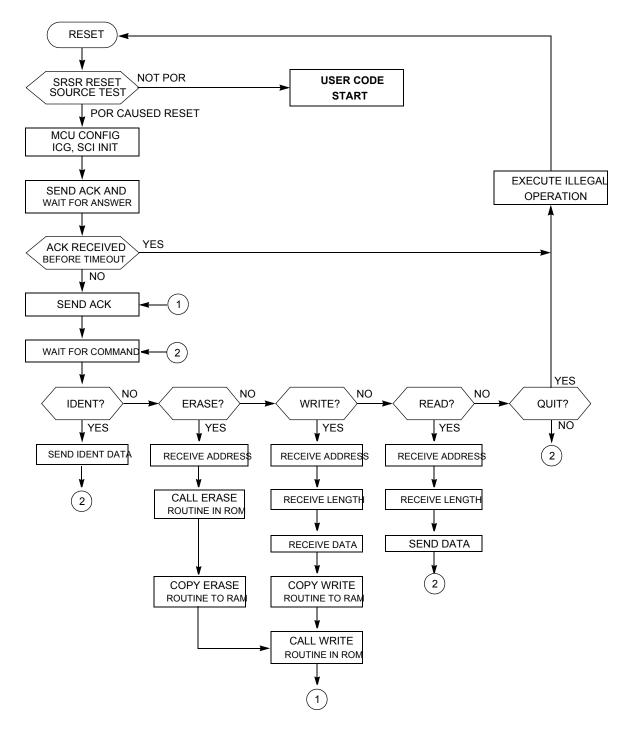

Figure 1. Top-level view

# 1.1 Project goals

Freescale Semiconductor M68HC08 MCUs use a standard monitor-mode interface for FLASH programming. Configuration of monitor mode requires a specific clock and high-voltage (monitor-mode entry voltage  $V_{TST} = V_{DD} + 2.5 = 8$  V) applied to the IRQ pin upon MCU startup. Also, establishing monitor-mode communication uses a few pins. If the application already uses a standard serial SCI interface for communication, a different code (the bootloader) can be used to communicate with the PC using the same interface used for reprogramming.

The bootloader can be used for only reprogramming, not for in-circuit debugging. The bootloader is a low-cost in-circuit programming solution.

# 1.2 Bootloader application requirements

The following points described important parameters of the bootloader application:

• Low memory use — The bootloader must use as little memory as possible. Other versions of bootloaders use more than 1 KB of memory, which is unacceptable on devices with 3 KB of memory available (such as the MC68HC908JK3). The solution described in this document

implements all features as simply as possible, excluding checksums, and so forth. The target size is less than 500 B for the 8-bit MCUs. The USB version of bootloaders included drivers for the communication over the USB. For this bootloaders is needed 8KB memory available (HCS08JM and MCF51JM). The Kinetis K and L series have a similar sizes (less than 2 KB).

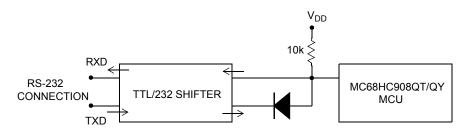

- **Low pin-count** This bootloader uses already implemented standard means of communication (typically SCI on boards primarily intended for communication). The standard SCI uses two wires, RxD and TxD. No additional wires are used to start bootloader.

- Transparency with respect to the user S19 file The complete application should be transparent to the user code S19 file. This means no adjustments are required in the S19 file. Other M68HC08, HCS08, and ColdFire V1 bootloader applications require modification to interrupt vectors or other modifications to the S19 file for it to accept the bootloader.

#### 1.3 Demo features of bootloader application

This document describes several different M68HC(S)08, ColdFire V1 (CFV1), and Kinetis bootloader implementations that vary mainly because the targets M68HC(S)08, CFV1, and Kinetis MCUs have different features. Several features of the M68HC(S)08, CFV1, and Kinetis Family are also demonstrated, making this document useful to a wider audience than those who require only the bootloader. The different M68HC(S)08, CFV1, and Kinetis implementations also demonstrate the following features:

- Use of built-in ROM routines for FLASH self-programming (see also AN1831, AN2545, and AN2635 in References).

- User implementation of in-circuit reprogramming routines on ROM-less MCUs such as the MC68HC908GP Family or the MC9S08GB/GT Family.

- Use of different implementations of the FLASH block protection technique (MC68HC908GP, MC68HC908GR, MC68HC908EY, versus MC68HC908JK/JL Families).

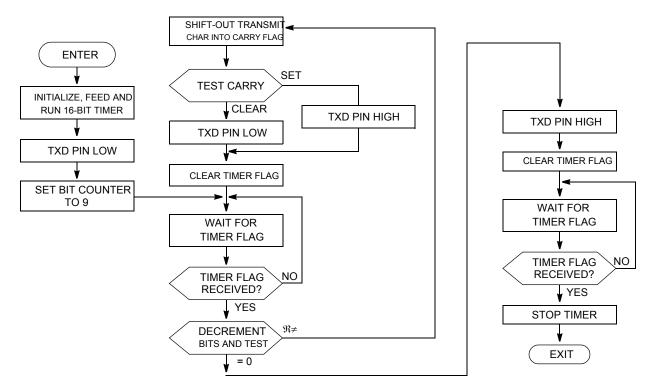

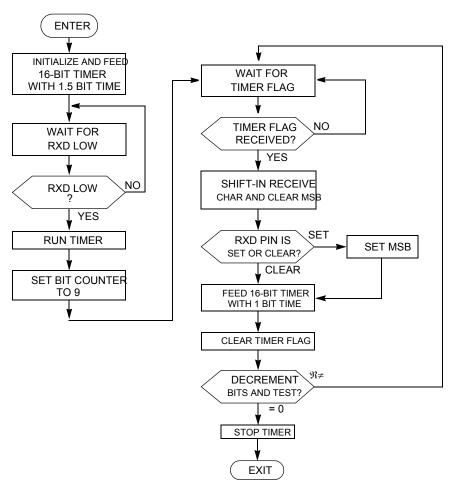

- Implementation of software SCI on SCI-less MCUs, such as the MC68HC908JK/JL Family.

- Use of the internal clock generator and its trimming (for the MC68HC908KX Family), for HCS08 Families (MC9S08GB/GT).

- EEPROM programming (for the MC68HC908AB/AS/AZ Family).

- USB communication implementation on USB2.0 Full-speed HS08 MCUs, such as the MC68HC908JW Family, HCS08JM and MCF51JM Family.

- Use implementation of flash programming routines for the HCS08 and the ColdFire (V1) devices (see also AN3492 in References).

#### 2 FC protocol description

As described in Bootloader application requirements implementation must be simple and use low memory. Therefore, the protocol running between the master PC and slave MCU is also very simple. It is called FC protocol because one significant character (acknowledge or ACK) 0xFC or 111111100b is used.

This section describes the protocol used to communicate between the PC and target MCU to reprogram the MCU. An explanation of family-specific implementation features follows a general description.

Developer's Serial Bootloader, Rev. 13 Freescale Semiconductor 3

#### FC protocol description

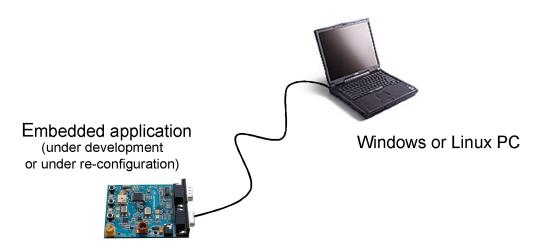

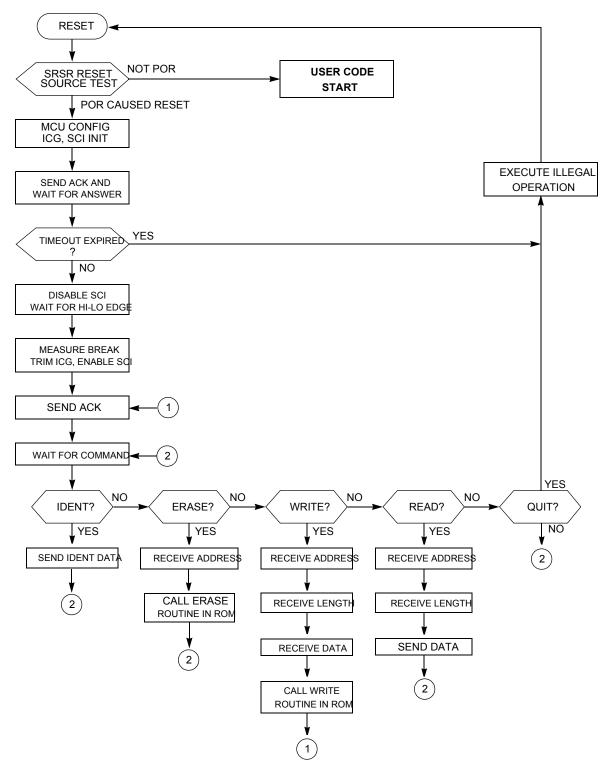

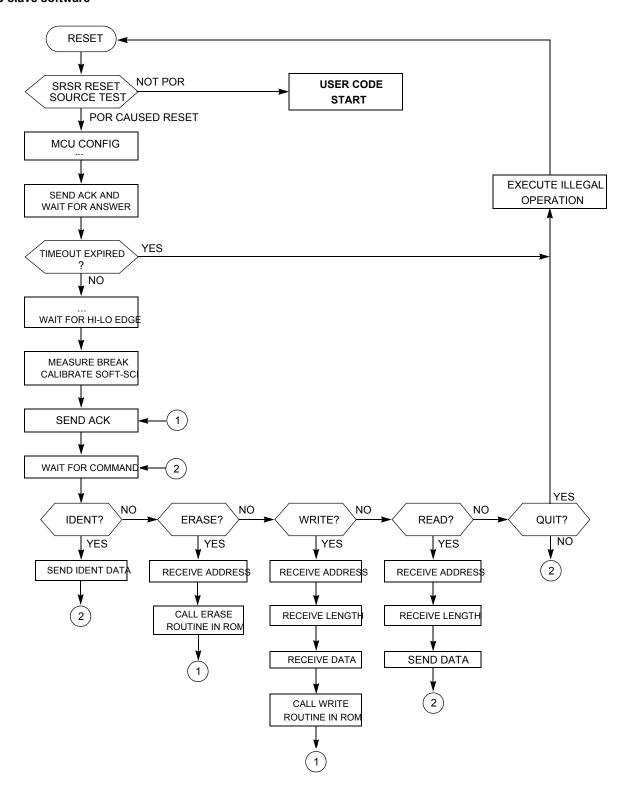

The following is a simplified state diagram that shows separate states of the bootloader, which is described in this document:

Figure 2. Simplified flow diagram of the bootloader application

# 2.1 Initial hook-up

Several methods can be used to enter bootloader mode. Several other solutions use a "certain level on certain pin" method. For example, if logic 0 appears on an IRQ pin during MCU startup, the bootloader code starts else the user code starts.

Because the developer's serial bootloader application must use the lowest number of pins, a "certain character at a certain time" method is used. This means that the MCU sends out an ACK character through the serial interface and waits for an answer. If no character is received within the specified time (hook-up time-out), the process continues with the user code.

If this becomes a limitation for any reason, the user may modify the bootloader code to meet the application needs (for example, an additional simple IRQ pin test at startup can be implemented). For more details, see M68HC08 system limitations.

## 2.2 Clock source

FC protocol allows two scenarios, depending on whether the MCU runs on a known and exact frequency or uses an RC (resistor, capacitor) clock or an internal clock (or any clock unknown at compile time).

# 2.2.1 Unknown MCU communication speed

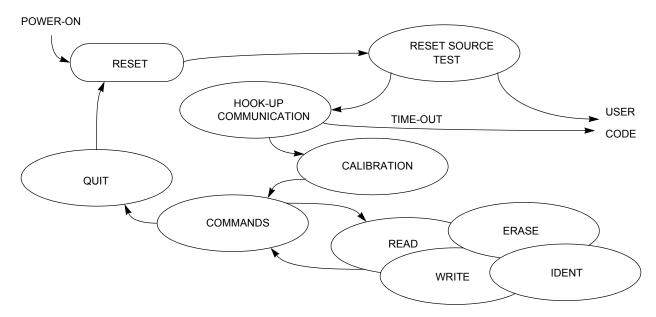

If the frequency is uncertain (unknown at compile time), the MCU will not check whether an incoming ACK character conforms only to the 0xFC pattern. Because of the MCU clock tolerance, several

characters can be interpreted differently instead of original 0xFC sent out by the PC (Figure 3). The 0xFC pattern check on the MCU side can be eliminated completely, which saves MCU memory.

PC TRANSMITS 0XFC CHARACTER AT PROPER DATA RATE:

Figure 3. Matching different communication speeds

The following table shows the characters that can be correctly received (without framing or noise errors) if transmit and receive speeds are not equal:

| PC Data Rate | MCU Data Rate | Character<br>Received<br>in Binary | Character<br>Received<br>in Hex |

|--------------|---------------|------------------------------------|---------------------------------|

| 9600         | 9600*1/3      | 11111111b                          | 0xff                            |

| 9600         | 9600*2/3      | 11111110b                          | 0xfE                            |

| 9600         | 9600*3/3      | 11111100b                          | 0xFC                            |

| 9600         | 9600*4/3      | 11111000b                          | 0xF8                            |

| 9600         | 9600*5/3      | 11110000b                          | 0xF0                            |

| 9600         | 9600*6/3      | 11100000b                          | 0xE0                            |

| 9600         | 9600*7/3      | 11000000b                          | 0xC0                            |

| 9600         | 9600*8/3      | 10000000b                          | 0x80                            |

| 9600         | 9600*9/3      | 00000000b                          | 0x00                            |

Table 1. PC to MCU transmission — unmatched data rate

Developer's Serial Bootloader, Rev. 13

#### FC protocol description

If the MCU transmits to the PC at an unmatched data rate, the PC receives (and accepts) characters that are different from the 0xFC character. The PC accepts all characters from the mentioned set (0xFF, 0xFE, 0xFC, 0xF8, 0xF0, 0xE0, 0xC0, 0x80, and 0x00). If a character is received, an ACK is immediately sent back to the MCU. After the MCU recognizes this answer, it enters the next phase, Slave frequency calibration.

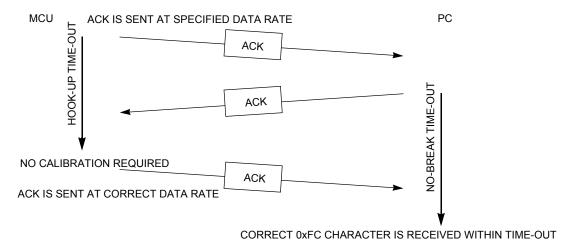

## 2.2.2 Known MCU communication speed

If the frequency is certain (known at compile time), the MCU will be configured to match exactly the communication speed of the PC. All characters are received correctly without any distortion.

The MCU sends 0xFC to the PC, which immediately sends an ACK to the MCU. After the ACK is received, the MCU also (formally) enters the Slave frequency calibration phase.

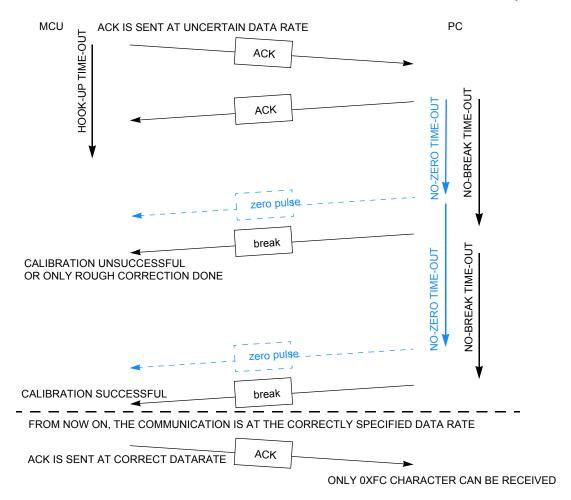

# 2.3 Slave frequency calibration

During this phase, the MCU clock is calibrated. Until now, the PC has communicated with the MCU at a speed that could be from 33% to 300% tolerance. During this phase, the MCU communication speed must be adjusted to match the PC communication speed.

After the PC enters the calibration phase, the no-break timeout starts. If a correct ACK character (0xFC) is not received within this period, a break character is sent at the communication data rate.

A break character consists of 10 consecutive logical zeros. For example, at a 9600 bd rate, its high-low-high pulse lasts  $10 \times 104 \, \mu s = 1.04 \, ms$ .

The MCU then measures the break character length and determines whether its clock is too fast or too slow. The MCU then makes an adjustment to its system clock (or an adjustment of receive routines if, for example, software serial communication is used). This can be repeated as many times as required for the MCU to achieve the proper clock speed.

#### **NOTE: Virtual ports workaround**

Most of the users are using **virtual serial ports** and some of these standards are not able to transfer break calibration character. For this reason, new feature using zero calibration character was added in place of the break character pulse (Figure 4). A zero calibration character consists of nine consecutive logical zeros.

The calibration feature with zero character is implemented in master application as "short TRIM" (checkbox "short TRIM", Master applications user guides). The target must be configured for using short calibration (trim) pulse.

After the MCU is calibrated to the correct clock (or after the receive routines are calibrated), the ACK character is sent to the PC to stop sending calibration characters (Figure 4).

Figure 4. StartUp communication with calibration

If the MCU is operating at the correct data rate (no calibration is possible or required, and the MCU clock is crystal driven), the PC can immediately send an ACK, skipping the calibration phase entirely (Figure 2).

Figure 5. Start-Up communication without calibration

Developer's Serial Bootloader, Rev. 13

#### FC protocol description

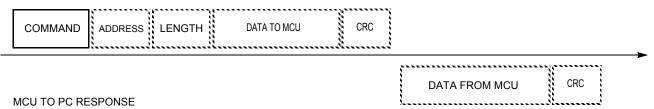

# 2.4 Interpreting MCU commands

After communication between MCU and PC is established, then MCU enters the main command interpreter loop. The MCU executes simple commands to reprogram its own nonvolatile memory. The communication is conducted on a master-slave mechanism: the PC issues the commands, the MCU executes them and acknowledges the completion of each command either by data or single ACK character.

The minimal set of commands is composed of:

- Ident command

- Quit command

Two more basic commands are implemented for pure reprogramming:

- Erase command

- Write command

If the user needs a verification feature, one additional (read) command must be compiled into the MCU code. This command is not required for pure reprogramming purposes (minimal configuration).

Read command

#### **CRC** safety protocol implementation

The protocol provides option to switch on CRC safety for all messages. For CRC is used standard 16 bit implementation CCITT16 and as reset value is used 0xFFFF.

Example value for erase command:

```

'E'-1byte - 0x45

'start address' - 2 bytes - 0x1234

'CRC - 2 bytes' - 0x2907

```

#### PC TO MCU COMMAND

<sup>\*</sup> Dashed fields are not always implemented, data from the MCU may contain only an ACK character instead.

Figure 6. Typical command and response

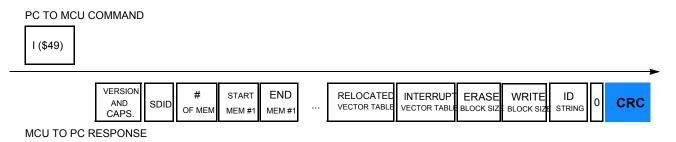

#### 2.4.1 Ident command

The ident command (coded as 'I', \$49) has no additional fields.

This command is immediately issued by the PC after communication is established. The purpose of the ident command is to notify the PC about several basic properties of the MCU being programmed. All multibyte fields are sent with MSB first.

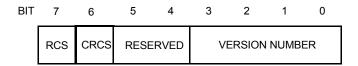

• Version number and capability table - 1 byte

Figure 7. Version number and capability table

- RCS The Read Command Supported (RCS) flag informs the PC if the read command is supported (implemented). If not, all calls to the read routine are ignored by the MCU and no response is sent back to the PC. The PC software warns the user that no read capabilities are available.

- Supported Not supported (usually due to memory constraints)

- CRCS The CRC Serial Protocol Supported flag informs the PC that all rest communication (including Ident command) is secured by CRC-CCITT checksum.

- Supported<sup>1</sup> Not supported (usually due to memory constraints)

- RSVD These bits are reserved for future use, unused, and should be set to 0.

- VER Protocol Version

## 2.4.2 FC protocol version 1 (M68HC08)

Version 1 of the protocol is for M68HC08 MCUs. Additional fields in version 1 are defined as follows:

- Start address of reprogrammable memory area 2 bytes.

- End address of reprogrammable memory area + 1 2 bytes.

- Address of Bootloader user table 2 bytes.

- Start address of MCU interrupt vector table 2 bytes.

- Length of MCU erase block 2 bytes.

- Length of MCU write block 2 bytes.

- Bootloader data (specific bootloader information, see device-specific implementation; compared in Table 2) 8 bytes.

- Identification string, zero terminated <n> bytes.

- If the CRC capability of serial protocol is enabled, then follows CRC-CCITT checksum 2 bytes.

<sup>1.</sup> Available since Q3 2011

#### FC protocol description

PC TO MCU COMMAND I (\$49) VERSION INTERRUPT END BOOTLOADER ERASE WRITE BOOTLOADE START ID STRING **CRC** AND DATA MEM USER TABLE VECTOR TAB BLOCK SIZE BLOCK SIZE MEM CAPS

MCU TO PC RESPONSE

Figure 8. Ident command (FC protocol version 1, M68HC08)

# 2.4.3 FC protocol version 2 (HCS08) and FC protocol version 3 (large M68HC08)

Version 2 of the protocol is for HCS08 MCUs; version 3 is for large M68HC08 (HC08 with two or more FLASH memory banks). In both versions, additional fields are defined as follows:

- System device Identification register content 2 bytes (unused in protocol version 3, coded as \$FFFF)

- Number of reprogrammable memory areas (N) 1 byte

- Start address of reprogrammable memory area #1 2 bytes

- End address of reprogrammable memory area #1 + 1 2 bytes

- Start address of reprogrammable memory area #2 2 bytes

- End address of reprogrammable memory area #2 + 1 2 bytes

- Start address of reprogrammable memory area #N 2 bytes

- End address of reprogrammable memory area #N + 1 2 bytes

- Address of relocated interrupt vector table 2 bytes

- Start address of MCU interrupt vector table 2 bytes

- Length of MCU erase block 2 bytes

- Length of MCU write block 2 bytes

- Identification string, zero terminated <n> bytes

- If the CRC capability of serial protocol is enabled, then follows CRC-CCITT checksum 2 bytes

Figure 9. Ident command (FC protocol versions 2 and 3, HCS08)

Developer's Serial Bootloader, Rev. 13

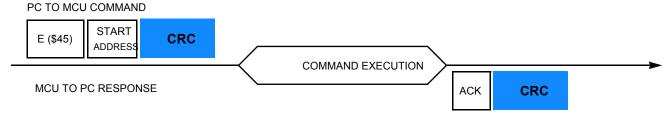

#### 2.4.4 Erase command

The erase command (coded as 'E', \$45) has only address field, length or data fields are not present. The start address is a 2-byte field, MSB first. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum.

The MCU erases the address block where the specified address resides. The length of block to be erased is equal to the erase-block size (typically depends on hardware).

After the MCU completes execution of the command, the ACK (\$FC) character is sent to the PC. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum. The erase command's minimum and maximum execution times are not specified.

Figure 10. Erase command

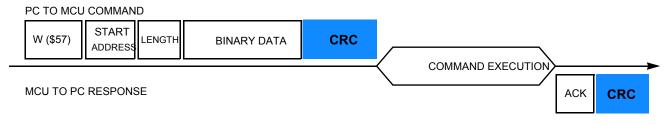

#### 2.4.5 Write command

The write command (coded as 'W', \$57) has both address and data fields. The address contains the first address to be programmed. The first byte is the length followed by the number of bytes to be programmed. The start address is a 2-byte field, MSB first and the length is a 1-byte field. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum.

After the MCU completes execution of the command, the ACK (\$FC) character is sent to the PC. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum. The write command's minimum and maximum execution times are not specified.

Figure 11. Write command

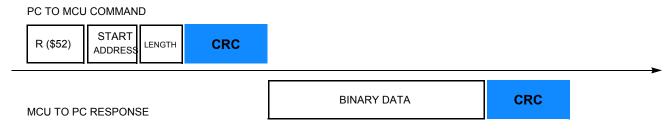

#### 2.4.6 Read command

The read command (coded as 'R', \$52) has address and data fields. The address contains the first address to be programmed; the single byte is the length of data to be read. The start address is a 2-byte field, MSB first and the length is a 1-byte field. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum.

#### FC protocol, version 1, M68HC908 implementation

The MCU sends this number of read bytes to the PC. If the CRC capability of serial protocol is enabled, then the 16 bits(2 bytes) follows with CRC-CCITT checksum.

Figure 12. Read command

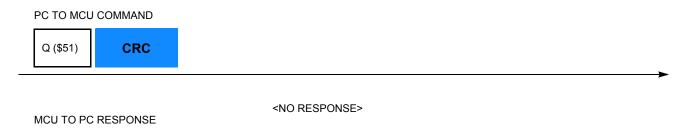

#### 2.4.7 Quit command

The quit command (coded as 'Q', \$51) has no address or data fields. Execution of bootloader code is immediately finished, and the user code is started. No ACK (\$FC) character is sent to the PC.

Figure 13. Quit command

#### 2.4.8 Bootloader user table

The bootloader user table is a reprogrammable memory area intended for storage of bootloader-specific data. This memory area is unavailable for the user program. For this table's memory allocation, refer to FC protocol, version 1, M68HC908 implementation.

# 3 FC protocol, version 1, M68HC908 implementation

This section describes features specific to the M68HC908 bootloader implementation. The memory allocation is heavily MCU specific, so the meaning of all variables is explained in this section in detail.

Developer's Serial Bootloader, Rev. 13

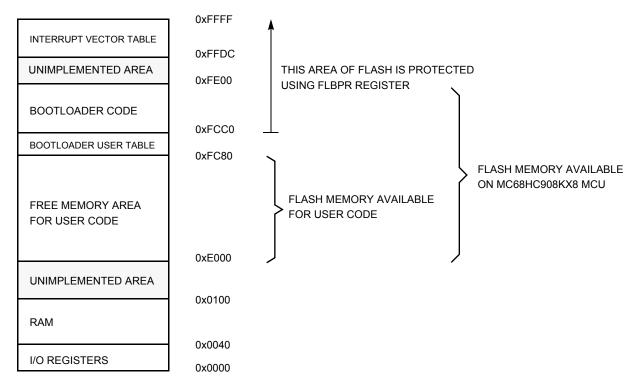

Figure 14 shows the typical memory allocation for M68HC908 MCUs with the bootloader preprogrammed. For example, the MC68HC908KX8 MCU memory map includes:

- 7680 bytes of FLASH memory (\$E000–\$FDFF)

- 192 bytes of random-access memory (RAM) (\$0040–\$00FF)

- 36 bytes of user-defined vectors (\$FFDC-\$FFFF)

13

Figure 14. Simplified example of memory allocation in MC68HC908KX8

# 3.1 Memory allocation

The bootloader code occupies the top-end of FLASH memory (the highest memory address space). This placement allows an effective use of the FLASH block protection technique (see the specific MCU data sheet for details).

# 3.2 FLASH Block Protection Register (FLBPR)

By setting a FLBPR (FLASH block protection register), all address space above this address is protected from intentional and unintentional erasing/rewriting. After both bootloader and FLBPR register are programmed into memory, the bootloader code is protected from unintentional modification by user code.

#### NOTE

Some M68HC908 MCUs have an FLBPR register in RAM instead of FLASH (for example, the MC68HC908JK/JL Families). The bootloader code sets this register properly but the user code can eventually modify FLBPR and erase/write the bootloader code. See FLBPR not usable (in some M68HC08 family MCUs).

For example, the MC68HC908KX8 bootloader to the PC memory allocation is:

- \$01 Version 1, read command not implemented (bit 7).

- \$E000 Start address of reprogrammable memory area.

- \$FC80 End address of reprogrammable memory area + 1.

#### FC protocol, version 1, M68HC908 implementation

- \$FC80 Address of Bootloader user table.

- \$FFDC Start address of MCU interrupt vector table.

- \$0040 Length of MCU erase block.

- \$0020 Length of MCU write block.

- 0,0,0,0,0,0,0,0 Bootloader data. No strictly defined syntax; different M68HC08 implementations provide different values (for example, the sixth value in the MC68HC908KX8 implementation is the value of the internal clock generator [ICG] trim register after calibration). All these bootloader data are then programmed back into the bootloader user table and can be retrieved during all subsequent starts (for example, to trim the MCU's ICG to the best-known value before user code start).

- 'KX8-IR',0 Identification string, zero terminated. Information to be displayed on PC screen.

## 3.3 Interrupt vector table relocation

Because the FLASH block protection technique also protects the interrupt vector table from being overwritten, some method must be used to relocate these vectors to the different locations. To do this, the bootloader user table is used. It is a part of memory not protected by the FLBPR, but it is unavailable to the user program. All standard interrupt vectors are pointing to this table where JMP instructions are expected to be stored for each interrupt. The only exception is the reset vector that points to the bootloader code start. When an interrupt occurs, the vector is fetched from protected memory and directs execution to continue at the corresponding JMP instruction in the bootloader user table.

The following figure shows interrupt vector table relocation for M68HC08 MCUs.

**INTERRUPT VECTOR TABLE**

#### RESET VECTOR 0xFFFE **INTERRUPT VECTOR 1** 0xFFEC **INTERRUPT VECTOR 2** 0xFFEA **INTERRUPT VECTOR 3** 0xFFE8 **BOOTLOADER CODE** 0xFE00 0xFFE0 **INTERRUPT VECTOR 16** 0xFFDE **EXIT INTERRUPT VECTOR 17** 0xFFDC **START BOOTLOADER USER TABLE** 0xFCC0 JMP USER INT. VECT. 17 0xFD00 0xFCBB <sup>◄</sup> JMP USER INT. VECT. 16 0xFCB8 0xFC84 JMP USER INT. VECT. 3 0xFC81 4 JMP USER INT. VECT. 2 0xFC8E JMP USER INT. VECT. 1 0xFC8B **USER CODE** JMP USER RESET VECTOR 0xFC88 ◀ START (RESET) **BOOTLOADER DATA** 0xFC80 **INTERRUPT ROUTINE 1 INTERRUPT ROUTINE 2 INTERRUPT ROUTINE 16 INTERRUPT ROUTINE 17**

Figure 15. Interrupt vector table relocation (M68HC08 MCUs)

#### NOTE

In a standard interrupt vector table, each record is 2 bytes long (each vector is a 16-bit address). This is different from the bootloader user table, for which each record is 3 bytes long - a JMP opcode (\$CC) plus a 16-bit address.

Developer's Serial Bootloader, Rev. 13

#### 3.3.1 S19 file

Because the bootloader operation must be transparent to the user S19 file, another piece of intelligence is built into the PC master code (instead of the MCU slave). The relocation works as follows:

If the data from an S19 record corresponds to an address in the interrupt vector table, the value is relocated into the corresponding area in the bootloader user table, including a JMP instruction (opcode \$CC). For example, if the user S19 file contains #3 interrupt vector \$E123 at address \$FFE8, such a vector is relocated into the sequence \$CC, \$E1, \$23 (JMP \$E123) programmed to the \$FC81 address in the bootloader user table.

Using this method, the user S19 file does not need to be modified, but the lower address of the end of FLASH memory must be considered. In addition, this JMP instruction (3T) delays every interrupt, as explained in Each interrupt 3T delayed.

#### 3.4 User code start

The user code is started in an unusual way to provide a register setup similar to how it appears after MCU reset.

#### 3.4.1 Software reset

If the bootloader must quit and run user code, an illegal operation is intentionally executed (M68HC08 illegal opcode \$32). This causes an illegal operation reset, and the MCU restarts. During bootloader startup, the System Integration Module (SIM) Reset Status Register (SRSR) is tested. If a power-on-reset is not detected, the user code is started instead of the bootloader code. This allows the transparent operation of all other resets (such as illegal address, and so forth) with only a short additional delay caused by testing the SRS register and executing associated jump instructions.

### 3.4.2 Hardware reset

In some implementations, a pin reset (caused by external reset pin) is also included as a valid source of reset for the bootloader to start. This allows remote in-circuit reprogramming in embedded applications able to drive the M68HC08 reset pin.

Another test has been added to the real bootloader application: if no reset source is detected (that is, if the SRS register is 0), the bootloader is selected by default. This may happen when an external pin causes reset, but the reset pulse is shorter than specified. In that case, the minimum length of reset pulse that will cause reset is shorter than the length needed for the proper propagation of the external reset flag to the SRS register.

Because the SRS register is one-time readable (it clears after read), no subsequent reads of this register provide a valid value. See M68HC08 system limitations for details.

# 3.5 M68HC08 system limitations

This section summarizes limitations that must be considered when using the bootloader with the user application.

## 3.5.1 Memory occupied

One of the most important requirements is to use the smallest code possible. Typical M68HC908 implementations are between 300 to 500 bytes, including the bootloader user table. If the target M68HC08 MCU is capable of FLASH programming using internal ROM routines, the memory consumption is near the lower limit. Larger M68HC08 MCUs (which are not usually equipped with ROM code for FLASH programming) will require approximately 500 bytes of FLASH of the total 32 KB (as is the case with the MC68HC908GP32).

The bootloader is placed at the upper end of FLASH memory; therefore, the only modification required in the user code is in the memory mapping (typically found in the linker parameter file).

The M68HC08 MCU signals the actual available FLASH addresses. The PC Bootloader software will not allow programming if the user code overlaps with bootloader code.

# 3.5.2 Time delay upon startup and initial communication

The number of pins with specific meanings during bootloader startup must be as small as possible. Especially in communication systems (for example, those using a standard serial port), pin overhead is zero and a "certain level character at a certain time" method is used. So, the bootloader waits a certain amount of time to receive an answer from the PC at startup. If none is received, the user code starts. The typical delay is in the range of several hundred milliseconds.

If this startup delay becomes an issue for the final application, the user may modify the bootloader code and use a "certain level on a certain pin" method instead. A simple test of the voltage level on the IRQ pin (or any other input pin) can be used to indicate whether the bootloading sequence is required.

# 3.5.3 Each interrupt 3T delayed

Every interrupt call is delayed by 3T bus clocks required to execute the JMP instruction stored in the bootloader user table. This interrupt vector relocation (as described in Interrupt vector table relocation) has been chosen as the best solution for achieving user code transparency and security of the bootloader code.

The interrupt latency is about 10 to 15T (assuming that no interrupt is being executed), so this additional delay is not significant for the most applications.

# 3.5.4 FLBPR not usable (in some M68HC08 family MCUs)

The bootloader uses a FLASH block protection technique to protect itself from being overwritten (where applicable; see FLASH Block Protection Register (FLBPR) for details).

Some M68HC08 MCUs (such as the KX, GP, and GR devices) have this FLASH block protection register stored in FLASH, so it cannot be modified in user mode. The FLBPR can be erased or programmed only

#### FC protocol, version 2, HC9S08 implementation

with an external voltage,  $V_{TST}$ , present on the IRQ pin (normal monitor mode). Because this feature is completely dedicated to bootloader code protection, it is unavailable to the user application code. If the value for FLPBR appears in the user S19 code, a warning is displayed. Such an occurrence should be omitted from user S19 code.

Some families have the FLASH block protection register stored in RAM instead (the MC68HC908JK/JL Families are like this). The bootloader sets the correct value at the beginning of its execution to protect itself. However, user code can modify this register and protect its own memory areas as needed. This also implies that the bootloader is not 100% protected from user code.

See the specific MCU data sheet for a detailed explanation.

## 3.5.5 SRS register unusable

The bootloader uses an SRS register (as described in User code start) to recognize the reset source to determine whether the user code will run. Because the SRS register is one-time readable (that is, it is reset after first read), the user code does not have access to the SRS register value (if the bootloader is present in the memory and makes the first read after each reset). There is no simple solution for this situation. After the SRS register is read by the bootloader, it is stored in one RAM location. Its memory location may differ from one implementation to another. If the application requires the SRS register and bootloader, the user must redirect the SRSR reading to this specific RAM location. This location can be obtained from the bootloader's MAP file.

# 4 FC protocol, version 2, HC9S08 implementation

This section describes features that are specific to the HC9S08 bootloader implementation. The memory allocation is heavily MCU specific so the meaning of variables is explained in this section.

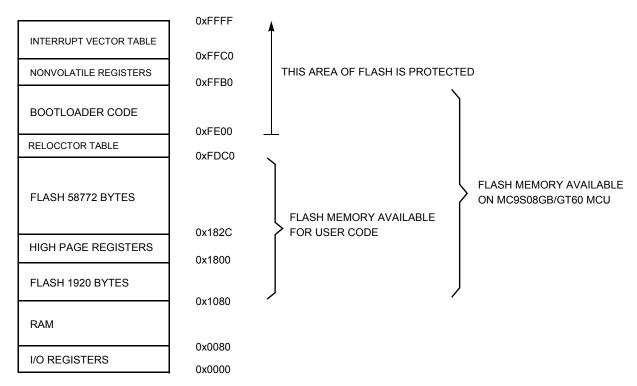

Figure 16 shows the memory allocation typical to the HC9S08 devices with the bootloader preprogrammed. For example, the MC9S08GB/GT60 device memory map includes:

- 60 KB of FLASH memory (\$1080–\$17FF, \$182C–\$FFAF)

- 4 KB of random-access memory (RAM) (\$0080–\$107F)

- 16 bytes of nonvolatile registers (\$FFB0-\$FFBF)

- 64 bytes of user-defined vectors (\$FFC0-\$FFFF)

19

Figure 16. Simplified example of memory allocation in MC9S08GB/GT60

# 4.1 Memory allocation

The bootloader code occupies the top-end of FLASH memory (the highest memory address space). This placement allows an effective use of the FLASH protection technique (see MCU specific data sheet for details).

# 4.2 FLASH protection

By setting a FLASH protection register, all address space above this address is protected from both intentional and unintentional erasing/rewriting. After the bootloader and the FLASH protection register are programmed into memory, the bootloader code is protected from unintentional modification by user code.

#### NOTE

See FLASH protection technique not usable for limitations.

# 4.3 Example memory allocation

Examples of the MC9S08GB/GT60 bootloader to the PC memory allocation are as follows:

- \$82 Version 2, read command implemented (bit 7)

- \$r002 System device identification register (SDIDR) content (\$002 for GB/GT Family, r (four top bits) is chip revision number reflecting current silicon level

- \$02 Number of reprogrammable memory areas

#### FC protocol, version 2, HC9S08 implementation

- \$1080 Start address of reprogrammable memory area #1

- \$1800 End address of reprogrammable memory area #1 + 1

- \$182C Start address of reprogrammable memory area #2

- \$FDC0 End address of reprogrammable memory area #2 + 1

- \$FDC0 Address of relocated interrupt vector table

- \$FFC0 Start address of MCU interrupt vector table

- \$0200 Length of MCU erase block

- \$0040 Length of MCU write block

- 'GB/GT60',0 Identification string, zero terminated. Information to be displayed on PC screen

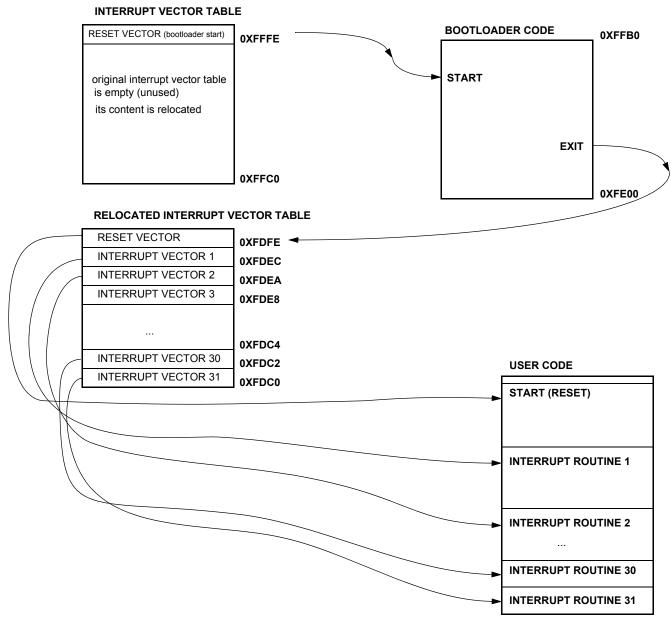

# 4.4 Interrupt vector table relocation

The reset and interrupt vectors would be protected if the flash protection is enabled. Vector redirection (HCS08 hardware feature) allows the user to modify memory allocation of interrupt vector information.

Vector redirection is enabled by programming the NVOPT (nonvolatile option) register. For redirection to occur, at least some portion but not all of the FLASH memory must be block-protected by programming the NVPROT (nonvolatile protection) register. All the interrupt vectors (memory locations \$FFC0-\$FFFD) are redirected except the reset vector (\$FFFE:FFFF).

For example, if 512 bytes of FLASH are protected, the protected address region is from \$FE00 through \$FFFF. The interrupt vectors (\$FFC0-\$FFFD) are redirected to the locations \$FDC0-\$FDFD.

For example, if an SPI interrupt is taken, the values in the locations \$FDE0:FDE1 are used for the vector instead of the values in the locations \$FFE0:FFE1. This allows the user to reprogram the unprotected portion of the FLASH with new program code, including new interrupt vector values while leaving the protected area, which includes unchanged default vector locations.

#### 4.4.1 S19 file

Because bootloader operation must be transparent to the user S19 file, another piece of intelligence is built into the PC master code (instead of the MCU slave). If the record in the interrupt vector table is detected in the user S19 file, the vector is relocated into the corresponding area in the relocated interrupt vector table. For example, if the user S19 file contains #2 interrupt vector at address \$FFEA, such a vector is relocated to the \$FDEA address in the relocated interrupt vector table.

Using this method, the user S19 file does not need to be modified, but the lower address of the end of FLASH memory must be considered.

The following figure illustrates HC9S08 interrupt vector table relocation:

Figure 17. Interrupt vector table relocation explanation (HCS08)

### 4.5 User code start

To provide a register setup similar to how it appears after MCU reset, the user code is started in an unusual way.

#### 4.5.1 Software reset

If the bootloader must quit and run user code, an illegal operation is intentionally executed (HCS08 illegal opcode \$8D). This causes an illegal operation reset and the MCU restarts. During bootloader startup, the System Reset Status (SRS) register is tested. If a power-on-reset is not detected, the user code starts instead

Developer's Serial Bootloader, Rev. 13

#### FC protocol, version 2, HC9S08 implementation

of the bootloader code. This allows the transparent operation of all other resets (such as illegal address and so forth) with only a small additional delay caused by testing of the SRS register and executing associated jump instructions.

#### 4.5.2 Hardware reset

In some implementations, pin reset (caused by external reset pin) is a valid source of reset for the bootloader to start. This allows remote in-circuit reprogramming in embedded applications that are able to drive the HCS08 MCU reset pin.

# 4.6 HCS08 system limitations

This section summarizes limitations that must be considered when using the bootloader with the user application.

# 4.6.1 Memory occupied

One of the strongest requirements is to use the smallest possible code. Typical HC9S08 implementations are 432 bytes (minimal memory size that can be protected) plus another 64 bytes page for relocated interrupt vector table.

The bootloader is placed at the upper-end of FLASH memory, therefore, the only modification required in the user code is in the memory mapping (typically found in the linker parameter file).

The HCS08 MCU signals the actual FLASH addresses available. The PC Bootloader software will warn before programming if the user code overlaps with bootloader code.

# 4.6.2 Time delay upon startup and initial communication

The number of pins with specific meaning during bootloader startup must be as small as possible. Especially in communication systems (for example, those using a standard serial port), pin overhead is zero and a "certain character at a certain time method" is used. So, the bootloader waits a certain amount of time to receive an answer from the PC at startup. If none is received, the user code starts. The typical delay is the range of several hundred milliseconds.

If this startup delay becomes an issue for the final application, the user may modify the bootloader code and use a "certain level on certain pin" method. A simple test of the voltage level on the IRQ pin (or any other input pin) can be used to decide whether the bootloading sequence is required.

# 4.6.3 FLASH protection technique not usable

The bootloader uses a FLASH block protection technique to protect itself from being overwritten, therefore, this feature is not available for the user code. This includes FLASH memory security-related registers (namely NVPROT, NVOPT, and NVBACKKEY) used for protection and interrupt-vector relocation by bootloader.

# 5 FC protocol, version 3, large M68HC08 implementation

This section describes features specific to the protocol version 3 of the bootloader. This is intended for large HC08s (with two or more FLASH memory banks or, more precisely, with two or more separated FLASH memory areas). The format of the Ident command from version 2 is used; the rest remains same as with protocol version 1 (HC08) namely Interrupt vector table relocation.

# 6 FC protocol, version 4, ColdFire (V1)

The protocol version 4 is divided into two versions, version A and version B. The main reason for this separation is the possibility of protecting the bootloader source code. This feature is important for flash programming because protection of the bootloader prevents the source code from being erased. The implementation of version A bootloader is not protected where as the version B implementation is protected.

# 6.1 Version A (unprotected version)

This section describes the features that are specific to Cold Fire V1 implementation version A. The memory allocation is MCU specific, so the meaning of all variables is explained in this section.

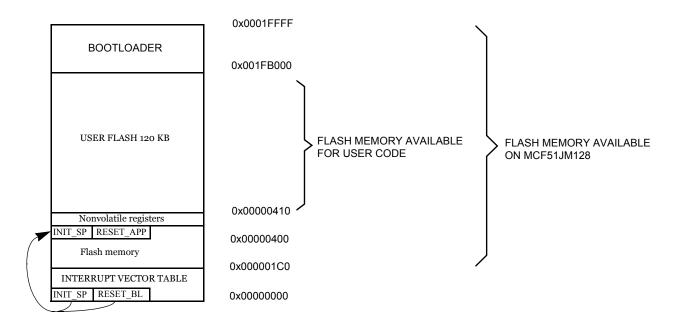

Figure 18 shows the memory allocation typical to the ColdFire V1 devices with the bootloader preprogrammed. For example, the MCF51JM128 device memory map includes:

- 128 KB of FLASH memory (\$0000000-\$0001FFFF)

- 16 KB of random access memory (RAM) (\$00800000-\$00803FFF)

- 16 bytes of nonvolatile registers (\$00000400-\$0000040F)

- 444 bytes of user-defined vectors (\$00000000-\$000001B8)

#### FC protocol, version 4, ColdFire (V1)

Figure 18. Simplified Example of Memory Allocation in MCF51JM128

## 6.1.1 Memory allocation

The bootloader code occupies the top of the FLASH memory (the highest memory address space). This placement reduces only the top of the memory space and it is necessary to modify the end of the user application LCF file; see Memory occupied.

# 6.1.2 FLASH protection

This version of MCU supports a flash protection technique from the beginning of the memory, from address 0x0, for 2 KB sectors.

Flash protection is not implemented in the version A of the protocol, because this version uses the original vector table at address 0x0 for placement of the user vector table.

# 6.1.3 Example of IDENT command

Example of the memory allocation for the ColdFire (V1) bootloaders are as follows:

- \$84 Version 4, read command implemented (bit 7)

- \$rC16 System Device Identification Register (SDIDR) content (\$C16 for JM Family), r (four top bits) is the chip revision number reflecting the current silicon level

- \$02 Number of reprogrammable memory areas

- \$00000 Start address of reprogrammable area #1

- \$003FF End address of reprogrammable area #1 + 1

Developer's Serial Bootloader, Rev. 13

25

- \$00410 Start address of reprogrammable area #2

- \$1FAFF End address of reprogrammable area #2 + 2

- \$00000 Address of the relocated interrupt vector table (value 0 means not allocated)

- \$00000 Start address of the MCU interrupt vector table (value 0 means not allocated)

- \$00400 Length of the MCU erase blocks

- \$00080 Length of the MCU write blocks

- 'MCF51xxxx/USB' Identification string, zero terminated. Information to be displayed on the PC screen

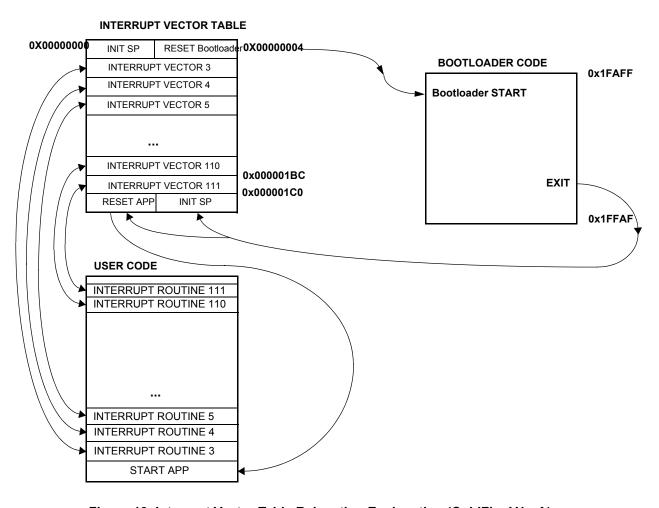

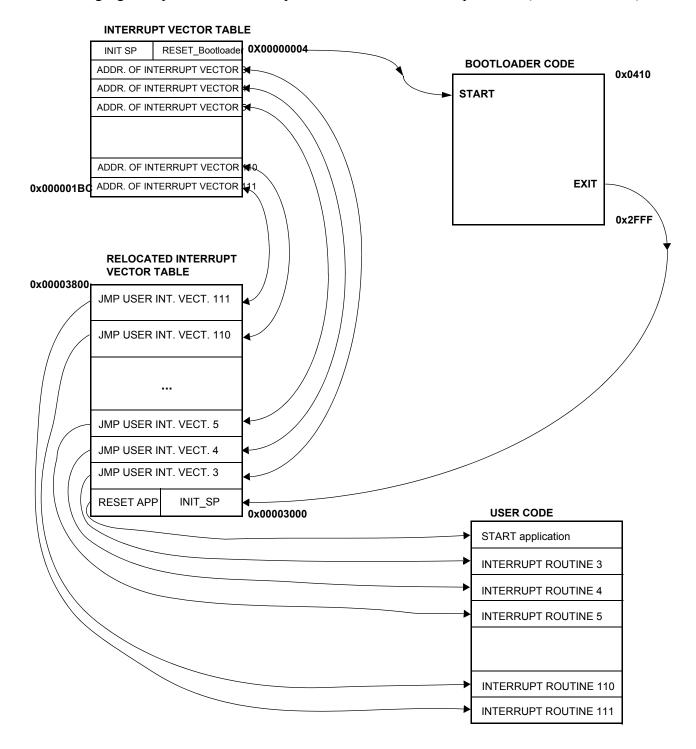

The following figure shows the interrupt vector table relocation for ColdFire V1 MCUs:

Figure 19. Interrupt Vector Table Relocation Explanation (ColdFire V1 - A)

## 6.1.4 Software reset

If the bootloader must quit and run user code, an illegal operation is intentionally executed (ColdFire illegal opcode stop #0). This causes an illegal operation reset and the MCU restarts. During bootloader startup, the system reset status register (SRS) is tested. If a power-on-reset is not detected, the user code

#### FC protocol, version 4, ColdFire (V1)

starts instead of the bootloader code. This allows the transparent operation of all other resets with only a short additional delay caused by testing of the SRS register and executing associated jump instruction.

## 6.1.5 ColdFire system limitations

This section summarizes the limitations that must be considered when using the bootloader with the user application.

## 6.1.5.1 Memory occupied

One major thing is to use the smallest code possible. Typical ColdFire V1 implementations are 1 KB (SCI version) and 8 KB (USB version for JM version). For the USB version, the biggest part of the source code is occupied by the USB drivers (5 KB).

The bootloader limits the top of flash memory, and therefore there must be a modified Linker Command File (LCF) user file. If the LCF file is not set correctly, bootloader will display a warning and the bootloader will be erased. An example of the modification is shown in the following code block:

# 6.1.5.2 Description of the reset transfer

The original vector 1(INIT SP) and vector 2(RESET) are rewritten to the bootloader's reset and stack pointer initialization values. The value of the beginning of the user application is programmed into address 0x1C0, and the initialization value of the stack pointer into address 0x1C4. These two values are reprogrammed every bootloading cycle to the current application values.

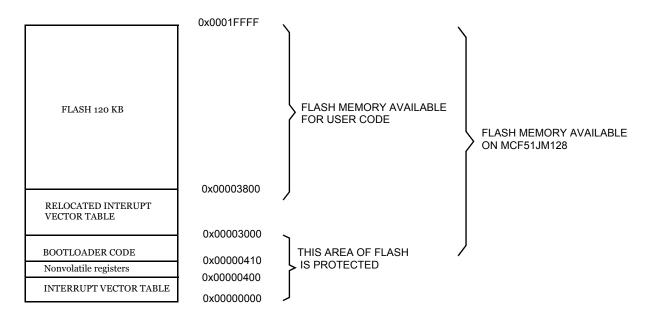

# 6.2 Version B (protected version)

This section describes features that are specific to the Cold Fire V1 implementation version B. The memory allocation is MCU specific, so the meaning of all variables is explained in this section in detail.

Figure 20 shows the memory allocation typical to the ColdFire V1 devices with the bootloader pre-programmed. For example, the MCF51JM128 device memory map includes:

- 128 KBof FLASH memory (\$0000000-\$0001FFFF)

- 16 KB of random access memory (RAM) (\$00800000-\$00803FFF)

- 16 bytes of nonvolatile registers (\$00000400-\$0000040F)

Figure 20. Simplified example of memory allocation in MCF51JM128 version B

## 6.2.1 Memory allocation

The bootloader code occupies the bottom of FLASH memory in the range 0x0410 to 0x3000 above the original interrupt vector table. This placement moves the start of memory space and for that reason it is necessary to modify the LCF file (see the MCU specific data sheet for details).

# 6.2.2 FLASH protection

By setting a FLASH protection register (FPROT), all address space under this address is protected from both intentional and unintentional erasing/rewriting. After the bootloader and the FLASH protection register are programmed into memory, the bootloader code is protected from unintentional modification by user code.

# 6.2.3 Example memory allocation

For example, the memory allocation for the ColdFire (V1) bootloaders is:

- \$84 Version 4, read command implemented (bit 7).

- \$rC16 System Device Identification Register (SDIDR) content (\$C16 for the JM Family), r (four top bits) is chip revision number reflecting the current silicon level.

- \$01 Number of reprogrammable memory areas.

- \$03800 Start address of the reprogrammable area.

- \$1FFFF End address of the reprogrammable area +1.

Developer's Serial Bootloader, Rev. 13

#### FC protocol, version 4, ColdFire (V1)

- \$03000 Address of the relocated interrupt vector table.

- \$001BC Start address of the MCU interrupt vector table.

- \$00400 Length of the MCU erase blocks.

- \$00080 Length of the MCU write blocks.

- 'MCF51JM128/USB' Identification string, zero terminated. Information to be displayed on the PC screen.

#### 6.2.4 Limitations

This section summarizes the limitations that must be considered when using the bootloader with the user application.

## 6.2.4.1 Memory occupied

This version of bootloader limits the beginning of the flash memory. For this reason, the user must modify the Linker Command File (LCF) and the boundary of the user flash start is moved to address 0x3800. The following code example shows the LCF file for a user application.

```

# Sample Linker Command File for CodeWarrior for the ColdFire MCF51JM128

# Memory ranges

MEMORY {

application (RX) : ORIGIN = 0x00003800, LENGTH = 0x0001C7FF //memory allocation

userram (RWX) : ORIGIN = 0x00800000, LENGTH = 0x00003FFF

}

```

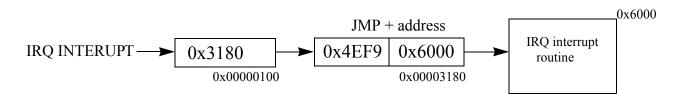

# 6.2.4.2 Delayed JMP instruction

The next limitation increases delays in the interrupts because there is a double jump instruction feature being used. The complete situation is described in the following figure:

Figure 21. The vector redirection using the JMP instruction

The following figure represents the interrupt vector table relocation explanation (ColdFire V1 - B):

Figure 22. Interrupt vector table relocation explanation (ColdFire V1 - B)

Developer's Serial Bootloader, Rev. 13

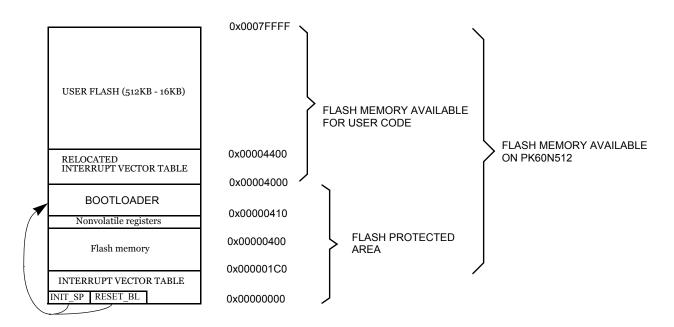

# FC protocol, version 5, Kinetis

This section describes features specific to the protocol Version 5 of the bootloader. This was created for a better compatibility with new Kinetis families of the MCUs. Protocol 4 for the ColdFire MCUs version B (protected version) is the basis for the Kinetis protocol version 5. The bootloader for the Kinetis MCUs includes an additional capability for CRC control. The memory allocation is MCU specific, so the meaning of all variables is explained in the following subsections.

Figure 23 shows the memory allocation typical to the Kinetis K60 devices with the bootloader preprogrammed. For example, the PK60N512 device memory map includes:

- 495 KB of FLASH memory (\$00004000 \$0007FFFF)

- 128 KB of random access memory (RAM) (\$001FFE0000-\$002001FFFF)

- 16 bytes of nonvolatile registers (\$00000400-\$0000040F)

- 444 bytes of user-defined vectors (\$00000000-\$000001B8)

Figure 23. Simplified example of memory allocation in PK60N512

#### 7.1 **Memory allocation**

The bootloader code occupies the first region of the FLASH memory (the lowest memory address space). This placement moves at the beginning of the available memory space and it is necessary to shift this address in the user application linker files (ICF file in IAR and in LCF file in CodeWarrior). The examples of the ICF and LCF linker files modification are as follows:

#### Kinetis K60

#### Example of modification ICF file in IAR6.4

```

// default linker file

define symbol __ICFEDIT_region_ROM_start__ = 0x00000000;

define symbol __code_start__ = 0x000000410;

// modified linker file for Kinetis K60 with 512KB flash memory

define symbol __ICFEDIT_region_ROM_start__ = 0x00004000;

define symbol __code_start__ = 0x000004400;

Example of modification LCF file in CodeWarrior 10.2

```

# # Default linker command file.

```

MEMORY {

m_interrupts (RX) : ORIGIN = 0x00000000, LENGTH = 0x000001E0

m_text (RX) : ORIGIN = 0x00000800, LENGTH = 0x00040000-0x00000800

m_data (RW) : ORIGIN = 0x1FFF8000, LENGTH = 0x00010000

m_cfmprotrom (RX) : ORIGIN = 0x00000400, LENGTH = 0x00000010

}

# Modified linker command file.

MEMORY {

m_interrupts (RX) : ORIGIN = 0x00000000, LENGTH = 0x000001E0

m_text (RX) : ORIGIN = 0x00004400, LENGTH = 0x00004000-0x00004400

m_data (RW) : ORIGIN = 0x1FFF8000, LENGTH = 0x00010000

m_cfmprotrom (RX) : ORIGIN = 0x00000400, LENGTH = 0x00010000

```

#### Kinetis KL25

#### Example of modification ICF file in IAR6.4

```

// default linker file

define symbol __ICFEDIT_region_ROM_start__ = 0x00000000;

define symbol __code_start__ = 0x000000410;

// modified linker file for Kinetis K60 with 512KB flash memory

define symbol __ICFEDIT_region_ROM_start__ = 0x00001000;

define symbol __code start = 0x0000010CO;

```

#### Example of modification LCF file in CodeWarrior 10.2

#### # Default linker command file.

```

MEMORY {

m_interrupts (RX) : ORIGIN = 0x00000000, LENGTH = 0x000001E0

m_text (RX) : ORIGIN = 0x00000800, LENGTH = 0x00010000-0x00000800

m_data (RW) : ORIGIN = 0x1FFF8000, LENGTH = 0x00010000

m_cfmprotrom (RX) : ORIGIN = 0x00000400, LENGTH = 0x00000010

}

# Modified linker command file.

MEMORY {

m_interrupts (RX) : ORIGIN = 0x00000000, LENGTH = 0x000001E0

m_text (RX) : ORIGIN = 0x000010C0, LENGTH = 0x00010000-0x000010C0

m_data (RW) : ORIGIN = 0x1FFF8000, LENGTH = 0x00010000

m_cfmprotrom (RX) : ORIGIN = 0x1FFF8000, LENGTH = 0x00010000

m_cfmprotrom (RX) : ORIGIN = 0x00000400, LENGTH = 0x00000010

```

Developer's Serial Bootloader, Rev. 13

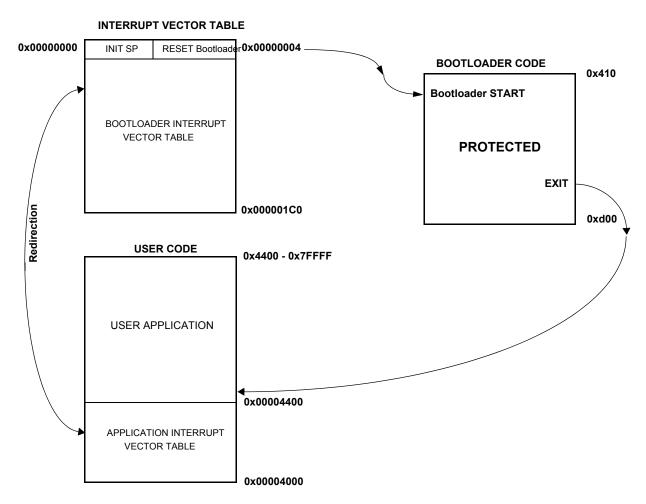

# 7.2 Interrupt vector table redirection

The FLASH block protection technique also protects the interrupt vector table from being overwritten, so some method must be used to relocate these vectors to the different locations. To do this, the bootloader user table is used.

The boundary where the flash memory begins is moved to address of first unprotected region of flash memory (0x00004000 for Kinetis K60 with 512 KB flash memory) because below this section of memory the protected bootloader is placed.

# 7.3 FLASH protection

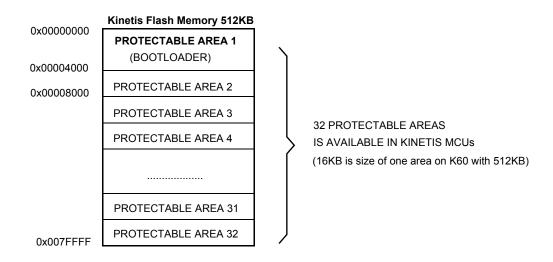

The Kinetis MCU supports flash protection using four 8-bit registers allowing 32 protectable regions. Each bit in these four registers protects a 1/32 region of the program flash memory. For example, for the Kinetis K60 with 512 KB flash memory, the smallest protected area is 16 KB. For the bootloader purposes, protection area of the first flash memory block between addresses \$00000000-\$00003FFF by Kinetis K60 with 512 KB is used.

The following figure represents the system of flash memory protection in Kinetis MCUs:

Figure 24. System of flash memory protection in Kinetis MCUs

# 7.4 Example of IDENT command

Example of the memory allocation for the Kinetis K60 bootloader are as follows:

• \$C8 - Version 5, read command implemented (bit 8), CRC enabled (bit 7)

- \$r14A -System Device Identification Register (SDID) content (\$14A for the K60 Family), r(13-16 bits) is the chip revision number reflecting the current silicon level

- \$01 Number of reprogrammable memory areas

- \$0004400 Start address of the reprogrammable area

- \$007FFFF End address of the reprogrammable area

- \$0000000 Address of the original vector table (1KB)

- \$0004000 Address of the new vector table (1KB)

- \$00400 Length of the MCU erase blocks

- \$0080 Length of the MCU write blocks

#### 7.5 Software reset

If the bootloader must quit and run user code, an MCU reset operation is intentionally executed by using the system reset sequence bit in register AIRCR (Application Interrupt and Reset Control Register). During bootloader startup, the System Reset Status (SRS) register is tested. If a power-on-reset is not detected, the user code starts instead of the bootloader code. This allows a transparent operation of all other resets with only a short additional delay caused by testing of the SRS register.

# 7.6 Kinetis system limitations

This section summarizes the limitations that must be considered, when using the bootloader with the user application.

# 7.6.1 Memory occupied

This version of the bootloader limits the beginning of the flash memory. Due to this, there must be a modified command linker file (ICF) for the target application and the memory boundary of the user flash start moved to an address under protected region (for example to address \$4400 by K60).

Developer's Serial Bootloader, Rev. 13

The following figure shows the interrupt vector table relocation for Kinetis K60 MCU:

Figure 25. Interrupt Vector Table Relocation Explanation for Kinetis (Version 5)

# 7.7 Correct setting of configuration file

Bootloader configuration file *bootloader\_cfg.h* offers a new feature to the users with using predefined configuration files for many of Kinetis evaluation boards and also allows the user to create any specific configuration.

Configuration file bootloader cfg.h (for example using predefined configuration for TOWER K60 board)

```

#ifdef KINETIS_K

#include "AN2295_TWR_K60_cfg.h"

#endif

```

For the correct function of the bootloader must be defined the following macros (configuration file AN2295 TWR K60 cfg.h):

/\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

Developer's Serial Bootloader, Rev. 13

```

/** USER SETTINGS OF KINETIS MCU */

/** Kinetis ARM Cortex-M4 model */

//K10 50MHz K11 50MHz K12 50MHz K10 72MHz K10 100MHz K10 120MHz

//K20 50MHz K21 50MHz K22 50MHz K20 72MHz K20 100MHz K20 120MHz

//K30 72MHz K30 100MHz

//K40 72MHz K40 100MHz

//K50 72MHz K51 72MHz K50 100MHz

//K60 100MHz K60 120MHz

//K70 120MHz

/** Kinetis ARM Cortex-M0+ model */

//KL0 48MHz

//KL1 48MHz

//KL2 48MHz KL25 48MHz

#define KINETIS MODEL K60 100MHz

/* in the case of using USB VIRTUAL SERIAL LINK you must activate No break TRIM CHECKBOX in

the master AN2295 PC Application */

^{\prime\star} the break impulse is replaced by using only 9 bits zero impulse ^{\star\prime}

// BREAK IMPULSE

// ZERO IMPULSE

|START| |0| |0| |0| |0| |0| |0| |0| |0| |STOP|

#define BOOTLOADER SHORT TRIM 1

Kinetis flash memory can be defined in different sizes and supported sizes are 32, 64, 128,

256, 512 and 1024 KBytes.

#define KINETIS_FLASH FLASH_512K

Following define determines if the bootloader code will be protected or not (protection is

recommended). First section of the flash will be protected (protected size = flash size / 32).

protection enabled - 1 , protection disabled - 0

\#define BOOTLOADER FLASH PROTECTION 1

Flash write access allows change mode of access to flash memory. Each model of MCU can support

different write access. Supported write access macros are defined as follows:

FLASH WRITE ACCESS LONG - 32 Bytes

FLASH WRITE ACCESS PHRASES - 64 Bytes

FLASH_WRITE_ACCESS_DOUBLE_PHRASES - 128 Bytes

#define FLASH WRITE ACCESS FLASH WRITE ACCESS PHRASES

Address of base pointer to actual used UART module

#define BOOT_UART_MODULE UART2 BASE PTR

Range of UART baudrates is between (9600 - 115200 Baud)

#define BOOT_UART_BAUD_RATE 115200

Address of peripheral base pointer for GPIO port (number of GPIO port shared with UART module)

#define BOOT_UART_GPIO_PORT PORTE BASE PTR

Setting of multiplexer for UART alternative of the pin

#define BOOT PIN UART ALTERNATIVE 3

Setting of multiplexer for GPIO alternative of the pin

#define BOOT PIN GPIO ALTERNATIVE 1

```

Developer's Serial Bootloader, Rev. 13

Freescale Semiconductor

35

#### FC protocol, version 5, Kinetis

```

Number of UART & GPIO pin for receiver (Rx)

#define BOOT UART GPIO PIN RX

Number of UART & GPIO pin for transmitter (Tx)

#define BOOT_UART_GPIO_PIN_TX

/*********************

/* Actual used PIN reset setting */

#define BOOT PIN ENABLE PORT BASE PORTC BASE PTR

#define BOOT PIN ENABLE GPIO BASE PTC BASE PTR

#define BOOT PIN ENABLE NUM

Following macros allows using of voluntary bootloader features:

Read command feature allows to check the flash memory.

#define BOOTLOADER ENABLE READ CMD 1

Watchdog timer can be enabled or disabled.

#define BOOTLOADER INT WATCHDOG

Verification of memory without CRC functions

#define BOOTLOADER ENABLE VERIFY

Verification of memory with CRC functions

#define BOOTLOADER CRC ENABLE

Autotrimming function allows to calibrate internal oscillator of MCU. If these feature is not

enabled user must define your own clock initialization or trimming of internal oscillator.

\verb|#define BOOTLOADER_AUTO_TRIMMING|

This feature allows using external pin for the bootloader starting

#define BOOTLOADER PIN ENABLE

/**********************************

/** CALIBRATION OF BOOTLOADER TRIM SETTINGS */

Address of flex timer base pointer

#define BOOT CALIBRATION TIMER FTM0 BASE PTR

Address of GPIO PORT base pointer

#define BOOT CALIBRATION GPIO PORT PTE BASE PTR

```

# 7.8 Quick guide: How to prepare the user Kinetis application for AN2295 bootloader

There are three limitations that must be taken care to modify the user application to be ready to run with AN2295 bootloader:

1. Linker File: The user application has to be moved above the bootloader code. The following rules inform where to move the user application:

- The MCU with bigger/equal flash than 64 KB (2048 B flash protection block): In this case

the start of the user application should start on the second protection block plus vector table

size. The vector table basically should be placed on the start of second protection block.

- The MCU with smaller flash than 64KB: In this case the user application should start on 0x800 with interrupt vectors and the application follows above the interrupt table.

- To modify linker file in more detail, see Memory allocation.

- 2. Flash configuration registers: The configuration of Flash (protection, security and others) is placed in Kinetis on address 0x400 because this address is placed in area of bootloader code, it should be removed definition of these registers from the user application.

- 3. VTOR register: Some user applications setup the VTOR(Vector Table Offset Register) register on startup with default value (0x0000), so the configuration of this register could be removed or updated to point to currently used vector table (In general case is the first byte of user application).

## 7.9 Using Kinetis bootloader for MQX based application

Kinetis bootloader can be used for programming of MQX based application. This topic explains what has to be done in MQX application to be ready for use with AN2295 bootloader.

The following steps are similar to the user application described in the Quick guide: How to prepare the user Kinetis application for AN2295 bootloader section, modification of VTOR register does not required by MQX based application.

The following two things must be updated in the MQX project:

- 1. Linker File: In the linker file of MQX the situation is similar to bare metal user application. The MQX application has to be moved above the AN2295 bootloader code. The MQX Linker file is using as standard linker definition as own some. For example the updated lines from Linker file for K60N512 and IAR6.4 tool:

- define symbol \_\_ICFEDIT\_intvec\_start\_\_ = 0x00004000;

- define symbol ICFEDIT region ROM start = 0x00004000;

- define exported symbol \_\_INTERNAL\_FLASH\_BASE = 0x00004000;

- define exported symbol \_\_VECTOR\_TABLE\_ROM\_START = 0x00004000;

- 2. Flash configuration registers: The setting of the flash configuration registers is simpler in MQX application than in general bare metal application. It is enough to define one MQX macro:

- #define BSPCFG\_ENABLE\_CFMPROTECT 0

#### NOTE

There could be with disabling the CFMPRROTECT with some BSP, but this should be solved individually.

# 8 MCU slave software

This section provides a detailed description of the five typical M68HC(S)08, Cold Fire V1 and Kinetis bootloader implementations. All code is written in assembly language. Several selected targets and different features are described in the following table:

\_

Table 2. Target implementation comparison

| MCU Family                                       | FLASH<br>Memory Use<br>(in Bytes) | Clock Source                                                   | ROM<br>Routines<br>Usage     | Calibration<br>Conducted | SCI                                  | FLASH<br>Erase<br>Page Size<br>(in Bytes) | FLASH<br>Program<br>Page Size<br>(in Bytes) |

|--------------------------------------------------|-----------------------------------|----------------------------------------------------------------|------------------------------|--------------------------|--------------------------------------|-------------------------------------------|---------------------------------------------|

| MC68HC908AP<br>AP8/AP16/<br>AP32/AP64            | 592                               | 32768 Hz XTAL or external clock.                               | Yes,<br>different<br>version | No                       | Hardware                             | 512                                       | 64                                          |

| MC68HC908AB/AS/AZ<br>AB32/AS32/AZ32<br>AS60/AZ60 | 640                               | 4.9152MHz XTAL                                                 | No                           | No                       | Hardware                             | 128                                       | 64                                          |

| MC68HC908EY<br>EY16                              | 384                               | ICG                                                            | Yes                          | Yes                      | Hardware                             | 64                                        | 32                                          |

| MC68HC908GP<br>GP32                              | 512                               | 32768 Hz XTAL or external clock.                               | No                           | No                       | Hardware                             | 128                                       | 64                                          |

| MC68HC908GR<br>GR4/GR8/GR16<br>GR8A/GR16A        | 320                               | 32768 Hz XTAL<br>or external clock;<br>8MHz XTAL<br>(A Family) | Yes                          | No                       | Hardware                             | 64                                        | 32                                          |

| MC68HC908GT<br>GT8/GT16                          | 384                               | ICG                                                            | Yes                          | Yes                      | Hardware                             | 64                                        | 32                                          |

| MC68HC908GZ<br>GZ8/GZ16                          | 512                               | 8 MHz XTAL                                                     | Yes                          | No                       | Hardware                             | 64                                        | 32                                          |

| MC68HC908GZ<br>GZ60                              | 512                               | 8 MHz XTAL                                                     | No                           | No                       | Hardware                             | 128                                       | 64                                          |

| MC68HC908JK/JL<br>JK1/JL1/<br>JK3/JL3            | 395                               | XTAL, RC<br>oscillator or ext.<br>source                       | Yes                          | Yes                      | Software,<br>single-wire<br>possible | 64                                        | 32                                          |

| MC68HC908JK/JL<br>JK8/JL8                        | 384                               | 4.9152MHz XTAL                                                 | Yes,<br>different<br>version | No                       | Hardware                             | 64                                        | 32                                          |

| MC68HC908JW<br>JW32                              | 1968                              | 4MHz or 6MHz<br>XTAL or resonator                              | Yes                          | N/A                      | USB2.0                               | 512                                       | 64                                          |

| MC68HC908LB<br>LB8                               | 384                               | ICG                                                            | Yes                          | Yes                      | Software,<br>single-wire<br>possible | 64                                        | 32                                          |

| MC68HC908LJ<br>LJ12/<br>LJ/LK24                  | 324                               | 32768 Hz XTAL or external clock.                               | Yes,<br>different<br>version | No                       | Hardware                             | 128                                       | 64                                          |

| MC68HC908KX<br>KX2/KX8                           | 384                               | ICG                                                            | Yes                          | Yes                      | Hardware                             | 64                                        | 32                                          |

| MC68HC908MR<br>MR8                               | 461                               | PLL with XTAL<br>(4 MHz)                                       | No                           | No                       | Hardware                             | 64                                        | 32                                          |

| MC68HC908MR<br>MR16/MR32                         | 461                               | PLL with XTAL<br>(4 MHz)                                       | No                           | No                       | Hardware                             | 128                                       | 64                                          |

Table 2. Target implementation comparison (continued)

| MCU Family                                                                          | FLASH<br>Memory Use<br>(in Bytes) | Clock Source         | ROM<br>Routines<br>Usage | Calibration<br>Conducted | SCI                                  | FLASH<br>Erase<br>Page Size<br>(in Bytes) | FLASH<br>Program<br>Page Size<br>(in Bytes) |

|-------------------------------------------------------------------------------------|-----------------------------------|----------------------|--------------------------|--------------------------|--------------------------------------|-------------------------------------------|---------------------------------------------|

| MC68HC908QB<br>QB4/QB8                                                              | 362/302                           | QB/QC ICG            | Yes                      | Yes/No                   | Hardware                             | 64                                        | 32                                          |

| MC68HC908QC<br>QC8/QC16                                                             | 387/323                           | QB/QC ICG            | Yes                      | Yes/No                   | Hardware                             | 64                                        | 32                                          |

| MC68HC908QT/QY<br>QT1/QT4/<br>QY1/QY4                                               | 320                               | Simpler ICG          | Yes                      | Yes                      | Software,<br>single-wire<br>possible | 64                                        | 32                                          |

| MC68HC908SR<br>SR12                                                                 | 512                               | 32768 Hz XTAL        | No                       | No                       | Hardware                             | 128                                       | 64                                          |

| MC9S08AW<br>HCS08AW32/48/64                                                         | 576                               | HCS08 ICG            | No                       | Yes                      | Hardware                             | 512                                       | 64                                          |

| HCS08AC8<br>HCS08AC16<br>HCS08AC32<br>HCS08AC48<br>HCS08AC60                        | 432                               | HCS08 ICG            | No                       | Yes                      | Hardware                             | 512                                       | 64                                          |

| HCS08AC128                                                                          | 694                               | HCS08 ICG            | No                       | Yes                      | Hardware                             | 512                                       | 128                                         |

| MC9S08GB/GT<br>HCS08GB/GT32<br>HCS08GB/GT60                                         | 576                               | HCS08 ICG            | No                       | Yes                      | Hardware                             | 512                                       | 64                                          |

| HCS08QE4<br>HCS08QE8<br>HCS08QE16<br>HCS08QE32                                      | 432                               | HCS08 ICG            | No                       | No                       | Hardware                             | 512                                       | 64                                          |

| MC9S08QG<br>HCS08QG4/8                                                              | 576                               | HCS08 ICG            | No                       | No (HW)<br>Yes (SW)      | Hardware<br>Software                 | 512                                       | 64                                          |

| MC9S08RX<br>HCS08RD/RG/RE8<br>HCS08RD/RG/RE16<br>HCS08RD/RG/RE32<br>HCS08RD/RG/RE60 | 335                               | 16MHz XTAL           | No                       | No                       | Hardware                             | 512                                       | 64                                          |

| HCS08JM32<br>HCS08JM60                                                              | 6000                              | 12MHz external clock | No                       | No                       | USB 2.0                              | 512                                       | 64                                          |

| MCF51JM64<br>MCF51JM128                                                             | 1108                              | S08 MCGV3            | No                       | No                       | Hardware                             | 1024                                      | 128                                         |

| MCF51QE32<br>MCF51QE64<br>MCF51QE128                                                | 1104                              | S08 ICSV3            | No                       | No                       | Hardware                             | 1024                                      | 128                                         |

| MCF51CN64<br>MCF51CN128                                                             | 1132                              | MCG                  | No                       | No                       | Hardware                             | 1024                                      | 128                                         |

Table 2. Target implementation comparison (continued)

| MCU Family                                         | FLASH<br>Memory Use<br>(in Bytes)      | Clock Source         | ROM<br>Routines<br>Usage | <b>Calibration</b><br><b>Conducted</b> | SCI      | FLASH<br>Erase<br>Page Size<br>(in Bytes) | FLASH<br>Program<br>Page Size<br>(in Bytes) |

|----------------------------------------------------|----------------------------------------|----------------------|--------------------------|----------------------------------------|----------|-------------------------------------------|---------------------------------------------|

| MCF51AC128<br>MCF51AC256                           | 1116                                   | MCG                  | No                       | No                                     | Hardware | 1024                                      | 128                                         |

| MCF51AG96<br>MCF51AG128                            | 1120                                   | ICS                  | No                       | No                                     | Hardware | 1024                                      | 128                                         |

| MCF51EM128<br>MCF51EM256                           | 1284                                   | ICS                  | No                       | No                                     | Hardware | 1024                                      | 128                                         |

| MCF51JM64<br>MCF51JM128                            | 1116                                   | MCG                  | No                       | No                                     | Hardware | 1024                                      | 128                                         |

| MCF51JM64<br>MCF51JM128                            | 8000                                   | 12MHz external clock | No                       | No                                     | USB 2.0  | 1024                                      | 128                                         |

| K10N1M0<br>K10N512<br>K10N256<br>K10N128<br>K10N64 | 32768<br>16384<br>8192<br>4096<br>2048 | MCG                  | No                       | No                                     | Hardware | 2048                                      | 128                                         |

| K20N512<br>K20N256<br>K20N128<br>K20N64<br>K20N32  | 16384<br>8192<br>4096<br>2048<br>1024  | MCG                  | No                       | No                                     | Hardware | 2048                                      | 128                                         |

| K30N512<br>K30N256                                 | 16384<br>8192                          | MCG                  | No                       | No                                     | Hardware | 2048                                      | 128                                         |

| K40N512<br>K40N256<br>K40N128                      | 16384<br>8192<br>4096                  | MCG                  | No                       | No                                     | Hardware | 2048                                      | 128                                         |