### Freescale Semiconductor Application Note

AN2349 Rev. 1, 11/2004

# MPC8260 Reset and Configuration Word

by Paul Genua, P.E. NCSG Field Applications Freescale Semiconductor, Inc.

This application note describes how to design for the 82xx Hardware Configuration Word fetch through programmable logic, as opposed to the EEPROM originally described in the *MPC8260 PowerQUICC II*<sup>TM</sup> User's Manual.

## **1** Introduction

With the advent of the MPC8260, Freescale Semiconductor has introduced a new method for providing the processor with initial hardware configuration data. Upon Power-On-Reset (POR) the 82xx is designed to fetch a 32 bit word from the 60x bus in four 8-bit accesses. Though this was originally intended to be provided via non-volatile memory, such as described in the 82xx databook, it is possible to provide the hardware configuration word through a PLD or FPGA located on the 60x bus. This allows the user to change the hardware configuration word without using the same NV-RAM for both boot code and hardware configuration word storage. This document is intended to give the designer examples of different possibilities for hardware configuration of the 82xx through programmable logic.

## 2 MPC8260 Hardware Configuration Sequence

As described in the processor reference manual, assertion of Power-On-Reset (POR) starts the power-on-reset flow and

### © Freescale Semiconductor, Inc., 2004. All rights reserved.

### Contents

| 1. | Introduction                              |

|----|-------------------------------------------|

| 2. | MPC8260 Hardware Configuration Sequence 1 |

| 3. | MPC8620 Slave Configuration 4             |

| 4. | MPC8260 Master Configuration 5            |

| 5. | Sample Master Configuration VHDL Code 7   |

| 6. | Revision History 10                       |

### MPC8260 Hardware Configuration Sequence

initializes the 82xx. Upon deassertion of POR, the 82xx reads the state of ~RSTCONF. If ~RSTCONF is detected as a logic-high state upon deassertion of POR, then the 82xx becomes a configuration slave and waits for toggling of ~RSTCONF to latch in a hardware reset configuration word from its data bus. If ~RSTCONF is logic-low upon deassertion of POR, then the 82xx determines that it is a configuration master and then initializes accesses to fetch its hardware configuration word.

The Configuration word for the now master 82xx is accessed as four, byte-wide transfers to a memory located at CS0 on the 60x Bus. The hardware word is read, most significant byte first, from the most significant byte lane on the 82xx.

| Byte 0 Address | Byte 1 Address | Byte 2 Address | Byte 3 Address |

|----------------|----------------|----------------|----------------|

| 0x00           | 0x08           | 0x10           | 0x18           |

Table 1. MPC8260 Reset Word Accesses

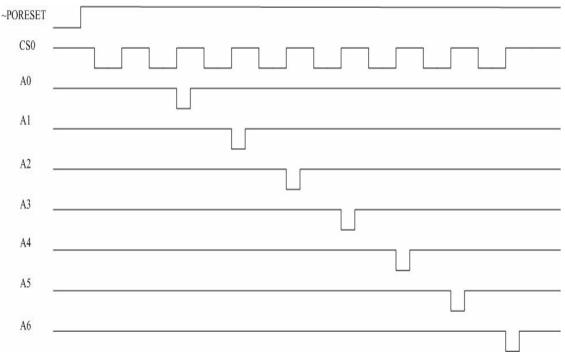

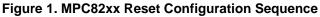

The master 82xx attempts to configure up to 7 slave 82xx devices. It continues reading 4 more bytes in order to form the configuration word of a first slave device. The Master 82xx then reassembles the word into one 32-bit word and drives the word onto the Slave's D[0-31] while toggling its RSTCONF as a strobe for latching in the hardware word. This will continue until the Master reads and configures slaves 1 through 7. See Figure 1 and Figure 2.

MPC8260 Hardware Configuration Sequence

Figure 2. Master Configuration of 1st Slave Device

The Hardware Configuration Word sequence will be initiated at every ~Hreset assertion.

**MPC8620 Slave Configuration**

# 3 MPC8620 Slave Configuration

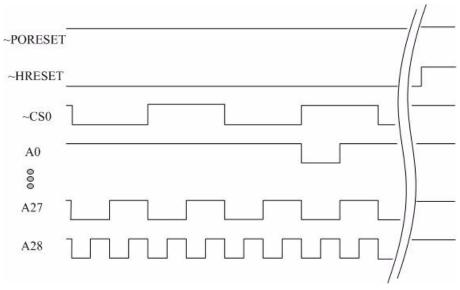

A system can be designed with a PLD emulating the intended master MPC8260, such that the MPC8260 in question can be configured as a slave. A typical schematic is shown in Figure 3.

Figure 3. MPC8260 Slave Configuration

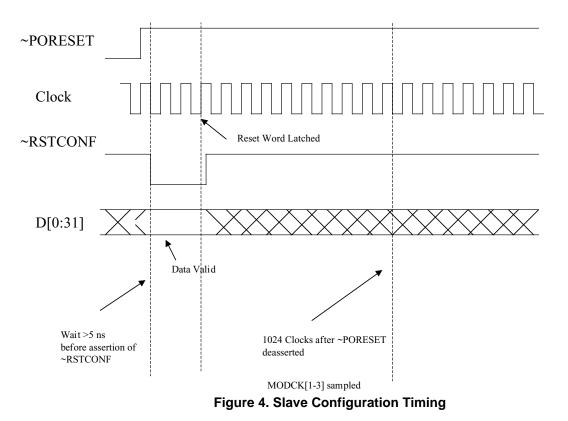

The PLD, in the slave configuration mode, will need to drive the whole configuration word onto the 82xx's data bus while toggling the ~RSTCONF line. Note that the 82xx needs a minimum of 5ns from deassertion of ~PORESET to driving ~RSTCONF to ensure the part does not come up in master mode.

The slave 82xx then will latch the reset configuration word from the 60x bus on the rising edge of the system clock. If the ~RSTCONF pulse spans multiple clock cycles, then the value of the data bus on the last clock's rising edge will be the one used for the reset configuration word. Thus one must ensure the ~RSTCONF pulse is greater than a clock period plus setup/hold time.

The configuration process must be completed before the MODCK pins are sampled by the processor (1024 clock cycles after ~PORESET is deasserted). If ~RSTCONF is not toggled by 1024 clocks after deassertion of ~PORESET, then the 8260 will boot with the default configuration as described in the reference manual.

**MPC8260 Master Configuration**

### 4 MPC8260 Master Configuration

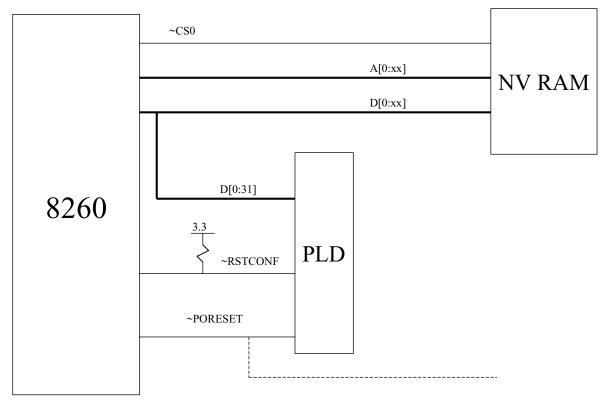

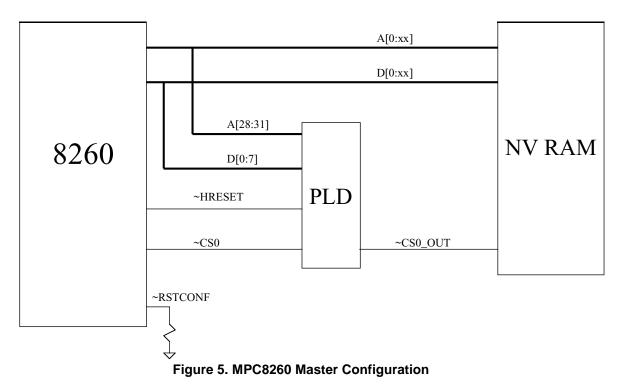

It may be desirable to design a system in which a PLD is used to emulate the intended EPROM for 82xx Master Configuration Setup. In such a design, the PLD would sit on the bus between the 8260 and nonvolatile memory, in effect intercepting Chip Select 0 (CS0) during the configuration phase and passing CS0 through to NV-RAM during normal operation.

### **MPC8260 Master Configuration**

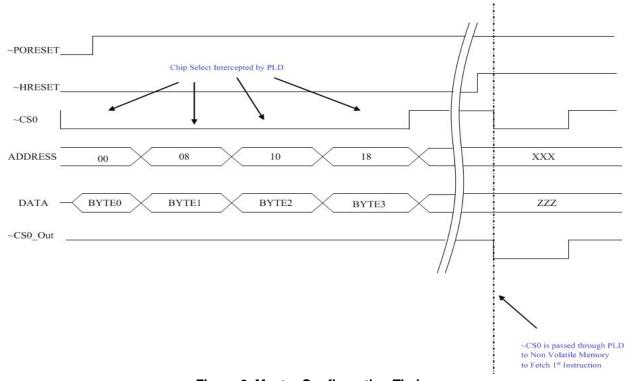

The 82xx, in Master configuration mode, will fetch the hardware configuration word from ~CS0 in four, byte-wide transfers. The PLD will act as a 4-byte device, to be accessed on ~CS0. If the master is not used to configure slave devices, only addresses A[27:28] are necessary at the PLD. Since the four configuration bytes are located at addresses 0x00, 0x08, 0x10, and 0x18, this would save pins on the external device. In the PLD logic we are able to use ~HRESET AND'ed with CS0 to select the PLD's register for the hardware configuration word since ~HRESET is always asserted during the configuration process.

Sample Master Configuration VHDL Code

Figure 6. Master Configuration Timing

### 5 Sample Master Configuration VHDL Code

File Name: master.vhd

Rev: 0.0

Author: Paul Genua

This code is meant to provide a hardware configuration word of 0x0C820205 to an MPC8260 configuration master during the boot-up sequence.

CS0 and HRESETN are used to determine that the configuration word is to be provided. In the absence of HRESETN low, CS0\_IN is passed through the PLD to CS0\_OUT which is connected to NVRAM.

MPC8260 Reset and Configuration Word, Rev. 1

```

Sample Master Configuration VHDL Code

```

```

-- CS0 output from 8260

: out STD LOGIC;

cs0 out

-- CS0 output from PLD to NVRAM

data860 out p: out STD LOGIC VECTOR (7 downto 0);

-- 8260 DataBus

: in STD LOGIC VECTOR (4 downto 0)

addr860

-- 8260 Address Bus

);

end component;

end pkgmaster;

library ieee;

use ieee.std logic 1164.all;

entity master is

port (

hresetn : in STD_LOGIC;

-- hresetn: 8260 hard reset

cs0 in

: in STD LOGIC;

-- CS0 output from 8260

cs0 out

: out STD LOGIC;

-- CS0 output from PLD to NVRAM

data860 out p: out STD LOGIC VECTOR (7 downto 0);

-- 8260 DataBus

: in STD LOGIC VECTOR (4 downto 0)

addr860

-- 8260 Address Bus

);

end master;

```

```

architecture master_arch of master is

```

```

signal data860 z: STD LOGIC VECTOR (7 downto 0);

signal data860_in: STD_LOGIC_VECTOR (7 downto 0);

signal data cs0 : std logic vector (7 downto 0);

signal csn d0 : std logic;

signal wr_cs0 : boolean;

begin

-- CS0 Process

-- When Hreset = 1 CS0 in gets passed through to CS0 out for FLASH

-- When resetting, acts as ROM & outputs 8260 HRESET config

-- HRESET Word is four byte accesses at 0x00, 0x08, 0x10, 0x18

process begin

if cs0 in = '0' then

if hresetn= '1' then

cs0 out <= '0';

wr cs0 <= false ;</pre>

else

cs0 out <='1';

wr cs0 <= true;</pre>

case addr860 is

when "00000" =>

data cs0 <= "00001100";</pre>

when "01000" =>

data cs0 <= "10000010";</pre>

when "10000" =>

data_cs0 <= "00000010";</pre>

when "11000" =>

```

**Revision History**

```

data_cs0 <= "00000101";</pre>

```

when others=>

data\_cs0 <= "00000000";</pre>

end case;

end process;

data860\_out\_p <= data\_cs0 when wr\_cs0 else (others => 'Z');

end master\_arch;

### 6 Revision History

### **Table 2. Revision History**

| Revision | Release Date | Changes                                                                                                                                                                                |

|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        |              | Updated Figure 2, Figure 5, and Figure 6. Added Figure 1. Updated text in Section 2,<br>"MPC8260 Hardware Configuration Sequence," in order to clarify the Master Configuration cycle. |

| 0        | 10/2002      | Initial release                                                                                                                                                                        |

**Revision History**

### THIS PAGE INTENTIONALLY LEFT BLANK

### How to Reach Us:

#### Home Page: www.freescale.com

email: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Technical Information Center 3-20-1, Minami-Azabu, Minato-ku Tokyo 106-0047 Japan 0120 191014 +81 3 3440 3569 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@ hibbertgroup.com

AN2349 Rev. 1 11/2004 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The PowerPC name is a trademark of IBM Corp. and is used under license. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2004.