# **FPGA MDR Interface for the MRC6011**

A VHDL Reference Design for the ROBIN Motherboard

By Dejan Minic

This application note describes how to implement the MRC6011 MDR antenna bus interface and the supporting ROBIN system design on the Xilinx<sup>®</sup> field-programmable gate array (FPGA) using VHDL. VHDL is an acronym that stands for *VHSIC hardware description language*. VHSIC is yet another acronym that stands for *very high speed integrated circuits*.

For the project reported in this document, the ROBIN motherboard was used for development and testing, and you should use this board if you have access to it. However, other development boards can be used.

This is one of two application notes that describe an FPGA reference design code for the ROBIN motherboard. The other application note is AN2889, *FPGA System Bus Interface for the MPC8260: A VHDL Reference Design for the ROBIN Motherboard.* This application note and the zip file of code that accompanies it are available at the website listed on the back cover of this document.

#### CONTENTS

| 1   | Baseband System Example                       | 2  |

|-----|-----------------------------------------------|----|

| 2   | MDR Bus                                       | 3  |

| 2.1 | MDR Bus Signals                               | 3  |

| 2.2 | MDR Signal Waveform                           | 4  |

| 3   | System Bus                                    |    |

| 4   | VHDL Code For the FPGA-MDR Interface          | 5  |

| 4.1 | Top-Level Architecture of the Interface       | 5  |

| 4.2 | Control Logic                                 |    |

| 4.3 | PowerQUICC II Logic Module                    |    |

| 4.4 | PowerQUICC II Data Multiplex                  | 21 |

| 4.5 | BlockRAM Storage Memory                       |    |

| 5   | FPGA Memory Space                             |    |

| 5.1 | Digital Clock Management (DCM) Logic          | 24 |

| 5.2 | JTAG Logic                                    |    |

| 5.3 | MDR Logic                                     | 28 |

| 5.4 | UCF file 3                                    | 0  |

| 5.5 | Registering External Signals at the FPGA IOBs | 30 |

| 6   | FPGA Operating Sequence                       |    |

| 6.1 | MPC8260 Programming Sequence                  | 32 |

| 7   | ROBIN Motherboard Configuration               | 35 |

| 8   | Integrated Software Environment (ISE)         |    |

|     | Tool Reports                                  | 36 |

| 8.1 | Synthesis Report                              | 36 |

| 8.2 | Map Report                                    | 36 |

| 8.3 | Place and Route (PAR) Report                  | 36 |

| 8.4 | Bitgen Report                                 |    |

| 9   | VHDL Code Listing                             | 37 |

| 10  | MPC8260 Code Listing                          | 37 |

band System Example

## **1** Baseband System Example

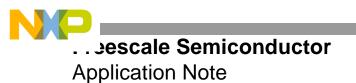

**Figure 1** illustrates the architecture of a generic ROBIN motherboard baseband system FPGA processor. The FPGA connects to external devices via the MPC8260 system bus. The data is exchanged and/or stored via the two internal memory structures. On the system bus, the MPC8260 processor can access either the control registers for FPGA/board configuration or all 128 KB of the FPGA internal storage BlockRAM memory. The control registers control the ROBIN motherboard settings and modes of operation. Additional space is allocated for custom registers integrated into a more complex system design. When the data is loaded into the FPGA, it is streamed via the multiplexed data router (MDR) bus to the MRC6011 processor.

Figure 1. Robin Motherboard Baseband FPGA System

## 2 MDR Bus

The MRC6011 is the first Freescale processor based on the reconfigurable compute fabric (RCF) technology. The MRC6011 device contains six RCF cores that compose a single homogeneous compute node. The device runs at up to 250 MHz and delivers a performance of 24 Giga complex correlations per second with 8 bits for I and Q. It has two external buses, the system bus and the multiplexed data router (MDR). The MDR is a bus interconnect that directs the input data to the input buffers of targeted RCF cores. The MDR receives data on two multiplexed data input (MDI) ports at a maximum rate of 400 MB per second. The MDI ports are 32-bit data buses with clock, data valid, and sync signals. The sync signal indicates the start of a backplane frame. The data can be captured on either the positive or negative edge of the MDI clock when the MDI data valid signal is asserted. The broadcast router can be configured to distribute data words to one or more RCF cores in a module.

The host can synchronize the multiplexed data to several RCF cores. The host uses the Release Input Buffer Reset (RIBR) signal to deassert the RCF core input buffer reset signal at the start of the next backplane frame in Sync mode.

In some applications, both MDR blocks receive the same data stream through one of the MDI ports. Either multiplexed data capture unit can be configured as the source for both broadcast routers, which distribute the timeslots in the multiplexed data stream according to their own configuration.

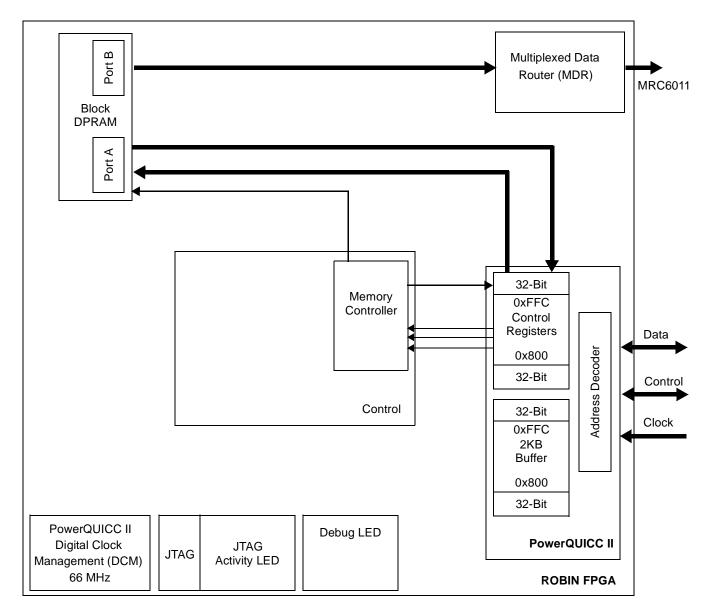

## 2.1 MDR Bus Signals

This reference design uses a total of 71 signals for the MDR bus communication, and each MDR bus has 36 total signals as shown in **Table 1**, and the MDR bus clock is shared between both MDR bus interfaces.

| •                                                                  | •                                                                                                                                                                                |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Type                                                        | Signals                                                                                                                                                                          |

| Control signals                                                    | fpga_mrc6011_data_valid1c<br>fpga_mrc6011_data_valid2c<br>fpga_mrc6011_clk1c<br>fpga_mrc6011_clk2c<br>fpga_mrc6011_fsync1c<br>fpga_mrc6011_fsync2c<br>fpga_mrc6011c_releaseibrst |

| Uni-direction data bus signals                                     | fpga_mrc6011_data1c<br>fpga_mrc6011_data2c                                                                                                                                       |

| MDR data valid signals                                             | fpga_mrc6011_data_valid1c<br>fpga_mrc6011_data_valid2c                                                                                                                           |

| Data clock signals                                                 | fpga_mrc6011_clk1c<br>fpga_mrc6011_clk2c                                                                                                                                         |

| Data frame signals to indicate the beginning of the new data frame | fpga_mrc6011_fsync1c<br>fpga_mrc6011_fsync2c                                                                                                                                     |

| Reset and set-up                                                   | fpga_mrc6011_releaseibrst                                                                                                                                                        |

Table 1. MDR Bus Signals in the FPGA Reference Design

**Figure 2** illustrates the interconnections between the MRC6011 and FPGA devices. The signal connection for the second MDR port is simply doubled, with the exception of the fpga\_mrc6011\_releaseibrst signal, which is shared between both MDR ports. For details on the MRC6011 and the MDR bus, consult the *MRC6011 Reference Manual*.

Figure 2. MDR Bus Signal Connection

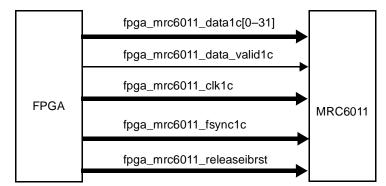

### 2.2 MDR Signal Waveform

Figure 3 illustrates the operation of the MDR bus. To initialize the MDR bus, the

fpga\_mrc6011\_releaseibrst reset is applied two frames before the data valid is asserted high. When the data valid is asserted, the FPGA can place the data on the data bus. The MRC6011 processor samples the data at either the rising or falling clock edge while the data valid signal is asserted high. When the data is loaded into the MRC6011, the data valid signal is cleared and the MRC6011 stops sampling data. To continue data streaming from the FPGA to the MRC6011, the data valid signal can be asserted again, but it should be aligned with the rising edge of the next frame sycn pulse.

Figure 3. MDR Signal Waveform

## 3 System Bus

The MPC8260 system bus is a flexible communication medium between the core and internal/external peripheral devices or other bus masters/slaves. The system bus provides 32-bit addressing for a 32-bit or 64-bit wide data base. The burst mode operation can transfer up to 256 bits of data in a four-beat burst. The system bus also supports 8-bit, 16-bit, and 32-bit data ports. Accesses of 1, 2, 3, and 4 bytes can be aligned or unaligned on 4-byte (word) boundaries. The 64-bit, 128-bit, 192-bit, and 256-bit accesses are supported as well. The address and data buses are set up to handle a one-level pipeline, synchronous transaction. The system bus operates in external and internal master modes. For our reference design, the UPM and system bus are configured as follows:

- 32-bit wide port and 32-bit addressing

- Synchronous, single-access transactions

- Single-Bus mode

For details on the system bus, signals used, MPC8260 UPM programming, and FPGA implementation consult AN2889, *FPGA System Bus Interface for the MPC8260: A VHDL Reference Design for the ROBIN Motherboard.*.

## 4 VHDL Code For the FPGA-MDR Interface

This section covers the top-level architecture of the FPGA-MDR interface, the FPGA control logic, PowerQUICC II logic, memory layout, and other aspects of the interface.

## 4.1 Top-Level Architecture of the Interface

The top level architecture is presented in **Figure 1**. The main components of the design are the MDR interface, the PowerQUICC II<sup>™</sup> interface, JTAG interface, FPGA internal memory register space, FPGA internal memory 4 KB buffer space, and FPGA internal memory BlockRAM data storage space.

### 4.1.1 Top Port Declaration

The top\_vhdl.vhd file contains definitions of all top-level ports of the system bus module. The top-level ports used in this design are as follows:.

fpga\_clock : in std\_logic; fpga reset : in std logic;

- fpga\_clock. An input clock connected to the FPGA primary clock pad. This pad is routed to the clock input of the digital clock manager (DCM).

- fpga\_reset. Connected to the reset switch on the ROBIN motherboard and resets the DCM module. In conjuction with the internal reset signal, this signal is the main reset signal to the internal FPGA components.

```

fpga_odyc_irq5_out: out std_logic;

fpga_dspc_irq5_out: out std_logic;

fpga_dspc_irq6_out: out std_logic;

fpga_pq2_irq4_out: out std_logic;

fpga_pq2_pd7_out: out std_logic;

```

• These interrupt lines connect to the MRC6011, MSC8102, and MPC8260 and can be used for various communication schemes among FPGA, MRC6011, MSC8102, and MPC8260.

```

fpga_pq2_clock : in std_logic;

fpga_pq2_csb : in std_logic;

fpga_pq2_rwb : in std_logic;

fpga_pq2_addr : in std_logic_vector (0 to 9);

fpga_pq2_data : inout std_logic_vector (0 to 31);

```

- fpga\_pq2\_clock. A system bus clock source to drive the PowerQUICC II interface logic.

- fpga\_pq2\_csb. A MPC8260 UPM chip select (chip enable) active low signal for FPGA internal memory.

- fpga\_pq2\_rwb. A MPC8260 UPM read/write signal. Logical "0" or low determines write and logical 1 or high determines read bus access.

- fpga\_pq2\_addr. Ten address lines used by the MPC8260 UPM for memory addressing.

- fpga\_pq2\_data. A data bus composed of 32 bidirectional data lines for use by the MPC8260 device.

```

fpga_pq2_trstb: in std_logic;

fpga_pq2_tms : in std_logic;

fpga_pq2_tdo : in std_logic;

fpga_pq2_tdi : in std_logic;

fpga_pq2_tck : in std_logic;

fpga_pq2_hreset: in std_logic;

```

These MPC8260 JTAG signals are used in this reference design only to display the PowerQUICC II JTAG activity on the board LED. These signals can be used to implement any custom JTAG controller or logic needed in a system.

```

fpga jtag conndsp tdi

: in std logic;

fpga_jtag_conndsp tdo

: out std logic;

fpga jtag conndsp commun : in std logic vector (0 to 3);

fpqa jtaq connmrc6011 tdi : in std loqic;

fpga jtag connmrc6011 tdo : out std logic;

fpga jtag connmrc6011 commun: in std logic vector (0 to 3);

fpga_jtag_dsp_a_tdi : out std_logic;

fpga_jtag_dsp_a_tdo : in std_logic;

fpga_jtag_dsp_a_commun : out std_logic_vector (0 to 3);

fpga_jtag_dsp_b_tdi : out std_logic;

fpga jtag dsp b tdo

: in std logic;

fpga_jtag_dsp_b_commun : out std_logic_vector (0 to 3);

fpga_jtag_dsp_c_tdi  : out std_logic;

fpga_jtag_dsp_c_tdo  : in std_logic;

fpga_jtag_dsp_c_commun  : out std_logic_vector (0 to 3);

fpga jtag mrc6011 a tdi : out std logic;

fpga jtag mrc6011 a tdo : in std logic;

fpga jtag mrc6011 a commun : out std logic vector (0 to 3);

fpga jtag mrc6011 b tdi : out std logic;

fpga jtag mrc6011 b tdo : in std logic;

fpqa jtaq mrc6011 b commun : out std logic vector (0 to 3);

: out std logic;

fpga jtag mrc6011 c tdi

fpga jtag mrc6011 c tdo

: in std logic;

fpga jtag mrc6011 c commun : out std logic vector (0 to 3);

: in std logic vector (0 to 2);

fpga jtag dipswdsp

: in std logic vector (0 to 2);

fpga jtag dipswmrc6011

```

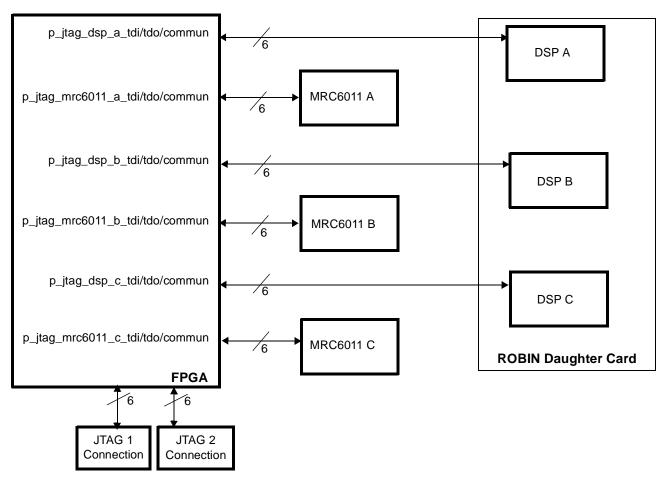

• The JTAG logic uses these signals to configure the JTAG chain. Six JTAG enabled devices connect to the FPGA, three MRC6011 and three MSC8102 devices. Each device has six signals for routing standard JTAG signals. In addition, there are two JTAG connectors for use by the JTAG master controller.

```

fpga_mrc6011_data1c : out std_logic_vector(31 downto 0);

fpga_mrc6011_data2c : out std_logic_vector(31 downto 0);

fpga_mrc6011_fsync2c : out std_logic;

fpga_mrc6011_fsync1c : out std_logic;

fpga_mrc6011_data_valid2c : out std_logic;

fpga_mrc6011_data_valid1c : out std_logic;

fpga_mrc6011_clk2c : out std_logic;

fpga_mrc6011_clk1c : out std_logic;

fpga_mrc6011_clk1c : out std_logic;

```

- fpga\_mrc6011\_data1c and fpga\_mrc6011\_data2c. Two 32-bit uni-directional buses used by the FPGA to stream MDR data to the MRC6011.

- fpga\_mrc6011\_fsync2c and fpga\_mrc6011\_fsync1c. Carry the MDR frame sync signals.

- fpga\_mrc6011\_data\_valid2c and fpga\_mrc6011\_data\_valid1c. Carry the MDR data valid signals to indicate when the MRC6011 processor should start sampling the MDR data.

- fpga\_mrc6011\_clk2c and fpga\_mrc6011\_clk1c. Provide the data sampling clock signals to the MRC6011 processor.

- fpga\_mrc6011c\_releaseibrst. Provides the reset release signal to the MDR port, and is used during MDR port initialization.

```

debug_mictor : out std_logic_vector(31 downto 0);

debug_led : out std_logic_vector(3 downto 0)

```

The debug\_mictor port consists of 32 debug lines routed to the P4 Mictor connector on the ROBIN motherboard. All 32 lines can be routed internally in the FPGA to any internal FPGA signal for probing/debugging. The debug\_led port consists of four lines that connect to four LEDs on the ROBIN motherboard. The four LEDs are marked as FPGA\_LED\_0 (D4), FPGA\_LED\_1 (D5), FPGA\_LED\_2 (D6), and FPGA\_LED\_3 (D7).

### 4.1.2 Internal Signals

All internal signals (wires) have a prefix of  $i_a$  and interconnect the modules and FPGA I/O pins. Other internal signals have a prefix of  $r_a$  to indicate that they are used as registers.

```

signal i_module_reset: std_logic;

signal r_jtag_reg : std_logic_vector(5 downto 0);

```

- i\_module\_reset. The main reset to all FPGA internal blocks, with the exception of DCM and the MPC8260 component. This line is active high and is driven by an inverted DCM lock signal ANDed with an MPC8260-accessible write reset register. This line is asserted either when the DCM is not locked or when the user manually resets the FPGA by writing to the FPGA configuration reset register via the MCP8260.

- r\_jtag\_reg. An internal bus reserved for future expansion of the reconfigurable JTAG chain.

```

signal i_clk1x_out : std_logic;

signal i_clkdv_out : std_logic;

signal i_clk2x_out : std_logic;

signal i_clk2x180_out: std_logic;

signal i_clkfx_out : std_logic;

signal i_dcm_lock_out: std_logic;

```

• The DCM uses these signals to provide various clock sources to the FPGA logic. Our reference design uses the i\_clkdv\_out clock source for the clock division capability of the DCM component. Other sources can be used. For example, use i\_clklx\_out for the clock source when frequency is not altered but the clock is de-skewed. Use i\_clk2x\_out for a de-skewed clock source with twice the input frequency.

# NP

#### Code For the FPGA-MDR Interface

```

signal i_sdram_dout : std_logic_vector(31 downto 0);

signal i_sdram_addra: std_logic_vector(14 downto 0);

signal i_sdram_ena : std_logic;

signal i_sdram_wea : std_logic;

signal i_sdram_addrb: std_logic_VECTOR(14 downto 0);

signal i_sdram_dinb : std_logic_VECTOR(31 downto 0);

signal i_sdram_doutb: std_logic_VECTOR(31 downto 0);

signal i_sdram_enb : std_logic;

signal i_sdram_web : std_logic;

signal i_sdram_web : std_logic;

signal i_sdram_a data: std_logic vector(31 downto 0);

```

• These signals connect the internal SDRAM (FPGA BlockRAM) component with other FPGA components. They can connect to the external SDRAM chip on the ROBIN motherboard.

```

signal i pq2 data out

: std logic vector (31 downto 0);

signal i_pq2_data in

: std logic vector (31 downto 0);

signal i pg2 ctrl rst

: std logic;

signal i pq2 ctrl sdram load : std logic;

signal i pq2 ctrl sdram unload : std loqic;

signal i pq2 ctrl sdram load done: std logic;

signal i pq2 ctrl sdram load done clr : std logic;

signal i pq2 ctrl sdram unload begin: std logic;

signal i pq2 ctrl sdram unload begin clr : std logic;

signal i pg2 ctrl simulation

: std logic;

signal i pq2 ctrl simulation on : std logic;

signal i_reg03_sdram_words : std_logic_vector(31 downto 0);

: std logic vector(9 downto 0);

signal i pg2mem addr

signal i pg2mem en

: std logic;

signal i pq2mem we

: std logic;

signal i pq2mem dout

: std logic vector(31 downto 0);

```

These signals carry the control logic from the MCP8260 interfaces to various locations in the internal FPGA logic:

- i\_pq2\_data\_out and i\_pq2\_data\_in. 32-bit output and input buses.

- i\_pq2\_ctrl\_rst. Issues a master internal FPGA reset signal.

- i\_pq2\_ctrl\_sdram\_load. Used by the main control state machine to select the SDRAM loading mode.

- i\_pq2\_ctrl\_sdram\_unload. Used by the main control state machine to select the SDRAM unloading mode.

- i\_pq2\_ctrl\_sdram\_load\_done and i\_pq2\_ctrl\_sdram\_unload\_begin. Trigger the internal memory controller and its state machine to begin loading/unloading data to/from FPGA memory.

- i\_pq2\_ctrl\_sdram\_load\_done\_clr and i\_pq2\_ctrl\_sdram\_unload\_begin\_clr. Internally generated FPGA signals to notify the FPGA memory controllers that loading and unloading of data is complete and the memory controllers should be temporarily disabled.

- i\_pq2\_ctrl\_simulation and i\_pq2\_ctrl\_simulation\_on. Reserved for additional unloading of data to the MRC6011 device.

- i\_reg03\_sdram\_words. A bus used by the FPGA memory access counter to count the number of MPC8260 memory read/writes. These signals connect to the MPC8260 memory-mapped read registers, providing debugging visibility into how many words are read or written in/out of the FPGA.

### 4.1.3 Debug Signals

The following signals are strictly for debugging and are routed to the Mictor connector P4 on the ROBIN motherboard. A Mictor-compatible logic analyzer can be used to sample and view these signals.

```

signal debug_addr : std_logic_vector (9 downto 0);

signal debug_ena : std_logic;

signal debug_wea : std_logic;

signal debug_ctrl_fsm : std_logic_vector(7 downto 0);

```

To simplify the design, the number of functional logic blocks is kept to minimum. When you add logical blocks for more complex designs, keep in mind that the design should be as modular and hierarchical as possible.

### 4.2 Control Logic

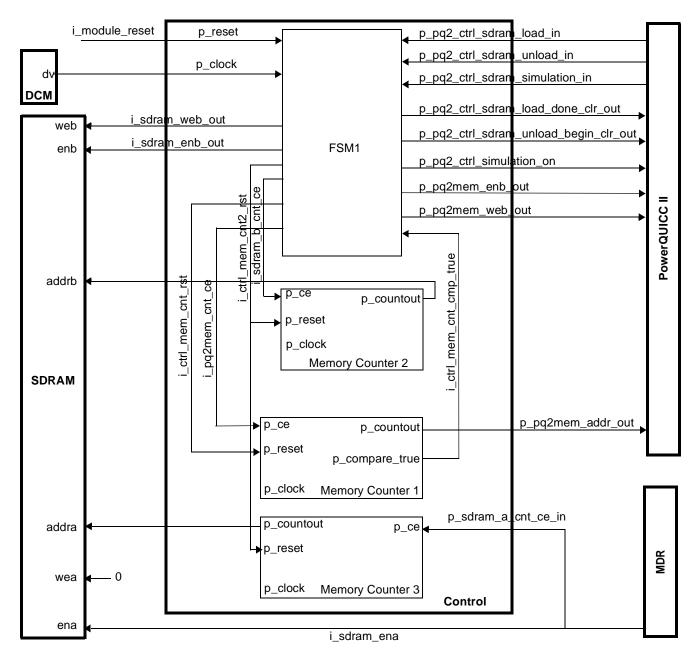

The control logic module is the brains of the FPGA architecture, which controls all FPGA modules. It uses the PowerQUICC II interface logic to receive configuration and operation instructions from the MPC8260 device and to send the FPGA status and debug information back to the MPC8260 (see **Figure 4**). The heart of the control module is the finite state machine (see **Figure 5**). Two smaller counter blocks serve as memory controllers for the two dual-ported memory blocks. The input and output port of the control logic is as follows:

| p_clock                                                                                                                                                                                             | : in std_logic;                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| p_reset                                                                                                                                                                                             | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_sdram_load_in                                                                                                                                                                            | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_sdram_unload_in                                                                                                                                                                          | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_simulation_in                                                                                                                                                                            | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_sdram_load_done_in                                                                                                                                                                       | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_sdram_load_done_clr_out                                                                                                                                                                  | : out std_logic;                                                                                                                                                                                                                                                                    |

| p_pq2_ctrl_sdram_unload_begin_in                                                                                                                                                                    | : in std_logic;                                                                                                                                                                                                                                                                     |

| p_pq2_ctrl_sdram_unload_begin_clr_out                                                                                                                                                               | : out std_logic;                                                                                                                                                                                                                                                                    |

| p_pq2_ctrl_simulation_on_out                                                                                                                                                                        | : out std_logic;                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                     |

| <pre>p_pq2mem_addrb_out<br/>p_pq2mem_enb_out<br/>p_pq2mem_web_out<br/>p_sdram_addrb_out<br/>p_sdram_enb_out<br/>p_sdram_web_out<br/>p_sdram_addra_out<br/>p_sdram_wea_out<br/>p_sdram_ena_out</pre> | <pre>: out std_logic_VECTOR(9 downto 0);<br/>: out std_logic;<br/>: out std_logic;<br/>: out std_logic_VECTOR(14 downto 0);<br/>: out std_logic;<br/>: out std_logic;<br/>: out std_logic_VECTOR(14 downto 0);<br/>: out std_logic;<br/>: out std_logic;<br/>: out std_logic;</pre> |

| <pre>p_pq2mem_enb_out<br/>p_pq2mem_web_out<br/>p_sdram_addrb_out<br/>p_sdram_enb_out<br/>p_sdram_web_out<br/>p_sdram_addra_out</pre>                                                                | <pre>: out std_logic;<br/>: out std_logic;<br/>: out std_logic_VECTOR(14 downto 0);<br/>: out std_logic;<br/>: out std_logic;<br/>: out std_logic_VECTOR(14 downto 0);</pre>                                                                                                        |

- p\_clock. The main clock tree fed from the DCM DV output (i\_clkdv) clock source.

- p\_reset. The main reset line to the block. It is primarily used to reset the main finite state machine. It is driven from the i\_module\_reset (global reset) line.

- The remaining signals control the finite state machine (see Figure 5).

- p\_pq2mem\_addrb\_out, p\_pq2mem\_enb\_out, and p\_pq2mem\_web\_out. Output ports to control the 4 KB buffer DPRAM in the PowerQUICC II logic block.

- p\_sdram\_addrb\_out, p\_sdram\_enb\_out, p\_sdram\_web\_out, p\_sdram\_addra\_out, p\_sdram\_wea\_out, and p\_sdram\_ena\_out. Output ports to control the dual-ported BlockRAM, which is 128 KB of FPGA internal storage memory.

#### Code For the FPGA-MDR Interface

• debug\_fsm. For debugging purposes only.

Figure 4. Control Logic Module

### 4.2.1 Memory Counter 1

Memory counter 1 is controlled by the FSM1 state machine and addresses the FPGA 4 KB buffer DPRAM in the PowerQUICC II logic block. The component has following input and output ports:

| p_clock        | : in std_logic;                     |

|----------------|-------------------------------------|

| p_reset        | : in std_logic;                     |

| p_ce           | : in std_logic;                     |

| p_countout     | : out std_logic_vector(9 downto 0); |

| p_compare_true | : out std_logic                     |

• p\_clock. A clock signal supplied from the i\_clkdv DCM clock source.

- p\_reset. Carries a reset signal to reset the addressing counter to 0. This reset signal is i\_ctrl\_mem\_cnt\_rst, and it is generated by the FSM1 state machine. The reset is asserted at FPGA initialization, at the beginning of the SDRAM load and unload memory operation sequence.

- p\_ce. Enables the address counter. This port connects to the i\_pq2mem\_cnt\_ce signal, which is controlled by the FSM1 state machine. This signal, and therefore the counter, is active during the SDRAM load and unload sequence. This address counter has address compare capability to detect when the address counter reaches the end of the 4 KB DPRAM address space.

- port p\_compare\_true. When the end of the address space is detected, this signal notifies the FSM1 state machine. When this signal is active, the SDRAM load and unload sequence in the FSM1 state machine completes, and the state machine is sent to the next state. The remaining port p\_countout is connected to the p\_addrb\_in port in the PowerQUICC II logical block via the i\_pq2mem\_addrb signal. This is a 10-bit bus carrying an address value to address port B of the 4 KB DPRAM. For details on memory control signal generation and the state machine, refer to Figure 5 and Table 2.

### 4.2.2 Memory Counter 2

Memory counter 2 is controlled by the FSM1 state machine and addresses the FPGA internal BlockRAM storage DPRAM. The component has following input and output ports:

| p_clock    | : in std_logic;                     |

|------------|-------------------------------------|

| p_reset    | : in std_logic;                     |

| p_ce       | : in std_logic;                     |

| p_countout | : out std_logic_vector(14 downto 0) |

- p\_clock. A clock signal supplied from the i\_clkdv DCM clock source.

- p\_reset. Carries a reset signal to reset the addressing counter to 0. This reset signal is i\_ctrl\_mem\_cnt2\_rst, and it is generated by the FSM1 state machine. The reset is asserted at FPGA initialization and the beginning of the SDRAM unload memory operation sequence.

- p\_ce. Enables the address counter and connects to the i\_sdram\_b\_cnt\_cnt\_ce signal, which is controlled by the FSM1 state machine. This signal, and therefore the counter, is active during the SDRAM load and unload sequence.

- p\_countout. Connects to address port B in the internal BlockRAM of DPRAM, via the i\_sdram\_addrb signal. This is a 15-bit bus carrying address values to address port B. For details on memory control signal generation and the state machine, refer to **Figure 5** and **Table 2**.

### 4.2.3 Memory Counter 3

Memory counter 3 is controlled by the FSM1 state machine and the MDR block. This counter addresses port A of the FPGA internal BlockRAM storage DPRAM. It has following input and output ports:

| p_clock    | : | in std_logic;           |      |    |    |

|------------|---|-------------------------|------|----|----|

| p_reset    | : | in std_logic;           |      |    |    |

| p_ce       | : | in std_logic;           |      |    |    |

| p_countout | : | out std_logic_vector(14 | down | to | 0) |

• p\_clock. A clock signal supplied from the i\_clkdv DCM clock source.

# NP

#### Code For the FPGA-MDR Interface

- p\_reset. Carries a reset signal to reset the addressing counter to 0. This reset signal is i\_ctrl\_mem\_cnt2\_rst and is generated by the FSM1 state machine. The reset is asserted at FPGA initialization and begins the unload SDRAM memory operation sequence.

- p\_ce. Enables the address counter and connects to p\_sdram\_a\_cnt\_cnt\_ce\_in, which is controlled by the MDR logic block. This signal and therefore the counter is active during the simulation sequence.

- p\_countout. Connects to the addra port A in the internal BlockRAM of DPRAM via the i\_sdram\_addra signal. This 15-bit bus carries the address value to address port A. For details on memory control signal generation and the state machine, see the state machine diagram in **Figure 5** and **Table 2**, *FSM1 Control Signal Assignment*, on page 14.

### 4.2.4 Finite State Machine 1 (FSM1)

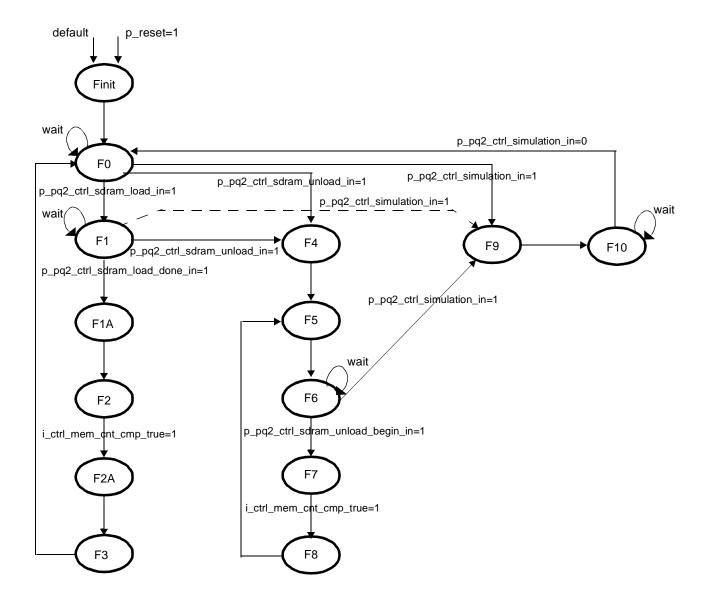

The FPGA FSM1 state machine is illustrated in the **Figure 9**. It has 14 states, 25 transitions, 6 inputs, and 16 outputs. The clock source is provided by port p\_clock, which is driven by the i\_clkdv clock. The rising clock edge is used for clocking. The p\_reset port provides the positive edge of the reset signal. The state machine encoding type used is one-hot encoding. The progression of states is as follows:

- **1.** In Finit, both address counters are reset.

- 2. F0 indicates the beginning of the state machine's repetitive operation. In this state, the ctrl\_mem\_cnt counter is the only counter that is reset.

- **3.** F1 is a decision or wait state. The machine waits until the p\_pq2\_ctrl\_sdram\_load\_done\_in, p\_pq2\_ctrl\_sdram\_unload\_in, or p\_pq2\_ctrl\_simulation\_in signals are asserted. Then, the next state is either F1A, F4, or F9, respectively.

In the F1A, F4 and F9 states, the SDRAM load, unload, and simulation operations are performed. When the p\_pq2\_ctrl\_sdram\_load\_done\_in signal is asserted high, the state machine proceeds to the next wait state, F1A. In this wait state, memory counter 1 is enabled, along with the PowerQUICC II 4 KB buffer DPRAM.

- **4.** In F2, memory counter 2 and the FPGA internal storage BlockRAM are enabled. During the F1A and F2 states, the data is unloaded from the 4 KB buffer DPRAM and loaded into the FPGA internal storage BlockRAM. One clock cycle delay is required before data is transmitted from the 4 KB buffer DPRAM.

- 5. F2 terminates when the address memory counter 1 detects the end of the 4 KB buffer space.

- **6.** In the F2A state, the 4 KB buffer DPRAM and its address counter are disabled, but the FPGA internal storage BlockRAM is enabled for one more clock cycle to allow the last data word to propagate.

- **7.** In the F3 state, the FPGA PowerQUICC II memory-mapped register in the PQ2 memory block notifies the MPC8260 that loading of the 4 KB data block is complete. The MPC8260 can use this register to determine when the next 4 KB of data should be sent.

- **8.** On the next clock cycle, the state machine returns to the F0, the decision wait state. In the F0 state, memory counter 1 is reset to zero.

- **9.** The operation of loading the 4 KB data can repeat.

VHDL Code For the FPGA-MDR Interface

Figure 5. Main Control Finite State Machine (FSM1) Operation

- 1. When data loading completes, the p\_pq2\_ctrl\_sdram\_unload\_in signal is asserted high and the state machine proceeds to the F4 state, in which memory counter 2 is reset to zero.

- 2. On the next clock cycle, the state increments to F5, in which memory counter 1 is reset to zero.

- **3.** On the next clock cycle, the state increments to F6, in which the state machine awaits further instructions. Based on the values of p\_pq2\_ctrl\_sdram\_unload\_begin\_in and p\_pq2\_ctrl\_simulation\_in, it proceeds to the SDRAM unload or simulation operations.

- **4.** When p\_pq2\_ctrl\_sdram\_unload\_begin\_in is asserted high, the next state is F7, in which both memory controllers and both memories are enabled to perform the SDRAM unload operation.

- **5.** At the end of the 4 KB address space, the state machine increments to the F8 state, in which the memory unloading signal is sent to the MPC8260 via the FPGA PQ2 memory-mapped register in the PowerQUICC II memory block. The MPC8260 can use this register to determine when the next block of 4 KB data should be read from the FPGA.

#### Code For the FPGA-MDR Interface

- **6.** On the next clock cycle, the state machine returns to the F5 state, and the operation of unloading the 4 KB of data can repeat.

- 7. When the p\_pq2\_ctrl\_simulation\_in signal is asserted in the F6 state, the state machine increments to the F9 state, a simulation state in which data streams from the FPGA into the MRC6011 via the MDR port. This operation is beyond the scope of this application note. See AN2890, FPGA MDR Antenna Interface for MRC6011: A VHDL Reference Design for the ROBIN Motherboard.

| Signal Name                               | Finit | F0 | F1 | F1A | F2 | F2A | F3 | F4 | F5 | F6 | F7 | F8 | F9 | F10 |

|-------------------------------------------|-------|----|----|-----|----|-----|----|----|----|----|----|----|----|-----|

| i_ctrl_mem_cnt_rst                        | 1     | 1  |    |     |    |     |    |    | 1  |    |    |    |    |     |

| i_ctrl_mem_cnt2_rst                       | 1     |    |    |     |    |     |    | 1  |    |    |    |    |    |     |

| i_pq2mem_cnt_ce                           |       |    |    | 1   | 1  |     |    |    |    |    | 1  |    |    |     |

| p_pq2mem_enb_out                          |       |    |    | 1   | 1  |     |    |    |    |    | 1  |    |    |     |

| p_pq2mem_web_out                          |       |    |    |     |    |     |    |    |    |    | 1  |    |    |     |

| i_sdram_a_cnt_ce                          |       |    |    |     | 1  | 1   |    |    |    |    | 1  |    |    |     |

| p_sdram_enb_out                           |       |    |    |     | 1  | 1   |    |    |    |    | 1  |    |    |     |

| p_sdram_web_out                           |       |    |    |     | 1  | 1   |    |    |    |    |    |    |    |     |

| p_pq2_ctrl_sdram<br>_load_done_clr_out    |       |    |    |     |    |     | 1  |    |    |    |    |    |    |     |

| p_pq2_ctrl_sdram_unload_<br>begin_clr_out |       |    |    |     |    |     |    |    |    |    |    | 1  |    |     |

| p_pq2_ctrl_simulation_on_out              |       |    |    |     |    |     |    |    |    |    |    |    |    | 1   |

Table 2.

FSM1 Control Signal Assignment

### 4.3 PowerQUICC II Logic Module

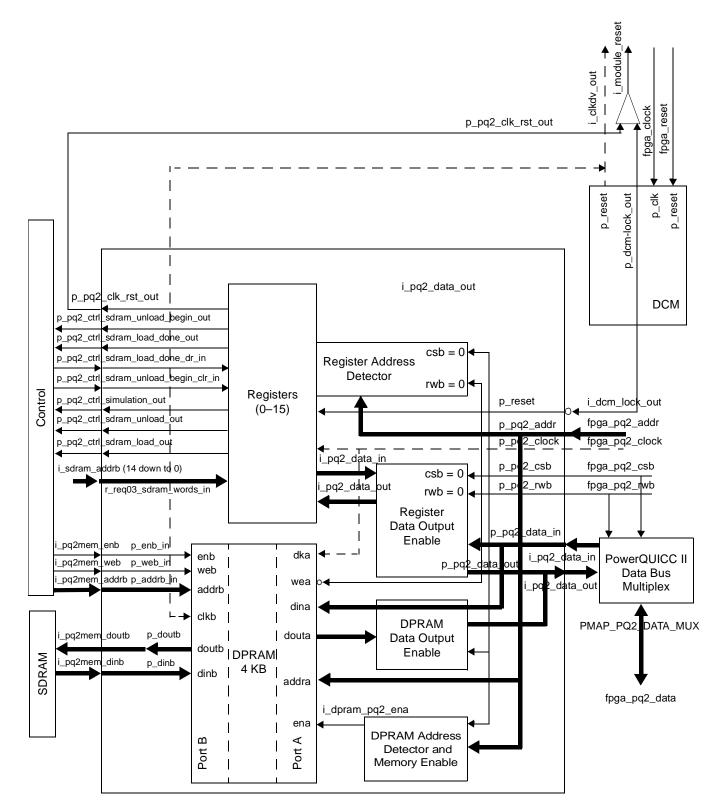

The PowerQUICC II logic module is the second largest module in the FPGA. It provides a system bus interface between the FPGA and MPC8260. Its main components are the 4 KB buffer DPRAM, sixteen 32-bit registers, memory and register detectors, output enable data multiplexes, and miscellaneous glue logic (see **Figure 6**). The PowerQUICC II logic module is strongly connected with the main control module as it receives and sends the PowerQUICC II control signals to the main FPGA state machine.

Figure 6. Architecture of the PowerQUICC II Logic Module

#### Code For the FPGA-MDR Interface

| p_pq2_clock | : | in std_logic; |

|-------------|---|---------------|

| p_reset     | : | in std_logic; |

- p\_pq2\_clock. The clock source for the PowerQUICC II logic module.

- p\_reset. Connected to fpga\_reset, which in turn connects to the FPGA reset button on the ROBIN motherboard.

| p_pq2_csb      | : in std_logic;                       |

|----------------|---------------------------------------|

| p_pq2_rwb      | : in std_logic;                       |

| p_pq2_addr     | : in std_logic_vector (9 downto 0);   |

| p_pq2_data_in  | : in std_logic_vector (31 downto 0);  |

| p_pq2_data_out | : out std_logic_vector (31 downto 0); |

- p\_pq2\_csb, p\_pq2\_rwb, and p\_pq2\_addr. PowerQUICC II UPM system bus control and address bus signals that connect directly to the MPC8260 processor.

- p\_pq2\_data\_in and p\_pq2\_data\_out. 32-bit buses that connect to the PowerQUICC II multiplexed data bus module. This multiplex is controlled by the fpga\_pq2\_csb and fpga\_pq2\_rwb signals to determine the value of the p\_pq2\_data\_in, p\_pq2\_data\_out, and fpga\_pq2\_data buses.

```

p_pq2_ctrl_rst_out : out std_logic;

p_pq2_ctrl_sdram_load_out : out std_logic;

p_pq2_ctrl_sdram_unload_out: : out std_logic;

p_pq2_ctrl_simulation_out : out std_logic;

p_pq2_ctrl_sdram_load_done_out : out std_logic;

p_pq2_ctrl_sdram_unload_begin_out : out std_logic;

p_pq2_ctrl_sdram_unload_begin_out : out std_logic;

p_pq2_ctrl_sdram_unload_begin_clr_in: in std_logic;

p_reg03_sdram_words_in : in std_logic_vector(31 downto 0);

```

• These ports are routed directly to the ports of the control logic module. The functionality of these ports is the same as described for the port of the control logic module. See **Section 4.2**, *Control Logic*, on page 9.

| p_addrb_in | : | IN s | td_logic_VECTOR(9 | downto | 0); |

|------------|---|------|-------------------|--------|-----|

| p_clkb_in  | : | IN s | td_logic;         |        |     |

| p_enb_in   | : | IN s | td_logic;         |        |     |

| p_web_in   | : | IN s | td_logic;         |        |     |

- p\_addrb\_in. A 10-bit address bus connected to the 4 KB DPRAM and driven by the control logic module.

- p\_clkb\_in. A clock source for port B of the 4 KB DPRAM that is run from the i\_clkdv clock tree.

- p\_enb\_in and p\_web\_in. Driven by the control logic module and connect to the memory enable and read/write enable ports of the port B DPRAM.

| p_dinb_in   | : | <pre>IN std_logic_VECTOR(31 downto 0);</pre> |

|-------------|---|----------------------------------------------|

| p_doutb_out | : | OUT std_logic_VECTOR(31 downto 0);           |

• p\_dinb\_in and p\_doutb\_out. 32-bit input and output buses to connect the 4 KB buffer DPRAM and FPGA internal storage BlockRAM.

```

debug_addr: out std_logic_vector(9 downto 0);debug_ena: out std_logic;debug_wea: out std_logic

```

• Used exclusively for debug purposes.

### 4.3.1 4 KB Buffer DPRAM

The Xilinx CORE Generator<sup>TM</sup> was used to create the 4 KB buffer dual-ported random access memory (DPRAM) module. Each memory port has an address bus, a data input bus, a data output bus, an individual clock signal, an individual memory enable signal, and an individual write enable signal. Both port A and B are 32 bits wide and 1024 words deep. To address the 1024 words, the 10 address lines are used for both port A and B.

```

Check:

Port A and B-> (2<sup>10</sup>) address lines * 32 bits port size = 32,768 bits = 4,096 bytes

component dpram pq2

port (

addra : IN std logic VECTOR(9 downto 0);

addrb : IN std logic VECTOR(9 downto 0);

: IN std logic;

clka

: IN std logic;

clkb

: IN std logic VECTOR(31 downto 0);

dina

: IN std_logic_VECTOR(31 downto 0);

dinb

douta : OUT std logic VECTOR(31 downto 0);

doutb : OUT std logic VECTOR(31 downto 0);

: IN std logic;

ena

: IN std logic;

enb

: IN std logic;

wea

: IN std logic);

web

end component;

```

- addra, clka, dina, douta, ena, and wea. Port A signals to connect to the MPC8260 system bus. The dina and douta 32-bit buses are routed to the DPRAM data output enable logic block. The ena port is driven by i\_dpram\_pq2\_ena, which is generated by the DPRAM address detector and memory enable logic block. The clka port is driven by the p\_pq2\_clock tree.

- addrb, clkb, dinb, doutb, enb and web. Port B signals to connect to FPGA internal storage BlockRAM. The dinb and doutb 32-bit ports directly connect to the FPGA internal storage BlockRAM data input and output buses. The enb, web, and addrb ports connect to the control logic module that drives these signals. The clkb port is driven by the i\_clkdv clock tree.

### 4.3.2 Xilinx CORE Generator

To create or modify the DPRAM core using the Xilinx CORE Generator, select the core in the source window within the Xilinx Project Navigator. Next, in the Process window run MANAGE CORES within the Coregen process. When the Xilinx CORE Generator application launches, you can chose either to edit or create a new core. The design core window for the dual-port block memory is straightforward. On the first page, set the width of port A to 32 bits and the depth to 1024. Set the width of port B to 32 bits and the depth to 1024, the same as for port A. Both port A and port B options for configuration should be set to READ AND WRITE and for write mode should be set to READ AND WRITE.

### L Code For the FPGA-MDR Interface

On the second core design page for port A, select ENABLE PIN. The HANDSHAKING PIN and REGISTER INPUT features are not used. In the output register options, set the Additional Output Pipe Stages to 0. The SINIT PIN functionality is not used, so the initialization value (hexadecimal) can be left blank. The pin polarity options are RISING EDGE TRIGGERED for an active clock edge, ACTIVE HIGH for the enable pin, and ACTIVE HIGH for the write enable pin.

On the third core design page for port B, select the optional ENABLE PIN. The HANDSHAKING PIN and REGISTER INPUT features are not used. In the output register options, set the Additional Output Pipe Stages to 0. The SINIT PIN functionality is not used, so the initialization value (hexadecimal) can be left blank. The pin polarity options are RISING EDGE TRIGGERED for active clock edge, ACTIVE HIGH for the enable pin, and ACTIVE HIGH for the write enable pin.

On the final, fourth core design page within the Initial Contents, the global initialization value is set to 0, but it can be set to any value desired. You can preload the memory with the initialization hexadecimal file (.coe), which can be useful in debugging. If desired, check the LOAD INIT FILE check box and load the initialization hexadecimal file. The bottom of this page presents the summary of the designed DPRAM core. For our example, the information panel should display as follows:

Address Width A10Address Width B10Blocks Used2Port A Read Pipeline Latency 1Port B Read Pipeline Latency 1

If these values are correct, click **GENERATE**, and the new core is generated.

### 4.3.3 PowerQUICC II FPGA Control Register Space

In addition to the 4 KB memory mapped buffer space, the MPC8260 can access the sixteen 32-bit register space. For the purpose of this generic reference design, only first four registers are used. The remaining twelve registers are available for future use.

| FPGA  | A_CTRL FPGA Control Register |                                 |    |    |    |    |    |    |    |    | BASE+0xFFC |    |    |     |     |    |

|-------|------------------------------|---------------------------------|----|----|----|----|----|----|----|----|------------|----|----|-----|-----|----|

|       | Bit 0                        | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 |    |    |    |    |    |    |    |    |            | 13 | 14 | 15  |     |    |

|       | R —                          |                                 |    |    |    |    |    |    |    |    |            |    |    |     |     |    |

| TYPE  |                              |                                 |    |    |    |    |    | R/ | W  |    |            |    |    |     |     |    |

| RESET | 1                            | 0                               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 0   | 0   | 0  |

|       | 16                           | 17                              | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26         | 27 | 28 | 29  | 30  | 31 |

|       |                              |                                 |    |    |    |    | —  |    |    |    |            |    |    | SIM | UNL | LD |

| TYPE  |                              |                                 |    |    |    |    |    | R/ | W. |    |            |    |    |     |     |    |

| RESET | 0                            | 0                               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0          | 0  | 0  | 0   | 0   | 0  |

FPGA\_CTRL is accessed from the MPC8260.

| Name             | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |        | Settings                                                                                                                   |

|------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| <b>R</b><br>0    | 1     | <b>Soft Reset</b><br>When this bit is set, the FPGA can be reset or held in the reset state<br>from the MPC8260. The MPC8260 reference code uses this bit to<br>reset the FPGA during FPGA initialization. This bit is set by default,<br>so the FPGA is kept in reset by default until instructed otherwise by<br>the MCP8260. The p_pq2_ctrl_rst_out signal carries the value of<br>the reset bit to the reset of the FPGA logic. | 0      | Deasserts the reset state<br>of the internal FPGA<br>modules.<br>Holds the internal FPGA<br>modules in the reset<br>state. |

| <br>1–28         | 0     | Reserved. Cleared to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                 |        |                                                                                                                            |

| <b>SIM</b><br>29 | 0     | <b>Simulation</b><br>Unloads the data from the SDRAM into the MDR port of the<br>MRC6011 processor. This operation is covered in <b>Section 6</b> , <i>FPGA</i><br><i>Operating Sequence</i> , on page 31. The p_pq2_ctrl_simulation_out<br>signal carries the value of this bit to the master control state<br>machine (FSM1).                                                                                                     | 0<br>1 | OFF.<br>ON.                                                                                                                |

| <b>UNL</b><br>30 | 0     | <b>Unload SDRAM</b><br>Initiates the FPGA unload SDRAM sequence within the FSM1 in<br>the main control block. When this bit is set, the state machine is<br>instructed to unload the SDRAM state. The<br>p_pq2_ctrl_sdram_unload_out signal carries the value of this bit to<br>the master control state machine (FSM1).                                                                                                            | 0<br>1 | OFF.<br>ON.                                                                                                                |

| <b>LD</b><br>31  | 0     | <b>Load SDRAM</b><br>Initiates the FPGA load SDRAM sequence within FSM1 in the main<br>control block. When this bit is set, the state machine is instructed to<br>load the SDRAM state. The p_pq2_ctrl_sdram_load_out signals<br>carries the value of this bit to the master control state machine<br>(FSM1).                                                                                                                       | 0<br>1 | OFF.<br>ON.                                                                                                                |

| Table 3. | FPGA | _CTRL | Bit Descriptions |  |

|----------|------|-------|------------------|--|

|----------|------|-------|------------------|--|

| FPGA | _VER  | ER FPGA Image Version Register |    |    |    |    |    |    |    |    |    | BASE+0xFF8 |     |    |    |    |

|------|-------|--------------------------------|----|----|----|----|----|----|----|----|----|------------|-----|----|----|----|

|      | Bit 0 | 1                              | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11         | 12  | 13 | 14 | 15 |

|      |       |                                |    | YE | AR |    |    |    |    |    |    | МО         | NTH |    |    |    |

| TYPE |       |                                |    |    |    |    |    | F  | र  |    |    |            |     |    |    |    |

|      | 16    | 17                             | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27         | 28  | 29 | 30 | 31 |

|      |       |                                |    | DA | ۹Y |    |    |    |    |    |    | VI         | ER  |    |    |    |

| TYPE |       |                                |    |    |    |    |    | F  | २  |    |    |            |     |    |    |    |

FPGA\_VER determines the FPGA image version.

| Table 4. | FPGA | _VER Bi | t Descriptions |

|----------|------|---------|----------------|

|----------|------|---------|----------------|

| Name               | Description                                                                               | Settings                   |

|--------------------|-------------------------------------------------------------------------------------------|----------------------------|

| <b>YEAR</b><br>0–7 | Year<br>Indicates the last two digits of the year in which the FPGA image was<br>created. | 2004 would appear as 0x04. |

| Name                 | Description                                                          | Settings                                                                                               |

|----------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| <b>MONTH</b><br>8–15 | Month<br>Indicates the month in which the FPGA image was created.    | 0x01 Corresponds to January.<br>0x0C Corresponds to December.                                          |

| <b>DAY</b><br>16–23  | <b>Day</b><br>Indicates the day in which the FPGA image was created. | 0x01 Corresponds to day 01 of the<br>given month.<br>0x07 Corresponds to day 31 of the<br>given month. |

| <b>VER</b><br>24–31  | Version<br>Indicates the version number of the FPGA image.           |                                                                                                        |

Table 4. FPGA\_VER Bit Descriptions (Continued)

| SDRA  | M_CT  | _CTRL SDRAM Control Register BA |    |    |    |    |    |    |    |    | ASE+C | xFF4 |    |    |     |    |

|-------|-------|---------------------------------|----|----|----|----|----|----|----|----|-------|------|----|----|-----|----|

|       | Bit 0 | 1                               | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10    | 11   | 12 | 13 | 14  | 15 |

|       |       |                                 |    |    |    |    |    | _  | _  |    |       |      |    |    |     |    |

| TYPE  |       |                                 |    |    |    |    |    | R/ | W  |    |       |      |    |    |     |    |

| RESET | 0     | 0                               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0    | 0  | 0  | 0   | 0  |

|       | 16    | 17                              | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26    | 27   | 28 | 29 | 30  | 31 |

|       |       |                                 |    |    |    |    | _  | _  |    |    |       |      |    |    | ULB | LD |

| TYPE  |       |                                 |    |    |    |    |    | R/ | W  |    |       |      |    |    | •   |    |

| RESET | 0     | 0                               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0    | 0  | 0  | 0   | 0  |

SDRAM\_CTRL can be accessed from the MPC8260.

The FPGA p\_pq2\_ctrl\_sdram\_load\_done\_clr\_in and

p\_pq2\_ctrl\_sdram\_unload\_begin\_clr\_in internal signals are used to clear the SDRAM\_CTRL register bit flags 30 and 31. If these signals are high, the SDRAM\_CTRL register is cleared. The two signals are controlled by the master control state machine (FSM1).

| Table 5. | SDRAM_ | CTRL Bi | t Descriptions |

|----------|--------|---------|----------------|

|----------|--------|---------|----------------|

| Name             | Reset | Description                                                                                                                                                                                |  |  |  |  |  |  |  |  |

|------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                  | 0     | Reserved. Cleared to zero for future compatibility.                                                                                                                                        |  |  |  |  |  |  |  |  |

| 0–29             |       |                                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| <b>ULB</b><br>30 | 0     | <b>SDRAM Block of 512 32-Bit Words Begin Unload</b><br>Sends a request to the FPGA FSM1 to begin the transfer of 512 32-bit words from the storage<br>BlockRAM to the 4 KB buffer space.   |  |  |  |  |  |  |  |  |

| <b>LD</b><br>31  | 0     | <b>SDRAM Block of 512 32-Bit Words Begin Load Done</b><br>Sends a request to the FPGA FSM1 to begin the transfer of 512 32-bit words from the 4 KB buffer space into the storage BlockRAM. |  |  |  |  |  |  |  |  |

| SDRA  | M_N   | 0   | :   | SDRAM Number of 32-Bit Words Register |     |     |     |     |     |     |     | BASE+0xFF0 |     |     |     |     |

|-------|-------|-----|-----|---------------------------------------|-----|-----|-----|-----|-----|-----|-----|------------|-----|-----|-----|-----|

|       | Bit 0 | 1   | 2   | 3                                     | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11         | 12  | 13  | 14  | 15  |

|       | C0    | C1  | C2  | C3                                    | C4  | C5  | C6  | C7  | C8  | C9  | C10 | C11        | C12 | C13 | C14 | C15 |

| TYPE  |       |     |     |                                       |     |     |     | F   | २   |     |     |            |     |     |     |     |

| RESET | 0     | 0   | 0   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0          | 0   | 0   | 0   | 0   |

|       | 16    | 17  | 18  | 19                                    | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27         | 28  | 29  | 30  | 31  |

|       | C16   | C17 | C18 | C19                                   | C20 | C21 | C22 | C23 | C24 | C25 | C26 | C27        | C28 | C29 | C30 | C31 |

| TYPE  |       |     |     |                                       |     |     |     | F   | र   |     |     |            |     |     |     |     |

| RESET | 0     | 0   | 0   | 0                                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0          | 0   | 0   | 0   | 0   |

SDRAM\_NO is used by MPC8260 to keep track of how many 32-bit words the FPGA reads or writes into the storage BlockRAM. The FPGA address counter logic holds the count.

| Table 6. | SDRAM | NO Bit | Descriptions |

|----------|-------|--------|--------------|

|----------|-------|--------|--------------|

| Name                  | Reset | Description      |

|-----------------------|-------|------------------|

| <b>C0–C31</b><br>0–31 | 0     | SDRAM Word Count |

### 4.3.4 PowerQUICC II Memory/Register Detector

The memory/register detector determines whether the MPC8260 is requesting the 4 KB buffer space or one of the sixteen 32-bit registers. The internal 32-bit data bus, p\_pq2\_dat\_out signal, connects to the 4 KB buffer data out bus only when p\_pq2\_csb and i\_dpram\_pq2\_addra(9) are equal to 0. Similarly, the 4 KB buffer DPRAM is enabled only when both of p\_pq2\_csb and i\_dpram\_pq2\_addra(9) are equal to 0. If the i\_dpram\_pq2\_addra(9) signal is equal to 1, the access is interpreted as a register read or write, and the data is read and written from one of the sixteen 32-bit registers.

### 4.4 PowerQUICC II Data Multiplex

The data multiplex component is used as a smart driver for the fpga\_pq2\_data 32-bit bidirectional data bus. The ports of the component are as follows:

```

p_pq2_oeb : IN std_logic;

p_pq2_csb : IN std_logic;

p_pq2_data_out: IN std_logic_vector(31 downto 0);

p_pq2_data_inout: INOUT std_logic_vector(31 downto 0);

p_pq2_data_in: OUT std_logic_vector(31 downto 0)

```

- p\_pq2\_oeb. Connects to the fpga\_pq2\_rwb signal to determine whether the system bus transaction is a read or write.

- p\_pq2\_csb. Connects to the fpga\_pq2\_csb signal, which is a system bus signal used by the UPM as a chip select.

- p\_pq2\_data\_out. A 32-bit input bus connected to the i\_pq2\_data\_out that provides connection to the register or 4 KB buffer memory-mapped space.

## Code For the FPGA-MDR Interface

- p\_pq2\_data\_inout. A bidirectional bus directly connected directly to the MPC8260 via the fpga\_pq2\_data port. p\_pq2\_data\_inout is equal to p\_pq2\_data\_out when p\_pq2\_oeb = 1 and p\_pq2\_csb = 0. Otherwise, p\_pq2\_data\_inout is held in *high z* state, allowing the MCP8260 UPM controller to drive the bus.

- p\_pq2\_data\_in. A 32-bit output bus connected to the i\_pq2\_data\_in to provide data to the register or 4 KB buffer memory-mapped space.

## 4.5 BlockRAM Storage Memory

The Xilinx CORE Generator<sup>™</sup> was used to create the dual-ported random access memory (DPRAM) module used as 128 KB storage BlockRAM. Each memory port has an address bus, a data input bus, a data output bus, an individual clock signal, an individual memory enable signal, and an individual write enable signal. Both port A and B are 32 bits wide and 32768 words deep. To address the 32768 words, the 15 address lines were used for both port A and B.

```

Check:

Port A and B-> (2^15) address lines * 32 bits port size = 1,048,576 bits = 131,072

bytes = 128 Kilo Bytes

component mdr test dpram

port (

addra : IN std logic VECTOR(14 downto 0);

addrb : IN std logic VECTOR(14 downto 0);

clka : IN std logic;

clkb : IN std logic;

: IN std logic VECTOR(31 downto 0);

dina

: IN std logic VECTOR(31 downto 0);

dinb

douta : OUT std logic VECTOR(31 downto 0);

doutb : OUT std logic VECTOR(31 downto 0);

: IN std logic;

ena

: IN std logic;

enb

: IN std logic;

wea

web

: IN std loqic);

end component;

```

- addrb, clkb, dinb, doutb, enb, and web. Port B signals that connect to the FPGA 4 KB buffer DPRAM and control logic module. The 32-bit dinb and doutb ports directly connect to the FPGA 4 KB buffer DPRAM data input and output buses. The enb, web, and addrb ports connect to the control logic module, which drives these signals. clkb is driven by the i\_clkdv clock tree.

- addra, clka, dina, douta, ena, and wea. Port A signals not used in this reference design. These signals are reserved for connection to the MDR interface, which is covered in second part of this reference design.

### 4.5.1 Xilinx CORE Generator

To create or modify the DPRAM core using the Xilinx CORE Generator, select the core in the source window within the Xilinx Project Navigator. Next, in the Process window run **MANAGE CORES** within the Coregen process. When the Xilinx CORE Generator application launches, you can chose either to edit or create a new core. The design core window for the dual-port block memory is straightforward. On the first page, set the width of port A to

32 bits and the depth to 32768. Set the width of port B to 32 bits and the depth to 32768, the same as for Port A. Both Port A and port B options for configuration should be set to **READ AND WRITE** and for write mode should be set to **READ AND WRITE**.

On the second core design page for port A, select ENABLE PIN. The HANDSHAKING PIN and REGISTER INPUT features are not used. In the output register options, set the Additional Output Pipe Stages to 0. The SINIT PIN functionality is not used, so the initialization value (hexadecimal) can be left blank. The pin polarity options are RISING EDGE TRIGGERED for an active clock edge, ACTIVE HIGH for the enable pin, and ACTIVE HIGH for the write enable pin.

On the third core design page for port B, select the optional ENABLE PIN. The HANDSHAKING PIN and REGISTER INPUT features are not used. In the output register options, set the ADDITIONAL OUTPUT PIPE STAGES to 0. The SINIT PIN functionality is not used, so the initialization value (hexadecimal) can be left blank. The pin polarity options are RISING EDGE TRIGGERED for active clock edge, ACTIVE HIGH for the enable pin, and ACTIVE HIGH for the write enable pin.

On the final, fourth core design page within the Initial Contents, the global initialization value is set to 0, but it can be set to any value desired. You can preload the memory with the initialization hexadecimal file (.coe), which can be useful in debugging. If desired, check the **LOAD INIT FILE** check box and load the initialization hexadecimal file. The bottom of this page presents the summary of the designed DPRAM core. For our example, the information panel should display as follows:

```

Address Width A15

Address Width B 15

Blocks Used 58

Port A Read Pipeline Latency 1

Port B Read Pipeline Latency 1

```

If these values are correct, click GENERATE, and the new core is generated.

## 5 FPGA Memory Space

The FPGA 4 KB buffer DPRAM is memory-mapped via the MPC8260 UPM system bus interface, along with sixteen 32-bit registers. The MPC8260 can access the buffer space from the following address range:

```

START BASE_ADDRESS + 0x0000

END BASE ADDRESS + 0x1000

```

In this reference design, the base address of 0x0300 0000 transfers into the 0x0300 0000–0x0300 1000 memory range reserved for accessing the FPGA 4 KB buffer space. The FPGA control registers are mapped in the following order:

| BASE_ADDRESS | + | 0x0FFC | = | r_reg00_FPGA_CTRL   |

|--------------|---|--------|---|---------------------|

| BASE_ADDRESS | + | 0x0FF8 | = | r_reg01_FPGA_VER    |

| BASE_ADDRESS | + | 0x0FF4 | = | r_reg02_SDRAM_CTRL  |

| BASE_ADDRESS | + | 0x0FF0 | = | r_reg03_SDRAM_WORDS |

| BASE_ADDRESS | + | 0x0FEC | = | r_test_5            |

| BASE_ADDRESS | + | 0x0FE8 | = | r_test_6            |

| BASE_ADDRESS | + | 0x0FE4 | = | r_test_7            |

| BASE_ADDRESS | + | 0x0FE0 | = | r_test_8            |

| BASE_ADDRESS | + | 0x0FDC | = | r_test_9            |

| BASE_ADDRESS | + | 0x0FD8 | = | r_test_10           |

| BASE_ADDRESS | + | 0x0FD4 | = | r_test_11           |

| BASE_ADDRESS | + | 0x0FD0 | = | r_test_12           |

| BASE_ADDRESS | + | 0x0FCC | = | r_test_13           |

| BASE_ADDRESS | + | 0x0FC8 | = | r_test_14           |

| BASE_ADDRESS | + | 0x0FC4 | = | r_test_15           |

|              |   |        |   |                     |

A Memory Space

### 5.1 Digital Clock Management (DCM) Logic

DCM is a standard feature in the Xilinx Virtex-II<sup>™</sup>, Virtex-II Pro<sup>™</sup>, and Spartan III® devices. Different models of these devices have different numbers of clock managers. The main features are clock de-skewing, frequency synthesis, phase shifting, and duty cycle correction. Our design uses only clock de-skewing and duty cycle correction. To keep the reference design simple, only clock input, clock output, clock reset, and DCM lock signals are used. Other signals, such as status and additional clock outputs, can be used in a larger design. The lock signal and its associated logic should keep all FPGA logic in the reset state until the lock signal goes high to indicate that the DCM DLL is locked and the clock output signal is stable. Until the lock signal activates, the DCM output clocks are not valid and can exhibit glitches, spikes, or other unwanted spurious signals.

```

DLL_FREQUENCY_MODE : string := "LOW";

DUTY_CYCLE_CORRECTION : boolean := TRUE;

CLKDV_DIVIDE : string := "6.0";

STARTUP_WAIT : boolean := TRUE

attribute DLL_FREQUENCY_MODE : string;

attribute DUTY_CYCLE_CORRECTION : string;

attribute CLKDV_DIVIDE : string;

attribute STARTUP_WAIT : string;

attribute DLL_FREQUENCY_MODE of U_DCM: label is "LOW";

attribute DUTY_CYCLE_CORRECTION of U_DCM: label is "TRUE";

attribute CLKDV_DIVIDE of U_DCM2: label is "6.0";

attribute STARTUP_WAIT of U_DCM2: label is "TRUE";

```

These parameters set up the DCM for low-frequency operation with the duty cycle correction enabled (50/50) and the start-up sequence wait enabled. If the clkdv output is used, it is divided by factor of 6.

```

component dcm main is

Port (

p clock

: in std logic;

: in std logic;

p reset

: out std logic;

p clk1x out

p clkdv out

: out std logic;

p clk2x out

: out std logic;

p clk2x180 out

: out std logic;

p clkfx out

: out std logic;

p dcm lock out

: out std logic

);

```

end component;

- p\_clock is a non-de-skewed input clock.

- p\_reset. This signal is inverted because DCM is active high and the master FPGA switch on the board in this reference design is active low.

- p\_clk1x\_out, p\_clkdv\_out, p\_clk2x\_out, p\_clk2x180\_out, p\_clkfx\_out, and p\_dcm\_lock\_out. These signals are routed to the DCM output ports for use in the top-level design.

```

-- DCM Instantiation

U_DCM2: DCM

port map

(

```

);

| CLKIN    | => | p_clock,        |

|----------|----|-----------------|

| CLKFB    | => | i_clk0,         |

| DSSEN    | => | gnd,            |

| PSINCDEC | => | gnd,            |

| PSEN     | => | gnd,            |

| PSCLK    | => | gnd,            |

| RST      | => | p_reset,        |

| CLK0     | => | i_clk0_tmp,     |

| CLKDV    | => | i_clkdv_tmp,    |

| CLKFX    | => | i_clkfx_tmp,    |

| CLK2X    | => | i_clk2x_tmp,    |

| CLK2X180 | => | i_clk2x180_tmp, |

| LOCKED   | => | i_lock          |

|          |    |                 |

Notice that the i\_clk0 signal is routed both to CLKFB and to the rest of the FPGA system bus logic. This signal is an output of the global clock buffer, BUFG, and must be routed to the CLKFB port on the DCM component for proper operation of the feedback circuit. In the following BUFG instantiation, i\_clk0\_tmp is a de-skewed output DCM signal serving as an input to the BUFG. The output of the BUFG is the clock signal to drive the rest of the FPGA logic. The DCM logic uses five BUFG global clock buffers. The BUFG instantiation for the i\_clk0 DCM clock output is presented as follows. The BUFG instantiation for i\_clk0, i\_clk2x, i\_clk2x180, and i\_clkfx are the same as for i\_clk0.

In this example, only clock output that is de-skewed and divided by 6 is used (i\_clkdv). The following deskewed clock output options can be used as needed:

- i\_clk1x = A frequency equal to one of the input clocks.

- i\_clk2x = A frequency multiplied by two of the input clocks.

- i\_clkfx = A frequency multiplied by factor of fx of the input clock.

- i clk2x180 = A frequency multiplied by two of the input clocks with a phase shift of 180 degrees.

### 5.2 JTAG Logic

The JTAG logic provides flexible control of the JTAG chain, which is composed of six JTAG-enabled devices: MRC6011A, MRC6011B, MRC6011C, DSPA, DSPB, and DSPC. You can create a custom JTAG chain of any or all six devices. The signals in the JTAG logic are as follows:

| p_jtag_conndsp_tdi        |   | in std_logic;       |           |

|---------------------------|---|---------------------|-----------|

| p_jtag_conndsp_tdo        | : | out std_logic;      |           |

| p_jtag_conndsp_commun     | : | in std_logic_vector | (0 to 3); |

| p_jtag_connmrc6011_tdi    | : | in std_logic;       |           |

| p_jtag_connmrc6011_tdo    | : | out std_logic;      |           |

| p_jtag_connmrc6011_commun | : | in std_logic_vector | (0 to 3); |

- p\_jtag\_conndsp\_tdi and p\_jtag\_conndsp\_tdo. Common JTAG TDI and TDO signals connected to the DSP JTAG connector.

- p\_jtag\_conndsp\_commun. A four-signal bus connected to the DSP JTAG connector, providing common JTAG signals.

- p\_jtag\_connmrc6011\_tdi and p\_jtag\_connmrc6011\_td0. Common JTAG TDI and TDO signals connected to the MRC6011 JTAG connector.

- p\_jtag\_connmrc6011\_commun. A four-signal bus connected to the MRC6011 JTAG connector, providing common JTAG signals.

| p_jtag_dsp_a_tdi :    | : | out std_logic;                            |

|-----------------------|---|-------------------------------------------|

| p_jtag_dsp_a_tdo :    | : | in std_logic;                             |

| p_jtag_dsp_a_commun : | : | <pre>out std_logic_vector (0 to 3);</pre> |

| p_jtag_dsp_b_tdi :    | : | out std_logic;                            |

| p_jtag_dsp_b_tdo :    | : | in std_logic;                             |

| p_jtag_dsp_b_commun : | : | <pre>out std_logic_vector (0 to 3);</pre> |

| p_jtag_dsp_c_tdi :    | : | out std_logic;                            |

| p_jtag_dsp_c_tdo :    | : | in std_logic;                             |

| p_jtag_dsp_c_commun : | : | <pre>out std_logic_vector (0 to 3);</pre> |

- p\_jtag\_dsp\_a\_tdi and p\_jtag\_dsp\_a\_tdo. Common JTAG TDI and TDO signals directly connected to DSP A.

- p\_jtag\_dsp\_a\_commun. A four-bit bus directly connected to DSP A, providing common JTAG signals.

- p\_jtag\_dsp\_b\_tdi and p\_jtag\_dsp\_b\_tdo. Common JTAG TDI and TDO signals directly connected to DSP B.

- p\_jtag\_dsp\_b\_commun. A four-bit bus directly connected to DSP B, providing common JTAG signals.

- p\_jtag\_dsp\_c\_tdi and p\_jtag\_dsp\_c\_tdo. Common JTAG TDI and TDO signals directly connected to DSP C.

- p\_jtag\_dsp\_c\_commun. A four-bit bus connected directly to DSP C, providing common JTAG signals.

| p_jtag_mrc6011_a_tdi    | : out std_logic;                 |

|-------------------------|----------------------------------|

| p_jtag_mrc6011_a_tdo    | : in std_logic;                  |

| p_jtag_mrc6011_a_commun | : out std_logic_vector (0 to 3); |

| p_jtag_mrc6011_b_tdi    | : out std_logic;                 |

| p_jtag_mrc6011_b_tdo    | : in std_logic;                  |

```

p_jtag_mrc6011_b_commun : out std_logic_vector (0 to 3);

p_jtag_mrc6011_c_tdi : out std_logic;

p_jtag_mrc6011_c_tdo : in std_logic;

p_jtag_mrc6011_c_commun : out std_logic_vector (0 to 3);

```

- p\_jtag\_mrc6011\_a\_tdi and p\_jtag\_mrc6011\_a\_tdo. Common JTAG TDI and TDO signals directly connected to MRC6011 A.

- p\_jtag\_mrc6011\_a\_commun. A 4-bit bus directly connected to MRC6011 A, providing common JTAG signals.

- p\_jtag\_mrc6011\_b\_tdi and p\_jtag\_mrc6011\_b\_tdo. Common JTAG TDI and TDO signals directly connected to MRC6011 B.

- p\_jtag\_mrc6011\_b\_commun. A 4-bit bus connected directly to MRC6011 B, providing common JTAG signals.

- p\_jtag\_mrc6011\_c\_tdi and p\_jtag\_mrc6011\_c\_tdo. Common JTAG TDI and TDO signals directly connected to MRC6011 C.

- p\_jtag\_mrc6011\_c\_commun. A 4-bit bus directly connected to MRC6011 C, providing common JTAG signals.

| p_jtag_dipswdsp     | : | <pre>in std_logic_vector (0 to 2);</pre> |

|---------------------|---|------------------------------------------|