Freescale Semiconductor Application Note AN2932 Rev. 0, 12/2005

# Serial RapidIO Bring-Up Procedure on PowerQUICC<sup>™</sup> III

by Lorraine McLuckie and Colin Cureton NCSD Platforms, East Kilbride

The MPC8548 PowerQUICC<sup>TM</sup> III processor features a 1x/4x serial RapidIO interface. This document provides guidelines for basic use of this interface, starting with local and remote processors setup with basic verification and discovery. It then describes booting over RapidIO and conducting simple data transfer tests.

Most of this document applies to any PowerQUICC III system enabled for serial RapidIO. However, the concepts are illustrated with a few device-specific examples.

#### Contents

| l | Introduction                    | 2 |

|---|---------------------------------|---|

| 2 | RapidIO Basics                  |   |

| 3 | Bring-up Procedure              |   |

| 1 | Output from Example Application |   |

| 5 | References                      |   |

|   |                                 |   |

|   | 1. 4                            |   |

#### Appendix A:

| Note | es on Maintenance Transactions        | 49 |

|------|---------------------------------------|----|

| A.1  | Terminology                           | 49 |

| A.2  | Example 1: 4 Mbyte Maintenance Window | 50 |

| A.3  | Example 2: 4 Kbyte Maintenance Window | 50 |

| A.4  | Maintenance Transactions Within       |    |

|      | Multi-Switch Systems                  | 51 |

© Freescale Semiconductor, Inc., 2005. All rights reserved.

## 1 Introduction

This document assists engineers in using the serial RapidIO interface on the MPC8548 PowerQUICC III processor. After summarizing basic aspects of the RapidIO specification, it describes a procedure to bring up simple RapidIO systems, including setting up the local processor, simplified discovery, booting over RapidIO, and executing simple memory reads/writes to the remote processors.

The following acronyms and terms are used throughout this application note.

| Term           | Description                                         |

|----------------|-----------------------------------------------------|

| ATMU           | Address translation and mapping unit                |

| BAR            | Base address register                               |

| CAR            | Capability attribute register                       |

| CCSR           | Configuration, control and status registers         |

| CCSRBAR        | CCSR base address register                          |

| CSR            | Capability status register                          |

| DDR SDRAM      | Double data rate SDRAM                              |

| DIDCAR         | Device identity capability register                 |

| DMA            | Direct memory access                                |

| EEPROM         | Electrically erasable programmable read only memory |

| HBDIDLCSR      | Host base device lock ID CSR                        |

| I/O            | Input/Output                                        |

| JTAG           | Joint test access group                             |

| LAW            | Local access window                                 |

| LP-LVDS        | Link protocol, low voltage differential signaling   |

| MAS            | MMU assist register                                 |

| MMU            | Memory management unit                              |

| PowerQUICC III | MPC85xx networking and communications processor     |

| R/W            | Read/Write                                          |

| RIO            | RapidIO                                             |

| RIW            | RapidIO inbound window                              |

| ROW            | RapidIO outbound window                             |

| SBTG           | Software bring-up technical group                   |

| SDRAM          | Synchronous dynamic random access memory            |

| SPR            | Special-Purpose Register                            |

| SRIO           | Serial RapidIO                                      |

| TLB            | Translation lookaside buffer                        |

#### Table 1. Glossary of Terms

## 2 RapidIO Basics

The RapidIO interconnect architecture is a high-performance packet-switched interconnect technology. It addresses the high-performance embedded industry's need for reliability, increased bandwidth, and faster bus speeds in an intra-system interconnect. The RapidIO interconnect allows chip-to-chip and board-to-board communications. This section summarizes information from the RapidIO specification. For details, consult the *RapidIO Interconnect Specification* [1].

## 2.1 RapidIO Layers

The RapidIO specification is written in layers, as follows, to ensure flexibility and modularity so that changes to one layer do not necessarily affect other layers:

- *Logical layer*. Defines the overall protocol and packet formats, the types of RapidIO transactions, and addressing. The logical layer is split into several categories depending on the system model:

- Input/output logical specification that defines the basic system architecture of RapidIO.

- Message passing logical specification that enables distributed I/O processing.

- Transport layer. Describes routing as packets move from one point to another.

- *Physical layer*. Defines the device-level interface such as packet transport mechanisms, flow control, electrical characteristics, and low-level error management.

This application note concentrates on the input/output logical specification. The RapidIO block implements the 1x/4x serial RapidIO physical layer.

## 2.2 Processing Element Models

Several types of devices can be used in a RapidIO based system. Only two device model types are described here: the integrated processor-memory processing element and the switch processing element.

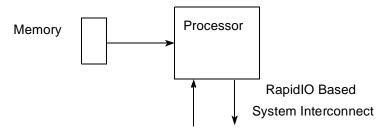

### 2.2.1 Integrated Processor-Memory Processing Element

One form of the processor-memory processing element is a fully integrated component that connects to a RapidIO interconnect system as shown in Figure 1. This type of device integrates a memory system and other support logic with a processor core on the same piece of silicon, or within the same package, and is one example of a RapidIO end-point. In this note, the processing element is an MPC8548 device.

Figure 1. Integrated Processor-Memory Processing Element

RapidIO Basics

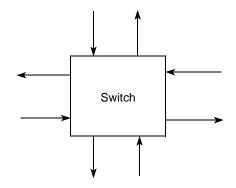

### 2.2.2 Switch Processing Element

A switch processing element allows communication with other processing elements through a switch. A switch can connect a variety of RapidIO-compliant processing elements. Behavior of the switches, and the interconnect fabric in general, is addressed in the *RapidIO Common Transport Specification* [1]. In this note the switch processing element used is the Tundra Tsi568 Serial RapidIO switch [3].

Figure 2. Switch Processing Element Model

### 2.2.3 CAR/CSR Block

The RapidIO specification defines a block of capability attributes registers (CARs) and command and status registers (CSRs) on each RapidIO device. These CAR/CSR registers are accessed using maintenance transactions, and they are used to configure a device across RapidIO. Each register has a maintenance offset used in the maintenance transaction to select the register to be accessed. Table 2 shows an extract from the list of CAR/CSR registers and their offsets. For details, consult the RapidIO specifications [1] or the *MPC8548E PowerQUICC III*<sup>TM</sup> *Integrated Host Processor Family Reference Manual*.

| Offset | Register Name                   |

|--------|---------------------------------|

| 0x00   | Device Identity CAR             |

| 0x04   | Device Information CAR          |

| 0x08   | Assembly Identity CAR           |

| 0x0C   | Assembly Information CAR        |

| 0x10   | Processing Element Features CAR |

| 0x14   | Switch Port Information CAR     |

Table 2. Extract from the table of CAR/CSRs

### 2.2.4 RapidIO Transactions

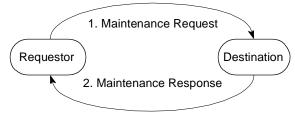

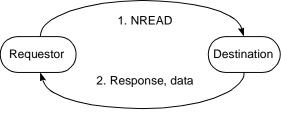

In the logical layer, RapidIO defines a broad range of transaction types, ranging from simple transactions to access an agent device's memory space to user-defined and implementation-dependent transactions. Each RapidIO transaction has a source and destination ID. The RapidIO specification defines two transport modes: large and small. In a small transport systems, source and destination IDs are 8 bits, and therefore a system can consist of up to 256 devices. In a large transport system, with 16-bit source and destination IDs, up to 65,536 devices can be supported. In this discussion, there are three different classes of requests and their associated responses. A request is a transaction issued by a processing element to accomplish an activity on a remote processing element. The three transactions types are as follows:

• *Maintenance transaction*. A special system support request. by a processing element to read or write data to CARs and CSRs, as defined in the RapidIO specification [1, 4]. Instead of addresses, maintenance requests use an offset into the CAR/CSR block to specify the register to be read or written. Maintenance transactions are used for system initialization and discovery and for altering system configuration.

Figure 3. Maintenance Transaction

• *NREAD transaction.* A processing element uses a read transaction, consisting of the NREAD request and corresponding RESPONSE, to read data from a specified address. The data is returned in a response packet and is of the size requested.

Figure 4. NREAD Transaction

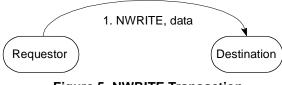

• *NWRITE/NWRITE\_R transaction*. A processing element uses a write transaction to write data to a specified address. The write transaction can take several forms including NWRITE and NWRITE\_R. The NWRITE request allows data writes, with no expected response, as shown in Figure 5.

Figure 5. NWRITE Transaction

*NWRITE\_R (write with response) transaction.* Identical to the NWRITE transaction except that it requires a response to notify the sender that the write has completed at the destination, as shown in Figure 6. This transaction is useful for guaranteeing read-after-write and write-after-write ordering through a system that can reorder transactions.

Figure 6. NWRITE\_R Transaction

**RapidIO Basics**

## 2.3 Serial RapidIO on the MPC8548

This section describes the implementation of RapidIO on MPC8548 devices, including other MPC8548 modules (for example, the MMU) that must be considered in the use of RapidIO. The MPC8548 1x/4x serial interface conforms to the *RapidIO Interconnect Specification* [1]. This RapidIO interface operates at up to 3.125Gbaud (unidirectional data rate 2.5Gbps, per lane).

The MPC8548 RapidIO controller is partitioned into inbound and outbound blocks, which are further divided into three implementation layers that loosely correspond to the logical, common transport, and physical layers of the RapidIO interconnect specification. Users access the RapidIO interface mainly at the logical and transport layers. The user does not directly control the physical layer.

The MPC8548 RapidIO implementation has a messaging unit that implements Part II of *RapidIO Interconnect Specification*.[1]. For details, see Freescale application note AN2923, *Using the Serial RapidIO Messaging Unit on PowerQUICC III*<sup>5</sup>. Other Freescale devices implement the 8-bit parallel RapidIO, and there are separate application notes on the operation of these devices [6, 7].

## 2.3.1 Mapping Memory to the RapidIO Interface

Because accesses to the RapidIO interface are memory-mapped, we must consider not only the specifics of the RapidIO interface but also the way memory accesses are redirected to the RapidIO interface.

### 2.3.1.1 Memory Management Unit

The MPC8548 supports demand paged virtual memory, as well as other memory management schemes that depend on precise control of effective-to-physical address translation and flexible memory protection. The memory management unit (MMU) uses software managed translation lookaside buffers (TLBs) that support variable-size pages, with per-page properties and permissions.

Although the MMU is not part of the RapidIO interface, it must be notified of any memory area that is translated to any interface, including RapidIO. Before RapidIO transactions are attempted, there must be a TLB entry to cover the area of the memory map used for RapidIO transactions. This entry can be initialized by a bootloader or a debugger. However, if a TLB entry is not initialized to cover the RapidIO region of the memory map, the bring-up software must do this. The TLB is initialized by the MMU assist (MAS) registers, which are initialized with information on the TLB entry (for example the required address range, size, and permissions). The **tlbwe** instruction is used to write the information into the TLB.

### 2.3.1.2 Local Memory Map and Local Access Windows

The MPC8548 local memory map refers to the address space from the processor and the internal DMA engines as they access memory and I/O space. In this map are memory-mapped configuration, control and status registers, and all memory accessible to the DDR SDRAM, local bus memory controllers, and other interfaces.

All addresses used by the system except configuration space (mapped by CCSRBAR), and the internal SRAM regions (mapped by L2SRBAR), must be mapped by a local access window (LAW). The local access windows are not specific to RapidIO, but they must cover the area of memory used to generate RapidIO transactions. The LAW is initialized by the bootloader, the debugger, or the bring-up software. If a LAW is not used, the bring-up software must cover the region of the memory map used for RapidIO. A set of 10 local access windows define the local memory map. Each local window maps a region of memory to a particular target interface, such as the DDR SDRAM controller or the RapidIO controller. The LAWs do not handle address translation. Each window can be configured from 4 Kbytes to 32 GBytes.

### 2.3.2 RapidIO ATMU (Address Translation and Mapping Unit)

The MPC8548 RapidIO controller is partitioned into outbound and inbound blocks. The outbound block uses RapidIO outbound windows (ROWs) to translate an address from the local address space to that of RapidIO. The inbound block uses RapidIO inbound windows (RIWs) to translate an address from the external address space of RapidIO to the local address space for the internal interfaces.

### 2.3.2.1 RapidIO Outbound ATMU Windows

RapidIO outbound ATMU windows (ROWs) map the 36-bit internal address space to the 34-bit RapidIO address space. ROWs also attach attributes such as transaction type and priority level. There are nine RapidIO outbound ATMU windows (0–8). Window 0 is always enabled and is the default window if the address does not match one of the other eight.

Each window can be divided into 2 or 4 segments of equal size. Each segment assigns attributes and the device ID for an outbound transaction, but each segment within a window translates to the same translation address. Each segment can be further sub-divided into 2, 4, or 8 subsegments of equal size. These subsegments allow a single segment to target a number of numerically adjacent target device IDs, using the same attributes and the same address translation.

### NOTE

Errata in early MPC8548 silicon prevents the use of segmented windows. Therefore, although the correct operation of the segments is described in this document, they are not used in the example software.

The default RapidIO outbound window is defined by three registers:

- Translation address register (ROWTAR*n*). Contains the RapidIO base address to which these transactions are translated. ROWTAR takes one of two formats depending on the type of transaction. For regular transactions (such as NREAD, NWRITE, and NWRITE\_R) it contains the device ID of the target and bits 0–21 of the translated address. For maintenance transactions without an address, ROWTAR contains the device ID of the target, the hopcount, and the upper bits of the maintenance offset into the CAR/CSR block.

- Attributes register (ROWAR*n*). Contains information on the window (for example, its size) and the types of transactions that are generated by it (for example, NWRITE, NWRITE\_R, or maintenance write).

- Base address register (ROWBAR*n*). Contains the base address of the window in the local memory address space. There is no ROWBAR for the default window.

In addition, each window has a set of segment registers (ROWS*x*R*n*) to define the attributes of each segment. For details on these registers, and their bit definitions, see Section 3, "Bring-up Procedure."

In regular transactions, the RapidIO address is created by concatenating the translation address in the ROWTAR with the transaction offset (that is, the offset of the transaction from the base address of the ROW). With the maintenance transactions, the maintenance offset is created from a combination of the 12-bit configuration field in the ROWTAR and the transaction offset. Further information on the operation of the maintenance window can be found in Appendix A

### 2.3.2.2 RapidIO Inbound ATMU Windows

RapidIO inbound ATMU windows (RIWs) translate addresses from the 34-bit external RapidIO address space to the 36-bit internal address space. These inbound ATMU windows also attach attributes such as transaction type and target interface to the transaction. There are five inbound ATMU windows (0–4). Window 0 is always enabled and is the default window if the address does not match one of the other four windows.

The default RapidIO inbound window is defined by three registers:

- Translation address register (RIWTAR*n*).Contains the local base address to which the transactions are translated.

- Attributes register (RIWAR*n*). Contains information on the window (size, for example) and what should be done with the transactions received through it (for example, snoop or not snoop local processor).

- Base address register (RIWBAR*n*). Contains the base address of the window in RapidIO address space. There is no RIWBAR for the default window.

### 2.3.2.3 Inbound ATMU Local Configuration Space Window

An additional inbound window can be used by external RapidIO devices to access the local configuration, control and status registers (CCSR) memory.<sup>2</sup> The base address of this 1 Mbyte window is defined in the local configuration space base address 1 command and status register (LBSBA1CSR). Incoming RapidIO reads and writes that match this window are redirected, at the same offset, into the CCSR area. This local configuration space window has the highest priority for incoming translation.

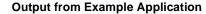

## 2.4 Example Target Hardware

This section describes the system referenced in the examples presented in Section 3, "Bring-up Procedure." The system either runs a bootloader and then the bring-up application is downloaded and run from this bootloader, or the system is initialized by a debugger and the code is downloaded and run across JTAG. Here, it is assumed that most system setup and initialization (for example, CCSRBAR, DDR, and Flash) is complete. No assumptions are made about the initialization of the RapidIO interface.

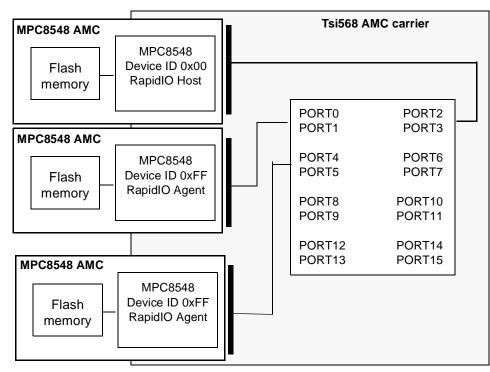

The fabric-based system in the example has an AMC carrier card featuring a Tundra Tsi568 serial RapidIO switch<sup>3</sup> and a number of MPC8548 AMC cards. The Tsi568 is a 16 port (x1) or 8 port (x4) RapidIO switch. In the example hardware, only three ports are routed to the AMC connectors. Any SRIO-capable AMC cards can be inserted into the AMC connectors. For simplicity, we assume that only MPC8548 boards are to be inserted. In the flexible hardware architecture depicted in Figure 7, several MPC8548 devices can connect to a single Tsi568. Only one of these processors can be configured as a RapidIO host, and this device has a device ID of 0x0. All other processors in the system are configured as RapidIO agents and have an initial device ID of 0xFF. The agent devices can be configured to boot from their local Flash memory devices or from RapidIO. The boot image on the Flash memory device connected to the host processor can be used to boot the host and/or the agent devices. This 4 Mbyte boot image is at addresses 0xFFC0\_0000–0xFFFF\_FFF.

## 3 Bring-up Procedure

The procedure to bring up basic RapidIO capability on a MPC8548 system may not apply to all systems. An application using this procedure was created and tested on the hardware system described in Section 2.4, "Example Target Hardware." This procedure executed on the host to discover and bring up the other elements in the system.

Figure 7. Fabric-Based Hardware and Example Configuration

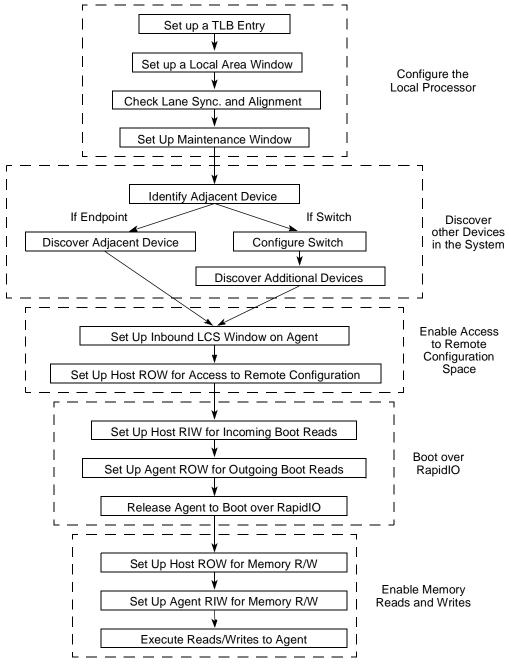

The subsections that follow are organized around five overall steps in the bring-up procedure:

1. Configure the local processor.

Configure and check the local processor before generating any RapidIO traffic. Set up a TLB entry, set up a local area window, check lane synchronization and alignment, and set up a maintenance window.

2. Discover all other devices in the system.

Using only maintenance transactions, identify adjacent devices, set up a switch, and discover other endpoints. Assume limited flexibility in the configuration of the system (as described in Section 2.4, "Example Target Hardware"). This step does not satisfy all requirements of the RapidIO SBTG documentation [4].

3. Enable access to remote configuration space.

Enable the local processor (host) to access the local configuration space of the remote device (agent). Set up the incoming window on the agent that redirects RapidIO transactions to the local configuration space, and set up an outbound window on the host to map outgoing transactions onto that window.

4. Boot over RapidIO.

Configure an agent to boot over RapidIO, that is, to boot from Flash memory attached to host. Set up an inbound window on the host to capture the incoming boot reads, and configure and release the agent to execute its boot procedure.

5. Enable memory reads and writes.

Enable host access to agent memory space. Set up the outbound window on the host and the inbound window on the agent.

Restrictions on software operation that cause the system to halt and report the findings to the user are as follows:

- This software operates on a small transport mode RapidIO system.

- All devices are MPC8548 or Tsi568 only.

- No more than one Tsi568 can be found.

- The software runs on a host with device ID 0.

- All other processors in the system are agents with an initial device ID of 0xFF.

- The software allocates device ID 1 and 2 to any other processors it discovers.

- The software does not find any more than two agent devices.

Figure 8. Procedure for Bringing Up a Simple RapidIO System

## 3.1 Configure the Local Processor

Before RapidIO traffic can be generated, several steps must be completed on the local (host) processor.

### 3.1.1 Set up a TLB Entry

The first step is to set up a TLB entry to cover the area of memory used for RapidIO accesses, which may or may not be necessary, depending on the configuration set by the bootloader or debugger. This example presents the minimum configuration for a 256 Mbyte entry covering address range 0x0\_C000\_0000-0x0\_CFFF\_FFFF. This area is used throughout the examples to access RapidIO. Entry 3 of TLB1 is used, but any unused entry in TLB1 can be used (some entries are used by bootloader/debugger configuration to cover CCSR, Flash, DDR and so on).

The TLB entry is created by initializing the relevant MAS registers with information on the area of memory and then loading this information into the TLB. MAS registers are special-purpose registers that are initialized using the **mtspr** instruction. For example, to load the value required into MAS0 (SPR 0x270), use the following sequence:

```

asm("lis 3, 0x1003");

asm("ori 3, 3, 0x0000");

asm("mtspr 0x270, 3");

```

### 3.1.1.1 Initialize MAS0

|         | 32               | 33 | 34 | 35         | 36 | 37       | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46  | 47 |

|---------|------------------|----|----|------------|----|----------|----|----|----|----|----|----|----|----|-----|----|

| Field   |                  | _  |    | TLB<br>SEL |    |          |    | -  | _  |    |    |    |    | ES | SEL |    |

| Setting |                  | 0× | :1 |            |    | 0x00 0x3 |    |    |    |    |    |    |    |    |     |    |

|         | 48               | 49 | 50 | 51         | 52 | 53       | 54 | 55 | 56 | 57 | 58 | 59 | 60 | 61 | 62  | 63 |

| Field   |                  |    |    |            |    |          |    | —  |    |    |    |    |    |    |     | NV |

| Setting | etting 0x000 0x0 |    |    |            |    |          |    | x0 |    |    |    |    |    |    |     |    |

#### Figure 9. MAS0 Setting for RapidIO Mapping

MAS0 contains the MMU Read/Write and replacement control. Table 3 lists the settings for the example.

| Bits  | Name   | Description and Setting                                                                                                                                                                                                                                                  |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35    | TLBSEL | Selects TLB for access<br>1 TLB1                                                                                                                                                                                                                                         |

| 44–47 | ESEL   | Entry select. Number of entry in selected array to be used for <b>tlbwe</b> . This field is also updated on TLB error exceptions (misses), and <b>tlbsx</b> hit and miss cases.<br>0011 This becomes entry 3.                                                            |

| 63    | NV     | <ul> <li>Next victim. Next victim bit value to be written to TLB0[NV] on execution of tlbwe. This field is also updated on TLB error exceptions (misses), tlbsx hit and miss cases and on execution of tlbre.</li> <li>A next victim has not been identified.</li> </ul> |

#### Table 3. MAS0 Field Descriptions and Settings

### 3.1.1.2 Initialize MAS1

|         | 32   | 33    | 34    | 35 | 36  | 37  | 38 | 39 | 40 | 41   | 42 | 43 | 44 | 45 | 46 | 47 |  |  |

|---------|------|-------|-------|----|-----|-----|----|----|----|------|----|----|----|----|----|----|--|--|

| Field   | V    | IPROT |       |    | _   | _   |    |    |    |      |    | TI | D  |    |    |    |  |  |

| Setting |      | 0x8   |       |    |     | 0x0 |    |    |    | 0x00 |    |    |    |    |    |    |  |  |

|         | 48   | 49    | 50    | 51 | 52  | 53  | 54 | 55 | 56 | 57   | 58 | 59 | 60 | 61 | 62 | 63 |  |  |

| Field   | — TS |       | TSIZE |    |     |     | _  |    |    |      |    |    |    |    |    |    |  |  |

| Setting | 0x0  |       |       |    | 0x9 |     |    |    |    |      |    | 0x | 00 |    |    |    |  |  |

### Figure 10. MAS1 Setting for RapidIO Window

MAS1 contains the descriptor context and configuration control. The settings in the example have the definitions listed in Table 4.

| Bits  | Name  | Description and Setting                                                                                                                                                                                               |

|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | V     | TLB valid bit     1   This TLB entry is valid.                                                                                                                                                                        |

| 33    | IPROT | Invalidate protect. Set to protect this TLB entry from invalidate operations due to the execution of <b>tlbiva[x]</b> (TLB1 only).<br>0 Entry is not protected from invalidation                                      |

| 40–47 | TID   | Translation identity. An 8-bit field that defines the process ID for this TLB entry.<br>All zeros. It is a global entry and can be used by any process.                                                               |

| 51    | TS    | <ul><li>Translation space. This bit is compared with the IS or DS fields of the MSR (depending on the type of access) to determine if this TLB entry may be used for translation.</li><li>0 Bit is not set.</li></ul> |

| 52–55 | TSIZE | Translation size. Defines the TLB entry page size.<br>1001 This entry has a page size of 256 Mbytes                                                                                                                   |

#### Table 4. MAS1 Field Descriptions and Settings

### 3.1.1.3 Initialize MAS2

|         | 32 | 33 | 34         | 35 | 36 | 37    | 38 | 39  | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |  |

|---------|----|----|------------|----|----|-------|----|-----|----|----|----|----|----|----|----|----|--|

| Field   |    |    |            |    |    |       |    | EPI | 1  |    |    |    |    |    |    |    |  |

| Setting |    |    | 0xC000     |    |    |       |    |     |    |    |    |    |    |    |    |    |  |

|         | 48 | 49 | 50         | 51 | 52 | 53    | 54 | 55  | 56 | 57 | 58 | 59 | 60 | 61 | 62 | 63 |  |

| Field   |    | EP | ٧N         |    |    |       | —  |     |    | X0 | X1 | W  | Ι  | М  | G  | Е  |  |

| Setting |    | 0x | <b>(</b> 0 |    |    | 0x008 |    |     |    |    |    |    |    |    |    |    |  |

#### Figure 11. MAS2 Setting for RapidIO Window

MAS2 contains the effective page number and page attributes. The settings in this example have the definitions listed in Table 5.

| Bits  | Name | Description and Setting                                                                                                                                                                                                                                       |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32–51 | EPN  | Effective page number. Depending on page size, only the bits associated with a page boundary are valid. Bits that represent offsets within a page are ignored and should be cleared.<br>0xC0000 Effective address of this space starts at address 0xC000_0000 |

| 57    | X0   | Implementation-dependent page attribute<br>0                                                                                                                                                                                                                  |

| 58    | X1   | Implementation-dependent page attribute<br>0                                                                                                                                                                                                                  |

| 59    | W    | Write-through<br>0 This page is considered write-back with respect to the caches in the system.                                                                                                                                                               |

| 60    | I    | <ul> <li>Caching-inhibited</li> <li>1 The page is considered caching-inhibited. All loads and stores to the page bypass the caches and are performed directly to main memory.</li> </ul>                                                                      |

| 61    | М    | Memory coherence required<br>0 Memory coherence is not required.                                                                                                                                                                                              |

| 62    | G    | <ul> <li>Guarded</li> <li>O Accesses to this page are not guarded and can be performed before it is known if they are required by the sequential execution model.</li> </ul>                                                                                  |

| 63    | E    | Endianness. Determines endianness for the corresponding page.<br>0 The page is accessed in big-endian byte order.                                                                                                                                             |

#### Table 5. MAS2 Field Descriptions and Settings

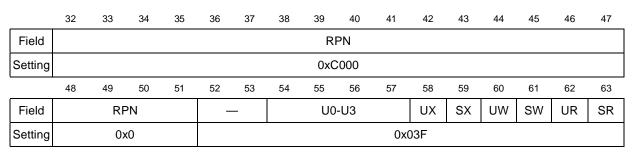

### 3.1.1.4 Initialize MAS3

### Figure 12. MAS3 Setting for RapidIO Window

MAS3 contains the real page number and access control. The settings in the example have the definitions listed in Table 6.

| Bits  | Name  | Description and Setting                                                                                                                                                  |

|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32–51 | RPN   | Real page number.<br>0xC0000 The real address of this space starts at 0x0_C000_0000.<br>The higher order bits of the 36-bit effective page number are contained in MAS7. |

| 54–57 | U0-U3 | User attribute bits. Associated with a TLB entry and can be used by system software.<br>All zeros                                                                        |

| 58    | UX    | Permission bit.<br>1 User mode has execute permission.                                                                                                                   |

| 59    | SX    | Permission bit.<br>1 Supervisor mode has execute permission.                                                                                                             |

| 60    | UW    | Permission bit.<br>1 User mode has write permission.                                                                                                                     |

| 61    | SW    | Permission bit.<br>1 Supervisor mode has write permission.                                                                                                               |

| 62    | UR    | Permission bit.<br>1 User mode has read permission.                                                                                                                      |

| 63    | SR    | Permission bit.<br>1 Supervisor mode has read permission.                                                                                                                |

#### Table 6. MAS3 Field Descriptions and Settings

### 3.1.1.5 Initialize MAS7

#### Figure 13. MAS7 Setting for RapidIO Window

MAS3 contains the real page number and access control. The settings in the example have the definitions listed in Table 7.

| Name | Description and Setting                                                                                   |

|------|-----------------------------------------------------------------------------------------------------------|

|      | Higher order bits of the Real page number.<br>0x0 The real address of this space starts at 0x0 C000 0000. |

|      | RPN                                                                                                       |

### 3.1.1.6 Load Information into the TLB

Finally, execute a **sync** instruction to ensure that all the MAS registers are written, a **tlbwe** instruction to load the information into the TLB, and a final **sync** to ensure that the TLB entry is created. For example:

```

asm("sync");

asm("tlbwe");

asm("sync");

```

### 3.1.2 Set Up a Local Area Window

We set up a local area window (LAW) to redirect memory accesses within a certain address range to the RapidIO interface. Whether this step is necessary depends on the configuration set by the bootloader or debugger. In the example, the LAWBAR and LAWAR registers are configured to ensure that a 256 Mbyte block of memory space covering address range 0x0\_C000\_0000-0x0\_CFFF\_FFFF is redirected to the RapidIO interface. The LAW registers are memory-mapped within the CCSR area, so they can be read and written using standard memory reads and writes.

### 3.1.2.1 Set LAWBAR

|         | 0         | 1  | 2  | 3  | 4  | 5  | 6  | 7    | 8     | 9  | 10 | 11    | 12   | 13 | 14 | 15 |

|---------|-----------|----|----|----|----|----|----|------|-------|----|----|-------|------|----|----|----|

| Field   |           |    |    | _  | _  |    |    |      |       |    |    | BASE_ | ADDR |    |    |    |

| Setting | 0x00 0x0C |    |    |    |    |    |    |      |       |    |    |       |      |    |    |    |

|         | 16        | 17 | 18 | 19 | 20 | 21 | 22 | 23   | 24    | 25 | 26 | 27    | 28   | 29 | 30 | 31 |

| Field   |           |    |    |    |    |    |    | BASE | _ADDR |    |    |       |      |    |    |    |

| Setting | 0x0000    |    |    |    |    |    |    |      |       |    |    |       |      |    |    |    |

#### Figure 14. LAWBAR Register for RapidIO Window

The local area window base address (LAWBAR) sets the base address of this window. The setting in the example has the following definition:

| Bits  | Name      | Description and Setting                                                                              |

|-------|-----------|------------------------------------------------------------------------------------------------------|

| 12–31 | BASE_ADDR | Identifies the 24 most-significant address bits of the 36-bit base address of local access window n. |

|       |           | 0x0C0000 The address of this space starts at 0x0_C000_0000.                                          |

#### Table 8. LAWBAR Field Description and Setting

### 3.1.2.2 Set LAWAR

|         | 0                       | 1 | 2 | 3   | 4  | 5 | 6 | 7 | 8         | 9  | 10 | 11 | 12 | 13 | 14 | 15 |  |  |

|---------|-------------------------|---|---|-----|----|---|---|---|-----------|----|----|----|----|----|----|----|--|--|

| Field   | EN                      |   |   |     | —  |   |   |   | TRGT_IF — |    |    |    |    |    |    | -  |  |  |

| Setting |                         |   |   | 0x8 | 30 |   |   |   | 0xC 0x0   |    |    |    |    |    | x0 |    |  |  |

|         | 16 17 18 19 20 21 22 23 |   |   |     |    |   |   |   | 24        | 25 | 26 | 27 | 28 | 29 | 30 | 31 |  |  |

| Field   |                         |   |   |     | -  | _ |   |   | SIZE      |    |    |    |    |    |    |    |  |  |

| Setting |                         |   |   | 0x0 | 00 |   |   |   |           |    | 0x | 1B |    |    |    |    |  |  |

#### Figure 15. LAWAR Record for RapidIO Window

The local area window attributes register (LAWAR) enables this window, sets the interface to which the transactions are directed, and sets the size of the window. The settings in the example have the definitions presented in Table 9

| Bits  | Name    | Description and Setting                                                                                                                     |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | EN      | 1 Window is enabled.                                                                                                                        |

| 8–11  | TRGT_IF | Identifies the target interface ID when a transaction hits in the address range defined by this window.<br>0xC Target interface is RapidIO. |

| 26–31 | SIZE    | Identifies the size of the window from the starting address.<br>0x1B Window size is 256 Mbytes.                                             |

#### Table 9. LAWAR Field Descriptions and Settings

### 3.1.3 Check Lane Synchronization and Alignment

Before creating any RapidIO traffic, we must ensure that the RapidIO interface is successfully synchronized with the adjacent device,<sup>4</sup> which is indicated in the error and status command and status register (ESCSR). The ESCSR[PO] bit indicates that the input and output ports are initialized and are exchanging error free control symbols with the attached device. This bit must be set before the RapidIO interface is used. To determine whether the RapidIO port is initialized in 1x or 4x mode, we can check the control command and status register (CCSR). The CCSR[IPW] field indicates the width of the initialized RapidIO port.

### 3.1.4 Set Up Maintenance Window

After checking synchronization and initialization, we create a RapidIO outbound window to generate RapidIO maintenance transactions. In this example, a single maintenance window is created and used to issue maintenance reads and writes to all the elements of the system. The ROWBAR, ROWTAR, and ROWAR registers are configured to initialize a 4 Mbyte RapidIO window at the very bottom of the area of the RapidIO space, that is, 0x0\_C000\_0000-0x0\_C040\_0000. Reads and writes within this window then generate RapidIO maintenance read and write transactions.

In maintenance transactions, the lower-order bits of the maintenance offset are taken from the offset into the maintenance window, but the higher-order bits are taken from the contents of the ROWTAR. Refer to Appendix A for details on the operation of the maintenance windows and the calculation of the maintenance offsets.

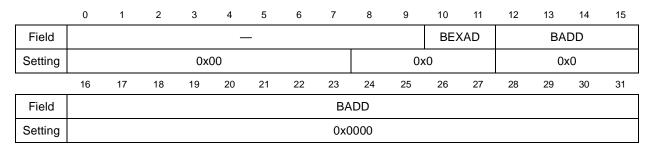

### 3.1.4.1 Set ROWBAR

|         | 0  | 1      | 2  | 3   | 4  | 5  | 6  | 7  | 8            | 9  | 10 | 11 | 12 | 13 | 14 | 15 |  |  |

|---------|----|--------|----|-----|----|----|----|----|--------------|----|----|----|----|----|----|----|--|--|

| Field   |    |        |    | _   | -  |    |    |    | BEXTADD BADD |    |    |    |    |    |    | DD |  |  |

| Setting |    |        |    | 0x0 | 00 |    |    |    | 0x0 0xC      |    |    |    |    |    | кС |    |  |  |

|         | 16 | 17     | 18 | 19  | 20 | 21 | 22 | 23 | 24           | 25 | 26 | 27 | 28 | 29 | 30 | 31 |  |  |

| Field   |    |        |    |     |    |    |    | BA | DD           |    |    |    |    |    |    |    |  |  |

| Setting |    | 0x0000 |    |     |    |    |    |    |              |    |    |    |    |    |    |    |  |  |

#### Figure 16. Maintenance Window ROWBAR Register

The base address register (ROWBAR), defines the start address of the window. The settings in the example are defined in Table 10.

| Bits  | Name    | Description and Setting                                                                                                                                                                                  |

|-------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8-11  | BEXTADD | Window base extended address, bits 0–3 of 36-bit base address<br>0x0 Extended addressing is not used                                                                                                     |

| 12–31 | BADD    | Base address of outbound window, bits 4-23 of the 36-bit base address. Source address that is the starting point for the outbound translation window.<br>0xC0000 Window starts at address 0x0_C000_0000. |

#### Table 10. ROWBAR Field Description and Setting

### 3.1.4.2 Set ROWAR

|         | 0       | 1           | 2 | 3   | 4   | 5   | 6   | 7  | 8    | 9  | 10         | 11 | 12  | 13 | 14  | 15 |  |

|---------|---------|-------------|---|-----|-----|-----|-----|----|------|----|------------|----|-----|----|-----|----|--|

| Field   | EN      |             | — |     | TFL | JOV | PCI | _  | NSEG |    | NSSEG      |    |     | RD | TYP |    |  |

| Setting |         |             |   | 0x8 | 30  |     |     |    |      | 0> | <b>‹</b> 0 |    | 0x7 |    |     |    |  |

|         | 16      | 16 17 18 19 |   |     |     | 21  | 22  | 23 | 24   | 25 | 26         | 27 | 28  | 29 | 30  | 31 |  |

| Field   | WRTYP — |             |   |     |     |     |     |    | SIZE |    |            |    |     |    |     |    |  |

| Setting | 0x7 0x0 |             |   |     |     |     |     |    |      |    | 0x         | 13 |     |    |     |    |  |

#### Figure 17. Maintenance Window ROWAR Settings

The attributes register defines attributes of the transactions created by this window; including the priority and transaction types. It also defines the size of the window. The settings in the example are defined in Table 11.

| Bits | Name  | Description and Setting                                                                     |

|------|-------|---------------------------------------------------------------------------------------------|

| 0    | EN    | Window address translation enable.         1       This RapidIO outbound window is enabled. |

| 4–5  | TFLOV | Transaction flow level priority of transaction00Lowest-priority transaction request flow.   |

| Bits  | Name  | Description and Setting                                                                                             |

|-------|-------|---------------------------------------------------------------------------------------------------------------------|

| 6     | PCI   | Follow PCI transaction ordering rules<br>0 Do not follow PCI transaction ordering rules.                            |

| 8-9   | NSEG  | Number of segments in this window0Single-segment (normal) window.                                                   |

| 10-11 | NSSEG | Number of subsegments per segment0No subsegments.                                                                   |

| 12–15 | RDTYP | Read transaction type. Transaction type to run on RapidIO interface if access is a read.<br>0x7 Maintenance read.   |

| 16–19 | WRTYP | Write transaction type. Transaction type to run on RapidIO interface if access is a write<br>0x7 Maintenance write. |

| 26–31 | SIZE  | Outbound window size.<br>0x13 One Mbyte.                                                                            |

#### Table 11. ROWAR Field Descriptions and Settings (continued)

### 3.1.4.3 Set ROWTAR

|         | 0                    | 1                    | 2          | 3  | 4  | 5     | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|----------------------|----------------------|------------|----|----|-------|----|----|----|----|----|----|----|----|----|----|

| Field   | _                    | - TRGTID - HOP_COUNT |            |    |    |       |    |    |    |    |    |    |    | -  |    |    |

| Setting | 0x3FC 0x0            |                      |            |    |    |       |    |    |    |    |    |    |    |    |    |    |

|         | 16                   | 17                   | 18         | 19 | 20 | 21    | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| Field   | HOP_COUNT CFG_OFFSET |                      |            |    |    |       |    |    |    |    |    |    |    |    |    |    |

| Setting |                      | 0>                   | <b>‹</b> 0 |    |    | 0x000 |    |    |    |    |    |    |    |    |    |    |

#### Figure 18. Maintenance Window ROWTAR Settings

The RapidIO outbound window translation address register (ROWTAR) defines the starting address in RapidIO space for hits in this window. The ROWTAR takes different forms for different transaction types. For maintenance transactions, it is of the form shown here. In the example, the settings are defined as shown in Table 12.

| Bits  | Name       | Description and Setting                         |  |  |  |  |  |  |

|-------|------------|-------------------------------------------------|--|--|--|--|--|--|

| 2–9   | TRGTID     | 0xFF Target ID for RapidIO Packet               |  |  |  |  |  |  |

| 12–19 | HOP_COUNT  | All zeros. Hop count of maintenance transaction |  |  |  |  |  |  |

| 20–31 | CFG_OFFSET | All zeros. Upper bits of maintenance offset.    |  |  |  |  |  |  |

#### NOTE

This is just an initial value for the ROWTAR. Users must ensure that the ROWTAR contains the correct destination ID, hopcount, and offset value for their transaction.

For details on the operation of the maintenance window, refer to Appendix A.

### 3.2 Discover Other Devices in the System

This application note does not cover all requirements of the discovery process described in the RapidIO specifications [4]. It provides examples of simplified discovery processes for use with simple systems (that is, with only one host, and not more than one switch). The target hardware system is described in Section 2.4, "Example Target Hardware."

### 3.2.1 Identify Adjacent Device

The first RapidIO transaction to be executed is a maintenance read to the device identity capability register (DIDCAR) of the adjacent device. The DIDCAR, at maintenance offset 0x00, contains a device identity field and a device vendor identity field. The RapidIO consortium maintains a list of the assigned values. Therefore, reading this register enables the identification of the adjacent device. This maintenance transaction is achieved by executing a read instruction within the area covered by the maintenance window. The attributes of this read are as follows:

- Destination ID = 0xFF. The RapidIO specifications state that non-boot-code and non-host devices should initially have a device ID of 0xFF.<sup>4</sup>

- Hopcount = 0x00. Adjacent device should initially be accessed with hopcount 0.

- Maintenance offset = 0x00.

The returned DIDCAR value should then be compared to the list of DIDCAR values of all devices recognized by the application. If the adjacent device is a processor (for example, a MPC8548), the application should directly discover that processor. If the adjacent device is a switch (for example a Tsi568 switch), this switch must be correctly configured before proceeding with the discovery of the processors beyond it. For the example hardware, the adjacent device is a Tsi568 serial RapidIO switch.

### 3.2.2 Initial Configuration of Switch

This section describes the configuration of the Tsi568 RapidIO switch. Steps may need to be added, removed, or changed for other RapidIO switches.

### 3.2.2.1 Check Switch Port

We must determine the number of ports on the switch and the port to which the device running the bring-up application is connected. In the Tsi568 switch example, we read the switch port information CAR(RIO\_SW\_PORT). See Figure 19. A read from this register returns the number of ports on the device and the number of the port from which this register was read. The maintenance read has the following attributes:

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x14 Switch port information CAR is at offset 0x14.

|         | 0  | 1  | 2  | 3               | 4     | 5  | 6  | 7   | 8        | 9  | 10 | 11   | 12     | 13 | 14 | 15 |  |  |

|---------|----|----|----|-----------------|-------|----|----|-----|----------|----|----|------|--------|----|----|----|--|--|

| Field   |    |    |    |                 |       |    |    | Res | erved    |    |    |      |        |    |    |    |  |  |

| Setting |    |    |    |                 |       |    |    | 0x0 | 0000     |    |    |      |        |    |    |    |  |  |

|         | 16 | 17 | 18 | 19              | 20    | 21 | 22 | 23  | 24       | 25 | 26 | 27   | 28     | 29 | 30 | 31 |  |  |

| Field   |    |    | F  | PORT_           | TOTAL | -  |    |     | PORT_NUM |    |    |      |        |    |    |    |  |  |

| Setting |    |    |    | 0x <sup>-</sup> | 10    |    |    |     |          |    |    | Unde | fined. |    |    |    |  |  |

#### Figure 19. Format of Tsi568 RIO\_SW\_PORT Register

### 3.2.2.2 Read Back the Switch HBDIDLCSR

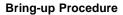

Each RapidIO device has a register (HBDIDLCSR) containing the device ID of the element in the system that configures it. See Figure 20. This register provides a locking mechanism, and an element should proceed to configure a device only if it gains the lock. The HBDIDLCSR of the switch can be read using a maintenance read with the following attributes:

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch

- Maintenance offset = 0x68. HBDIDLCSR is at offset 0x68

If the agent is not locked, the default value of this HBDIDLCSR is 0x0000\_FFFF. If a read of HBDIDLCSR yields any other value, the device is already locked, and the mechanism to deal with this situation is beyond the scope of this application note.

Figure 20. Format of the HBDIDLCSR

### 3.2.2.3 Lock HBDIDLCSR of Switch

To identify the processor running this application as the device that initializes the switch, its device ID is written into the switch HBDIDLCSR using a maintenance write with the following attributes:

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x68, Offset to HBDIDLCSR

### 3.2.2.4 Confirm that Switch Has Accepted Lock

The HBDIDLCSR is read to confirm that it is updated with the ID of the host device. If not, the lock was not accepted, and the host should not proceed to configure the switch. Rejection of the lock suggests that there is another host in the system, which is beyond the scope of this discussion. Refer to the interoperability specification for the bring-up requirements for multi-host systems [4]. The HBDIDLCSR can be read using a maintenance read with the following attributes:

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x68, Offset to HBDIDLCSR

### 3.2.2.5 Route Responses Back to Host

To ensure that responses issued by the processors beyond the switch are correctly routed to the requesting processor, we must initialize the routing information of the switch with that information. (Maintenance transactions to the switch are always routed back to the port from which they were received). The Tsi568 maintains an independent

look-up table for each port of the switch, so we can create different routing information on a per-port basis. However, it can also update all routing tables simultaneously using an indirect read/write mechanism. In this example, the routing tables for all ports are identical, and the indirect read/write mechanism is used. Figure 21 and Figure 22 show the RIO\_ROUTE\_CFG\_DESTID and the RIO\_ROUTE\_CFG\_PORT registers, which are used to update the routing tables for the whole device.

|       | 0               | 1  | 2  | 3   | 4  | 5  | 6  | 7   | 8    | 9  | 10 | 11   | 12     | 13 | 14 | 15 |

|-------|-----------------|----|----|-----|----|----|----|-----|------|----|----|------|--------|----|----|----|

| Field |                 |    |    |     |    |    |    |     | -    |    |    |      |        |    |    |    |

| e.g   |                 |    |    |     |    |    |    | 0x0 | 0000 |    |    |      |        |    |    |    |

|       | 16              | 17 | 18 | 19  | 20 | 21 | 22 | 23  | 24   | 25 | 26 | 27   | 28     | 29 | 30 | 31 |

| Field | LRG_CFG_DEST_ID |    |    |     |    |    |    |     |      |    |    | FG_D | EST_II | D  |    |    |

| e.g.  |                 |    |    | 0x( | 00 |    |    |     |      |    |    | 0x   | :00    |    |    |    |

#### Figure 21. RIO\_ROUTE\_CFG\_DESTID

|       | 0  | 1  | 2  | 3   | 4  | 5  | 6  | 7   | 8    | 9  | 10 | 11 | 12 | 13 | 14 | 15 |  |

|-------|----|----|----|-----|----|----|----|-----|------|----|----|----|----|----|----|----|--|

| Field |    |    |    |     |    |    |    |     | -    |    |    |    |    |    |    |    |  |

| e.g.  |    |    |    |     |    |    |    | 0x0 | 0000 |    |    |    |    |    |    |    |  |

|       | 16 | 17 | 18 | 19  | 20 | 21 | 22 | 23  | 24   | 25 | 26 | 27 | 28 | 29 | 30 | 31 |  |

| Field |    |    |    | -   |    |    |    |     | PORT |    |    |    |    |    |    |    |  |

| e.g.  |    |    |    | 0x0 | 00 |    |    |     | 0x02 |    |    |    |    |    |    |    |  |

#### Figure 22. RIO\_ROUTE\_CFG\_PORT

For example, if the host processor was connected to port 2, all packets bound for device ID 0 should be directed to port 2. The routing tables are updated with this information in 2 maintenance writes. First, write the device ID to be updated, in this case 0x00, to the RIO\_ROUTE\_CFG\_DESTID using a maintenance write with the following attributes.

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x70

Then write the number of the port to which packets for this device should be directed (in this case 0x02), to the RIO\_ROUTE\_CFG\_PORT using a maintenance write with the following attributes.

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x74

### 3.2.3 Discover the Devices Beyond the Tsi568 Switch

The next step is to identify which devices are connected to the other ports of the RapidIO switch. If any of these devices is another switch, or another RapidIO host it is beyond the scope of this simple application. Further details of how to discover systems with multiple hosts, or multiple switches can be found in the interoperability specification.<sup>4</sup> The example scenario is simplified by the assumption that there is only one switch, and all other

processors are configured as RapidIO agents. The following steps should be executed for each of the ports on the switch (with the exception of the port to which the processor running this application is attached).

### 3.2.3.1 Check Lane Synchronization and Alignment on Port N

Ensure that the port under investigation (port *n*) is initialized. If it is not initialized, then the remaining steps are omitted for this iteration. In the Tsi568 switch example, each of the ports has an error and status CSR (SPn\_ERR\_STAT). SPn\_ERR\_STAT[PORT\_OK] can be examined to determine if each port has successfully completed the RapidIO lane synchronization and alignment procedure with an adjacent device.<sup>1</sup> This maintenance transaction has the following attributes:

- Destination ID = 0xXX, ID is 'don't care' when accessing first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x158 (port0), 0x178 (port1), 0x198 (port2),....0x338 (port15)

### 3.2.3.2 Route Packets for Device ID 0xFF to Port N

The agents initially have a device ID of 0xFF. The routing table must be updated to ensure that packets with this destination are directed to the port under investigation using the indirect routing update mechanism described in Section 3.2.2.5, "Route Responses Back to Host." A value of 0xFF is written to the RIO\_ROUTE\_CFG\_DESTID and the port number is written to RIO\_ROUTE\_CFG\_PORT. For example, packets with a destination ID of 0xFF can be routed to port 4 by two maintenance writes. A maintenance write of 0xFF to RIO\_ROUTE\_CFG\_DESTID sets the destination ID for which the routing is to be changed:

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x70.

A maintenance write of *N* to RIO\_ROUTE\_CFG\_PORT updates the port to which these packets will be routed.

- Destination ID = 0xXX, ID is 'don't care' when accessing the first switch in the system.

- Hopcount = 0x00, Transaction applies to first switch.

- Maintenance offset = 0x74.

### 3.2.3.3 Read Back the DIDCAR of Device on Port N

The routing is now in place to permit access to the device connected to port n of the switch. The initial read should be to the DIDCAR to identify the device.

|         | 0         | 1         | 2    | 3                  | 4          | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|---------|-----------|-----------|------|--------------------|------------|----|----|----|----|----|----|----|----|----|----|----|

| Field   | _         | _         |      | TRGTID — HOP_COUNT |            |    |    |    |    |    |    |    |    |    |    |    |

| Setting |           | 0x3FC 0xF |      |                    |            |    |    |    |    |    |    |    |    |    |    |    |

|         | 16        | 17        | 18   | 19                 | 20         | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 |

| Field   | I         | HOP_C     | OUNT |                    | CFG_OFFSET |    |    |    |    |    |    |    |    |    |    |    |

| Setting | 0xF 0x000 |           |      |                    |            |    |    |    |    |    |    |    |    |    |    |    |

#### Figure 23. ROWTAR Setting for Accessing DIDCAR of Device on Port N

The read of the DIDCAR is a maintenance read with the following attributes:

- Destination ID = 0xFF, accessing the agent with a destination ID of 0xFF.

- Hopcount=0xFF, transaction bypasses switch.

- Maintenance offset = 0x00, offset to DIDCAR.

### 3.2.3.4 Read Back the HBDIDLCSR of Device on Port N

Each RapidIO device has a register (HBDIDCSR) which contains the device ID of the element in the system which is responsible for its configuration. This provides a locking mechanism and a device should only proceed with the configuration of a device if it gains the lock. The HBDIDLCSR is read using a maintenance read with the following attributes:

- Destination ID = 0xFF, accessing the agent with a destination ID of 0xFF

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance offset = 0x68, offset to HBDIDLCSR

If this device has not yet been locked, the default value for the HBDIDLCSR is 0xFFFF.

### 3.2.3.5 Lock HBDIDLCSR of Device on Port N

To identify the processor running this application as the initializing device, its device ID is written into the HBDIDLCSR of the device on Port n using a maintenance write with the following attributes:

- Destination ID = 0xFF, accessing the agent with a destination ID of 0xFF

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance offset = 0x68, offset to HBDIDLCSR

### 3.2.3.6 Confirm that Device on Port N Has Accepted Lock

The HBDIDLCSR register is read to confirm that it is updated with the host device ID. If not, the lock was not accepted, and the host should not further configure the device on this port. Rejection of the lock suggests that there is another host in the system, which is beyond the scope of this example. Refer to the SBTG specification for the bring-up requirements for multi-host systems.<sup>4</sup>

The HBDIDLCSR can be read using a maintenance read with the following attributes:

- Destination ID = 0xFF, accessing the agent with a destination ID of 0xFF.

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance Offset = 0x68, offset to HBDIDLCSR

### 3.2.3.7 Update the Device ID

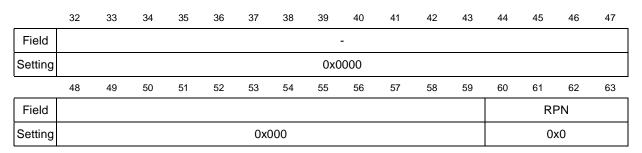

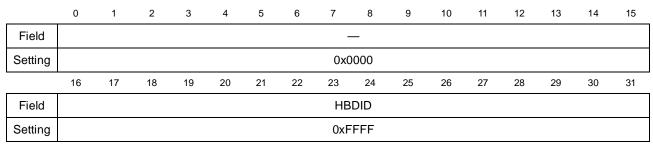

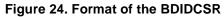

All the agents have an initial device ID of 0xFF. After the host discovers them, the host must allocate a permanent device ID by writing into the base device ID command and status register (BDIDCSR). See Figure 24. In the example, the host device, connected to Port 0, has a device ID of 0x00. The host allocates device IDs in ascending order to the agents it discovered. That is, the first agent to be discovered becomes Device ID 1, the next to be discovered becomes Device ID 2, and so on. In the BDIDCSR, the BDID field contains the device ID required in small transport systems, and LBDID contains the additional device ID bits required in a large transport system. The BDIDCSR can be updated by executing a maintenance write with the following attributes:

• Destination ID = 0xFF, accessing the agent with a destination ID of 0xFF.

## NP

#### Bring-up Procedure

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance Offset = 0x60, offset to BDIDCSR

|         | 0  | 1         | 2  | 3  | 4  | 5  | 6  | 7   | 8   | 9  | 10 | 11 | 12  | 13 | 14 | 15 |

|---------|----|-----------|----|----|----|----|----|-----|-----|----|----|----|-----|----|----|----|

| Field   |    |           |    | _  | -  |    |    |     |     |    |    | BD | DID |    |    |    |

| Setting |    | 0x00 0xnn |    |    |    |    |    |     |     |    |    |    |     |    |    |    |

|         | 16 | 17        | 18 | 19 | 20 | 21 | 22 | 23  | 24  | 25 | 26 | 27 | 28  | 29 | 30 | 31 |

| Field   |    |           |    |    |    |    |    | LB  | DID |    |    |    |     |    |    |    |

| Setting |    |           |    |    |    |    |    | 0xr | nnn |    |    |    |     |    |    |    |

### 3.2.3.8 Update the Routing Table, All Ports

After the BDIDCSR is updated with the new device ID, the routing table of the switch must be updated to reflect this information using the indirect write mechanism described in Section 3.2.2.5, "Route Responses Back to Host." The device ID allocated in the previous step should be written to the RIO\_ROUTE\_CFG\_DESTID, and the number of the port to which it connects should be written to RIO\_ROUTE\_CFG\_PORT.

### 3.2.3.9 Read Back from Updated Device ID

When the device ID is set, we verify that the device can be accessed using that device ID as the destination. That is, update the ROWTAR with the new device ID and read from the BDIDCSR with the following attributes:

- Destination ID = 0x02, 0x03, and so on. Accessing the agent with updated device ID.

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance Offset = 0x60, offset to BDIDCSR

Software should confirm that this read returns the expected value.

|         | 0                    | 1         | 2  | 3                                      | 4 | 5   | 6    | 7 | 8 | 9 | 10 | 11 | 12 | 13    | 14    | 15 |

|---------|----------------------|-----------|----|----------------------------------------|---|-----|------|---|---|---|----|----|----|-------|-------|----|

| Field   | -                    | _         |    |                                        |   | TRC | GTID |   |   |   | _  | _  |    | HOP_( | COUNT | -  |

| Setting |                      | 0x00C 0xF |    |                                        |   |     |      |   |   |   |    |    |    |       |       |    |

|         | 16                   | 17        | 18 | 19 20 21 22 23 24 25 26 27 28 29 30 31 |   |     |      |   |   |   |    |    |    |       |       |    |

| Field   | HOP_COUNT CFG_OFFSET |           |    |                                        |   |     |      |   |   |   |    |    |    |       |       |    |

| Setting | ng 0xF 0x000         |           |    |                                        |   |     |      |   |   |   |    |    |    |       |       |    |

Figure 25. ROWTAR for Accessing BDIDCSR on Device 3

## 3.3 Enable Access to Remote Configuration Space

To access the local configuration (CCSR) space on a remote processor, complete the following steps:

- 1. On the remote processor, set up the LCSBA1CSR to accept RapidIO transactions in a certain address range.

- 2. On the local processor, set up an outbound window with the correct address translation into the same range.

### NOTE

When the remote access to the remote configuration space is enabled, all further accesses to the agent devices occur by this method rather than by maintenance transactions.

### 3.3.1 Set Up Inbound LCS Window on Agent

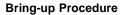

We set up the LCSBA1CSR of each of the processor to redirect RapidIO arriving at the 1 Mbyte window, starting at RapidIO address 0x0\_0100\_0000, to the CCSR area by setting the LCSBA1CSR as described here.

#### Figure 26. LCSBA1CSR Settings

In the example, LCSBA = 0x0010 and the 1 Mbyte LCS window starts at RapidIO address  $0x0_0100_0000$ . (LCSBA contains the most significant 14 bits of the 34-bit address). The update of the LCSBA1CSR on the agent is achieved using a maintenance write with the following attributes:

- Destination ID = 0x02, 0x03, and so on, depending on which agent is accessed.

- Hopcount = 0xFF, transaction bypasses switch.

- Maintenance offset = 0x5C, Offset to LCSBA1CSR.

### 3.3.2 Set Up Outbound Window on Host

To map outbound transactions into the address space with the appropriate destination device ID, a RapidIO outbound window is set up on the host for each agent processor. For each device found, a 1 MByte window is set up to map the outbound transactions to the LCSBAR on the agent. In the example, a 1 MByte window starting at address 0xc110000 is used to map RapidIO transactions to the LCS space of deviceID 1.

#### NOTE

We can also target multiple devices with the same translation address via a single, segmented window. However, errata in early MPC8548 silicon prevents the use of segments and sub-segments for targeting the same address space on multiple devices.

### 3.3.2.1 ROWBAR

|         | 0  | 1            | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9   | 10   | 11 | 12 | 13 | 14 | 15 |

|---------|----|--------------|----|----|----|----|----|----|----|-----|------|----|----|----|----|----|

| Field   |    |              |    | _  | -  |    |    |    |    | BEX | FADD |    |    | BA | DD |    |

| Setting |    | 0x00 0x0 0xC |    |    |    |    |    |    |    |     |      |    |    |    |    |    |

|         | 16 | 17           | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25  | 26   | 27 | 28 | 29 | 30 | 31 |

| Field   |    | BADD         |    |    |    |    |    |    |    |     |      |    |    |    |    |    |

| Setting |    | 0x1100       |    |    |    |    |    |    |    |     |      |    |    |    |    |    |

#### Figure 27. ROWBAR Settings for Remote CCSR Access

The base address register (ROWBAR), defines the start address of the window. The settings in the example are defined in Table 13.

| Bits  | Name    | Description and Setting                                                                                                                                             |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8-11  | BEXTADD | Window base extended address. Contains bits 0-3 of 36-bits address.<br>0x0 Extended addressing not used.                                                            |

| 12–31 | BADD    | Base address of outbound window. Source address that is the starting point for the outbound translation window.<br>0xC1100, Window starts at address 0x0_C110_0000. |

#### Table 13. ROWBAR Field Description and Setting

### 3.3.2.2 ROWAR

|         | 0         | 1  | 2   | 3  | 4      | 5   | 6   | 7  | 8    | 9  | 10         | 11  | 12 | 13          | 14  | 15 |  |  |

|---------|-----------|----|-----|----|--------|-----|-----|----|------|----|------------|-----|----|-------------|-----|----|--|--|

| Field   | EN        |    | _   |    | TFL    | JOV | PCI | _  | NS   | EG | NSS        | SEG |    | RD          | TYP |    |  |  |

| Setting | 0x80      |    |     |    |        |     |     |    |      | 0> | <b>(</b> 0 |     |    | 0           | x4  |    |  |  |

|         | 16        | 17 | 18  | 19 | 20     | 21  | 22  | 23 | 24   | 25 | 26         | 27  | 28 | 28 29 30 31 |     |    |  |  |

| Field   |           | WR | ΓΥΡ |    | — SIZE |     |     |    |      |    |            |     |    |             |     |    |  |  |

| Setting | g 0x5 0x0 |    |     |    |        |     |     |    | 0x13 |    |            |     |    |             |     |    |  |  |

#### Figure 28. Remote CCSR Window ROWAR Settings

The attributes register defines attributes of the transactions created by this window. This includes the priority and transaction types. It also defines the size of the window. The settings in the example are defined in Table 14.

#### Table 14. ROWAR Descriptions and Settings

| Bits | Name  | Description and Setting                                                                                                                                    |

|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | EN    | <ul><li>Window address translation enable. Note that for ROWAR0 this bit is read-only and hardwired to 1.</li><li>1 Address translation enabled.</li></ul> |

| 4–5  | TFLOV | Transaction flow level priority of transaction.00Lowest priority transaction request flow.                                                                 |

#### Table 14. ROWAR Descriptions and Settings

| Bits  | Name  | Description and Setting                                                                                                               |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| 6     | PCI   | Follow PCI transaction ordering rules.<br>0 Do not follow PCI transaction ordering rules.                                             |

| 8-9   | NSEG  | Number of segments in this window.         00       Single segment.                                                                   |

| 10-11 | NSSEG | Number of sub-segments in this window.<br>00 No sub-segments.                                                                         |

| 12–15 | RDTYP | Read transaction type. Transaction type to run on RapidIO interface if access is a read.<br>0x4 NREAD.                                |

| 16–19 | WRTYP | Write transaction type. Transaction type to run on RapidIO interface if access is a write.<br>0x5 NWRITER.                            |

| 26–31 | SIZE  | Outbound window size. Outbound window size n, which is the encoded 2 <sup>n+1</sup> -byte window size.<br>0x13 Window size is 1Mbyte. |

### 3.3.2.3 ROWTAR

N

| _       | 0   | 1   | 2  | 3  | 4  | 5   | 6    | 7   | 8   | 9  | 10  | 11  | 12 | 13 | 14 | 15 |

|---------|-----|-----|----|----|----|-----|------|-----|-----|----|-----|-----|----|----|----|----|

| Field   | LTG | TID |    |    |    | TRO | GTID |     |     |    | TRE | XAD |    | TR | AD |    |

| Setting |     |     |    |    |    | 0x0 | 004  |     |     |    |     |     |    | 0: | x0 |    |

|         | 16  | 17  | 18 | 19 | 20 | 21  | 22   | 23  | 24  | 25 | 26  | 27  | 28 | 29 | 30 | 31 |

| Field   |     |     |    |    |    |     |      | TF  | RAD |    |     |     |    |    |    |    |

| Setting |     |     |    |    |    |     |      | 0x1 | 000 |    |     |     |    |    |    |    |

### Figure 29. ROWTAR*n* Settings for Remote CCSR Access

The settings in the example are defined in Table 15.

### Table 15. ROWTARn Descriptions and Settings

| Bits  | Name   | Description and Setting                                                                                                        |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| 0–1   | LTGTID | Corresponds to bits 6-7 of device ID in large transport systems.<br>0x00 This application note assumes small transport system. |

| 2–9   | TRGTID | Target ID for RapidIO packet.<br>0x01 Transactions have destination ID of 1.                                                   |

| 10–11 | TREXAD | Translation extended address of outbound window.<br>00 The 2 extended address bits are both zero.                              |

| 12–31 | TRAD   | Translation address of outbound window.<br>0x01000 Outbound transactions start at address 0x0_0100_0000.                       |

### 3.3.3 Confirm Access to Remote LCS

The software should verify that the local configuration space of the agent can be read in this way. For example, with the ROW on the host and the LCS window on agent 1 set up as shown in the preceding figures, the accesses should return the following values:

- Reading host processor address 0x0\_C110\_0000 returns the CCSRBAR of processor 1.

- Reading host processor address 0x0\_C11C\_0000 returns the DIDCAR of processor 1.

- Reading host processor address 0x0\_C11C\_005C returns the LCSBA1CSR of processor 1.

## 3.4 Boot over RapidIO

In the example hardware, some agents can be configured to boot from their local Flash devices, and others can be configured to boot over RapidIO. This section describes how to boot over RapidIO. A device that is to boot over RapidIO must be configured as follows: