### Freescale Semiconductor

**Application Note**

AN3045 Rev. 3, 5/2006

## A Comparison of the MPC5200B (Mask Set M62C) with Prior MPC5200 Versions

by: Charles Melear Infotainment, Multimedia, and Telematics Division

## 1 Overview

This document describes the basic differences between the MPC5200B (Mask Set M62C Rev. 1) and prior revisions of the MPC5200 microprocessors. In the context of this document, MPC5200B always refers to the device built with Mask Set M62C Rev. 1. The MPC5200B adds enhancements to the device, including an updated SDRAM memory controller, upgrades to the programmable serial controller, and other functions to improve the operation of the device. Fixes to known errata were also incorporated into the MPC5200B, as well as features for improved testability. The MPC5200B microcontroller is based on an e300 core using the PowerPC<sup>TM</sup> instruction set.

The MPC5200B pinout is identical to its predecessor, the MPC5200.

While the MPC5200B is pin compatible with prior versions of the MPC5200, there are significant differences in the electrical characteristics of the pins, particularly with respect to the drive strength and slew rate capabilities on the SDRAM Bus.

#### **Table of Contents**

| Ove  | rview1                                                                                                                       |

|------|------------------------------------------------------------------------------------------------------------------------------|

| Cha  | nges to the Hardware Specification 2                                                                                         |

| 2.1  | Electrical and Timing Characteristics 2                                                                                      |

| 22   | AC Electrical Characteristics—                                                                                               |

|      | Memory Interface                                                                                                             |

| 23   | I/O Pins                                                                                                                     |

|      | HRESET                                                                                                                       |

|      | Reset Configuration                                                                                                          |

|      | •                                                                                                                            |

|      | nges to the Programmer's Interface                                                                                           |

| 3.1  | CDM Clock Enable Register                                                                                                    |

|      | —MBAR + 0x0214                                                                                                               |

| 3.2  | CDM 48-MHz Fractional Divider                                                                                                |

|      | Configuration Register—MBAR + 0x02106                                                                                        |

| 3.3  | SDRAM Memory Controller 8                                                                                                    |

| 3.4  | BestComm                                                                                                                     |

| 3.5  | PCI                                                                                                                          |

| 3.6  | PSC                                                                                                                          |

| 3.7  | Registers Added To Implement                                                                                                 |

|      | the Enhanced AC97 Mode                                                                                                       |

| 3.8  | l <sup>2</sup> C                                                                                                             |

| 0.0  |                                                                                                                              |

| 0.0  | LPC/GPIO 55                                                                                                                  |

| 3.10 | MSCAN 56                                                                                                                     |

| 3.11 | ID Codes                                                                                                                     |

| Doc  | umentation                                                                                                                   |

|      | Cha<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>Cha<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 |

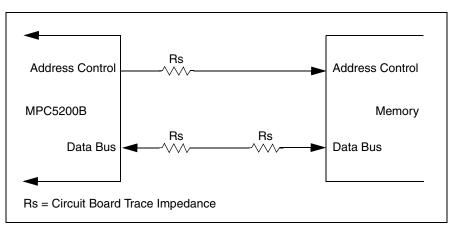

#### Changes to the Hardware Specification

When upgrading an existing MPC5200 design to use the MPC5200B, it is imperative that circuit board layout and signal line impedance matching issues be checked for proper performance. In particular, series termination resistors, as shown in Figure 1, must match the PC board line impedance as closely as possible.

#### NOTE

Place termination resistors as close to package pins as possible.

Figure 1. Proper Use of Series Termination Resistors

## 2 Changes to the Hardware Specification

### 2.1 Electrical and Timing Characteristics

The target for the electrical and timing characteristics of the MPC5200B is the MPC5200 hardware specifications.

### 2.2 AC Electrical Characteristics—Memory Interface

The improved DDR interface (DQS) results in a changed timing specification. Refer to the *MPC5200B* User's Guide for details.

## 2.3 I/O Pins

Additional Schmitt Trigger inputs have been added to these pins for better noise rejection:

- PSC1\_3

- PSC2\_3

- PSC3\_2

- PSC6\_3

- JTAG\_TCK

The pins associated with the PSC ports can be used as the BITCLOCK for the AC97 interface or the CLOCK for the CODEC interface. The JTAG\_TCK pin is the clock input for the JTAG interface. Schmitt Triggers on these inputs improve noise immunity/rejection as well as system performance and reliability. This improvement does not require any system level design changes.

### 2.4 HRESET

The MPC5200B HRESET pin is asserted when Power On Reset is asserted, regardless of whether the SYS\_XTAL clock is running or not.

On prior versions of the MPC5200, a running system clock was required to configure the internal circuitry driving the HRESET pin.

This means that for the period of time between the application of power and the start of the SYS\_XTAL clock, the HRESET pin was not driven to a specified value. If by random chance the HRESET pin assumed a logic 1 as its output value, the HRESET pin would rise along with Vdd during power up until the system clock started. As soon as the SYS\_XTAL clock started, the HRESET pin would be actively driven to a logic 0 (assuming that POR is currently being driven to a logic 0).

Some applications used the HRESET pin to hold various peripherals, including certain FLASH memory devices, in the reset state. By allowing the HRESET pin to float to a logic 1 during the time that power was being applied, these peripherals would momentarily be taken out of reset. In some cases, this condition was responsible for memory corruption issues.

Actively forcing HRESET on the MPC5200B to a logic 0 while Power On Reset is asserted, even if the SYS\_XTAL clock has not started, avoids these reset issues.

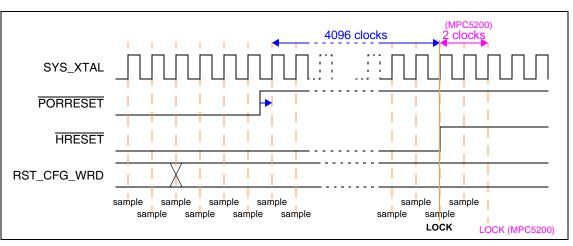

## 2.5 Reset Configuration

During reset (HRESET and PORRESET), the reset configuration word is latched in the related reset configuration word register with each rising edge of the SYS\_XTAL signal. If both resets (HRESET and PORRESET) are inactive (high), the contents of this register get locked.

Figure 2. Reset Configuration Word Locking

For the MPC5200B, as well as prior versions of the device, pins that are configured by the assertion of Power On Reset/HRESET will maintain their reset state as long as POR or HRESET is asserted. That is, even though the configuration word is sampled on each rising edge of the SYS\_XTAL clock, the actual microcontroller pins maintain their reset state until HRESET is released. Upon the release of HRESET, the various pins assume the state controlled by the configuration word.

In versions of the MPC5200 prior to the MPC5200B, the configuration word was latched and locked into the reset configuration register on the second rising edge of the SYS\_XTAL clock after the release of HRESET. This meant that the external circuitry driving the various configuration pins of prior versions of the MPC5200 had to continue to drive the configuration pins for two additional SYS\_XTAL clock cycles after HRESET was released to insure that the configuration word was properly latched. Also, any other devices that could possibly drive the configuration pins had to be held in reset for these two SYS\_XTAL clock cycles so that potential conflict issues would be avoided.

The MPC5200B latches and locks the configuration word into the reset configuration register on the first rising edge of SYS\_XTAL after the release of HRESET. This change makes external configuration word circuitry easier to design as it significantly reduces the hold time for the logic driving the reset configuration word.

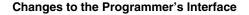

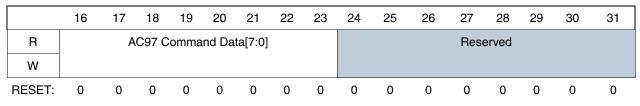

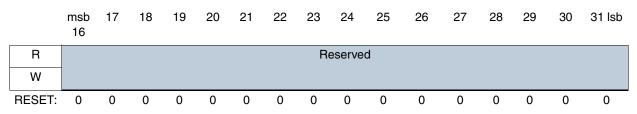

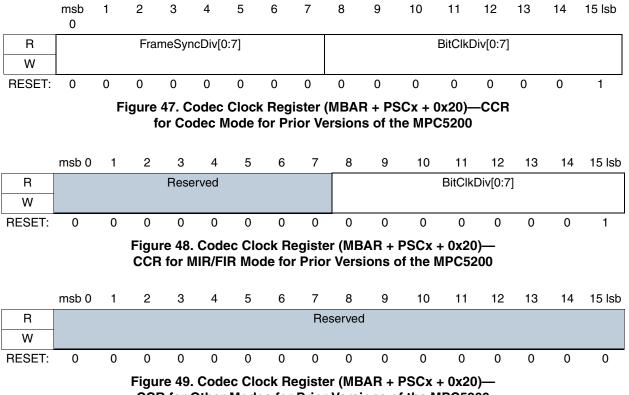

### 3 Changes to the Programmer's Interface

There are some differences in the programmer's interface between the MPC5200B and prior versions of the MPC5200. Some registers were added, and some reserved bits are used to provide extra functionality.

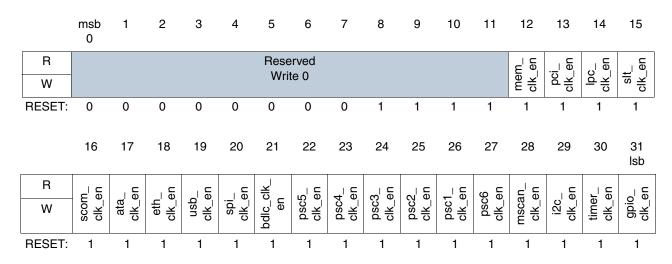

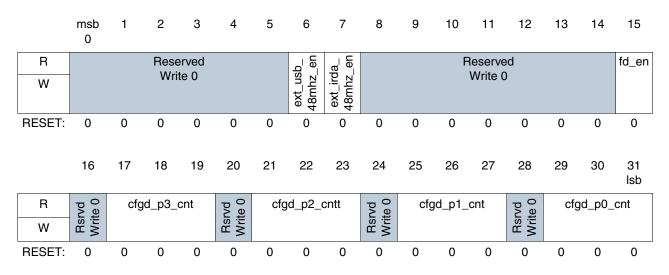

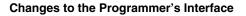

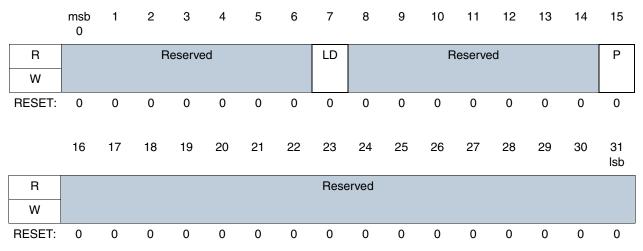

### 3.1 CDM Clock Enable Register—MBAR + 0x0214

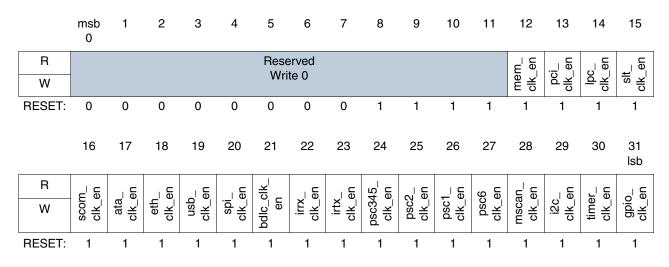

Bit 24 (psc345\_clk\_en) is separated into 3 bits psc3\_clk\_en, psc4\_clk\_en, and psc5\_clk\_en. The function of bits IR\_TX and IR\_RX are replaced by psc4\_clk\_en and psc5\_clk\_en, respectively.

Only bits 22, 23 and 24 have changed between the MPC5200B and prior versions of the MPC5200.

On prior versions of the MPC5200, bits 22 and 23 of the CDM clock enable register were associated with an IR function. The IR function has been removed from the MPC5200B, along with the functionality of these two bits. Bit 24 of this register on prior versions of the MPC5200 was used to enable the IP bus clock to PSC3, PSC4, and PSC5. On the MPC5200B, bits 22 and 23 are now used to enable the IP bus clock to PSC5 and PSC4 respectively. Now, bit 24 only enables the IP bus clock to PSC3.

In all versions of the MPC5200, the RESET state of all the clock enable bits in the CDM clock enable register is a logic 1. That is, all of the clock enable bits are set to enable. The software for prior versions of the MPC5200 may have to be changed to work on the MPC5200B. Specifically, if the user's current software wrote bits 22 or 23 to a logic 0 and the user wants to use PSC4 or PSC5, these bits will have to be written to a logic 1. If the user's software does not write to this register, then no software changes will be required. That is, PSC4 and PSC5 will be enabled after the release of reset.

### 3.1.1 CDM Clock Enable Register for MPC5200B

Figure 3. CDM Clock Enable Register for MPC5200B

## 3.1.2 CDM Clock Enable Register for Prior Versions of the MPC5200

#### Figure 4. CDM Clock Enable Register for Prior Versions of the MPC5200

**Note:** The MPC5200B does not contain the IR module that was present on prior versions of the MPC5200. The clock enable bits referred to above enabled the clocks to this module; however, in the PSC module, there is a CODEC mode that does implement an IR function. This note is for information only.

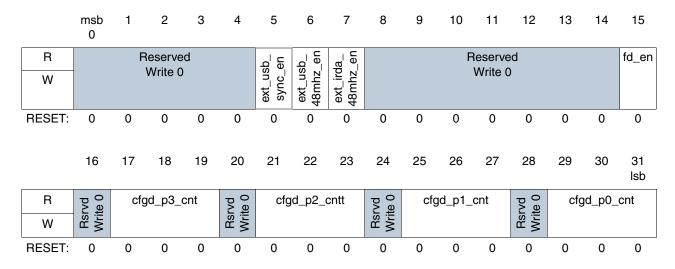

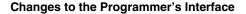

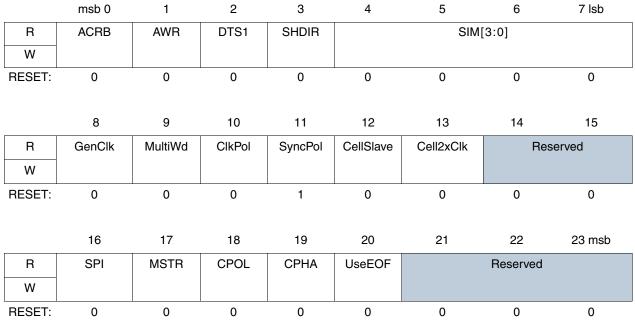

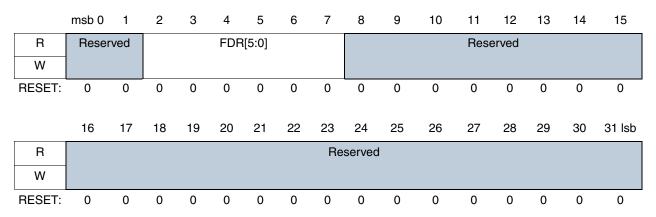

### 3.2 CDM 48-MHz Fractional Divider Configuration Register—MBAR + 0x0210

Bit 5 (ext\_usb\_clk\_sync) is added.

The ability to synchronize the external USB clock with the internal buses was added to improve USB performance above 1 Mbit/second. The user should set this bit when using USB at higher speeds.

The default state of bit 5 is a logic 0, which causes the external 48-MHz clock to not be synchronized with the internal clock. If the user's software for prior versions of the MPC5200 wrote this bit to a logic 0, then no changes to the software will be required for the MPC5200B; however, if the user wants to take advantage of this feature, the software will have to be modified. That is, bit 5 will need to be set to a logic 1.

Only bit 5 of this register is affected.

## 3.2.1 CDM 48-MHz Fractional Divider Configuration Register for MPC5200B

Figure 5. CDM 48-MHz Fractional Divider Configuration Register for MPC5200B

## NP

### 3.2.2 CDM 48-MHz Fractional Divider Configuration Register for Prior Versions of the MPC5200

Figure 6. CDM 48-MHz Fractional Divider Configuration Register for Prior Versions of the MPC5200

### 3.3 SDRAM Memory Controller

### 3.3.1 New Module Design

The hardware for the SDRAM memory controller has been redesigned; however, the module has complete backward software compatibility with prior versions of the MPC5200.

### 3.3.2 Multiple Open Pages

The support of multiple open pages is an internal function of the MPC5200B memory controller. It adds functionality to the SDRAM interface but does not require any change to software.

### 3.3.3 Support of 16-bit Memory Interface

The SDRAM bus now supports both 16-bit and 32-bit memory structures. Bit 18 of the SDRAM bus control register (MBAR + 0x0104) has been added to select between the modes. To convert an existing MPC5200 design to the MPC5200B, bit 18 should be a logic 0 (select 32-bit port size).

# 3.3.4 SDRAM Bus Memory Controller Control Register—MBAR + 0x0104

#### msb 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Rsvd hi Rsvd ref\_interval[0:5] R mode cke ddr drive ref addr \_rule \_en \_en W RESET: 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 lsb R Reserved mem Rsv dqs\_oe Reserved Rsvd d W soft soft ps \_ref \_pre 0 0 0 0 0 0 0 RESET: 0 0 0 0 0 0 0 0 0

#### 3.3.4.1 Memory Controller Control Register for the MPC5200B

Figure 7. Memory Controller Control Register for the 20065200B

## 3.3.4.2 Memory Controller Control Register for Prior Versions of the MPC5200

|        | msb 0 | 1    | 2    | 3   | 4  | 5    | 6   | 7    | 8    | 9     | 10      | 11 | 12      | 13      | 14   | 15        |

|--------|-------|------|------|-----|----|------|-----|------|------|-------|---------|----|---------|---------|------|-----------|

| R      | mode  | cke  | ddr  | ref |    | Rsvd |     |      | Rsvd |       |         | r  | ef_inte | rval[0: | 5]   |           |

| W      | _en   |      |      | _en |    |      |     | addr |      | _rule |         |    |         |         |      |           |

| RESET: | 0     | 0    | 0    | 0   | 0  | 0    | 0   | 0    | 0    | 0     | 0       | 0  | 0       | 0       | 0    | 0         |

|        |       |      |      |     |    |      |     |      |      |       |         |    |         |         |      |           |

|        | 16    | 17   | 18   | 19  | 20 | 21   | 22  | 23   | 24   | 25    | 26      | 27 | 28      | 29      | 30   | 31<br>Isb |

|        |       | _    |      |     | -  |      |     |      |      | _     |         |    |         | -       |      |           |

| R      |       | Rese | rved |     |    | dqs_ | _oe |      |      | н     | leserve | d  |         |         |      | Rsvd      |

| W      |       |      |      |     |    |      |     |      |      |       |         |    |         | soft    | soft |           |

|        |       |      |      |     |    |      |     |      |      |       |         |    |         | _ref    | _pre |           |

| RESET: | 0     | 0    | 0    | 0   | 0  | 0    | 0   | 0    | 0    | 0     | 0       | 0  | 0       | 0       | 0    | 0         |

Figure 8. Memory Controller Control Register for Prior Versions of the MPC5200

### **3.3.5** BURST TERMINATION

BURST TERMINATION is an SDRAM controller command. This command was not functional on revisions of the MPC5200 prior to the MPC5200B. The BURST TERMINATION command is fully functional on the MPC5200B.

The BURST command is issued automatically by the SDRAM bus memory controller to terminate a burst read or write when only one word of data needs to be transferred. This function is handled automatically by the SDRAM bus memory controller.

This is a hardware change inside the SDRAM memory controller and has no effect on system software. The BURST TERMINATION command simply improves performance on the SDRAM bus.

### 3.3.6 H/W Wakeup from Deep Sleep Mode

The MPC5200B SDRAM memory controller automatically handles putting the external memory devices into self-refresh mode when the processor enters the deep sleep mode. Likewise, when the deep sleep mode of the MPC5200B is exited, the SDRAM memory controller automatically causes the SDRAM to exit self-refresh mode.

Note that SDRAMs from various manufacturers require certain amounts of delay time between exiting the self-refresh mode and resuming data fetches. It is the responsibility of the software writer to insure that this delay is enforced.

When entering the deep sleep mode, the SDRAM memory controller automatically issues a series of commands to the SDRAM memory devices to put them into self-refresh mode. The SDRAM memory controller also controls the state of the clock enable pin to properly put the SDRAM devices into the self-refresh mode.

Hardware wakeup from deep sleep causes the SDRAM memory controller to automatically issue a series of commands to the SDRAM memory devices to take them out of self-refresh mode. Also, the state of the MPC5200B clock enable line is properly set by the SDRAM memory controller. No change to software is required because of this hardware change, other than to enforce the proper amount of delay between exiting the self-refresh mode of the SDRAM devices and the first memory access to those devices.

### 3.3.7 New 32-bit to 64-bit XLB Gasket

The new XL bus gasket and the improved read clock recovery circuit are internal improvements that do not affect system software. This change is a hardware change only and is for improvement of internal system bus performance.

### 3.3.8 New DQS Read Data Sampling Circuitry

Configuration register 1 MBAR + 0x0108 - Bit [4] has been added to the swt2rwp field.

The width of the single write to read-write-precharge delay field has been increased from 3 to 4 bits. The default state of the added bit is a logic 0. On prior versions of the MPC5200, this bit was reserved.

The user software for versions of the MPC5200 prior to the MPC5200B should be checked to see that the added bit was written to a logic 0 to insure compatibility.

### 3.3.9 SDRAM Bus Memory Controller Configuration Register 1— MBAR + 0x0108

### 3.3.9.1 Memory Controller Configuration Register 1 for MPC5200B

|        | msb 0 | 1    | 2      | 3  | 4  | 5   | 6     | 7  | 8   | 9     | 10      | 11 | 12   | 13  | 14     | 15     |

|--------|-------|------|--------|----|----|-----|-------|----|-----|-------|---------|----|------|-----|--------|--------|

| R      |       | srd2 | rwp    |    |    | swt | 2rwp  |    |     | rd_la | tency   |    | Rsvd |     | act2rv | V      |

| W      |       |      |        |    |    |     |       |    |     |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0  | 0   | 0     | 0  | 0   | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

|        |       |      |        |    |    |     |       |    |     |       |         |    |      |     |        |        |

| _      | 16    | 17   | 18     | 19 | 20 | 21  | 22    | 23 | 24  | 25    | 26      | 27 | 28   | 29  | 30     | 31 lsb |

| R      | Rsvd  | F    | ore2ad | ct |    | re  | f2act |    | Rsv | w     | r_laten | су |      | Res | served |        |

| W      |       |      |        |    |    |     |       |    | d   |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0  | 0   | 0     | 0  | 0   | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

Figure 9. Memory Controller Configuration Register 1 for MPC5200B

#### Table 1. Memory Controller Configuration Register 1 Field Descriptions

| Bit | Name | Description                                                                                                                                                                           |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:7 | •    | Single Write to Read/Write/Precharge delay. Limiting case is Write to Precharge.<br>For DDR, suggested value = 0x3 ( $t_{WR}$ + 1 clk)<br>For SDR, suggested value = 0x2 ( $t_{WR}$ ) |

## 3.3.9.2 Memory Controller Configuration Register 1 for Prior Versions of the MPC5200

|        | msb 0 | 1    | 2      | 3  | 4    | 5  | 6       | 7  | 8   | 9     | 10      | 11 | 12   | 13  | 14     | 15     |

|--------|-------|------|--------|----|------|----|---------|----|-----|-------|---------|----|------|-----|--------|--------|

| R      |       | srd2 | rwp    |    | Rsvd |    | swt2rwp | )  |     | rd_la | tency   |    | Rsvd |     | act2rv | v      |

| W      |       |      |        |    |      |    |         |    |     |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0    | 0  | 0       | 0  | 0   | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

|        |       |      |        |    |      |    |         |    |     |       |         |    |      |     |        |        |

|        | 16    | 17   | 18     | 19 | 20   | 21 | 22      | 23 | 24  | 25    | 26      | 27 | 28   | 29  | 30     | 31 lsb |

| R      | Rsvd  | Ŗ    | ore2ac | t  |      | re | f2act   |    | Rsv | w     | r_laten | су |      | Res | served |        |

| W      |       |      |        |    |      |    |         |    | d   |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0    | 0  | 0       | 0  | 0   | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

Figure 10. Memory Controller Configuration Register 1 for Prior Versions of the MPC5200

Table 2. Memory Controller Configuration Register 1 Field Descriptions

| Bit | Name | Description                                                                                                                                                                           |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | _    | Reserved                                                                                                                                                                              |

| 5:7 |      | Single Write to Read/Write/Precharge delay. Limiting case is Write to Precharge.<br>For DDR, suggested value = 0x3 ( $t_{WR}$ + 1 clk)<br>For SDR, suggested value = 0x2 ( $t_{WR}$ ) |

### 3.3.10 Read Clock Recovery (RCR)—Registers Added

The read clock recover registers are located from MBAR + 0x090 to MBAR + 0xBC. User software MUST NOT write to these registers.

User software should be checked to make sure that these memory locations are not accessed to insure MPC5200B compatibility.

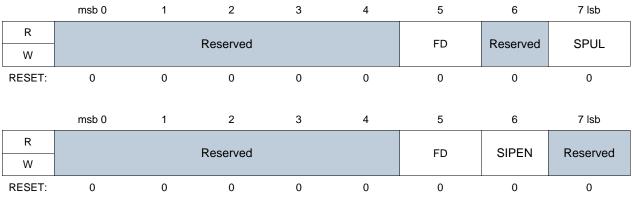

### 3.4 BestComm

### 3.4.1 Bus Snoop Enable Bit Added in the XLB Arbiter

Bit 15 of the arbiter configuration register has been added. This bit enables BestComm XL address bus snooping. This feature is enabled from the release of reset.

The BestComm unit fetches data from memory and places it in its read line buffer in preparation for transmitting that data through one of the peripheral elements, such as the Ethernet port. If the CPU writes to the memory location just accessed by the BESTComm unit but before the data is transmitted from the read line buffer, the bus snooping logic will mark the data as dirty in the read line buffer and cause the XL bus arbiter to re-fetch the fresh data from memory.

User software should be checked to ensure that this bit is set to the desired setting.

### 3.4.2 BESTComm Arbiter Configuration Register-MBAR + 0x1F40

### 3.4.2.1 Arbiter Configuration Register for MPC5200B

#### Figure 11. Arbiter Configuration Register for MPC5200B

#### **Table 3. Arbiter Configuration Field Descriptions**

| Bit | Name | Description                                                                                                         |

|-----|------|---------------------------------------------------------------------------------------------------------------------|

| 15  |      | BestComm snooping disable.<br>0 BestComm XLB address snooping enabled.<br>1 BestComm XLB address snooping disabled. |

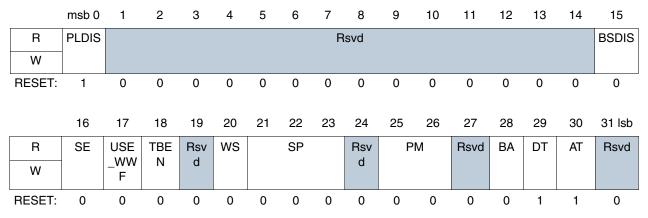

### 3.4.2.2 Arbiter Configuration Register for Prior Versions of the MPC5200

|        | msb 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8   | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|--------|-------|---|---|---|---|---|---|---|-----|---|----|----|----|----|----|----|

| R      | PLDIS |   |   |   |   |   |   |   | Rsv | d |    |    |    |    |    |    |

| W      |       |   |   |   |   |   |   |   |     |   |    |    |    |    |    |    |

| RESET: | 1     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0  | 0  | 0  | 0  | 0  | 0  |

|        | 16 | 17       | 18  | 19  | 20 | 21 | 22 | 23 | 24  | 25 | 26 | 27   | 28 | 29 | 30 | 31 lsb |

|--------|----|----------|-----|-----|----|----|----|----|-----|----|----|------|----|----|----|--------|

| R      | SE | USE      | TBE | Rsv | WS |    | SP |    | Rsv | Р  | М  | Rsvd | BA | DT | AT | Rsvd   |

| W      |    | _WW<br>F | Ν   | d   |    |    |    |    | d   |    |    |      |    |    |    |        |

| RESET: | 0  | 0        | 0   | 0   | 0  | 0  | 0  | 0  | 0   | 0  | 0  | 0    | 0  | 1  | 1  | 0      |

Figure 12. Arbiter Configuration Register for Prior Versions of the MPC5200

| Bit  | Name | Description |

|------|------|-------------|

| 1:15 | —    | Reserved    |

#### **Table 4. Arbiter Configuration Field Descriptions**

### 3.4.3 External Breakpoint

The SDMA debug module control register, for both the MPC5200B and prior versions of the MPC5200, are exactly alike; however, in versions of the MPC5200 prior to Revision B, the "E" and "EB" bits did not work. In the MPC5200B, the bits do work as described. If these bits were set to a logic 1 in versions of the MPC5200 prior to Revision B, external breakpoints would not cause the BestComm unit to halt. If software written for versions of the MPC5200 prior to Revision B, set the "E" and "EB" bits to a logic 1, and this software is used on the MPC5200B, external breakpoints will cause the BestComm unit to halt. For compatibility, check the software to see that the "E" and "EB" bits are set to a logic 0 when upgrading to the MPC5200B. This may affect existing user software that uses the SDMA debug module control register at MBAR + 0x1278.

### 3.4.3.1 SDMA Debug Module Control Register—MBAR + 0x1278

|        | msb 0 | 1  | 2   | 3       | 4      | 5    | 6  | 7      | 8       | 9  | 10      | 11       | 12 | 13 | 14 | 15     |

|--------|-------|----|-----|---------|--------|------|----|--------|---------|----|---------|----------|----|----|----|--------|

| R      |       |    |     |         |        |      |    | Bloc   | ck Task | S  |         |          |    |    |    |        |

| W      |       |    |     |         |        |      |    |        |         |    |         |          |    |    |    |        |

| RESET: | 0     | 0  | 0   | 0       | 0      | 0    | 0  | 0      | 0       | 0  | 0       | 0        | 0  | 0  | 0  | 0      |

|        |       |    |     |         |        |      |    |        |         |    |         |          |    |    |    |        |

|        | 16    | 17 | 18  | 19      | 20     | 21   | 22 | 23     | 24      | 25 | 26      | 27       | 28 | 29 | 30 | 31 lsb |

| R      | AA    | В  | Com | oaratoi | r Type | Comp |    | r Type | and/    | E  | EU brea | lkpoints | ;  | Е  | Ι  | EB     |

| W      |       |    |     | 1       |        |      | 2  |        | or      |    |         |          |    |    |    |        |

| RESET: | 0     | 0  | 0   | 0       | 0      | 0    | 0  | 0      | 0       | 0  | 0       | 0        | 0  | 0  | 0  | 0      |

### 3.4.3.2 SDMA Debug Module Control Register for MPC5200B

Figure 13. Debug Module Control Register for MPC5200B

| Table 5. SDMA | <b>A Debug Module Control Field Descriptions</b> |

|---------------|--------------------------------------------------|

|---------------|--------------------------------------------------|

| Bit   | Name                 | Description                                                                                                                                                                                                                                                                                   |

|-------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Block Tasks          | Specify for each of tasks 15-0, whether to block that task with detection of a breakpoint<br>(bit 0 halts TASK 15, bit 1 halts TASK 14, etc)<br>0 Do not block task<br>1 Block the task                                                                                                       |

| 16    | AA                   | AutoArm—specifies whether or not the triggered bit dbgStatusReg[16] will be<br>automatically reset to 0 following the saving of context for a breakpoint. This bit is set to 0<br>at reset.<br>0 Triggered bit will not be automatically reset<br>1 Triggered bit will be automatically reset |

| 17    | В                    | Breakpoint—This bit specifies whether or not to take a breakpoint. This bit is set to 0 at reset.<br>0 Disable breakpoints<br>1 Enable breakpoints                                                                                                                                            |

| 18:20 | Comparator<br>Type 1 | Comparator 1 type—These bits specify the type of data that has been loaded into comparator 1.                                                                                                                                                                                                 |

| Bit   | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21:23 | Comparators<br>Type 2 | Comparator 2 type—These bits specify the type of data that has been loaded into comparator 2.                                                                                                                                                                                                                                                                                           |

| 24    | and / or              | <ul> <li>AND/OR—This specifies what type of operation is to be used with the comparators. This bit is set to 0 at reset.</li> <li>0 Indicates an OR'ing of the comparators</li> <li>1 Indicates an AND'ing of the comparators</li> </ul>                                                                                                                                                |

| 25:28 | EU breakpoints        | euBreakpoint These bits indicate that a breakpoint has occurred in one of the four execution units. Each execution unit has one bit dedicated to it. A 1 in any of these bits indicates that the associated execution unit has issued breakpoint. These bits are sticky and must be overwritten to continue. These bits are cleared to zero at reset. MPC5200B has integrated only EU3. |

| 29    | E                     | <ul> <li>Enable external breakpoint to cause HALT condition.</li> <li>0 Do not enable external breakpoint to cause a halt condition</li> <li>1 Allow external breakpoint to cause a halt condition</li> </ul>                                                                                                                                                                           |

| 30    | I                     | Enable internal breakpoint<br>0 Do not enable internal breakpoint to cause a halt condition<br>1 Allow internal breakpoint to cause a halt condition                                                                                                                                                                                                                                    |

| 31    | EB                    | Master breakpoint enable (this bit must be always set to allow any kind of breakpoint to halt<br>the task)<br>0 Disable external breakpoint<br>1 Enable external breakpoint                                                                                                                                                                                                             |

#### Table 5. SDMA Debug Module Control Field Descriptions (continued)

## 3.4.3.3 SDMA Debug Module Control Register for Prior Versions of the MPC5200

|        | msb 0 | 1  | 2   | 3       | 4    | 5    | 6       | 7    | 8      | 9  | 10      | 11      | 12 | 13 | 14 | 15     |

|--------|-------|----|-----|---------|------|------|---------|------|--------|----|---------|---------|----|----|----|--------|

| R      |       |    |     |         |      |      |         | Bloc | k Task | S  |         |         |    |    |    |        |

| W      |       |    |     |         |      |      |         |      |        |    |         |         |    |    |    |        |

| RESET: | 0     | 0  | 0   | 0       | 0    | 0    | 0       | 0    | 0      | 0  | 0       | 0       | 0  | 0  | 0  | 0      |

|        |       |    |     |         |      |      |         |      |        |    |         |         |    |    |    |        |

|        | 16    | 17 | 18  | 19      | 20   | 21   | 22      | 23   | 24     | 25 | 26      | 27      | 28 | 29 | 30 | 31 lsb |

| R      | AA    | В  | Com | parator | Туре | Comp | parator | Туре | and/   | I  | EU brea | kpoints |    | Е  | Ι  | EB     |

| W      |       |    |     | 1       |      |      | 2       |      | or     |    |         |         |    |    |    |        |

| RESET: | 0     | 0  | 0   | 0       | 0    | 0    | 0       | 0    | 0      | 0  | 0       | 0       | 0  | 0  | 0  | 0      |

Figure 14. SDMA Debug Module Control Register for Prior Versions of the MPC5200

| Bit   | Name                  | Description                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Block Tasks           | Specify for each of tasks 15-0, whether to block that task with detection of a breakpoint (bit                                                                                                                                                                                                                                                                                          |

| 0.15  | DIUCK TASKS           | 0 halts TASK 15, bit 1 halts TASK 14, etc)                                                                                                                                                                                                                                                                                                                                              |

|       |                       | 0 Do not block task                                                                                                                                                                                                                                                                                                                                                                     |

|       |                       | 1 Block the task                                                                                                                                                                                                                                                                                                                                                                        |

| 16    | AA                    | AutoArm—specifies whether or not the triggered bit dbgStatusReg[16] will be<br>automatically reset to 0 following the saving of context for a breakpoint. This bit is set to 0<br>at reset.<br>0 Triggered bit will not be automatically reset                                                                                                                                          |

|       |                       | 1 Triggered bit will be automatically reset                                                                                                                                                                                                                                                                                                                                             |

| 17    | В                     | Breakpoint—This bit specifies whether or not to take a breakpoint. This bit is set to 0 at reset.<br>0 Disable breakpoints<br>1 Enable breakpoints                                                                                                                                                                                                                                      |

| 18:20 | Comparator<br>Type 1  | Comparator 1 type—These bits specify the type of data that has been loaded into comparator 1.                                                                                                                                                                                                                                                                                           |

| 21:23 | Comparators<br>Type 2 | Comparator 2 type—These bits specify the type of data that has been loaded into comparator 2.                                                                                                                                                                                                                                                                                           |

| 24    | and / or              | <ul> <li>AND/OR—This specifies what type of operation is to be used with the comparators. This bit is set to 0 at reset.</li> <li>0 Indicates an OR'ing of the comparators</li> <li>1 Indicates an AND'ing of the comparators</li> </ul>                                                                                                                                                |

| 25:28 | EU breakpoints        | euBreakpoint These bits indicate that a breakpoint has occurred in one of the four execution units. Each execution unit has one bit dedicated to it. A 1 in any of these bits indicates that the associated execution unit has issued breakpoint. These bits are sticky and must be overwritten to continue. These bits are cleared to zero at reset. MPC5200B has integrated only EU3. |

| 29    | E                     | <ul><li>Enable external breakpoint to cause HALT condition.</li><li>0 Do not enable external breakpoint to cause a halt condition</li><li>1 Allow external breakpoint to cause a halt condition</li></ul>                                                                                                                                                                               |

| 30    | I                     | Enable internal breakpoint<br>0 Do not enable internal breakpoint to cause a halt condition<br>1 Allow external breakpoint to cause a halt condition                                                                                                                                                                                                                                    |

| 31    | EB                    | Master breakpoint enable (this bit must be always set to allow any kind of breakpoint to halt<br>the task)<br>0 Disable external breakpoint<br>1 Enable external breakpoint                                                                                                                                                                                                             |

| Table 6. SDMA | Debug | Module | Control | Field | Descriptions |

|---------------|-------|--------|---------|-------|--------------|

|---------------|-------|--------|---------|-------|--------------|

### 3.4.4 External BestComm Request (GPIO)

The ability to use simple and interrupt GPIO as BestComm requestors has been added.

The SDMA requestor muxcontrol register encoding values have been expanded to use the values %01 and %10. These new values allow various simple and interrupt GPIO pins to be selected as BestComm requestors.

This may affect user software. User code should be checked to make sure that reserved values were not used in software written for MPC5200 devices prior to MPC5200B to insure software compatibility.

### 3.4.5 SDMA Requestor MuxControl—MBAR + 0x125C

|        | msb 0 | 1           | 2  | 3   | 4  | 5   | 6  | 7   | 8  | 9   | 10  | 11  | 12 | 13  | 14 | 15     |

|--------|-------|-------------|----|-----|----|-----|----|-----|----|-----|-----|-----|----|-----|----|--------|

| R      | Rec   | <b> </b> 31 | Re | q30 | Re | q29 | Re | q28 | Re | q27 | Red | q26 | Re | q25 | Re | eq24   |

| W      |       |             |    |     |    |     |    |     |    |     |     |     |    |     |    |        |

| RESET: | 0     | 0           | 0  | 0   | 0  | 0   | 0  | 0   | 0  | 0   | 0   | 0   | 0  | 0   | 0  | 0      |

|        |       |             |    |     |    |     |    |     |    |     |     |     |    |     |    |        |

|        | 16    | 17          | 18 | 19  | 20 | 21  | 22 | 23  | 24 | 25  | 26  | 27  | 28 | 29  | 30 | 31 lsb |

| R      | Rec   | 23          | Re | q22 | Re | q21 | Re | q20 | Re | q19 | Red | q18 | Re | q17 | Re | eq16   |

| W      |       |             |    |     |    |     |    |     |    |     |     |     |    |     |    |        |

| RESET: | 0     | 0           | 0  | 0   | 0  | 0   | 0  | 0   | 0  | 0   | 0   | 0   | 0  | 0   | 0  | 0      |

#### Figure 15. SDMA Request MuxControl

| Table 7. SDMA Request MuxControl Field Descriptions | Table 7. SDMA | Request | <b>MuxControl</b> | Field | Descriptions |

|-----------------------------------------------------|---------------|---------|-------------------|-------|--------------|

|-----------------------------------------------------|---------------|---------|-------------------|-------|--------------|

| Bit   | Name  | Description for the MPC5200B<br>(Mask Set M62C Rev. 1)                                    | Description for Prior Versions of<br>the MPC5200                                                                |

|-------|-------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| 0:1   | Req31 | 00 Requestor (RESERVED)<br>01 GPIO_PSC2_3<br>10 GPIO_IRDA_1<br>11 Always Requestor 31     | <ul><li>00 Requestor (RESERVED)</li><li>01-10 No active requestor</li><li>11 Always Requestor 31</li></ul>      |

| 2:3   | Req30 | 00 Requestor (RESERVED)<br>01 GPIO_PSC2_2<br>10 GPIO_IRDA_0<br>11 Always Requestor 30     | <ul><li>00 Requestor (RESERVED)</li><li>01-10 No active requestor</li><li>11 Always Requestor 30</li></ul>      |

| 4:5   | Req29 | 00 Requestor (RESERVED)<br>01 GPIO_PSC2_1<br>10 GPIO_ETH_3<br>11 Always Requestor 29      | <ul><li>00 Requestor (RESERVED)</li><li>01-10 No active requestor</li><li>11 Always Requestor 29</li></ul>      |

| 6:7   | Req28 | 00 Requestor (RESERVED)<br>01 GPIO_PSC2_0<br>10 GPIO_ETH_2<br>11 Always Requestor 28      | <ul><li>00 Requestor (RESERVED)</li><li>01-10No active requestor</li><li>11 Always Requestor 28</li></ul>       |

| 8:9   | Req27 | 00 Requestor (RESERVED)<br>01 GPIO_PSC1_3<br>10 GPIO_ETH_1<br>11 Always Requestor 27      | <ul><li>00 Requestor (RESERVED)</li><li>01-10 No active requestor</li><li>11 Always Requestor 27</li></ul>      |

| 10:11 | Req26 | 00 Requestor IrDA TX (PSC_6)<br>01 GPIO_PSC1_2<br>10 GPIO_ETH_0<br>11 Always Requestor 26 | 00 Requestor IrDA TX (PSC_6)<br>01-10 No active requestor<br>11 Always Requestor 26                             |

| 12:13 | Req25 | 00 Requestor IrDA RX (PSC_6)<br>01 GPIO_PSC1_1<br>10 GPIO_USB_3<br>11 Always Requestor 25 | <ul><li>00 Requestor IrDA RX (PSC_6)</li><li>01-10 No active requestor</li><li>11 Always Requestor 25</li></ul> |

| 14:15 | Req24 | 00 Requestor I2C1_TX<br>01 GPIO_PSC1_0<br>10 GPIO_USB_2<br>11 Always Requestor 24         | <ul><li>00 Requestor I2C1_TX</li><li>01-10 No active requestor</li><li>11 Always Requestor 24</li></ul>         |

|       |       | -                                                                                                                       |                                                                             |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Bit   | Name  | Description for the MPC5200B<br>(Mask Set M62C Rev. 1)                                                                  | Description for Prior Versions of<br>the MPC5200                            |

| 16:17 | Req23 | <ul> <li>00 Requestor I2C1_RX</li> <li>01 GPIO_SINT_7</li> <li>10 GPIO_USB_1</li> <li>11 Always Requestor 23</li> </ul> | 00 Requestor I2C1_RX<br>01-10 No active requestor<br>11 Always Requestor 23 |

| 18:19 | Req22 | 00 Requestor I2C2_TX<br>01 GPIO_SINT_6<br>10 GPIO_USB_0<br>11 Always Requestor 22                                       | 00 Requestor I2C2_TX<br>01-10 No active requestor<br>11 Always Requestor 22 |

| 20:21 | Req21 | 00 Requestor I2C2_RX<br>01 GPIO_SINT_5<br>10 GPIO_PSC3_5<br>11 Always Requestor 21                                      | 00 Requestor I2C2_RX<br>01-10 No active requestor<br>11 Always Requestor 21 |

| 22:23 | Req20 | 00 Requestor PSC4_TX<br>01 GPIO_SINT_4<br>10 GPIO_PSC3_4<br>11 Always Requestor 20                                      | 00 Requestor PSC4_TX<br>01-10 No active requestor<br>11 Always Requestor 20 |

| 24:25 | Req19 | 00 Requestor PSC4_RX<br>01 GPIO_SINT_3<br>10 GPIO_PSC3_3<br>11 Always Requestor 19                                      | 00 Requestor PSC4_RX<br>01-10 No active requestor<br>11 Always Requestor 19 |

| 26:27 | Req18 | 00 Requestor PSC5_TX<br>01 GPIO_SINT_2<br>10 GPIO_PSC3_2<br>11 Always Requestor 18                                      | 00 Requestor PSC5_TX<br>01-10 No active requestor<br>11 Always Requestor 18 |

| 28:29 | Req17 | 00 Requestor PSC5_RX<br>01 GPIO_SINT_1<br>10 GPIO_PSC3_1<br>11 Always Requestor 17                                      | 00 Requestor PSC5_RX<br>01-10 No active requestor<br>11 Always Requestor 17 |

| 30:31 | Req16 | 00 Requestor LP<br>01 GPIO_SINT_0<br>10 GPIO_PSC3_0<br>11 Always Requestor 16                                           | 00 Requestor LP<br>01-10 No active requestor<br>11 Always Requestor 16      |

### 3.5 PCI

### 3.5.1 SC PCI—Packet Size Increase

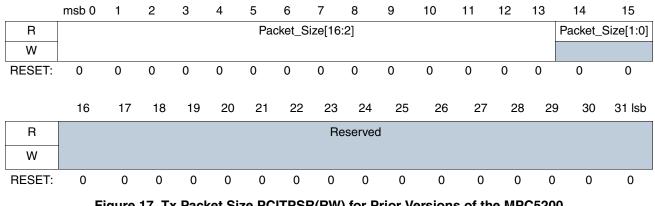

- Tx packet size PCITPSR(RW)—0x3800—The Packet\_Size field has been increased in width from 16 to 32 bits.

- Tx done counts PCITDCR(R)—0x3818—The Bytes\_Done field has been increased from 16 to 32 bits. The Packets\_Done field has been moved to the Tx packets done counts PCITPDCR(R) at MBAR + 0x3820, and this field has been increased from 16 to 32 bits.

- Add Tx packets done counts register—PCITPDCR(R) at MBAR + 0x3820—for changed Packets\_Done and increased field size from 16 to 32 bits.

## NP

3.5.2.1

#### Changes to the Programmer's Interface

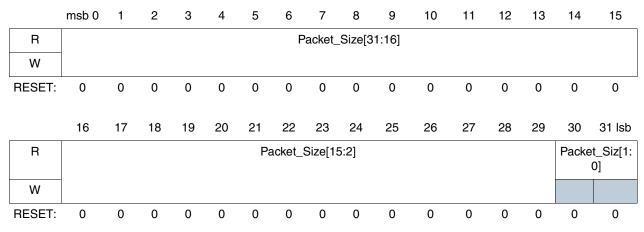

- Rx packet size PCIRPSR(RW)—0x3880—The Packet\_Size field has been increased in width from 16 to 32 bits.

- RxDone counts PCIRDCR(R)—0x3898—The Bytes\_Done field has been increased from 16 to 32 bits. The Packets\_Done field has been moved to the Rx packets done counts PCIRPDCR(R) at MBAR + 0x38A0, and this field has been increased from 16 to 32 bits.

- Add Rx packets done counts register—PCIRPDCR(R) at MBAR + 0x38A0—for changed Packets\_Done and increased field size from 16 to 32 bits.

### 3.5.2 Tx Packet Size PCITPSR(RW)—MBAR + 0x3800

Tx Packet Size PCITPSR(RW) for MPC5200B

#### msb 0 R Packet\_Size[31:16] W RESET: 31 lsb Packet\_Size[15:2] PacketSize[1:0] R W RESET:

Figure 16. Tx Packet Size PCITPSR(RW) for MPC5200B

| Bits | Name        | Description                                                                                                                                                                                                                                                                                                                      |

|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Packet_Size | User writes the number of bytes for transmit controller to send over PCI. The two low bits are hardwired low; only 32-bit data transfers to the FIFO are allowed. Writing to this register also completes a Restart Sequence as long as the Master Enable bit, PCITER[ME], is high and Reset Controller bit, PCITER[RC], is low. |

### 3.5.2.2 Tx Packet Size PCITPSR(RW) for Prior Versions of the MPC5200

Figure 17. Tx Packet Size PCITPSR(RW) for Prior Versions of the MPC5200

| Bits  | Name        | Description                                                                                                                                                                                                                                                                                                                      |

|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Packet_Size | User writes the number of bytes for transmit controller to send over PCI. The two low bits are hardwired low; only 32-bit data transfers to the FIFO are allowed. Writing to this register also completes a restart sequence as long as the master enable bit, PCITER[ME], is high and reset controller bit, PCITER[RC], is low. |

| 16:31 | Reserved    | Unused. Software should write zero to these bits.                                                                                                                                                                                                                                                                                |

#### Table 9. Tx Packet Size PCITPSR(RW) Field Descriptions

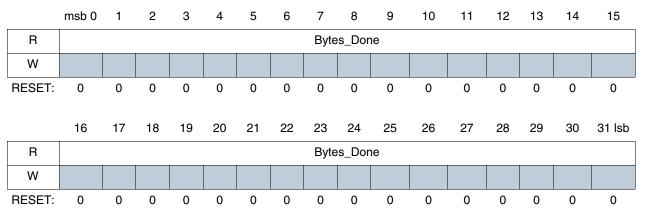

### 3.5.3 Tx Bytes Done Counts PCITDCR(R)—MBAR + 0x3818

### 3.5.3.1 Tx Bytes Done Counts PCITDCR(R) for MPC5200B

#### Figure 18. Tx Bytes Done Counts PCITDCR(R) for MPC5200B

#### Table 10. Tx Bytes Done Counts PCITDCR(R) Field Descriptions

| Bits | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Bytes_Done | This status register indicates the number of bytes transmitted since the start of a packet. It is updated at the end of each successful PCI data beat. For normally terminated packets, the Bytes_Done value and the Packet_Size values will be equal. If continuous mode is active the Bytes_Done value will read zero at the end of a successful packet, and the Packets_Done field will be incremented. |

### 3.5.3.2 Tx Done Counts PCITDCR(R) for Prior Versions of the MPC5200B

Figure 19. Tx Done Counts PCITDCR(R) for Prior Versions of the MPC5200B

| Bits  | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Bytes_Done   | This status register indicates the number of bytes transmitted since the start of a packet. It is updated at the end of each successful PCI data beat. For normally terminated packets, the Bytes_Done value and the Packet_Size values will be equal. If continuous mode is active, the Bytes_Done value will read zero at the end of a successful packet, and the Packets_Done field will be incremented.                                                                                                                                                                                                                                          |

| 16:31 | Packets_Done | <ul> <li>This status register indicates the number of packets transmitted and is active only if continuous mode is in effect. The counter is reset if the following occurs</li> <li>Reset controller bit, PCITER[RC], is asserted (normal way to restart continuous mode)</li> <li>Master enable bit, PCITER[ME], becomes negated</li> <li>Master enable can reset Packets_Done status without disturbing continuous mode addressing. At any point in time, the total number of bytes transmitted can be calculated as (Packets_Done x Packet_Size) + Bytes_Done</li> <li>This assumes Packet_Size is the same for all restart sequences.</li> </ul> |

#### Table 11. Tx Done Counts PCITDCR(R) Field Descriptions

### 3.5.4 Rx Packet Size PCIRPSR(RW)—MBAR + 0x3880

### 3.5.4.1 Rx Packet Size PCIRPSR(RW) for MPC5200B

Figure 20. Rx Packet Size PCIRPSR(RW) for MPC5200B

| Bits | Name        | Description                                                                                                                                                                                                                                                                                                                                         |

|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Packet_Size | The user writes this register with the number of bytes for receive controller to fetch over PCI. The two low bits are hardwired low; only 32-bit data transfers to the FIFO are allowed. Writing to this register also completes a restart sequence as long as master enable bit, PCIRER[ME], is high and reset controller bit, PCIRER[RC], is low. |

### 3.5.4.2 Rx Packet Size PCIRPSR(RW) for Prior Versions of the MPC5200

Figure 21. Rx Packet Size PCIRPSR(RW) for Prior Versions of the MPC5200

| Bits  | Name        | Description                                                                                                                                                                                                                                                                                                                                         |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Packet_Size | The user writes this register with the number of bytes for receive controller to fetch over PCI. The two low bits are hardwired low; only 32-bit data transfers to the FIFO are allowed. Writing to this register also completes a restart sequence as long as master enable bit, PCIRER[ME], is high and reset controller bit, PCIRER[RC], is low. |

| 16:31 | Reserved    | Unused bits. Software should write zero to these bits. No bus error is generated                                                                                                                                                                                                                                                                    |

#### Table 13. Rx Packet Size PCIRPSR(RW) Field Descriptions

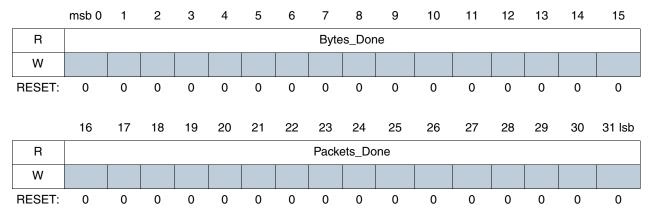

### 3.5.5 Rx Bytes Done Counts PCIRDCR(R) — MBAR + 0x3898

### 3.5.5.1 Rx Bytes Done Counts PCIRDCR(R) for MPC5200B

|        | msb 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7    | 8      | 9  | 10 | 11 | 12 | 13 | 14 | 15     |

|--------|-------|----|----|----|----|----|----|------|--------|----|----|----|----|----|----|--------|

| R      |       |    |    |    |    |    |    | Byte | es_Dor | e  |    |    |    |    |    |        |

| W      |       |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

| RESET: | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

|        |       |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

|        | 16    | 17 | 18 | 19 | 20 | 21 | 22 | 23   | 24     | 25 | 26 | 27 | 28 | 29 | 30 | 31 lsb |

| R      |       |    |    |    |    |    |    | Byte | es_Dor | ie |    |    |    |    |    |        |

| W      | 1     |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

| RESET: | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

#### Figure 22. Rx Bytes Done Counts PCIRDCR(R) for MPC5200B

#### Table 14. Rx Bytes Done Counts PCIRDCR(R) Field Descriptions

| Bits | Name       | Description                                                                                                                                                                                                                                                                                                                                                                              |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Bytes_Done | This status register indicates the number of bytes received since the start of a packet. It is updated at the end of each successful PCI data beat. For normally terminated packets, the Bytes_Done value and the Packet_Size values are equal. If continuous mode is active, the Bytes_Done value reads 0 at the end of a successful packet, and the Packets_Done field is incremented. |

### 3.5.5.2 RxDone Counts PCIRDCR(R) for Prior Versions of the MPC5200

|        | msb 0 | 1  | 2  | 3  | 4  | 5  | 6  | 7    | 8      | 9  | 10 | 11 | 12 | 13 | 14 | 15     |

|--------|-------|----|----|----|----|----|----|------|--------|----|----|----|----|----|----|--------|

| R      |       |    |    |    |    |    |    | Byte | s_Dor  | ne |    |    |    |    |    |        |

| W      |       |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

| RESET: | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

|        |       |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

|        | 16    | 17 | 18 | 19 | 20 | 21 | 22 | 23   | 24     | 25 | 26 | 27 | 28 | 29 | 30 | 31 lsb |

| R      |       |    |    |    |    |    |    | Pack | ets_Do | ne |    |    |    |    |    |        |

| W      |       |    |    |    |    |    |    |      |        |    |    |    |    |    |    |        |

| RESET: | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0      |

Figure 23. RxDone Counts PCIRDCR(R) for Prior Versions of the MPC5200

| Bits  | Name         | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:15  | Bytes_Done   | This status register indicates the number of bytes received since the start of a packet. It is updated at the end of each successful PCI data beat. For normally terminated packets, the Bytes_Done value and the Packet_Size values are equal. If continuous mode is active, the Bytes_Done value reads 0 at the end of a successful packet, and the Packets_Done field is incremented. |

| 16:31 | Packets_Done | <ul> <li>This status register indicates the number of packets received. It is active only if continuous mode is in effect. If the following occurs, the counter is reset:</li> <li>Reset controller bit, PCIRER[RC], is asserted (normal way to restart continuous mode)</li> <li>Master enable bit, PCIRER[ME], is negated</li> </ul>                                                   |

|       |              | In this way, master enable can be used to reset Packets_Done status without disturbing continuous mode addressing. At any point in time the total number of Bytes received can be calculated as (Packets_Done x Packet_Size) + Bytes_Done This assumes Packet_Size is the same for all restart sequences.                                                                                |

#### Table 15. xDone Counts PCIRDCR(R) Field Descriptions

### 3.5.6 Tx Packets Done Counts PCITPDCR(R) — MBAR + 0x3820

### 3.5.6.1 Tx Packets Done Counts PCITPDCR(R) for MPC5200B

Figure 24. x Packets Done Counts PCITPDCR(R) for MPC5200B

#### Table 16. Tx Packets Done Counts PCITPDCR(R) Field Descriptions

| Bits | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Packets_Done | <ul> <li>This status register indicates the number of packets transmitted and is active only if continuous mode is in effect. The counter is reset if the following occurs</li> <li>Reset controller bit, PCITER[RC], is asserted (normal way to restart continuous mode)</li> <li>Master enable bit, PCITER[ME], becomes negated</li> <li>Master enable can reset Packets_Done status without disturbing continuous mode addressing. At any point in time, the total number of bytes transmitted can be calculated as (Packets_Done x Packet_Size) + Bytes_Done</li> <li>This assumes Packet_Size is the same for all restart sequences.</li> </ul> |

The Tx packets done counts register has been added to the MPC5200B. There is no corresponding register in prior versions of the MPC5200.

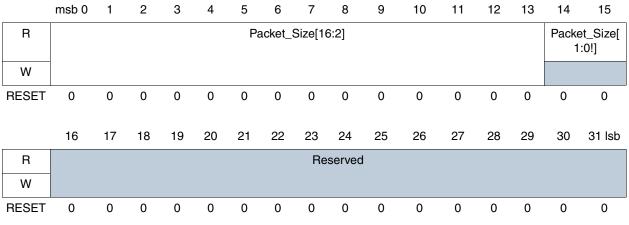

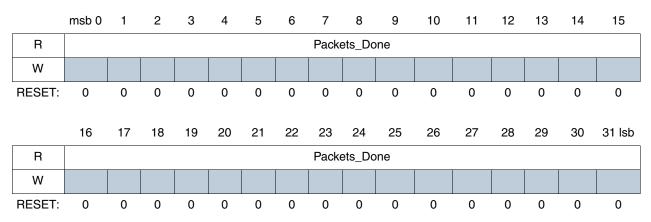

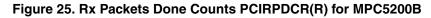

### 3.5.7 Rx Packets Done Counts PCIRPDCR(R) — MBAR + 0x38A0

#### msb 0 R Packets Done W RESET: 31 lsb R Packets\_Done W RESET:

#### 3.5.7.1 Rx Packets Done Counts PCIRPDCR(R) for MPC5200B

| Bits | Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:31 | Packets_Done | <ul> <li>This status register indicates the number of packets received. It is active only if continuous mode is in effect. If the following occurs, the counter is reset:</li> <li>Reset controller bit, PCIRER[RC], is asserted (normal way to restart continuous mode)</li> <li>Master enable bit, PCIRER[ME], is negated</li> <li>In this way, master enable can be used to reset Packets_Done status without disturbing continuous mode addressing. At any point in time the total number of Bytes received can be calculated as <ul> <li>(Packets_Done x Packet_Size) + Bytes_Done</li> <li>This assumes Packet_Size is the same for all restart sequences.</li> </ul> </li> </ul> |

The Rx packets done counts register has been added to the MPC5200B. There is no corresponding register in prior versions of the MPC5200.

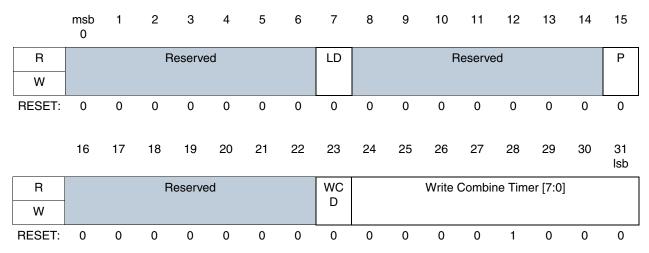

### 3.5.8 XTPCI Write Combining Programmability

The target control register PCITCR(RW)—0xD6C—has additional bits for the write combine feature:

- Bit 23—WCD—write combine disable

- Bits[24:31]—WCT[7:0] write combine timer

The purpose of this feature, added to the MPC5200B, allows partial packets of incoming data to be transferred to the XL bus if a break in incoming PCI data occurs greater than specified by the write combine timer.

This feature is a hardware function that was added to improve system bus performance and does not affect user software. This feature can be disabled by the WCD bit in the PCITCR register.

NOTE

The MPC5200B allows an external burst write to the internal XL Bus. Prior versions of the MPC5200 do not allow an external PCI initiator to do a write burst on the XL Bus.

### 3.5.9 Target Control Register PCITCR(RW) — MBAR + 0x0D6C

### 3.5.9.1 Target Control Register PCITCR(RW) for MPC5200B

Figure 26. Target Control Register PCITCR(RW) for MPC5200B

#### Bits Name Description 16:22 Reserved Unused bits. Software should write zero to this register. 23 Write Combine This control bit applies only when MPC5200 is Target. When set, it prevents the PCI Disable Controller from automatically combining write data to be sent out on the XL bus as a burst, (WCD) if possible. Instead, data is transferred as soon as possible on the XL bus as single-beat transactions. Better target write performance is achieved when this bit cleared. 24:31 Write Combine This register contains the timer value, in PCI clocks, used when a partial burst has been Timer (WCT) buffered in the target write data path and write data stops being transferred to local memory from the external PCI device. Every time a sequential beat of write data is stored in the buffer, the counter is reset with this value. If partial burst data has been buffered, thereby activating the count-down counter, and this field is reprogrammed to a value less than the current counter value, the counter will jump down to the new write combine timer value. This way, software can force the write buffer to flush data to the XL bus more quickly than when the counter was initialized. The reset value of the write combine timer is 0x08. All 8 bits are programmable.

#### Table 18. Target Control Field Descriptions

## 3.5.9.2 Target Control Register PCITCR(RW) for Prior Versions of the MPC5200

Figure 27. Target Control Register PCITCR(RW) for Prior Versions of the MPC5200

Table 19. Target Control Field Descriptions

| Bits  | Name     | Description                                               |

|-------|----------|-----------------------------------------------------------|

| 16:31 | Reserved | Unused bits. Software should write zero to this register. |

### 3.5.10 PCITTCR and PCIRTCR

- Tx transaction control register PCITTCR

- Rx transaction control register PCIRTCR

On prior revisions of the MPC5200, setting the Max\_Retries field of either the PCITTCR or PCIRTCR registers to 0xFF or 0x00 would allow INFINITE retries. The MPC5200B only uses the value 0x00 to allow INFINITE retries. Now, the value of 0xFF will specify 255 retires.

# 3.5.11 Tx Transaction Control Register PCITTCR(RW) — MBAR + 0x3808

### 3.5.11.1 Tx Transaction Control Register PCITTCR(RW) for MPC5200B

|        | msb 0 | 1     | 2     | 3  | 4  | 5    | 6     | 7   | 8  | 9       | 10 | 11    | 12      | 13      | 14 | 15     |

|--------|-------|-------|-------|----|----|------|-------|-----|----|---------|----|-------|---------|---------|----|--------|

| R      |       | Reser | rved  |    |    | PCI_ | cmnd  |     |    |         |    | Max_F | Retries |         |    |        |

| W      |       |       |       |    |    |      |       |     |    |         |    |       |         |         |    |        |

| RESET: | 0     | 0     | 0     | 0  |    | 01   | 11    |     | 0  | 0       | 0  | 0     | 0       | 0       | 0  | 0      |

|        |       |       |       |    |    |      |       |     |    |         |    |       |         |         |    |        |

|        | 16    | 17    | 18    | 19 | 20 | 21   | 22    | 23  | 24 | 25      | 26 | 27    | 28      | 29      | 30 | 31 lsb |

| R      |       | Re    | serve | b  |    | Ма   | ax_Be | ats | F  | Reserve | ed | W     | F       | leserve | ∋d | DI     |

| W      |       |       |       |    |    |      |       |     |    |         |    |       |         |         |    |        |

| RESET: | 0     | 0     | 0     | 0  | 0  | 0    | 0     | 0   | 0  | 0       | 0  | 0     | 0       | 0       | 0  | 0      |

Figure 28. Tx Transaction Control Register PCITTCR(RW) for MPC5200

| Bits | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8:15 | Max_Retries | The user writes this field with the maximum number of retries to permit perpacket. The retry counter is reset when the packet completes normally or is terminated by a master abort, target abort, or an abort due to exceeding the retry limit. A slow or malfunctioning target might issue infinite disconnects and therefore permanently tie up the PCI bus. A finite (0x01 to 0xff) Max_Retries value will detect this condition and generate an interrupt. Setting Max_Retries to 0x00 will not generate any interrupt. |

#### Table 20. Tx Transaction Control Field Descriptions

## 3.5.11.2 Tx Transaction Control Register PCITTCR(RW) for Prior Versions of the MPC5200

|        | msb 0 | 1     | 2      | 3  | 4  | 5    | 6     | 7   | 8  | 9       | 10 | 11    | 12      | 13      | 14 | 15     |

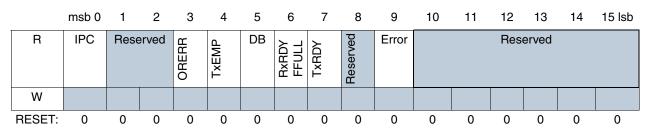

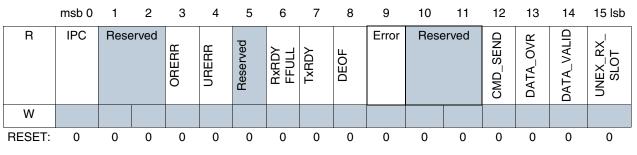

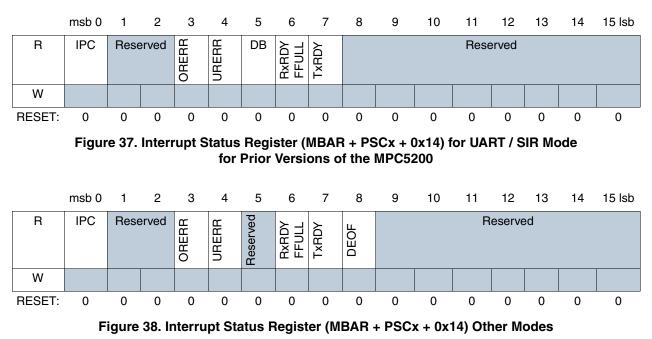

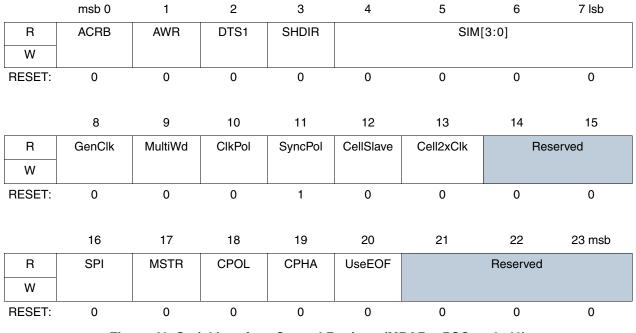

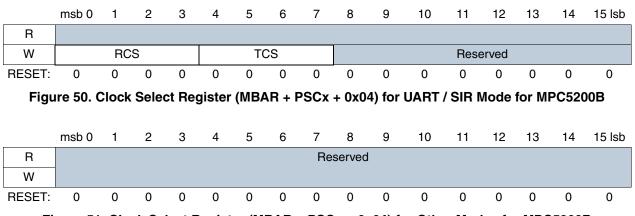

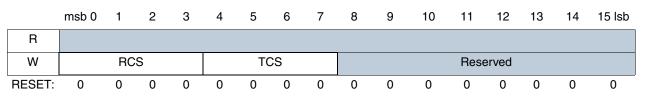

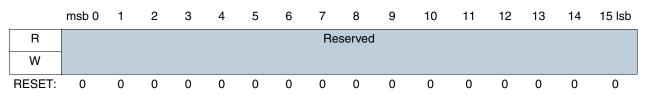

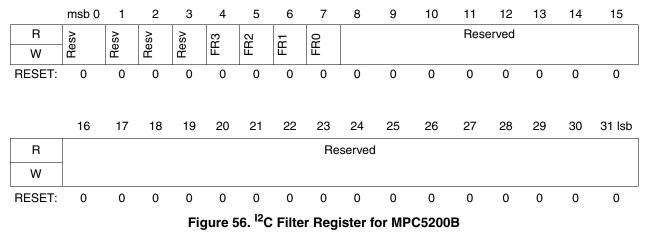

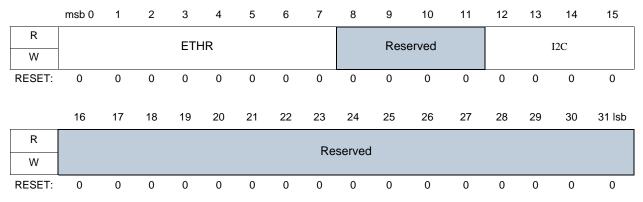

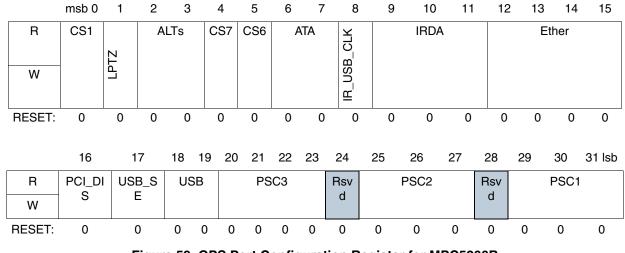

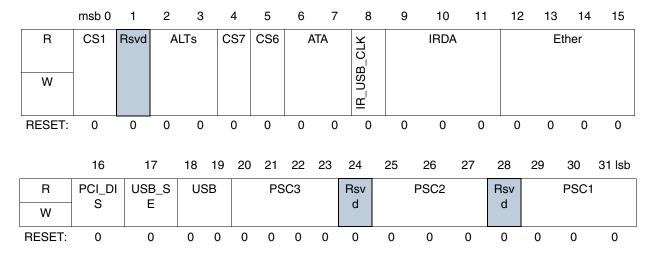

|--------|-------|-------|--------|----|----|------|-------|-----|----|---------|----|-------|---------|---------|----|--------|