### **Freescale Semiconductor Application Note**

Document Number: AN3098 Rev. 0. 11/2006

# **MSC8144 PCI Example Software**

bv Barbara Johnson NCSD DSP Applications Freescale Semiconductor, Inc. Austin, TX

In a PCI system, auto-configuration software offers ease of use for the system user by automatically configuring PCI add-in cards at power-on. This application note provides example software for use by a PCI host to configure the MSC8144 DSP as a PCI agent. This device configuration is required before any PCI transactions can occur between the host and the MSC8144.

#### **PCI Basics** 1

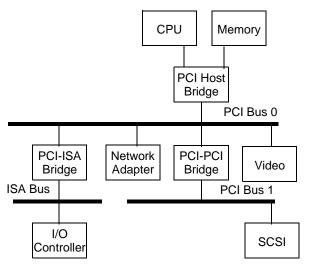

Peripheral component interconnect (PCI) is a standard that provides an interconnect mechanism between peripheral components, add-on devices, and memory subsystems. Developed by Intel, PCI is widely used in modern PCs to provide a way of adding peripherals such as video cards, sound cards, and network adapters on the same bus that is used to communicate with the CPU. Figure 1 shows an example PCI-based system. The CPU connects to the primary PCI bus on a PCI host bridge that translates between CPU bus cycles and PCI bus cycles. The PCI-PCI bridge connects the primary PCI bus to the secondary PCI bus. Electrical loading issues limit the number of devices that a single PCI bus can support, so PCI-PCI bridges are often used to allow the system to support more PCI devices. To support older, legacy devices, some PCs use a PCI-ISA bridge for connecting to the PCI bus.

Contents

| 1  | PCI Basics1                                    |

|----|------------------------------------------------|

| 2  | MSC8144 PCI Controller                         |

| 3  | Hardware Requirements and Setup3               |

|    | 3.1 Requirements                               |

|    | 3.2 Switch Settings                            |

|    | 3.3 Board Control and Status Register Setting4 |

| 4  | PCI Device Detection Example                   |

| 5  | Memory Allocation Example7                     |

| 6  | MSC8144 Inbound Configuration Example9         |

| 7  | MSC8144 CCSR Mapping Example11                 |

| 8  | MSC8144 Outbound Configuration Example 13      |

| 9  | Cache Line Size15                              |

| 10 | Latency Timer 15                               |

| 11 | Interrupt Handling16                           |

| 12 | MPC8560 Host Configuration Code                |

| 13 | MPC8560 Header File                            |

© Freescale Semiconductor, Inc., 2006. All rights reserved.

Figure 1. Example PCI System

In Figure 1, the CPU operates as the PCI host. In the host mode, the CPU configures the PCI devices attached to the bus. Because PCI uses a shared bus topology, there must be an arbitration scheme to grant bus mastership to the requesting PCI device. Arbitration is handled by the host or an external arbitration.

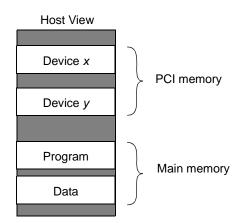

From the host perspective, the PCI devices are accessible through a read-write mechanism. An address space dedicated for PCI use contains a memory range for each PCI device on the bus. The host accesses the PCI devices by performing reads or writes to specific addresses in the PCI memory space, as shown in Figure 2.

Figure 2. Example Host View

Devices on the PCI bus must be configured before they can be used. For example, when a PC first boots up, each PCI device is assigned a region of PCI address space so that it becomes accessible to the CPU. After the devices are initialized, they respond to transactions that fall within their allocated memory ranges.

# 2 MSC8144 PCI Controller

The MSC8144 PCI controller complies with the *PCI Local Bus Specification*, Revision 2.2. It operates in agent mode and can act as initiator (master) or target (slave) device. It uses a 32-bit multiplexed address/data bus that operates at frequencies up to 66 MHz. Features of the PCI controller are as follows:

- 32-bit PCI interface

- Up to 66 MHz operation

- Agent mode

- Accesses to all PCI address spaces

- 64-bit dual-address cycles (as a target only)

- Internal configuration registers accessible from PCI and internal buses

- Contains L2 ICache-line (32 byte) buffers to allow PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Posting of processor-to-PCI and PCI-to-memory writes

- Inbound and outbound address translation units for address mapping between PCI and local busses

- Supports parity

- PCI 3.3-V compatible

# 3 Hardware Requirements and Setup

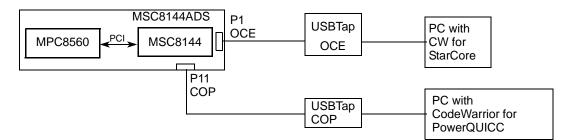

All tests described in this document were performed on the MSC8144 application development system (MSC8144ADS), which consists of an MPC8560 host processor that connects to the MSC8144 on the PCI bus.

### 3.1 Requirements

The following items are required to run the examples presented in this document:

- MSC8144ADS board

- PC with CodeWarrior<sup>TM</sup> for StarCore version 3.2 or later

- PC with CodeWarrior for PowerPC<sup>TM</sup> version 8.7 or later

- USBTap for MSC8144 OCE connection

- USBTap for MPC8560 COP connection

Two sets of debugger tools are required to connect to the MSC8144 and the MPC8560. A USBTap for OCE connects the MSC8144 to the CodeWarrior for StarCore tools through JTAG. Similarly, a USBTap for COP connects the MPC8560 to the CodeWarrior for PowerQUICC tools through JTAG. Figure 3 shows the hardware setup.

PCI Device Detection Example

Figure 3. Hardware Setup

### 3.2 Switch Settings

Table 1 shows the switch settings required to connect the MSC8144 and the MPC8560 to the debugger tools. Refer to the MSC8144 ADS User's Manual for details about the switch settings.

| Switch                | Settings 1:8 | Description                                                                 |  |  |  |

|-----------------------|--------------|-----------------------------------------------------------------------------|--|--|--|

| SW1                   | 00000110     | Default setting.                                                            |  |  |  |

| SW2                   | 01101111     | Host MPC8560 operates normally; disable JTAG chain for MSC8144 and MPC8560. |  |  |  |

| SW3                   | 10010111     | Default setting.                                                            |  |  |  |

| SW4                   | 01100010     | Default setting.                                                            |  |  |  |

| Note: 0 = ON, 1 = OFF |              |                                                                             |  |  |  |

### Table 1. MSC8144ADS Switch Settings

### 3.3 Board Control and Status Register Setting

The board control and status registers (BCSR*x*) are a group of 8-bit read/write registers that control or monitor most ADS hardware options. These registers can be accessed from the host local bus. To enable the PCI interface on the MSC8144ADS, bits 2 and 3 of BCSR1 must by set as shown in Example 1. For details on the BCSR*x* bit definitions, refer to the *MSC8144ADS User's Manual*.

Example 1. Enable PCI in BCSR1

# 4 PCI Device Detection Example

Before the PCI host can configure each device on the bus, it must first scan the bus to determine what PCI devices or PCI-PCI bridges are on the bus. By scanning the bus, the host can determine each device part number, manufacturer, and device number on the bus. The PCI specification requires each PCI device to provide 256 bytes of configuration registers. The configuration registers supply the information needed for device configuration, including the vendor ID, device ID, command and status, revision ID, class code and header type fields, as shown in Figure 4.

|                        |                                        |                       |                        | Address Offset |  |  |  |

|------------------------|----------------------------------------|-----------------------|------------------------|----------------|--|--|--|

| Device ID              |                                        | Vendor ID             |                        | 0x00           |  |  |  |

| PCI Status             |                                        | PCI Comm              | PCI Command Config     |                |  |  |  |

| Base Class<br>Code     | Subclass<br>Code                       | Std Prog<br>Interface | Revision ID            | 0x08           |  |  |  |

| BIST<br>Control        | Header<br>Type                         | Latency<br>Timer      | Cache Line<br>Size     | 0x0C           |  |  |  |

| PIMMR E                | Base Address                           | Register              |                        | 0x10           |  |  |  |

| GPL Bas                | e Address Re                           | egister 0             |                        | 0x14           |  |  |  |

| GPL Bas                | e Address Re                           | egister 1             |                        | 0x18           |  |  |  |

| GPL Exte               | ended Base A                           | ddress Regi           | ster 1                 | 0x1C           |  |  |  |

| GPL Bas                | 0x20                                   |                       |                        |                |  |  |  |

| GPL Exte               | 0x24                                   |                       |                        |                |  |  |  |

|                        | Reserved                               |                       |                        |                |  |  |  |

| Subsyster<br>Device ID | n                                      | Subsys<br>Vendor      | tem<br>ID              | 0x2C           |  |  |  |

|                        | Reser                                  | ved                   |                        | 0x30           |  |  |  |

|                        | 0x34                                   |                       |                        |                |  |  |  |

|                        | 0x38                                   |                       |                        |                |  |  |  |

| PCI Bus<br>MAX LAT     | PCI Bus<br>MIN GNT                     | PCI Bus<br>Interr Pin | PCI Bus<br>Interr Line | 0x3C           |  |  |  |

|                        | Reserved                               |                       |                        |                |  |  |  |

| Reserv                 | Reserved PCI Function<br>Configuration |                       |                        |                |  |  |  |

### Figure 4. MSC8144 PCI Configuration Space Registers

On the MSC8144ADS, the MPC8560 host can access the MSC8144 configuration space registers through two registers that are memory-mapped in the MPC8560 memory space:

- CONFIG\_ADDR Specifies the selected device configuration register to be accessed.

- CONFIG\_DATA. Data is transferred to or from the CONFIG\_DATA register.

For example, the host addresses a particular device on the bus by writing to the CONFIG\_ADDR with the bus number, device number, and the configuration register to access. Next, the host either writes the CONFIG\_DATA with the value to write to the selected configuration register or the host reads the CONFIG\_DATA to determine the value of the selected configuration register. Note that in the MPC8560, the CONFIG\_ADDR register uses big-endian but the CONFIG\_DATA register uses the little-endian convention.

#### **PCI Device Detection Example**

To scan the bus, the host will try to read the Vendor and Device ID Configuration Registers for all valid device number values. A target is selected during a configuration access when its IDSEL signal is selected. The IDSEL signal acts as the chip select signal. On the MSC8144ADS, the MPC8560's AD21 pin connects to the MSC8144's IDSEL pin. This connection means that the MSC8144 has a device number of 21 on bus 0. The MPC8560 has a device number of 0 on bus 0. Selecting a device number other than 0 and 21 will return an invalid value since only the MPC8560 and MSC8144 are present on the PCI bus on the MSC8144ADS. If the device does not exist, the Vendor ID returns a 0xFFFF which indicates an invalid vendor.

Table 2 shows the CONFIG\_ADDR and CONFIG\_DATA register values that the MPC8560 accesses to read its own and the MSC8144's vendor and device information.

| Access | Register    | Value      | Access<br>Type | Description                                                                                                                                                                      |

|--------|-------------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CONFIG_ADDR | 0x80000000 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 0<br>Access the PCI Vendor ID Configuration Register (offset 0x00)  |

|        | CONFIG_DATA | 0x1057     | Read           | Vendor ID = 0x1057 Freescale Semiconductor                                                                                                                                       |

| 2      | CONFIG_ADDR | 0x80000002 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 0<br>Access the PCI Device ID Configuration Register (offset 0x02)  |

|        | CONFIG_DATA | 0x0009     | Read           | Device ID = 0x0009 MPC8560                                                                                                                                                       |

| 3      | CONFIG_ADDR | 0x8000A800 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the PCI Vendor ID Configuration Register (offset 0x00) |

|        | CONFIG_DATA | 0x1957     | Read           | Vendor ID = 0x1957 Freescale Semiconductor                                                                                                                                       |

| 4      | CONFIG_ADDR | 0x8000A802 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the PCI Device ID Configuration Register (offset 0x02) |

|        | CONFIG_DATA | 0x1400     | Read           | Device ID = 0x1400 MSC8144                                                                                                                                                       |

### Table 2. Device Detection by MPC8560

Example 2 shows code that runs on the MPC8560 to scan the PCI bus for devices. This code has been simplified to scan only bus number 0.

**Example 2. Scan PCI Devices**

```

void scanDevices()

{

uint32_t i;

uint16_t VendorID, DeviceID;

uint32_t BusNum = 0;

for(i = 0; i < 0x20; i++)

{

VendorID = getPCIConfigReg16(BusNum, i, REG_VENDORID);

DeviceID = getPCIConfigReg16(BusNum, i, REG_DEVID);

if(VendorID != 0xFFFF)

{

printf(" Device found: Device %x, Bus %x, DevID = %x,

VendorID = %x\n", i, BusNum, DeviceID, VendorID);

}

}</pre>

```

# 5 Memory Allocation Example

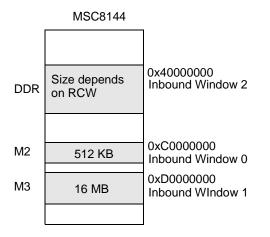

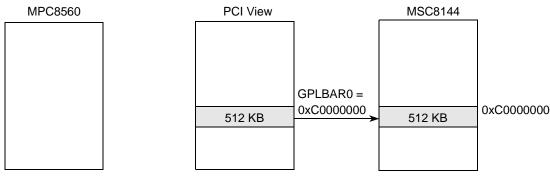

A transaction with the MSC8144 as the target is an inbound transaction. When the MSC8144 boots from PCI, the boot code sets up the three inbound windows for M2, M3, and DDR memory as shown in Figure 5. The MSC8144 PCI boot code configures the base addresses in local memory and the sizes of these inbound windows. The PCI inbound translation address register (PITAR*n*) defines the base address of the inbound translation windows in the MSC8144 memory space. The PCI inbound window attribute register (PIWAR*n*) defines the size of a window as well as other properties and enables that window. It is the host that allocates memory to each device on the PCI bus in a device-independent manner. The host allocates memory by creating a memory map in the PCI memory space. It writes to each device GPL base address register (GPLBAR*x*) in the PCI configuration space to create a mapping between the PCI view and the device local memory view.

Figure 5. MSC8144 Inbound Window Configuration at Boot

MSC8144 PCI Example Software, Rev. 0

#### Memory Allocation Example

To determine the size requirements of the MSC8144 inbound windows, the MPC8560 writes to the MSC8144 GPLBAR*x* in the PCI configuration space as shown in Figure 4. These base address registers specify the mapping of the device inbound windows in the PCI space. The host first reads these base address registers to get the initial setting. It then writes all 1's to these base address registers and reads them back to determine the memory size required by the inbound window. Then the host can allocate memory for each device in the PCI space.

Table 3 shows the steps by which the MPC8560 determines the MSC8144 inbound window 0 memory requirement. The MPC8560 addresses the MSC8144 GLBAR0 register by writing to the CONFIG\_ADDR register. Then it reads the CONFIG\_DATA to get the value of the GPLBAR0, which defines the inbound window 0 base address register in the PCI memory space. The host must save this value to restore later. Next, the host writes 0xFFFFFFFF to the MSC8144 GPLBAR0 and reads back the register. The number of bits set determines how much address space is required. For example, a GPLBAR0 value of 0xFFF80000 has the upper 13 bits of the address register set, indicating a size of  $2^{(32-13)} = 512$  Kbytes. Now, the host knows that it must allocate 512 Kbytes of memory in the PCI memory space before it can access the MSC8144 inbound window 0. The host must then assign an address in the PCI space because the GPLBAR0 now contains the sizing information. These steps should be repeated for GPLBAR1 and GPLBAR2 registers to determine the memory requirements for inbound windows 1 and 2.

| Access | Register    | Value      | Access<br>Type | Description                                                                                                                                                             |

|--------|-------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | CONFIG_ADDR | 0x8000A814 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the GPL Base Address Register 0 (offset 0x14) |

|        | CONFIG_DATA | 0x0000000  | Read           | GPLBAR0 = 0x00000000 inbound window 0 in PCI space                                                                                                                      |

| 2      | CONFIG_ADDR | 0x8000A814 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the GPL Base Address Register 0 (offset 0x14) |

|        | CONFIG_DATA | 0xFFFFFFFF | Write          | GPLBAR0 = 0xFFFFFFF                                                                                                                                                     |

| 3      | CONFIG_ADDR | 0x8000A814 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the GPL Base Address Register 0 (offset 0x14) |

|        | CONFIG_DATA | 0xFFF80000 | Read           | GPLBAR0 = 0xFFF80000 Upper 13 bits are set<br>Size = $2^{(32 - 13)}$ = 512 KB                                                                                           |

| 4      | CONFIG_ADDR | 0x8000A814 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the GPL Base Address Register 0 (offset 0x14) |

|        | CONFIG_DATA | 0xC0000000 | Write          | Reassign new GPLBAR0 = 0xC0000000                                                                                                                                       |

### Table 3. Memory Allocation by MPC8560

In this example, the host assigns a chunk of memory in the PCI memory space to map the MSC8144 inbound window in M2. The host configures the MSC8144 GPLBAR0 = 0xC0000000 to give a one-to-one mapping between the PCI view and the MSC8144 local view, as shown in Figure 6.

Figure 6. Example MSC8144 GPLBAR0 Configuration

Example 3 shows the function called by the MPC8560 to calculate the size of a device inbound window.

**Example 3. Determine Memory Requirement**

```

uint32 t getWindowSize(uint32 t BusNum, uint32 t DevNum, uint32 t Reg)

{

uint32_t new, orig;

uint32 t size;

// Read CfqReq

orig = getPCIConfigReg32(BusNum, DevNum, Reg);

// Write all 1's

setPCIConfigReg32(BusNum, DevNum, Reg, 0xFFFFFFFF);

// Read back to determine size

new = getPCIConfigReg32(BusNum, DevNum, Reg);

// Restore orig register value

setPCIConfigReg32(BusNum, DevNum, Reg, orig);

// Calculate size required by agent

if (new & 1)

size = (~new | 3) + 1;

// I/O space

else

size = (~new | 0xF) + 1; // Memory space

return size;

}

```

# 6 MSC8144 Inbound Configuration Example

An inbound transaction in which the MSC8144 is the target means that the host MPC8560 is the bus master or the initiator performing an outbound transaction. Outbound transactions require address translation to map transactions from the internal address space of the MPC8560 to the external PCI address space.

#### MSC8144 Inbound Configuration Example

MPC8560 registers to handle the address translation task are as follows:

- PCI outbound translation address register (POTAR*n*) selects the base address of the external PCI address space for hits in the outbound window.

- PCI outbound window base address register (POWBAR*n*) points to the base address of the outbound window in the MPC8560 local address space.

- PCI outbound window attributes register (POWAR*n*) enables the address translation window, specifies the transaction type, and defines the window size.

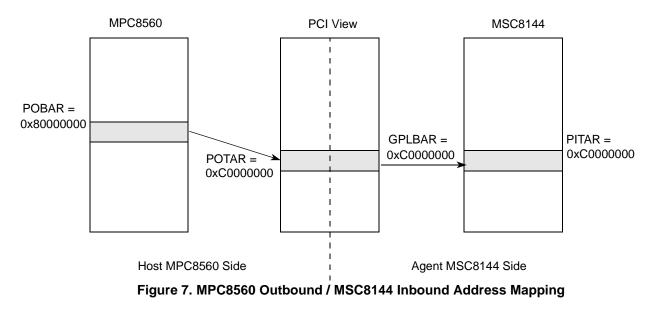

Table 4 shows the outbound window 1 of size 512 Kbytes starting at 0x80000000 in the MPC8560 local address space for translation to the external PCI address starting at 0xC0000000.

| Register | Value      | Description                                                                                                                          |  |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| POTAR1   | 0x000C0000 | Set base address 0xC0000000 as the translated address in the PCI address space                                                       |  |

| POWBAR1  | 0x00080000 | Set base address 0x80000000 as the outbound address from the MPC8560                                                                 |  |

| POWAR1   | 0x80044012 | Enable the outbound translation window 1<br>Enable memory read and write transactions<br>Set translation window 1 size as 512 Kbytes |  |

Table 4. MPC8560 PCI Outbound Register Settings

Figure 7 depicts the MPC8560 outbound address translation mapping. An access to the MPC8560 local address starting at 0x80000000 is routed to the PCI memory space starting at 0xC0000000. Notice that the PCI address is configured to be the same as the local address for a simple one-to-one mapping. The left side of the dotted line gives register settings on the MPC8560 side, and the right side of the dotted line gives register settings on the MPC8560 POTAR must have the same value as the MSC8144 GPLBAR.

MSC8144 PCI Example Software, Rev. 0

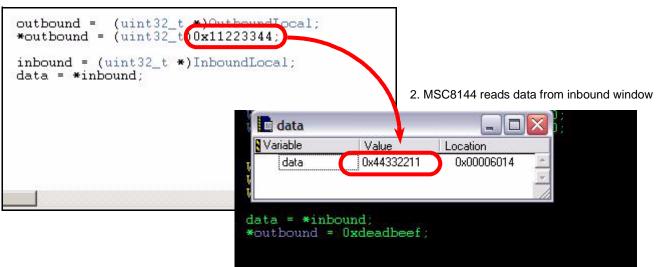

Before the MSC8144 DSP can respond to memory accesses, the MPC8560 processor must configure the MSC8144 PCI command configuration register, which has an offset of 0x04 in the PCI configuration space. The MEM bit must be set to allow the MSC8144 to respond to memory accesses. Figure 8 shows an example in which the MSC8144 performs an inbound transaction. The left screenshot shows the MPC8560 writing the value 0x11223344 to its local outbound window. This address is translated to the PCI address that is mapped to the MSC8144 local inbound window. The right screenshot shows the MSC8144 reading the same value from its local inbound window.

1. MPC8560 writes data to outbound window

Figure 8. MSC8144 Inbound Example

# 7 MSC8144 CCSR Mapping Example

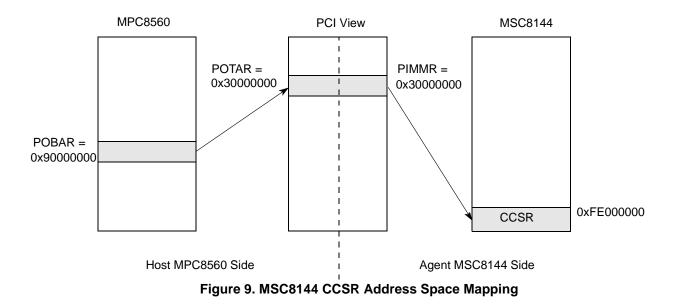

Before we look at an example MSC8144 outbound transaction, let us first consider how to configure the host MPC8560 to view the MSC8144 configuration control and status registers (CCSR) map. The CCSR address space includes control and status registers for DMA, CLASS, DDR, clock, I<sup>2</sup>C, timers, TDM, GPIO, PCI, RapidIO, and so on.

External masters do not need the location of a device's CCSR memory space. Instead, they access a device's CCSR through a window defined by the PIMMR base address configuration register in the configuration register space, as shown in Figure 4. The PIMMR defines the address for accessing the local CCSR memory space of a device. It specifies an address in the PCI space where the CCSR space is mapped.

The CCSR memory space is 32 Mbytes. Subtracting 32 Mbytes from the top of the MSC8144 address space gives the CCSR base address of 0xFE000000. In this example, the host configures PIMMR to 0x30000000 through the CONFIG\_ADDR and CONFIG\_DATA configuration access registers. The host also configures another outbound window at 0x90000000 so that transactions from this space are mapped to the PCI space at 0x30000000. Figure 9 shows a diagram of the CCSR address space mapping, and Table 5 shows how the MPC8560 configures the MSC8144 PIMMR base address.

### MSC8144 CCSR Mapping Example

| Table 5. | MPC8560 | Outbound | Window for | MSC8144 | CCSR Mapping |

|----------|---------|----------|------------|---------|--------------|

|          |         |          |            |         |              |

| Register    | Value      | Access<br>Type | Description                                                                                                                                                             |

|-------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONFIG_ADDR | 0x8000A810 | Write          | Allow a PCI configuration access when CONFIG_DATA is accessed<br>Select bus number 0<br>Select device number 21<br>Access the PIMMR Base Address Register (offset 0x10) |

| CONFIG_DATA | 0x30000000 | Write          | PIMMR = 0x30000000 CCSR mapping in PCI space                                                                                                                            |

For example, if the MPC8560 needs to read the MSC8144 PCI error status register (PCI\_ESR), then the MPC8560 accesses the outbound window that maps to the MSC8144 CCSR space. The PCI\_ESR is at 0xFFF7A000 in the MSC8144 local space. With a CCSR base address of 0xFE000000, the PCI\_ESR has an offset of 0x01F7A000 from the CCSR base. To access this register, the MPC8560 needs to read the following address:

Eqn. 1

### $PCI\_ESR = 0x90000000 + (0xFFF7A000 - 0xFE000000) = 0x91F7A000$

As you can see, the PIMMR allows an external master to access a device's internal memory-mapped registers without knowing where the CCSR resides. This is especially useful because the CCSR base address is programmable so that the PCI host can read and write the MSC8144 memory-mapped registers.

# 8 MSC8144 Outbound Configuration Example

In Section 5, "Memory Allocation Example," we noted that the MSC8144 configures three inbound windows for M2, M3, and DDR at bootup. The boot code does not configure the outbound windows, so the host must configure them. Knowing how the MPC8560 can access the MSC8144 memory-mapped registers, we allow the MPC8560 to set up the MSC8144 outbound window using the PIMMR. The MSC8144 defines an outbound memory window in the address range 0xE0000000–0xE7FFFFFF. Both the configuration access registers CONFIG\_ADDR and CONFIG\_DATA fall within this 128 Mbyte window. If the address is not 0xE7FFFFF0 (CONFIG\_ADDR) or 0xE7FFFFF4 (CONFIG\_DATA), then the transaction is forwarded to the PCI port.

When the MSC8144 initiates a transaction, the PCI outbound base address register (POBAR*n*) defines the location of the outbound translation in MSC8144 memory space. The POTAR*n* defines the starting-point of the outbound translation address in the destination PCI memory space. The POCMR*n* defines the size of an outbound translation window, defines properties, and enables that window.

Mapping the MSC8144 outbound window to the PCI space with a one-to-one mapping means that both the POBAR0 and POTAR0 registers are set to map a window at 0xE0000000. The MPC8560 writes to these registers through the PIMMR mapping in the PCI space. The MSC8144 can access the POTAR0 locally at 0xFFF7A100. Based on the settings for mapping the CCSR map, the MPC8560 can access the MSC8144 POTAR0 from its local space at 0x91F7A100. Similarly, it can access the MSC8144 POBAR0 and POCMR0 registers from 0x91F7A108 and 0x91F7A110, respectively.

Eqn. 2

$$POTAR0 = 0x90000000 + (0xFFF7A100 - 0xFE000000) = 0x91F7A100$$

Eqn. 3

*POBAR0* = 0*x*90000000 + (0*xFFF*7A108 - 0*xFE*000000) = 0*x*91*F*7A108

### Eqn. 4

$$POCMR0 = 0x90000000 + (0xFFF7A110 - 0xFE000000) = 0x91F7A110$$

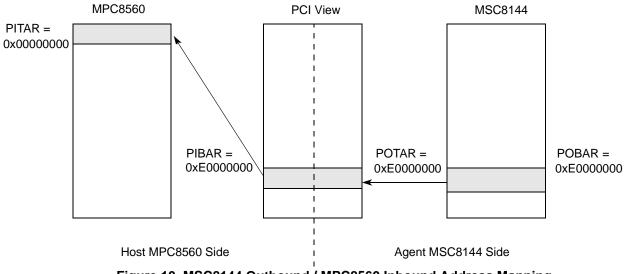

Suppose the MPC8560 receives inbound transactions at address 0x00000000 so that the mapping is as shown in Figure 10. The MPC8560 configures the MSC8144 outbound window register settings as shown in Table 6. Its inbound window register settings are shown in Table 7.

#### MSC8144 Outbound Configuration Example

Figure 10. MSC8144 Outbound / MPC8560 Inbound Address Mapping

| MSC8144<br>Register | Address as Visible<br>to MSC8144 | Address as Visible<br>to MPC8560 | Value      | Description                                                                                                                                |

|---------------------|----------------------------------|----------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| POTAR0              | 0xFFF7A100                       | 0x91F7A100                       | 0x000E0000 | Set base address 0xE0000000 as the translated address in the PCI memory space                                                              |

| POBAR0              | 0xFFF7A108                       | 0x91F7A108                       | 0x000E0000 | Set base address 0xE0000000 as the outbound window 0 in the MSC8144 local memory space                                                     |

| POCMR0              | 0xFFF7A110                       | 0x91F7A110                       | 0xA00F8000 | Enable the inbound translation window 0<br>Map window 0 to PCI memory space<br>Enable streaming<br>Set translation window 0 size as 128 MB |

### Table 6. MSC8144 PCI Outbound Registers Settings

### Table 7. MPC8560 PCI Inbound Registers Settings

| Register | Value      | Description                                                                                                                                                                                       |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PITAR1   | 0x0000000  | Set base address 0x00000000 as the translated address in the local MPC8560 memory space                                                                                                           |

| PIWBAR1  | 0x000E0000 | Set base address 0xE0000000 as the address in the PCI memory space                                                                                                                                |

| PIWAR1   | 0xA0F5501B | Enable the inbound translation window 1<br>Inbound window 1 is prefetchable<br>Target interface is local memory<br>Enable read and write with snooping<br>Set translation window 1 size as 256 MB |

Before the MSC8144 can initiate PCI accesses, the MPC8560 must configure the MSC8144 PCI bus command register, which has an offset of 0x04 in the PCI configuration space as shown in Figure 4. The BMST bit must be set so that the MSC8144 behaves as a bus master.

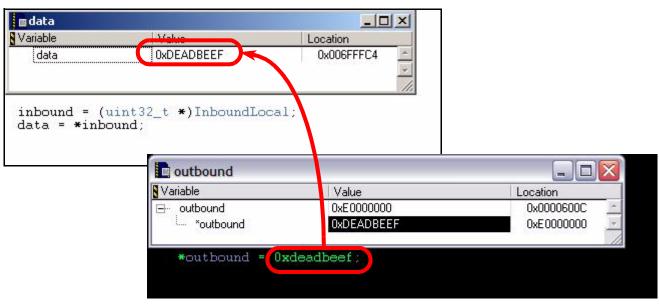

In Figure 11, the MSC8144 performs an outbound transaction. The bottom screenshot shows the MSC8144 writing the value 0xDEADBEEF to its local outbound window. This address is translated to the PCI address that is mapped to the MPC8560 local inbound window. The top screenshot shows the MPC8560 reading the same value from its local inbound window.

1. MSC8144 writes data to outbound window

Figure 11. MSC8144 Outbound Example

# 9 Cache Line Size

The MSC8144 PCI controller has an internal cache line of 32 bytes. Although the cache line size register in the configuration space is writable, only the value 8 is valid. This value indicates a cache line of 8 doublewords or 32 bytes. When the MSC8144 acts as a target, the bus command PCI MEMORY READ fetches a cache line of data. 32 bytes of data are fetched, regardless of the size requested by the initiator. In the MSC8144, there is no difference between the PCI MEMORY READ and PCI MEMORY READ LINE commands because the entire cache line is fetched in both cases. The PCI MEMORY READ MULTIPLE command is also similar, but it supports prefetching. This command causes a prefetch of the next cache line.

# 10 Latency Timer

The minimum grant (MIN\_GNT) space register defines the minimum time, in increments of 250 ns, during which the master retains ownership of the bus for adequate performance. This read-only register is useful in determining the value to be programmed into the bus master latency timer (LT) configuration register. Because the MSC8144 PCI controller is a bridge between PCI and local memory, it does not have specific requirements for the LT when it operates as a bus master. Therefore, MIN\_GNT is hard-wired to zero.

#### Interrupt Handling

Configuration software should configure LT according to system requirements. The LT value is system-dependent and this value should be tuned to maximize utilization without starving the other PCI bus masters. For example, leaving the LT at zero may require the master to rearbitrate for the bus for long data transfers, but setting it to the maximum value may potentially keep other masters from accessing the bus.

# 11 Interrupt Handling

In many PCI devices, the INTA, INTB, INTC, and INTD pins signal interrupts to the PCI bus. The interrupt pin configuration register in the configuration space at offset 0x3D indicates which of these four pins the device uses. However, the MSC8144 does not implement these four PCI interrupt pins. It is recommended that the general-purpose interrupt request lines IRQ0:15 and INT\_OUT be used to route interrupt sources.

# 12 MPC8560 Host Configuration Code

```

// Switch settings:

// SW1 00000110 PCI boot

// SW2 01101111 Disable JTAG chain

// SW3 10010111 PCI (256M DDR)

// SW4 01100010

#include <stdio.h>

#include "mpc8560pci.h"

// Check which ADx pin is connected to IDSEL

#define MSC8144 PCIDEVICENUM21

#define MPC8560 PCIDEVICENUM0

// PCI device id for MSC8144

#define MSC8144 PCIDEVID0x1400

#define MPC8560 PCIDEVID0x0009

#define MPC8560 PCIVENDORID0x1057

#define MSC8144 PCIVENDORID0x1957

#define READ UINT8(data, arg)

data = (uint8 t) (arg)

#define READ UINT16(data, arg)

data = (uint16_t) (arg)

#define READ_UINT32(data, arg)

data = (uint32 t) (arg)

#define GET UINT8(arg)

(uint8 t) (arg)

#define GET_UINT16(arg)

(uint16_t) (arg)

#define GET UINT32(arg)

(uint32 t) (arg)

#define WRITE UINT8(arg, data)

arg = (uint8 t) (data)

#define WRITE UINT16(arg, data)

arg = (uint16 t) (data)

#define WRITE UINT32(arg, data)

arg = (uint32 t) (data)

uint32_t IMMR8144Local = 0x90000000;

uint32 t OutboundLocal = 0x80000000;

uint32_t InboundLocal = 0x00000000;

uint32 t IMMR8144PCI

= 0 \times 3000000;

uint32 t OutboundPCI

= 0 \times C 0 0 0 0 0 0;

```

#### MPC8560 Host Configuration Code

```

NP

```

```

uint32 t InboundPCI

= 0 \times E 0 0 0 0 0 0;

uint32_t PCI8144BASE = 0x01F7A000;

msc8144 pci reqs *msc8144;

mpc8560_pci_regs *mpc8560 = (mpc8560_pci_regs*)0x40008000;

void setBCSR1();

uint32_t SwapLong(uint32_t);

uint32 t ConstructConfigWord (uint32 t , uint32 t, uint32 t);

void setPIMMR(uint32 t);

void scanDevices();

uint32_t getWindowSize(uint32_t, uint32_t, uint32_t);

void setOutbound1(uint32_t, uint32_t, uint32_t);

void setOutbound2(uint32_t, uint32_t, uint32_t);

uint32 t calcWindowSize(uint32 t);

void writePCIConfigReg(uint32 t, uint32 t, uint32 t);

void setPCIConfigReg32(uint32_t, uint32_t, uint32_t, uint32_t);

void setPCIConfigReg16(uint32_t, uint32_t, uint32_t, uint16_t);

void setPCIConfigReg8(uint32_t, uint32_t, uint32_t, uint8_t);

uint32_t readPCIConfigReg(uint32_t, uint32_t, uint32_t);

uint32_t getPCIConfigReg32(uint32_t, uint32_t, uint32_t);

uint16_t getPCIConfigReg16(uint32_t, uint32_t, uint32_t);

uint8_t getPCIConfigReg8(uint32_t, uint32_t, uint32_t);

uint32_t SwapLong(uint32_t value)

{

value = ((value & 0xFF)

<< 24)

((value & 0xFF00)

<< 8)

((value & 0xFF0000UL)

>> 8)

((value & 0xFF000000UL) >> 24) ;

return value;

}

uint32_t ConstructConfigWord (uint32_t BusNum,uint32_t DevNum,uint32_t RegNum)

{

uint32 t value;

uint32_t FuncNum=0x0;

value = (

((BusNum & 0xFF) << 16)

((DevNum & 0xFF) << 11)

((FuncNum & OxFF)

<< 8)

((RegNum & 0xFC)

)

ENABLE

);

return value;

}

void writePCIConfigReg(uint32_t BusNum, uint32_t DevNum, uint32_t Reg, uint32_t Data)

{

uint32 t cfg addr;

uint32_t data32;

data32 = SwapLong(Data);

if ((Reg & 0x3) == 1)

data32 = data32 >> 8;

```

MSC8144 PCI Example Software, Rev. 0

```

NP

```

```

MPC8560 Host Configuration Code

```

```

else if ((Reg & 0x3) == 2)

data32 = data32 >> 16;

else if ((Reg & 0x3) == 3)

data32 = data32 >> 24;

cfg addr = ConstructConfigWord(BusNum, DevNum, Reg);

WRITE UINT32(mpc8560->config addr, cfg addr);

WRITE_UINT32(mpc8560->config_data, data32);

}

void setPCIConfigReg32(uint32 t BusNum, uint32 t DevNum, uint32 t Reg, uint32 t Data)

writePCIConfigReg(BusNum, DevNum, Reg, Data);

}

void setPCIConfigReg16(uint32_t BusNum, uint32_t DevNum, uint32_t Reg, uint16_t Data)

writePCIConfigReg(BusNum, DevNum, Reg, Data);

}

void setPCIConfigReg8(uint32 t BusNum, uint32 t DevNum, uint32 t Reg, uint8 t Data)

{

writePCIConfigReg(BusNum, DevNum, Reg, Data);

}

uint32 t readPCIConfigReg(uint32 t BusNum, uint32 t DevNum, uint32 t Reg)

uint32_t cfg_addr;

uint32_t cfg_data;

cfg_addr = ConstructConfigWord(BusNum, DevNum, Reg);

WRITE UINT32(mpc8560->config addr, cfg addr);

READ UINT32(cfg data, mpc8560->config data);

cfg_data = SwapLong(cfg_data);

if ((Reg & 0x3) == 1)

cfg_data = cfg_data >> 8;

else if ((Reg & 0x3) == 2)

cfg data = cfg data >> 16;

else if ((Reg & 0x3) == 3)

cfg data = cfg data >> 24;

return cfg_data;

}

uint32_t getPCIConfigReg32(uint32_t BusNum, uint32_t DevNum, uint32_t Reg)

ł

return (uint32 t)readPCIConfigReg(BusNum, DevNum, Reg);

}

uint16 t getPCIConfigReg16(uint32 t BusNum, uint32 t DevNum, uint32 t Reg)

return (uint16 t)readPCIConfigReg(BusNum, DevNum, Reg);

}

```

MSC8144 PCI Example Software, Rev. 0

```

uint8 t getPCIConfigReg8(uint32 t BusNum, uint32 t DevNum, uint32 t Reg)

{

return (uint8 t)readPCIConfigReg(BusNum, DevNum, Reg);

}

void scanDevices()

{

uint32_t i;

uint16 t VendorID, DeviceID;

uint32 t BusNum = 0;

for(i = 0; i < 0x100; i++)</pre>

{

VendorID = getPCIConfigReg16(BusNum, i, REG VENDORID);

DeviceID = getPCIConfigReg16(BusNum, i, REG DEVID);

if(VendorID != 0xFFFF)

{

printf(" Device found: Device %x, Bus %x, DevID = %x, VendorID =

%x\n",

i, BusNum, DeviceID, VendorID);

}

}

}

void setBCSR1()

{

uint8 t *bcsr1 = (uint8 t*)0xF8000001;

*bcsr1 |= 0x30;

}

uint32_t getWindowSize(uint32_t BusNum, uint32_t DevNum, uint32_t Reg)

{

uint32_t new, orig;

uint32_t size;

// Read CfgReg

orig = getPCIConfigReg32(BusNum, DevNum, Reg);

// Write all 1's

setPCIConfigReg32(BusNum, DevNum, Reg, 0xFFFFFFFF);

// Read back to determine size

new = getPCIConfigReg32(BusNum, DevNum, Reg);

// Restore orig register value

setPCIConfigReg32(BusNum, DevNum, Reg, orig);

// Calculate size required by agent

if (new & 1)

size = (~new | 3) + 1;// I/O space

else

size = (~new | 0xF) + 1;// Memory space

return size;

}

```

#### MPC8560 Host Configuration Code

```

void setOutbound2(uint32_t LocalAddr, uint32_t PCIAddr, uint32_t WindowSize)

{

// PCI address

mpc8560->potar2

= PCIAddr

>> 12;

// Local Addr

mpc8560->powbar2 = LocalAddr >> 12;

// Enable, memory read/write, window size

mpc8560->powar2 = 0x80044000 | WindowSize ;

}

void setOutbound1(uint32_t LocalAddr, uint32_t PCIAddr, uint32_t WindowSize)

{

// PCI address

mpc8560->potar1

= PCIAddr

>> 12;

// Local Addr

mpc8560->powbar1 = LocalAddr >> 12;

// Enable, memory read/write, window size

mpc8560->powar1

= 0x80044000 | WindowSize ;

}

uint32_t calcWindowSize(uint32_t Size)

{

int i;

uint32 t WindowSize = 0;

for(i = 0; i < 32; i++)</pre>

{

if(Size & 0x01)

{

WindowSize += i;

}

Size = Size >> 1;

}

WindowSize = WindowSize - 1;

return WindowSize;

}

void main()

{

uint32_t BusNum = 0;

uint32_t *outbound, *inbound;

uint32_t size;

uint32_t windowstart;

uint16_t status_8144;

uint32 t data;

// Set BCSR1[RGMII1EN and RGMII2EN] = 1 (Disable) to select PCI/UTP instead of RGMII

setBCSR1();

// Scan devices on the bus

```

#### MPC8560 Host Configuration Code

```

scanDevices();

// Set 8560 as the arbiter

setPCIConfigReg16(BusNum, MPC8560 PCIDEVICENUM, REG ARBITER, 0);

// Set latency timer to max clock cycles to generate stop

setPCIConfigReg8(BusNum, MPC8560 PCIDEVICENUM, REG BUSLATENCY, 0xF8);

// 8560 Outbound / 8144 Inbound

// 8560 0x8000_0000 --> PCI 0x8000_0000 --> 8144 0xC000_0000

// Size 512KB

// Determine window sizes for 8144 GPLx = 0x0010 0000

size = getWindowSize(BusNum, MSC8144 PCIDEVICENUM, REG GPLBAR0); //M2

// Reassign 8144 inbound window 0 start addr in PCI memory space

setPCIConfigReg32(BusNum, MSC8144 PCIDEVICENUM, REG GPLBAR0, OutboundPCI);

// Read 8144 PCI base inbound window = 0x2000 0008 (prefetchable)

windowstart = getPCIConfigReg32(BusNum, MSC8144 PCIDEVICENUM, REG GPLBAR0);

// Set outbound window local address 0x80000000, PCI address 0x20000000, 512KB size

setOutbound1(OutboundLocal, OutboundPCI, calcWindowSize(size));

// 8144 Outbound / 8560 Inbound

// 8144 0xE000_0000 --> PCI 0xE000_0000 --> 8560 0x0000_0000

// Size 256MB

// Set inbound window local address 0x00000000, PCI address 0xE0000000

// PCI address

mpc8560->piwbar1 = InboundPCI >> 12;

// Local Addr

mpc8560->pitar1 = InboundLocal >> 12;

// Enable, prefetch, target i/f local mem, r/w snoop, 256MB size

mpc8560->piwar1 = 0xA0F5501B;

// 8144 PIMMR memory mapped space

// 8560 0x9000 0000 --> PCI 0x3000 0000 --> 8144 0xFE00 0000 (IMMR)

// Size 32MB

// Determine window size and set start addr for 8144 PIMMR

size = getWindowSize(BusNum, MSC8144_PCIDEVICENUM, REG_PIMMRBACR);//IMMR 32MB

// Reassign 8144 inbound window 1 start addr in PCI memory space

setPCIConfigReg32(BusNum, MSC8144 PCIDEVICENUM, REG PIMMRBACR, IMMR8144PCI);

windowstart = getPCIConfigReg32(BusNum, MSC8144 PCIDEVICENUM, REG PIMMRBACR);

// Set outbound window local address 0x00000000, PCI address 0x30000000, 32MB size

```

setOutbound2 (IMMR8144Local, IMMR8144PCI, calcWindowSize(size));

```

NP_

```

MPC8560 Header File

```

// BMST=1, MEM=1, PERR/SERR=1

setPCIConfigReg16(BusNum, MPC8560 PCIDEVICENUM, REG BUSCMD, 0x0146);

// BMST=1, MEM=1, PERR/SERR=1

setPCIConfigReg16(BusNum, MSC8144_PCIDEVICENUM, REG_BUSCMD, 0x0146);

// Now 8560 can access 8144 memory-mapped registers to set up

// 8144's outbound windows

PCI8144BASE = PCI8144BASE + IMMR8144Local;

msc8144 = (msc8144 pci regs*)PCI8144BASE;

// MSC8144 outbound 0 enable, prefetch, streaming

msc8144->outbound[0].potar = InboundPCI >> 12;

msc8144->outbound[0].pobar = 0x000E0000;

msc8144->outbound[0].pocmr = 0xA00F8000;

// Perform outbound transaction

// 8560 writes to 8144 memory

// Step through code here to write to memory

// Then in 8144 project, step through code to read memory

outbound = (uint32 t *)OutboundLocal;

*outbound = (uint32_t) 0x11223344;

// Perform inbound transaction

// 8144 writes to 8560 memory

// In 8144 project, step through code to write to memory

// Then step through code here to read memory

inbound = (uint32 t *)InboundLocal;

data = *inbound;

```

}

### 13 MPC8560 Header File

#include "os\_datatypes.h"

// CONFIG\_ADDR bits

#define ENABLE 0x80000000

// Configuration Access Registers

#define REG\_VENDORID 0x0000

| REG_VENDORID  | 0x0000                  |

|---------------|-------------------------|

| REG_DEVID     | 0x0002                  |

| REG_BUSCMD    | 0x0004                  |

| REG_BUSSTATUS | 0x0006                  |

|               | REG_DEVID<br>REG_BUSCMD |

MSC8144 PCI Example Software, Rev. 0

#### #define REG REVID 0x0008 #define REG\_BUSPROGIF 0x0009 #define REG SUBCLASS 0x000A #define REG BASECLASS 0x000B #define REG CACHELINESZ 0x000C #define REG\_BUSLATENCY 0x000D #define REG HDRTYPE 0x000E #define REG BISTCTL 0x000F #define REG PIMMRBACR 0x0010 #define REG GPLBAR0 0x0014 #define REG\_GPLBAR1 0x0018 #define REG\_GPLEXTBAR1 0x001C #define REG GPLBAR2 0x0020 #define REG\_GPLEXTBAR2 0x0024 #define REG SUBSYSVENDORID 0x002C #define REG SUBSYSID 0x002E #define REG CAPABILITYPTR 0x0034 #define REG INTERRLINE 0x003C #define REG INTERRPIN 0x003D #define REG MINGNT 0x003E #define REG MAXLAT 0x003F #define REG FUNCTION 0x0044 #define REG\_ARBITER 0x0046 #define SIZE 4KB 0x0B #define SIZE\_8KB 0x0C #define SIZE 16KB 0x0D#define SIZE 32KB 0x0E#define SIZE 64KB 0x0F#define SIZE 128KB $0 \times 10$ #define SIZE 256KB 0x11 #define SIZE 512KB 0x12 #define SIZE 1MB 0x13 #define SIZE 2MB 0x14 #define SIZE\_4MB 0x15 #define SIZE\_8MB 0x16 #define SIZE 16MB 0x17 #define SIZE\_32MB 0x18 #define SIZE 64MB 0x19 #define SIZE 128MB 0x1A #define SIZE 256MB 0x1B #define SIZE 512MB $0 \times 1 C$ #define SIZE 1GB 0x1D #define SIZE 2GB 0x1E #define SIZE 4GB 0x1F

```

typedef struct

{

volatile uint32_tconfig_addr;

volatile uint32_tconfig_data;

volatile uint32_tint_ack;

volatile uint8_treserved[0xBF4];

volatile uint32_tpotar0;

volatile uint32_tpotear0;

volatile uint32_tpowbar0;

```

#### MPC8560 Header File

MPC8560 Header File

```

volatile uint8 treserved0[0x4];

volatile uint32_tpowar0;

volatile uint8_treserved1[0xC];

volatile uint32_tpotar1;

volatile uint32 tpotear1;

volatile uint32 tpowbar1;

volatile uint8_treserved2[0x4];

volatile uint32 tpowar1;

volatile uint8 treserved3[0xC];

volatile uint32_tpotar2;

volatile uint32 tpotear2;

volatile uint32_tpowbar2;

volatile uint8 treserved4 [0x4];

volatile uint32 tpowar2;

volatile uint8_treserved5[0xC];

volatile uint32_tpotar3;

volatile uint32_tpotear3;

volatile uint32 tpowbar3;

volatile uint8 treserved6[0x4];

volatile uint32_tpowar3;

volatile uint8_treserved7[0xC];

volatile uint32_tpotar4;

volatile uint32 tpotear4;

volatile uint32 tpowbar4;

volatile uint8 treserved8[0x4];

volatile uint32_tpowar4;

volatile uint8 treserved9[0x10C];

volatile uint32 tpitar3;

volatile uint8 treserved10[0x4];

volatile uint32_tpiwbar3;

volatile uint32_tpiwbear3;

volatile uint32 tpiwar3;

volatile uint8_treserved11[0xC];

volatile uint32 tpitar2;

volatile uint8 treserved12[0x4];

volatile uint32_tpiwbar2;

volatile uint32 tpiwbear2;

volatile uint32_tpiwar2;

volatile uint8 treserved13[0xC];

volatile uint32_tpitar1;

volatile uint8_treserved14[0x4];

volatile uint32 tpiwbar1;

volatile uint32_tpiwbear1;

volatile uint32 tpiwar1;

volatile uint8 treserved15[0xC];

```

```

} mpc8560_pci_regs;

```

```

MPC8560 Header File

```

```

typedef struct

{

volatile uint32 t potar;

/* PCI Outbound Translation Address Register */

volatile uint8 t reserved1[0x4];

volatile uint32_t pobar;

/* PCI Outbound Base Address Register */

volatile uint8_t reserved2[0x4];

volatile uint32 t pocmr;

/* PCI Outbound Comparison Mask Register */

volatile uint8_t reserved3[0x4];

} pci outbound window t;

typedef struct

ł

volatile uint32 t pitar;

/* PCI Inbound Translation Address Register */

volatile uint8_t reserved1[0x4];

volatile uint32 t pibar;

/* PCI Inbound Base Address Register */

/* PCI Inbound Extended Base Address Register */

volatile uint32 t piebar;

volatile uint32 t piwar;

/* PCI Inbound Window Attributes Register */

volatile uint8 t reserved2[0x4];

} pci inbound window t;

typedef struct

{

/* PCI Error Management Registers */

/* PCI error capture disable register */

volatile uint32 t pci ecdr;

volatile uint32_t pci_err;

/* PCI error enable register */

volatile uint32 t pci eatcr;

/* PCI error attributes capture register */

volatile uint32_t pci_eacr;

/* PCI error address capture register */

volatile uint32 t pci eeacr;

/* PCI error extended address capture register */

/* PCI error data capture register */

volatile uint32_t pci_edcr;

volatile uint8 t reserved1[0x038 - 0x01C];

/* PCI Inbound Registers */

pci inbound window t inbound2;

pci_inbound_window_t inbound1;

pci_inbound_window_t inbound0;

volatile uint8 t

reserved2[0x100 - 0x080];

/* PCI Outbound Registers */

pci outbound window_t outbound[6];

volatile uint8 t

reserved3[0x1F8 - 0x190];

/* PCI Control Registers */

volatile uint32_t dtcr;

/* Discard Timer Control Register */

volatile uint8 t reserved4[0x200 - 0x1FC];

} msc8144_pci_regs;

```

MPC8560 Header File

### THIS PAGE INTENTIONALLY LEFT BLANK

MPC8560 Header File

### THIS PAGE INTENTIONALLY LEFT BLANK

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. IEEE nnn, nnn,nnn, and nnn are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2006. All rights reserved.

Document Number: AN3098 Rev. 0 11/2006