# Freescale Semiconductor

**Application Note**

AN3221 Rev. 0, 01/2006

# MPC5200B SDRAM Initialization and Configuration

by: Lamar Hansford Infotainment, Multimedia, and Telematics Division

This document is presented for the purpose of developing knowledge in the area of the MPC5200B DRAM interface. Both the hardware and software aspects of configuring SDRAM and DDR DRAM devices are provided here. The MPC5200B is based on a an MPC603e PowerPC<sup>TM</sup> core.

# 1 Overview

The MPC5200B SDRAM interface module is a flexible controller enabling systems using either SDR and DDR devices. The memory subsystem on the MPC5200B has the following features.

- Two chip selects

- Up to 256 MB programmable space on each chip select

- Support for 2 and 3 CAS latency SDR

- Support for 2 & 2.5 CAS latency DDR

- Programmable timing interface which allows support for memories from multiple vendors

## Table of Contents

| 1 |

|---|

| 2 |

| 2 |

| 2 |

| 3 |

| 3 |

| 4 |

| 5 |

| 8 |

| 9 |

| 4 |

| 5 |

| 7 |

| 7 |

|   |

| 5 |

|   |

© Freescale Semiconductor, Inc., 2006. All rights reserved.

MPC5200B Memory Interface & Architecture

# 2 MPC5200B Memory Interface & Architecture

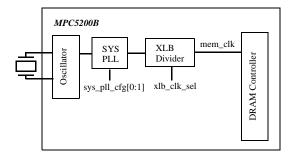

# 2.1 Clock Generation

When configuring the DRAM interface, it is critical that developers understand how the DRAM clock (mem\_clk) is generated.

Figure 1. DRAM Clock Generation

In the diagram above, the signals sys\_pll\_cfg[0:1] and xlb\_clk\_sel are controlled at boot time through the CDM power on reset configuration register–MBAR + 0x0204, bits [24:26].

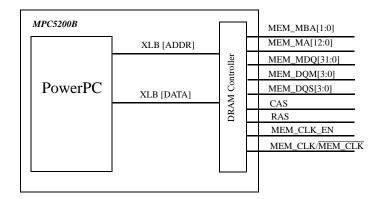

# 2.2 MPC5200B Bus Architecture

The MPC5200B DRAM controller address and data is derived from the XL Bus driven from the PowerPC system. Care must be taken to ensure that PowerPC notation is translated to conventional notation when considering the external interface<sup>1</sup>.

Figure 2. DRAM Signals

<sup>1.</sup> In PowerPC notation, the bit 0 is the MSB, and bit 31 is the LSB.

## 2.2.1 DRAM External Signals

## Table 1. SDRAM External Signals

| External Signal<br>Name | Direction     | Description                                                                                                                                                                                 | Derived From                                                               |

|-------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| MEM_CLK                 | 0             | Memory clock–Frequency is the same as the internal XL bus clock. Maximum allowed value is 132 MHz.                                                                                          | xlb_clock <sup>1</sup>                                                     |

| MEM_CLK                 | 0             | Inverted memory clock–Used for DDR-SDRAM devices.<br>Internally generated "DQS" for SDR-SDRAM devices.                                                                                      | xlb_clock                                                                  |

| MEM_CLK_EN              | 0             | Memory clock enable (CKE)–When low, the SDRAM is disabled. Used to switch memory into and out of self-refresh/power-down modes.                                                             |                                                                            |

| MEM_CS[1:0]             | 0             | Memory chip select.                                                                                                                                                                         | See Section 3.2.1,<br>"SDRAM Chip<br>Select<br>Configuration<br>Registers" |

| MEM_RAS                 | 0             | Memory row address select–Asserts on read and write operations to the SDRAM memory space.                                                                                                   | See Table 2                                                                |

| MEM_CAS                 | 0             | Memory Column Address Select–Asserts on read and write operations to the SDRAM memory space.                                                                                                | See Table 2                                                                |

| MEM_WE                  | 0             | Memory write enable–Asserts on write operation to the SDRAM memory space.                                                                                                                   | See Table 2                                                                |

| MEM_MA[12:0]            | 0             | Memory multiplexed address <sup>2</sup>                                                                                                                                                     | See Table 10                                                               |

| MEM_MBA[1:0]            | 0             | Memory bank address                                                                                                                                                                         | xlb_addr[20:21]                                                            |

| MEM_DQM[3:0]            | 0             | Memory data mask–Addressing = 0:3<br>0 Data byte read/write is enabled<br>1 Data byte read/write is inhibited<br>In all modes the memory controller ignores mask bits when<br>reading data. | xlb_addr[1:0]                                                              |

| MEM_MDQ[31:0]           | I/O           | Memory data. addressing                                                                                                                                                                     | xlb_data[31:0] <sup>3</sup>                                                |

| MEM_MDQS[3:0]           | I/O           | Memory data strobe, DDR only-Addressing = 0:3.                                                                                                                                              |                                                                            |

| Note: For 16-bit mo     | de external p | bulldown devices are required on MEM_MDQS[1:0].                                                                                                                                             |                                                                            |

NOTES:

<sup>1</sup> xlb\_clock is controlled through the reset configuration word.

<sup>2</sup> MEM\_MA[10] is used as a control signal per DRAM specifications.

<sup>3</sup> When a port size of 16-bits is selected, data bits are mapped from the upper half-word, or xlb\_data[31:16].

## 2.2.2 DRAM Command Generation

The MPC5200B generates DRAM commands on the memory interface according to JEDEC specifications. This specification dictates that the  $\overline{CS}$ ,  $\overline{CAS}$ ,  $\overline{RAS}$ , and  $\overline{WE}$  signals can be driven to place the DRAM into a corresponding mode which allows read, write, precharge, and internal setup mode (others may be available depending on manufacturer). These commands are used by the memory controller during normal operation of the device without user intervention. The list of supported commands can be seen in Section 2.2.2.1, "Supported DRAM Commands".

## 2.2.2.1 Supported DRAM Commands

When performing DRAM transactions, the memory controller generates the corresponding SDRAM command. Table 2 lists SDRAM commands supported by the memory controller. These commands are automatically generated by the controller any time read and write operations occur to the selected DRAM chip select range. Additionally the memory controller will generate refresh commands according to the parameters programmed in the ref\_interval bit field of the Memory Controller Control Register–MBAR + 0x0104 of the MPC5200B.

| Function                    | Symbol | CKE <sup>1</sup> | CS <sup>2</sup> | RAS | CAS | WE | BA[1:0] <sup>3</sup> | A10 <sup>4</sup> | Other A |

|-----------------------------|--------|------------------|-----------------|-----|-----|----|----------------------|------------------|---------|

| Command inhibit             | INH    | Н                | Н               | Х   | Х   | Х  | Х                    | Х                | Х       |

| No operation                | NOP    | Н                | L               | Н   | Н   | Н  | Х                    | Х                | Х       |

| Read                        | READ   | Н                | L               | Н   | L   | Н  | V                    | L                | V       |

| Write                       | WRIT   | Н                | L               | Н   | L   | L  | V                    | L                | V       |

| Row and bank active         | ACT    | Н                | L               | L   | Н   | Н  | V                    | V                | V       |

| Burst terminate             | BST    | Н                | L               | Н   | Н   | L  | Х                    | Х                | Х       |

| Precharge all banks         | PALL   | Н                | L               | L   | Н   | L  | Х                    | Н                | Х       |

| Load mode register          | LMR    | Н                | L               | L   | L   | L  | LL                   | V                | V       |

| Load extended mode register | LEMR   | Н                | L               | L   | L   | L  | LH                   | V                | V       |

| CBR auto refresh            | AREF   | Н                | L               | L   | L   | Н  | Х                    | Х                | Х       |

| Self refresh                | SREF   | H→L              | L               | L   | L   | Н  | Х                    | Х                | Х       |

| Power down                  | PDWN   | H→L              | Н               | Х   | Х   | Х  | Х                    | Х                | Х       |

| Table | 2. | SDRAM | Commands |

|-------|----|-------|----------|

|-------|----|-------|----------|

## Note:

• H = High

• L = Low

• V = Valid

• X = Don't care

NOTES:

- <sup>1</sup> MEM\_CLK\_EN

- <sup>2</sup> MEM\_CS[0:1] <sup>3</sup> MEM\_MBA[1:0]

- <sup>3</sup> MEM\_MBA[1:0] <sup>4</sup> MEM\_MA[10]

- <sup>4</sup> MEM\_MA[10]

# 3 Software Configuration

Software configuration of the DRAM memory interface is performed by following 4 basic steps.

- 1. GPIO configuration

- 2. Memory map and chip select configuration

- 3. DRAM interface configuration

- 4. DRAM vendor specific configuration

This software initialization should be combined into the standard boot flow and should be addressed in separate phases. The list above represents four different software modules.

# 3.1 GPIO Configuration

By default "chip select 1" is configured as a general purpose IO pin. To use this pin as a chip select, it must be reconfigured as a chip select. This is accomplished by programming bit 0 (MSB) of the GPS port configuration register–MBAR + 0x0B00–to 1 (reset value is 0).

## 3.1.1 GPS Port Configuration Register

| MBAR<br>offset |         | Name |      |     | Description                     |    |     |    |     |       |    |      |      |      |      |       |        |

|----------------|---------|------|------|-----|---------------------------------|----|-----|----|-----|-------|----|------|------|------|------|-------|--------|

| 0x0B00         | GPS     | _POR | CFG  | GP  | PIO port configuration register |    |     |    |     |       |    |      |      |      |      |       |        |

|                | msb 0   | 1    | 2    | 3   |                                 | 4  | 5   | 6  | 7   | 8     | ç  | 9 10 | ) 11 | 12   | ! 13 | 14    | 15     |

| R              | CS1     | 21   | A    | LTs | C                               | S7 | CS6 |    | ATA | 3_CLK |    | IRD  | A    |      | E    | Ether |        |

| W              | -       | LPTZ |      |     |                                 |    |     |    |     |       |    |      |      |      |      |       |        |

| RESET:         | 0       | 0    | 0    | 0   |                                 | 0  | 0   | 0  | 0   | 0     | (  | ) 0  | 0    | 0    | 0    | 0     | 0      |

|                | 16      | 1    | 7    | 18  | 19                              | 20 | 21  | 22 | 23  | 24    | 25 | 26   | 27   | 28   | 29   | 30    | 31 lsb |

| R              | PCI_DIS | USE  | 3_SE | US  | βB                              |    | PS  | C3 |     | Rsvd  |    | PSC2 |      | Rsvd |      | PSC1  |        |

| W              |         |      |      |     |                                 |    |     |    |     |       |    |      |      |      |      |       |        |

| RESET:         | 0       |      | 0    | 0   | 0                               | 0  | 0   | 0  | 0   | 0     | 0  | 0    | 0    | 0    | 0    | 0     | 0      |

## Table 3. GPS Port Configuration Register

## Table 4. GPS Port Configuration Field Description (Sheet 1 of 3)

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                        |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | CS1  | Memory chip select bit<br>0 gpio_wkup_6<br>1 mem_cs1 (second SDRAMC chip select) on gpio_wkup_6 pin                                                                                                                                                                                                                                |

| 1   | LPTZ | LocalPlus non-muxed TSIZ bit<br>0 gpio_wkup_7 and test_sel_1<br>1 TSIZ 1 on gpio_wkup_7 and TSIZ 2 on test_sel_1                                                                                                                                                                                                                   |

| 2:3 | ALTS | <ul> <li>Alternatives<sup>1</sup></li> <li>00No Alternatives: CAN1/2 on PSC2 according to PSC2 setting;<br/>SPI on PSC3 according to PSC3 setting.</li> <li>01 ALT CAN position: CAN1 on I2C1, CAN2 on Tmr0/1 pins<sup>2</sup></li> <li>10 ALT SPI position: SPI on Tmr2/3/4/5 pins<sup>1</sup></li> <li>11 Both on ALT</li> </ul> |

| 4   | CS7  | 0 Interrupt GPIO on PSC3_5 <sup>3</sup><br>1 CS7 on PSC3_5                                                                                                                                                                                                                                                                         |

| Bit    | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | CS6        | 0 Interrupt GPIO on PSC3_4 <sup>3</sup><br>1 CS6 on PSC3_4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6:7    | ΑΤΑ        | Advanced technology attachment<br>00 No ATA chip selects, csb_4/5 used as normal chip select<br>01 ATA cs0/1 on csb_4/5<br>10 ATA cs0/1 on i2c2 clk/io<br>11 ATA cs0/1 on Tmr0/1 <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8      | IR_USB_CLK | Infrared USB clock<br>0 IrDA/USB 48MHz clock generated internally. Pin is GPIO.<br>1 IrDA/USB clock is sourced externally, input only                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9:11   | IRDA       | Infrared data association<br>000 All IrDA pins are GPIOs<br>001 Reserved<br>010 Reserved<br>011 Reserved<br>100 Reserved<br>101 UART (without CD) / IrDA<br>110 Reserved<br>111 CODEC (without MCLK) / IrDA                                                                                                                                                                                                                                                                                                                                                                                          |

| 12: 15 | Ether      | Ethernet<br>0000 All 18 Ethernet pins are GPIOs<br>0001 USB2 on Ethernet <sup>4</sup><br>0010 Ethernet 10Mbit (7-wire) mode<br>0011 Ethernet 7-wire and USB2 <sup>4</sup><br>0100 Ethernet 100Mbit without MD<br>0101 Ethernet 100Mbit with MD<br>011X Reserved<br>1000 Ether 7-wire, UARTe, J1850<br>1001 Ether 7-wire, J1850<br>1010 Two UARTs, J1850<br>1011 One UARTe, J1850<br>1101 Reserved<br>1101 Reserved<br>111X Reserved                                                                                                                                                                  |

| 16     | PCI_DIS    | <ul> <li>0 PCI controller enabled</li> <li>1 PCI controller disabled</li> <li>When large Flash or most graphics modes are enabled on the LocalPlus bus interface, the<br/>PCI interface cannot be used (PCI control signals are used to support these modes).</li> <li>When these modes are enabled (see LocalPlus control registers), the PCI controller must<br/>be disabled to prevent interference.</li> <li>If these modes are enabled at boot, this bit will come out of reset set to 1.</li> <li>If these modes are not enabled at boot, this bit will come out of reset set to 0.</li> </ul> |

## Table 4. GPS Port Configuration Field Description (Sheet 2 of 3)

| Table 4. GPS Port Configuration Field Description | (Sheet 3 of 3) |

|---------------------------------------------------|----------------|

|                                                   |                |

| Bit   | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | USB_SE | USB single ended mode<br>The USB interface is able to support both differential and single-ended modes. This bit<br>allows the USB I/O interface to be programmed to single-ended mode. Differential mode<br>supplies TXP/TXN and RXP/TXN.<br>Single ended mode supplies TXP/TX_SE0 and RXP/RX_SE0.<br>This bit controls <i>all</i> USB ports (that is, they are not individually programmable). Default is<br>differential mode.<br>0 Differential mode (Default after reset)<br>1 Single ended mode |

| 18:19 | USB    | 00 4 GPIOs and 1 interrupt GPIO<br>01 USB<br>10 Two UARTs<br>11 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 20:23 | PSC3   | Programmable serial controller 3<br>0000 All PSC3 pins are GPIOs<br>0001 USB2 on PSC3, no GPIOs available <sup>4</sup><br>001X Reserved<br>0100 UART functionality without CD<br>0101 UARTe functionality with CD<br>0110 CODEC3 functionality<br>0111 CODEC3 functionality (with MCLK)<br>100X SPI<br>101X Reserved<br>1100 SPI with UART3<br>1101 SPI with UART3e<br>111X SPI with CODEC3                                                                                                           |

| 24    | _      | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25:27 | PSC2   | Programmable serial controller 2<br>000 All PSC2 pins are GPIOs<br>001 CAN1&2 on PSC2 pins <sup>4</sup><br>01X AC97 functionality<br>100 UART functionality without CD<br>101 UARTe functionality with CD<br>110 CODEC2 functionality(without MCLK)<br>111 CODEC2 functionality (with MCLK)                                                                                                                                                                                                           |

| 28    |        | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 29:31 | PSC1   | Programmable serial controller 1<br>00X All PSC1 pins are GPIOs<br>01X AC97 functionality<br>100 UART functionality without CD<br>101 UARTe functionality with CD<br>110 CODEC1 functionality (without MCLK)<br>111 CODEC1 functionality (with MCLK)                                                                                                                                                                                                                                                  |

# NOTES:

<sup>1</sup> ALT SPI cannot exist with any SPI on PCS3.

$^{2}$  ALT CAN cannot exist with ATA on Tmr0/1, and not with CAN on PSC2.

<sup>3</sup> PSC3\_4 and PSC3\_5 default to zero (interrupt gpio) after reset; however, if the PSC3 is programmed to USB2 mode, RXP and RXN will be on these pins. If PSC is programmed to UARTe mode, CD will be on the PSC3\_4 pin.

<sup>4</sup> USB cannot exist on both Either and PSC3.

# 3.2 Memory Map And Chip Select Configuration

The chip select configuration register can be found in the bank of registers located at MBAR + 0x34. These two registers control the configuration on the start address of each DRAM chip select and the size of the DRAM.

## 3.2.1 SDRAM Chip Select Configuration Registers

| MBAR<br>offset | Name                   | Description                                                                                   |

|----------------|------------------------|-----------------------------------------------------------------------------------------------|

| 0x0034         | SDRAM Chip<br>Select 0 | Contains the base addresses and configurations for SDRAM's connected to the SDRAM controller. |

| 0x0038         | SDRAM Chip<br>Select 1 |                                                                                               |

## Table 5. SDRAM Chip Select Configuration Register

|       | msb 0 | 1                | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11     | 12       | 13 | 14 | 15     |  |

|-------|-------|------------------|----|----|----|----|----|----|----|----|----|--------|----------|----|----|--------|--|

| R     |       | Base XLB Address |    |    |    |    |    |    |    |    |    |        | Reserved |    |    |        |  |

| w     |       |                  |    |    |    |    |    |    |    |    |    |        |          |    |    |        |  |

| RESET | 0     | 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0      |  |

|       |       |                  |    |    |    |    |    |    |    |    |    |        |          |    |    |        |  |

|       | 16    | 17               | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27     | 28       | 29 | 30 | 31 lsb |  |

| R     |       | Reserved         |    |    |    |    |    |    |    |    | SD | RAM Si | ze       |    |    |        |  |

| w     |       |                  |    |    |    |    |    |    |    |    |    |        |          |    |    |        |  |

| RESET | 0     | 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0      | 0        | 0  | 0  | 0      |  |

| Bit     | Name                                                                 | Description                                                                                                      |  |  |  |  |  |  |

|---------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0:11    | Base XLB<br>Address                                                  | Start address for memory                                                                                         |  |  |  |  |  |  |

| 12:26   | Reserved                                                             | These bits are reserved                                                                                          |  |  |  |  |  |  |

| 27:31   | SDRAM size                                                           | Should be set to size of SDRAM at corresponding SDRAM chip select. Settings are included in the following table. |  |  |  |  |  |  |

| Note: 7 | Note: The Base XL bus address must be consistent with the SDRAM size |                                                                                                                  |  |  |  |  |  |  |

| SDRAM<br>Memory Size | SDRAM size bit setting |

|----------------------|------------------------|

| 11111 <sup>1</sup>   | 4GB <sup>1</sup>       |

| 11110 <sup>1</sup>   | 2GB <sup>1</sup>       |

| 11101 <sup>1</sup>   | 1GB <sup>1</sup>       |

| 11100 <sup>1</sup>   | 512MB <sup>1</sup>     |

| SDRAM<br>Memory Size | SDRAM size bit setting |

|----------------------|------------------------|

| 11011                | 256MB                  |

| 11010                | 128MB                  |

| 11001                | 64MB                   |

| 11000                | 32MB                   |

| 10111                | 16MB                   |

| 10110                | 8MB                    |

| 10101                | 4MB                    |

| 10100                | 2MB                    |

| 10011                | 1MB                    |

| 00001-10010          | Reserved               |

| 0000                 | Disable                |

NOTES:

Unsupported values

# 3.3 DRAM Interface Configuration

The hardware interface for the SDRAM is configured through registers starting at MBAR + 0x100. These registers enable selection of:

- SDR / DDR type selection

- Refresh configuration

- Row/column configuration

- Hi-Z operation

- Timing configuration

Timing parameters in configuration registers 1 and 2 must be configured based on the DRAM manufacturers data sheet. These parameters ensure that the delays between transactions are not violated by the MPC5200B. For an electrical description of these settings, please refer to Section 4, "Memory Timing Parameters".

When configuring the MPC5200B DRAM interface, perform the following 3 steps in this order:

- 1. Write the "SDelay" register

- 2. Configure timing (Section 3.3.2, "Configuration Register 1—MBAR + 0x0108 & Section 3.3.3, "Configuration Register 2—MBAR + 0x010C)

- 3. Enable and configure the DRAM control (Section 3.3.4, "Control Register—MBAR + 0x0104)

Following the above sequence ensures critical DRAM timing, and as a result, refresh parameters will be written correctly prior to the enabling of the DRAM.

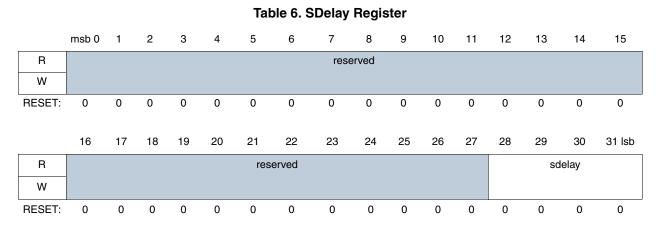

## 3.3.1 SDelay—MBAR + 0x0190

| Bit   | Name   | Description                                                |

|-------|--------|------------------------------------------------------------|

| 28:31 | sdelay | Special configuration delay–Must be written to 0x00000004. |

The SDelay should be written to a value of 0x00000004. It is required to account for changes caused by normal wafer processing parameters.

## 3.3.2 Configuration Register 1—MBAR + 0x0108

|        | msb 0 | 1    | 2      | 3  | 4  | 5  | 6     | 7  | 8    | 9     | 10      | 11 | 12   | 13  | 14     | 15     |

|--------|-------|------|--------|----|----|----|-------|----|------|-------|---------|----|------|-----|--------|--------|

| R      |       | srd2 | rwp    |    |    | SW | t2rwp |    |      | rd_la | tency   |    | Rsvd |     | act2rw | 1      |

| W      |       |      |        |    |    |    |       |    |      |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0  | 0  | 0     | 0  | 0    | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

|        |       |      |        |    |    |    |       |    |      |       |         |    |      |     |        |        |

|        | 16    | 17   | 18     | 19 | 20 | 21 | 22    | 23 | 24   | 25    | 26      | 27 | 28   | 29  | 30     | 31 lsb |

| R      | Rsvd  |      | pre2ac | t  |    | re | f2act |    | Rsvd | w     | r_laten | су |      | Res | served |        |

| W      |       |      |        |    |    |    |       |    |      |       |         |    |      |     |        |        |

| RESET: | 0     | 0    | 0      | 0  | 0  | 0  | 0     | 0  | 0    | 0     | 0       | 0  | 0    | 0   | 0      | 0      |

## Table 7. Memory Controller Configuration Register 1

| Bit | Name    | Description <sup>1</sup>                                                         |

|-----|---------|----------------------------------------------------------------------------------|

| 0:3 | srd2rwp | Single read to read/write/precharge delay, This is specified in MEM_CLK cycles.  |

| 4   | _       | Reserved                                                                         |

| 4:7 | swt2rwp | Single write to read/write/precharge delay. This is specified in MEM_CLK cycles. |

| Bit   | Name       | Description <sup>1</sup>                                                                                                                |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 8:11  | rd_latency | Read CAS latency.<br>For DDR:<br>If CL==2, write 0x6<br>If CL==2.5, write 0x7<br>For SDR:<br>If CL==2, write 0x2<br>If CL==3, write 0x3 |

|       |            | <b>Note:</b> CL=2.5 is not supported for SDR.                                                                                           |

| 12    | —          | Reserved                                                                                                                                |

| 13:15 | act2rw     | Active to read/write delay. This is specified in MEM_CLK clock cycles.                                                                  |

| 16    | _          | Reserved                                                                                                                                |

| 17:19 | pre2act    | Precharge to active or refresh delay. This is specified in MEM_CLK clock cycles.                                                        |

| 20:23 | ref2act    | Refresh to active delay. This is specified in MEM_CLK clock cycles.                                                                     |

| 24    |            | Reserved                                                                                                                                |

| 25:27 | wr_latency | Write latency. This is specified in 2xMEM_CLK clock cycles.                                                                             |

| 28:31 | _          | Reserved                                                                                                                                |

# NOTES:

In SDR mode all delays are calculated in terms of MEM\_CLK cycles. In DDR mode all delays are calculated in terms of 2xMEM\_CLK cycles.

## 3.3.3 Configuration Register 2—MBAR + 0x010C

|        | msb 0 | 1    | 2   | 3  | 4  | 5   | 6    | 7  | 8      | 9   | 10   | 11 | 12 | 13    | 14      | 15     |

|--------|-------|------|-----|----|----|-----|------|----|--------|-----|------|----|----|-------|---------|--------|

| R      |       | brd2 | ?rp |    |    | bwť | 2rwp |    |        | bro | l2wt |    |    | burst | _length | I      |

| W      |       |      |     |    |    |     |      |    |        |     |      |    |    |       |         |        |

| RESET: | 0     | 0    | 0   | 0  | 0  | 0   | 0    | 0  | 0      | 0   | 0    | 0  | 0  | 0     | 0       | 0      |

|        |       |      |     |    |    |     |      |    |        |     |      |    |    |       |         |        |

|        | 16    | 17   | 18  | 19 | 20 | 21  | 22   | 23 | 24     | 25  | 26   | 27 | 28 | 29    | 30      | 31 lsb |

| R      |       |      |     |    |    |     |      | Re | served |     |      |    |    |       |         |        |

| W      |       |      |     |    |    |     |      |    |        |     |      |    |    |       |         |        |

| RESET: | 0     | 0    | 0   | 0  | 0  | 0   | 0    | 0  | 0      | 0   | 0    | 0  | 0  | 0     | 0       | 0      |

| Table 8. Memory Controller | Configuration Register 2 |

|----------------------------|--------------------------|

|----------------------------|--------------------------|

| Bit  | Name    | Description                                                                             |

|------|---------|-----------------------------------------------------------------------------------------|

| 0:3  | brd2rp  | Burst read to read/precharge delay. This is expressed in terms of MEM_CLK clock cycles. |

| 4:7  | bwt2rwp | Burst write to read/write/precharge delay. This is expressed in terms of MEM_CLK.       |

| 8:11 | brd2wt  | Burst read to read/write/precharge delay. This is expressed in terms of MEM_CLK         |

RESET:

| Bit   | Name         | Description                                                                           |

|-------|--------------|---------------------------------------------------------------------------------------|

| 12:15 | burst_length | This value is burst length - 1. The MPC5200B only supports a burst length of 8 (0x7). |

| 16:31 | _            | Reserved                                                                              |

## 3.3.4 Control Register—MBAR + 0x0104

The 32-bit read/write control register controls specific operations and generates some SDRAM commands. This register is reset only by a power-up reset signal.

|        | msb 0       | 1    | 2    | 3          | 4  | 5    | 6   | 7           | 8    | 9              | 10      | 11 | 12       | 13           | 14           | 15     |

|--------|-------------|------|------|------------|----|------|-----|-------------|------|----------------|---------|----|----------|--------------|--------------|--------|

| R<br>W | mode<br>_en | cke  | ddr  | ref<br>_en |    | Rsvd |     | hi_<br>addr | Rsvd | drive<br>_rule |         |    | ref_inte | rval[0:5     | ]            |        |

| RESET: | 0           | 0    | 0    | 0          | 0  | 0    | 0   | 0           | 0    | 0              | 0       | 0  | 0        | 0            | 0            | 0      |

|        | 16          | 17   | 18   | 19         | 20 | 21   | 22  | 23          | 24   | 25             | 26      | 27 | 28       | 29           | 30           | 31 lsb |

| R      | Reser       | rved | mem_ | Rsvd       |    | dqs_ | _oe |             |      | F              | Reserve | b  |          |              |              | Rsvd   |

| W      |             |      | ps   |            |    |      |     |             |      |                |         |    |          | soft<br>_ref | soft<br>_pre |        |

## Table 9. Memory Controller Control Register

| Bit   | Name              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | mode_en           | <ul><li>0 Mode register locked; cannot be written.</li><li>1 Mode register enabled; can be written.</li></ul>                                                                                                                                                                                                                                                                                                                                  |

| 1     | cke               | 0 MEM_CLK_EN negated (low).<br>1 MEM_CLK_EN asserted (high).<br>cke must be set to 1 to perform normal read and write operations. Set cke to 0 to put the<br>memory in self refresh or powerdown mode.                                                                                                                                                                                                                                         |

| 2     | ddr               | 0 SDR mode<br>1 DDR mode                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3     | ref_en            | <ul><li>0 Automatic refresh disabled.</li><li>1 Automatic refresh enabled.</li></ul>                                                                                                                                                                                                                                                                                                                                                           |

| 4:6   | —                 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7     | hi_addr           | Control the translation of internal address signals to the external pins. See Table 3.                                                                                                                                                                                                                                                                                                                                                         |

| 8     | _                 | Reserved (must be written 0)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9     | drive_rule        | <ol> <li>Tri-state except to write mode: MPC5200B drives the MDQ and MDQS lines only when<br/>necessary to perform write commands.</li> <li>Drive except to read mode: MPC5200B tri-states the MDQ and MDQS lines only when<br/>necessary to perform read commands. This mode prevents unterminated memory<br/>signals from floating for extended periods; however, terminated routing is always<br/>recommended over unterminated.</li> </ol> |

| 10:15 | ref_interval[0:5] | The average periodic interval at which the controller generates refresh commands to memory; it is measured in increments of 64 x MEM_CLK period.                                                                                                                                                                                                                                                                                               |

| Bit   | Name        | Description                                                                                                                                                                                                                                                                                                                               |

|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16:17 |             | Reserved                                                                                                                                                                                                                                                                                                                                  |

| 18    | mem_ps      | Memory data port size<br>0 32-bit data bus<br>1 16-bit data bus                                                                                                                                                                                                                                                                           |

| 19    |             | Reserved                                                                                                                                                                                                                                                                                                                                  |

| 20:23 | dqs_oe[3:0] | <ul> <li>Each bit individually controls one MEM_MDQS output.</li> <li>The corresponding MEM_MDQS pin is <i>never</i> driven, regardless of memory operation and drive_rule. Always set to 0000 for SDR.</li> <li>The corresponding MEM_MDQS pin <i>can</i> be driven, depending on memory operations and drive_rule. DDR only.</li> </ul> |

| 24:28 | _           | Reserved                                                                                                                                                                                                                                                                                                                                  |

| 29    | soft_ref    | <ul> <li>0 No operation.</li> <li>1 Generate a non-periodic Auto Refresh command as soon as possible.</li> <li>This is a write-only bit; always returns 0 on a read. A software requested refresh is completely independent of the periodic refresh interval counter. Software refresh is only possible when mode_en==1.</li> </ul>       |

| 30    | soft_pre    | <ul> <li>0 No operation</li> <li>1 Generate a Precharge All command as soon as possible.</li> <li>This is a write-only bit; always returns 0 on a read. Software precharge is only possible when mode_en==1.</li> </ul>                                                                                                                   |

| 31    |             | Reserved                                                                                                                                                                                                                                                                                                                                  |

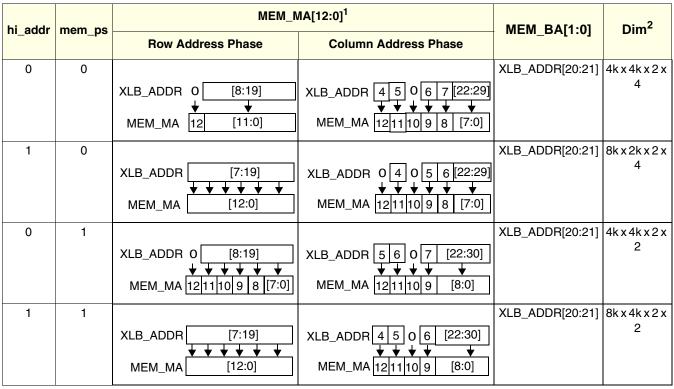

## 3.3.5 Address Translation

In order for the MPC5200B to provide a flexible interface for a variety of memories, the registers provide two configuration settings for address, row, and column configurations.

Table 10 indicates how the internal XL bus address bits are translated internally to support sdram devices on the external electrical interface. This address translation is controlled through programming the hi\_addr and mem\_ps bits of the control register.

## Table 10. Address Translation

NOTES:

<sup>1</sup> Fields marked with a '0' are always driven low.

<sup>2</sup> ROW x COL x BANK x WORDS

# 3.4 Vendor Specific Configuration

In the final stage of configuration the developer should configure the vendor specific settings in the DRAM mode registers. This may include programming for burst length, CAS settings, precharge during initialization, and locking of clocks. This is done by using the mode register as described in Section 3.4.1, "Mode Command Generation".

## 3.4.1 Mode Command Generation

Mode commands may be generated by the DRAM controller through use of the mode register. When written, this register will generate a LMR/LEMR command (see Table 2). The data driven onto the bit shown in the register are then latched into the mode register of the external device to program memory specific settings without altering the contents of memory. Some settings which may be available by the manufacturer are as follows:

- Burst length

- CAS latency

- Burst type (sequential or interleaved)

- Clock functions (lock, etc)

See manufacturer's data sheet for further details.

**Memory Timing Parameters**

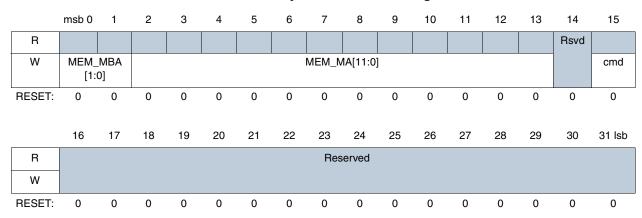

## 3.4.1.1 Mode Register—MBAR + 0x0100

Each time the 32-bit write-only mode register (mode[0:31]) is written (and cmd is set to 1), the controller generates command over the sdram interface.

## Table 11. Memory Controller Mode Register

| Bit   | Name             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0:1   | MEM_MBA<br>[1:0] | See the SDRAM data sheet. Select either the memory device mode register or the memory device extended mode register, if present.                                                                                                                                                                                                                                                                                                                               |

| 2:13  | MEM_MA[11:0]     | <ul> <li>See the SDRAM data sheet. MPC5200B supports the following:</li> <li>Read CAS latency, SDR: 2, 3</li> <li>Read CAS latency, DDR: 2, 2.5</li> <li>Burst type: Sequential only</li> <li>Burst length: 8 only</li> <li>Other fields: As appropriate</li> <li>Specific bit allocation can vary from device to device. All devices in all CS spaces must have compatible format(s) because all are written at the same time with the same value.</li> </ul> |

| 14    | —                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15    | cmd              | <ol> <li>Generate a (extended) mode register set memory command. Apply to all CS at once.</li> <li>Do not generate any memory command.</li> </ol>                                                                                                                                                                                                                                                                                                              |

| 16:31 | _                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

To ensure that commands are generated properly care should be taken to ensure that signals are connected correctly.

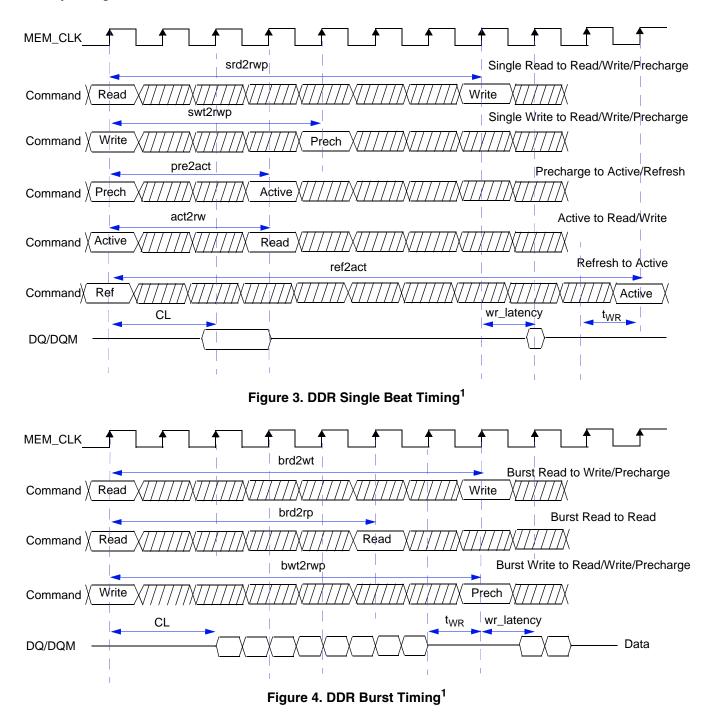

# 4 Memory Timing Parameters<sup>1</sup>

Memory timing parameters are controlled through settings found in the memory controller register map. These are detailed in Section 3, "Software Configuration."

<sup>1.</sup> For signals listed as 'command,' refer to Section 2.2.2.1, "Supported DRAM Commands" for electrical description.

**Memory Timing Parameters**

<sup>1.</sup> Timings values are relative to a specific command sequence. Care must be taken to select the appropriate command from the listed sequence.

## 5.1 Example Micron Initialization

This example will use a MT46V16M16 memory available from Micron. The initialization description presented in Section 5.1.1, "Micron DDR Initialization Sequence," is taken verbatim from the Micron data sheet. This is revised in Section 5.1.2, "MPC5200B Initialization Sequence for Micron DDR Memories," with details on how each step is accomplished using the MPC5200B. The next section provides pseudocode for initializing the Micron device.

## 5.1.1 Micron DDR Initialization Sequence

Per the Micron data sheet. To ensure device operation the DRAM must be initialized as described below:

- 1. Simultaneously apply power to VDD and VDDQ.

- 2. Apply VREF and then VTT power.

- 3. Assert and hold CKE at a LVCMOS logic low.

- 4. Provide stable CLOCK signals.

- 5. Wait at least  $200 \ \mu s$ .

- 6. Bring CKE high, and provide at least one NOP or DESELECT command. At this point, the CKE input changes from a LVCMOS input to a SSTL2 input only and will remain a SSTL\_2 input unless a power cycle occurs.

- 7. Perform a PRECHARGE ALL command.

- 8. Wait at least tRP time. During this time, NOPs or DESELECT commands must be given.

- 9. Using the LMR command, program the extended mode register (E0 = 0 to enable the DLL and E1 = 0 for normal drive, or E1 = 1 for reduced drive. E2 through En must be set to 0, where n = most significant bit).

- 10. Wait at least tMRD time. Only NOPs or DESELECT commands are allowed.

- 11. Use the LMR command program and the mode register to set operating parameters and to reset the DLL. **Note:** At least 200 clock cycles are required between a DLL reset and any READ command.

- 12. Wait at least tMRD time. Only NOPs or DESELECT commands are allowed.

- 13. Issue a PRECHARGE ALL command.

- 14. Wait at least tRP time. Only NOPs or DESELECT commands are allowed.

- 15. Issue an AUTO REFRESH command. Note: This may be moved prior to step 13.

- 16. Wait at least tRFC time. Only NOPs or DESELECT commands are allowed.

- 17. Issue an AUTO REFRESH command. Note: This may be moved prior to step 13.

- 18. Wait at least tRFC time. Only NOPs or DESELECT commands are allowed.

- 19. Although not required by the Micron device, JEDEC requires a LMR command to clear the DLL bit (set M8 = 0). If an LMR command is issued, the same operating parameters should be utilized as in step 11.

- 20. Wait at least tMRD time. Only NOPs or DESELECT commands are allowed.

21. At this point, the DRAM is ready for any valid command. **Note:** 200 clock cycles are required between step 11 (DLL Reset) and any READ command. VDD and VDDQ Ramp Apply VREF and VTT CKE must be LVCMOS Low

## 5.1.2 MPC5200B Initialization Sequence for Micron DDR Memories

Translating the Micron data sheet into actions performed on the MPC5200B, the following steps are obtained:

- 1. Power-up the system. (Meet the requirements specified in the MPC5200B User's Guide.)

- 2. Apply VREF, and then apply the VTT power.

- 3. CKE is automatically held at logic low until the DRAM controller is enabled.

- 4. mem\_clock is automatically provided at reset.

- 5. Wait at least 200µs. MPC5200B initialization is included in this time.

Initialize GPIOs (See Section 3.1, "GPIO Configuration.")

Initialize Chip Selects (See Section 3.2, "Memory Map And Chip Select Configuration.") Initialize DRAM interface (See Section 3.3, "DRAM Interface Configuration.")

- 6. CKE will automatically be brought high when SDRAM is enabled. An NOP command will be issued by the controller.

- 7. Perform a PRECHARGE ALL command by writing the soft\_pre bit of the SDRAM control register. (See Section 3.3.4, "Control Register—MBAR + 0x0104.)

- 8. Wait at least tRP<sup>1</sup> time. During this time, NOPs or DESELECT commands must be given. By default, the MPC5200B will issue these commands. By waiting the appropriate time period, this requirement will be satisfied.

- 9. Enable the DRAM DLL by writing the appropriate value to the mode register.<sup>2</sup>

The LMR command enabling the DLL is programmed by writing a value of 0x40010000 to the mode register. (See Section 3.4.1, "Mode Command Generation.")

- 10. Wait at least  $tMRD^1$  time.

- 11. Reset the DLL, and program operational mode parameters by writing a value of 0x02C70000<sup>1</sup> mode register. (See Section 3.4.1, "Mode Command Generation.")

DLL reset

2.5 CAS latency

Sequential Burst

8 word burst length

- 12. Wait at least  $tMRD^1$ .

- 13. Perform a PRECHARGE ALL command by writing the soft\_pre bit of the SDRAM control register. (See Section 3.3.4, "Control Register—MBAR + 0x0104.")

- 14. Wait at least  $tRP^1$ .

<sup>1.</sup> See manufacturers data sheet

<sup>2.</sup> The mode register cannot be written unless bit 0 of the Control register (Section 3.3.4, "Control Register—MBAR + 0x0104) is set.

- 15. Perform a AUTO REF by writing the soft\_ref bit of the SDRAM control register. (See Section 3.3.4, "Control Register—MBAR + 0x0104.")

- 16. Wait at least tRFC time<sup>1</sup>.

- 17. Perform a AUTO REF by writing the soft\_ref bit of the SDRAM control register. (See Section 3.3.4, "Control Register—MBAR + 0x0104.")

- 18. Wait at least  $tRFC^{1}$ .

- 19. Although not required by the Micron device, JEDEC requires an LMR command to clear the DLL bit (set M8 = 0) by writing a value of  $0x00C70000^{1}$  to the mode register. (See Section 3.4.1, "Mode Command Generation.")

- 20. Wait at least  $tMRD^1$  time.

- 21. At this point, the DRAM is ready for any valid command. **Note:** 200 clock cycles are required between step 11 (DLL Reset) and any READ command. A delay may be added at this point to ensure that this constraint is met.

## 5.1.3 Example Pseudo Code

This code assumes MBAR has been already set to 0x10000000. In actual implementation, it will be more efficient for the boot loader to initialize the SDRAM using assembly language since a stack (required by C) is typically not available before SDRAM configuration.

## 5.1.3.1 Main initialization Sequence

```

start:

```

- /\*

- \* 1. Configure GPIOs

- \* Some pins may have alternate functionality (DRAM1)

- \* therefore we will configure PIN muxing before

- \* prior to memory map configuration

- \*/

```

bl gpio_pin_init

```

/\*

\* 2. Configure Clocks (not required for DRAM configuration)

\*/

clock\_init

/\*

\* 3. Configure DRAM space

\*/

## MPC5200B SDRAM Initialization and Configuration, Rev. 0

bl

```

dram_init( );

/* Initializaiton complete */

```

## 5.1.3.2 GPIO initialization

/\* GPIO offsets \*/

#define REL\_GPIO\_PORT\_CFG 0xB00

#define REL\_GPIO\_PORT\_ENABLES 0xB04

#define REL\_GPIO\_PORT\_IO 0xB0C

/\* Register Values \*/

#define GPIO\_PORT\_CONFIG\_INIT

0x81000004

gpio\_pin\_init:

/\* Make sure r4 contains mbar \*/

mfspr r4,SPR\_MBAR

/\* Configure General Purpose Pins \*/

lis r3,(GPIO\_PORT\_CONFIG\_INIT)@h

ori r3, r3, (GPIO\_PORT\_CONFIG\_INIT)@l

stw r3, REL\_GPIO\_PORT\_CFG(r4)

..... /\* Perform Intialization for board here \*/

blr

## 5.1.3.3 DRAM Initialization

```

/* SDRAM Extended Mode Write */

#define SDRAM_MODE_WR_M(extended_cmd, cmd)\

( ( extended_cmd << 17 ) | \

( cmd ))</pre>

```

```

Example Initialization Sequence

```

```

* Relative Register Definitions

* These are needed because the definitions in the standard includes

* are absolute.

#define REL_SDRAM0_BASE 0x34

#define REL_SDRAM1_BASE 0x38

#define REL_SDRAM_MODE 0x100

#define REL_SDRAM_CTRL 0x104

#define REL_SDRAM_CONFIG1 0x108

#define REL_SDRAM_CONFIG2 0x10C

#define REL_SDRAM_SDELAY 0x190

/* vendor specific macros for mode register assignment */

#define MICRON_MODE_M(op_mode, cas, burst_type, burst_len, cmd)\

( ( 0<<30 ) | \

( op_mode << 25 ) | \

( cas << 22) | \

( burst_type << 21 ) | \setminus

( burst_len << 18) | \

( cmd << 16) )

#define MICRON_EMODE_M(op_mode, ds, dll, cmd)\

( ( 1<<30 ) | \

( op_mode << 20 ) | \

( ds << 19 ) | \

( dll<< 18 ) | \

( cmd << 16 ) )

/* Register Values */

#define IPBI_SDRAM_CS0_CFG_INIT 0x000001A

#define IPBI_SDRAM_CS1_CFG_INIT 0x0000000

#define CFG_SDRAM_CTRL 0x715F0F00

```

```

#define CFG_SDRAM_CFG1 0x73722930

#define CFG_SDRAM_CFG2 0x47770000

#define CFG_SDRAM_SDELAY 0x0x0000004

#define DRAM_PROG_DELAY 200

dram_init:

/* Make sure r4 contains mbar */

mfspr r4,SPR_MBAR

/*

*

This section programs the operational DRAM parameters

*

(DRAM Size and address range)

*/

/* DRAM0 CS Configuration */

lis r3, (IPBI_SDRAM_CS0_CFG_INIT)@h

ori r3, r3, (IPBI_SDRAM_CS0_CFG_INIT)@l

stw r3, REL_SDRAM0_BASE(r4)

/* DRAM1 CS Configuration */

lis r3, (IPBI_SDRAM_CS1_CFG_INIT)@h

ori r3, r3, (IPBI_SDRAM_CS1_CFG_INIT)@l

stw r3, REL_SDRAM1_BASE(r4)

/* DRAM CTRL Configuration - Unlock the register */

SETBITS(REL_SDRAM_CTRL, BITS_DRAM_CTRL_UNLOCK)

/* DRAM CFG1 Configuration */

lis r3, (CFG_SDRAM_CFG1)@h

ori r3, r3, (CFG_SDRAM_CFG1)@l

stw r3, REL_SDRAM_CONFIG1(r4)

/* DRAM CFG2 Configuration */

lis r3, (CFG_SDRAM_CFG2)@h

```

```

ori r3, r3, (CFG_SDRAM_CFG2)@l

stw r3, REL_SDRAM_CONFIG2(r4)

/* DRAM CTRL Configuration - Cd

lis r3, ( CFG_SDRAM_CTRL )@h

ori r3, r3, ( CFG_SDRAM_CTRL )

stw r3, REL_SDRAM_CTRL(r4)

/* DRAM TAP Delay Initial Sett.

lis r3, (CFG_SDRAM_SDELAY)@h

ori r3, r3, (CFG_SDRAM_SDELAY)

```

```

stw r3, REL_SDRAM_CONFIG2(r4)

/* DRAM CTRL Configuration - Configure the register */

lis r3, ( CFG_SDRAM_CTRL )@h

ori r3, r3, ( CFG_SDRAM_CTRL )@l

stw r3, REL_SDRAM_CTRL(r4)

/* DRAM TAP Delay Initial Setting */

lis r3, (CFG_SDRAM_SDELAY)@h

ori r3, r3, (CFG_SDRAM_SDELAY)@l

stw r3, REL_SDRAM_SDELAY(r4)

/*

* Start Vendor Configuration here

* This section programs DRAM device through the 'mode'

* register (see manufacturers data sheet).

*/

/* Assume clocks have been stable for 200us */

/* precharge all banks */

SETBITS(REL_SDRAM_CTRL, BITS_DRAM_CTRL_SOFT_PRE)

/* DRAM Vendor Specific Configuration

* - Enable DLL

* - Use Normal Drive strength

* MICRON_EMODE_M(op_mode, ds, dll, cmd)

*/

lis r3, MICRON_EMODE_M(0, 0, 1, 1)@h

ori r3, r3, MICRON_EMODE_M(0, 0, 1, 1)@l

stw r3, REL_SDRAM_MODE(r4)

/* DRAM Vendor Configuration

```

```

* - Burst Size = 8

```

```

NP

```

```

* - CAS 2.5

* - Sequential mode

* - Reset DLL

* MICRON_MODE_M(op_mode, cas, burst_type, burst_len, cmd)

*/

lis r3, MICRON_MODE_M(2, 6, 0, 3, 1)@h

ori r3, r3, MICRON_MODE_M(2, 6, 0, 3, 1)@h

stw r3, REL_SDRAM_MODE(r4)

/* Wait for DLL to lock */

DELAY( dram_delay, DRAM_PROG_DELAY )

/* precharge all banks */

SETBITS (REL_SDRAM_CTRL, BITS_DRAM_CTRL_SOFT_PRE)

/* DRAM - Perform a manual refresh */

SETBITS ( REL_SDRAM_CTRL, BITS_DRAM_CTRL_SOFT_REF )

/* DRAM Vendor Configuration

* - Burst Size = 8

* - CAS 2.5

* - Sequential mode

* - Reset DLL

* MICRON_MODE_M(op_mode, cas, burst_type, burst_len, cmd)

*/

lis r3, MICRON_MODE_M(0, 6, 0, 3, 1)@h

ori r3, r3, MICRON_MODE_M(0, 6, 0, 3, 1)@h

stw r3, REL_SDRAM_MODE(r4)

/* DRAM Configuration Complete*/

```

blr

# Appendix A Micron MT46V16MT16 Programming Guide

This section outlines the mode and extended mode registers in the Micron MT46V16MT16 DDR device. The extended mode registers have been mapped from the electrical signals described by the Micron data sheet to the mode register described in Section 2.2.2, "DRAM Command Generation" & Section 3.4.1, "Mode Command Generation".

|   | msb 0 | 1  | 2  | 3   | 4        | 5     | 6  | 7  | 8   | 9  | 10            | 11 | 12       | 13  | 14   | 15     |

|---|-------|----|----|-----|----------|-------|----|----|-----|----|---------------|----|----------|-----|------|--------|

| R |       |    |    |     |          |       |    |    |     |    |               |    |          |     | Rsvd |        |

| W | 0     | 0  |    | Ope | rating N | /lode |    |    | CAS |    | Burst<br>Type | Βι | irst Len | gth |      | cmd    |

|   | 16    | 17 | 18 | 19  | 20       | 21    | 22 | 23 | 24  | 25 | 26            | 27 | 28       | 29  | 30   | 31 lsb |

## Table A1. Normal Mode Programming - MBAR + 0x100

| R | Reserved |

|---|----------|

| W |          |

|   |          |

| Bit   | Name           | Description                                                                                                                                         |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:6   | operating mode | 00000 Normal mode<br>00010 Reset DLL                                                                                                                |

| 7:9   | CAS            | CAS latency<br>000 Reserved<br>001 Reserved<br>010 2<br>011 Reserved<br>100 Reserved<br>101 Reserved<br>110 2.5<br>111 Reserved                     |

| 10    | burst type     | 0 Sequential<br>1 Interleaved                                                                                                                       |

| 11:13 | burst length   | Burst length<br>000 Reserved<br>001 2<br>010 4<br>011 8<br>1xx Reserved                                                                             |

| 15    | cmd            | <ol> <li>Generate a (extended) mode register set memory command. Applied to all CS at once.</li> <li>Do not generate any memory command.</li> </ol> |

| 16:31 | _              | Reserved                                                                                                                                            |

|   | msb 0 | 1  | 2  | 3  | 4  | 5  | 6        | 7       | 8      | 9  | 10 | 11 | 12 | 13  | 14   | 15     |

|---|-------|----|----|----|----|----|----------|---------|--------|----|----|----|----|-----|------|--------|

| R |       |    |    |    |    |    |          |         |        |    |    |    |    |     | Rsvd |        |

| W | 0     | 1  |    |    |    |    | Operatir | ng Mode | e      |    |    |    | DS | DLL |      | cmd    |

|   |       |    |    |    |    |    |          |         |        |    |    |    |    |     |      |        |

|   | 16    | 17 | 18 | 19 | 20 | 21 | 22       | 23      | 24     | 25 | 26 | 27 | 28 | 29  | 30   | 31 lsb |

| R |       |    |    |    |    |    |          | Res     | served |    |    |    |    |     |      |        |

| W |       |    |    |    |    |    |          |         |        |    |    |    |    |     |      |        |

## Table A2. Extended Mode Programming - MBAR + 0x100

| Bit   | Name           | Description                                                                                                                                         |

|-------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:11  | operating mode | 00000000 Valid                                                                                                                                      |

| 12    | DS             | Drive Strength<br>0 Normal<br>1 Reduced                                                                                                             |

| 13    | burst type     | DLL Enable<br>0 Disabled<br>1 Enabled                                                                                                               |

| 15    | cmd            | <ol> <li>Generate a (extended) mode register set memory command. Applied to all CS at once.</li> <li>Do not generate any memory command.</li> </ol> |

| 16:31 | _              | Reserved                                                                                                                                            |

\_\_\_\_\_

This page intentionally left blank.

#### How to Reach Us:

Home Page: www.freescale.com

#### E-mail: support@freescale.com

#### .....

USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

AN3221 Rev. 0, 01/2006 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The described product is a PowerPC microprocessor core. The PowerPC name is a trademark of IBM Corp. and is used under license. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006. All rights reserved.