Freescale Semiconductor

**Application Note**

AN3555 Rev. 0, 11/2007

# Investigating XGATE Software Errors

# XGATEV2 (S12X) Software Error Debugging Aid

by: Dirk Heisswolf MCD Design Munich, Germany

## 1 Introduction

The XGATE peripheral coprocessor includes a safety feature called Software Error Detection. The Software Error Detection feature lets the XGATE detect conditions which should not occur during program execution. The detection of these conditions indicate that there are problems in the application code.

Whenever XGATE detects a Software Error Condition, it ceases program execution immediately and flags an interrupt to the CPU12X to perform corrective action. In a typical application this corrective action simply consists of initialization and system restart. However during the development and debug phase of application code it is desirable to know the exact cause of XGATE Software Errors.

This document helps you investigate XGATE Software Errors on S12X devices<sup>1</sup>. The S12XE (and S12XF)

#### Contents

| 1  | Intro  | duction                                  |

|----|--------|------------------------------------------|

| 2  | The    | Software Error Detection Feature         |

|    | 2.1    | Software Error Conditions                |

|    | 2.2    | Software Error Interrupts 4              |

|    | 2.3    | Software Error State                     |

| 3  | Deb    | ugging Goal                              |

| 4  | Inve   | stigating Software Errors5               |

|    | 4.1    | Sources of Information                   |

|    | 4.2    | Memory Protection                        |

|    | 4.3    | Observable Conditions 8                  |

|    | 4.4    | Software Error Scenarios 10              |

|    | 4.5    | Finding the Cause of a Software Error 20 |

|    | 4.6    | Examples 22                              |

| 5  | Refe   | erences                                  |

| Ар | oendix | A 30                                     |

|    | A.1    | List of S12X MCUs 30                     |

© Freescale Semiconductor, Inc., 2007. All rights reserved.

<sup>1.</sup> Appendix A.1 provides a list of relevant S12X MCUs

product family is discussed in part II of this document series.

#### CAUTION

This application note describes the behavior of the XGATE as it is shipped on S12X devices as of today. Some descriptions show behavior which is not specified in the reference manual and may be invalid on future implementations of the XGATE. The intent of this document is to provide helpful information for debugging application code. It is not to be understood as an addition to the XGATE specification.

# 2 The Software Error Detection Feature

Software Error Detection is a safety feature of the XGATE. It provides a mechanism to stop program execution and call for help, whenever the XGATE is instructed to do something illegal.

Illegal actions are defined by a set of Software Error Conditions (Section 2.1). These Software Error Conditions consist of features which are not supported by the MCU's architecture and violations of the MCU's memory protection scheme. Software Error Conditions should never occur in an application. They are considered to be an indicator for a software problem.

Whenever a Software Error Condition is detected, XGATE ceases program execution and performs two distinct actions: It flags an interrupt to the CPU12X (Section 2.2) and enters a special Software Error State (Section 2.3).

To minimize the harm that erroneous XGATE application code can do to the system, the XGATE ceases code execution in the instant that the problem is detected. It doesn't finish the execution of the current instruction.

While stopping program execution in the middle of an instruction execution is desirable from a safety viewpoint, it does add some complexity when it comes to the debugging of Software Errors.

Instructions are stopped before their specified operation has been completed. Which part of the operation has been processed and which not depends on the implementation of the XGATE module.

At present there are two revisions available: XGATEV2 which is integrated in most in S12X devices and XGATEV3 (enhanced XGATE) which is built into S12XE MCUs. These versions have slightly different implementations of the Software Error Detection feature. This document discusses the behavior of Software Errors, as they are implemented on XGATEV2.

# 2.1 Software Error Conditions

Not every instruction given to the XGATE can or should be executed. Instructions which invoke an unimplemented hardware feature cannot be processed with a meaningful outcome. Instructions that violate the memory protection scheme must be prevented to preserve data consistency. Section 2.1.1 and Section 2.1.2 list the Software Error Conditions for these two categories. A compact summary of all conditions is given in Figure 2.

#### 2.1.1 Invocation of Unsupported Features

There are four Software Error Conditions that indicate the usage of an unsupported hardware feature:

• Undefined Opcodes - The XGATE's instruction set leaves a number of opcodes undefined. Their execution results in Software Errors. Figure 1 lists all illegal XGATE instructions. This list may decrease on later releases of the XGATE, as new features are added.

| Functionality        | 15                       | 14 | 13 | 12                   | 11 | 10         | 9                | 8          | 7          | 6      | 5   | 4 | 3          | 2     | 1      | 0    |

|----------------------|--------------------------|----|----|----------------------|----|------------|------------------|------------|------------|--------|-----|---|------------|-------|--------|------|

| Illegal Instructions |                          |    |    | I                    |    |            |                  |            | 1          |        |     |   |            |       |        |      |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 0          | 0      | 0   | 0 | 0          | 0     | 0      | 1    |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 0          | 0      | 0   | 0 | 0          | 0     | 1      | dc   |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 0          | 0      | 0   | 0 | 0          | 1     | don't  | care |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 0          | 0      | 0   | 0 | 1          | do    | n't ca | are  |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 0          | 0      | 0   | 1 |            | don't | care   |      |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | don't care 0 0 1 |            | don't care |        |     |   |            |       |        |      |

|                      | 0 0 0 0 0 don't care 0 1 |    |    |                      |    | don't care |                  |            |            |        |     |   |            |       |        |      |

| Undefined opcode     | 0                        | 0  | 0  | 0 0 0 don't care 1 0 |    |            |                  | don't care |            |        |     |   |            |       |        |      |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 1          | 1      | 0   |   | don't care |       |        |      |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 1          | 1      | 1   | 0 |            | don't | care   |      |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 1          | 1      | 1   | 1 | 1          | 0     | 1      | 1    |

|                      | 0                        | 0  | 0  | 0                    | 0  | do         | n't ca           | ire        | 1          | 1      | 1   | 1 | 1          | 1     | don't  | care |

|                      | 0                        | 0  | 0  | 0                    | 0  | 1          | don't            | care       | 0          | 0      | 0   | 0 | 0          | 0     | 0      | 0    |

|                      | 0                        | 0  | 0  | 0                    | 1  |            |                  | don't      | care       |        |     | 0 | 0          | do    | n't ca | are  |

|                      | 0                        | 0  | 0  | 0                    | 1  |            |                  | do         | n't ca     | are    |     |   | 1          | 0     | 0      | 0    |

|                      | 0                        | 0  | 0  | 1                    | 0  |            |                  |            | do         | n't ca | ire |   |            |       | 0      | 1    |

#### Figure 1. Illegal Instructions

• Misaligned word accesses (16-bit accesses to an odd address)

The S12X architecture does not allow the XGATE to perform is aligned word accesses to its memories. So any of the following three accesses results in a Software Error:

- Opcode fetches from an odd address

- 16 Bit data read accesses from an odd address

- 16 Bit data write accesses to an odd address

- Unimplemented address locations

On S12X devices it is possible to hide the Flash memory if the MCU is secured and in expanded mode. Accesses to these unimplemented address locations trigger a Software Error.

• Write accesses to Flash space

The Flash memory on S12X devices can not be programmed by the XGATE through write access to the address space of the nonvolatile memory. As general application code would never try to write to these memory locations; a Software Error is issued if the write attempt takes place.

### 2.1.2 Violations of the Memory Protection Scheme

The second category of Software Error Conditions contains artificial restrictions for memory access. Their purpose is to minimize the damage that faulty application code can cause. Two types of memory protection are implemented on S12X products.

Code execution from register space On every S12X product family the XGATE is not allowed to execute code from the register space.

This serves two purposes. It is a safety feature. As code execution from register space is generally

not a good practice; it can be used as an indicator for runaway code. It is also a security feature

used to prevent intruders from accessing system resources of a secured MCU.

Vector fetches of the XGATEV2 are treated as opcode fetches. Fetching a vector from register

space results in a Software Error.

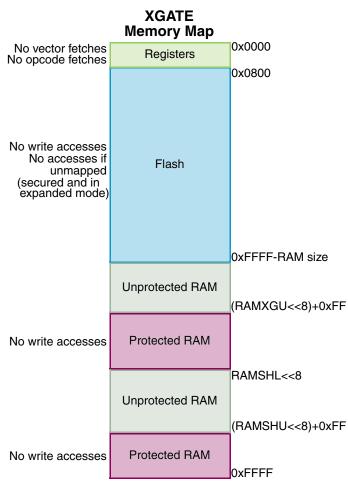

User defined memory protection -S12X MCUs offer a simple RAM write protection scheme. The RAM is divided into three sections: A CPU12X section, an XGATE section, and a shared section. The borders between these sections are configurable (Figure 4). Whenever the XGATE tries to write to the S12X section, a Software Error is triggered.

|    | Softw                     | are Error Condition                |  |  |  |  |  |

|----|---------------------------|------------------------------------|--|--|--|--|--|

| 1  | Execution of an unit      | mplemented opcode                  |  |  |  |  |  |

| 2  | Vector fetch<br>(VF)      | from an unimplemented address      |  |  |  |  |  |

| 3  | (•••)                     | from register space                |  |  |  |  |  |

| 4  | Opcode fetch<br>(OF)      | from an odd address                |  |  |  |  |  |

| 5  |                           | from an unimplemented address      |  |  |  |  |  |

| 6  |                           | from register space                |  |  |  |  |  |

| 7  | Byte read access<br>(BR)  | from an unimplemented address      |  |  |  |  |  |

| 8  | Word read access (WR)     | to an odd address                  |  |  |  |  |  |

| 9  |                           | to an unimplemented address        |  |  |  |  |  |

| 10 | Byte write access<br>(BW) | from an unimplemented address      |  |  |  |  |  |

| 11 | (511)                     | to Flash memory                    |  |  |  |  |  |

| 12 |                           | causing a RAM protection violation |  |  |  |  |  |

| 14 | Word write access (WW)    | to an odd address                  |  |  |  |  |  |

| 15 | ()                        | from an unimplemented address      |  |  |  |  |  |

| 16 |                           | to Flash memory                    |  |  |  |  |  |

| 17 |                           | causing a RAM protection violation |  |  |  |  |  |

Figure 2. Summary of Software Error Conditions

# 2.2 Software Error Interrupts

As soon as the XGATE detects a Software Error Condition it sets the Software Error Interrupt Flag (XGSWEIF) that triggers a maskable<sup>1</sup> interrupt to the CPU12X. This interrupt request persists until the XGSWEIF flag is cleared in an interrupt service routine.

<sup>1.</sup> Maskable via the I-bit in the CPU12X Condition Code Register.

## 2.3 Software Error State

If the XGATE ceases code execution due to a Software Error, it enters a Software Error State. This state gives the application code a chance to log and fix the problem (typically by reinitializing the application) before resuming normal operation. The XGATE stays in the Software Error State until the XGSWEIF flag is cleared. Leaving the Software Error State always terminates the current thread.

The investigation of XGATE Software Errors as it is described in this document (see Section 4) must be performed while the XGATE remains in the Software Error State.

# 3 Debugging Goal

To understand the cause of a Software Error the following information is pertinent:

- Which channel was active when the problem occurred?

- Which instruction was executed or which vector was fetched?

- In which cycle of the instruction or vector fetch did the error occur?

- Which Software Error Condition was triggered?

- What was the state of the RISC core's registers, when the problem occurred?

Unfortunately the XGATE doesn't have any means to provide this information directly. It does however provide enough information to help track down the cause of the problem.

There are only a limited number of scenarios that lead to a Software Error. Each one of these scenarios leaves a characteristic signature inside the XGATE's registers after the Software Error has occurred.

To investigate the cause of a Software Error these signatures are broken down into a set of observable conditions. These conditions must be checked one after the other. Software Error scenarios can be excluded from further investigation if an associated observable condition is not fulfilled. The elimination process is complete if only one of the potential Software Error scenarios remains. The desired debug information can be extracted as soon as the Software Error scenario is determined.

The XGATE typically provides enough information to conclude the prehistory of the error. However there are a few cases that leave two possible scenarios that could have led to the problem. In these cases further investigation based on the context of the application code is required.

# 4 Investigating Software Errors

The following sections explain the process of finding the cause of an XGATE Software Error in detail.

## 4.1 Sources of Information

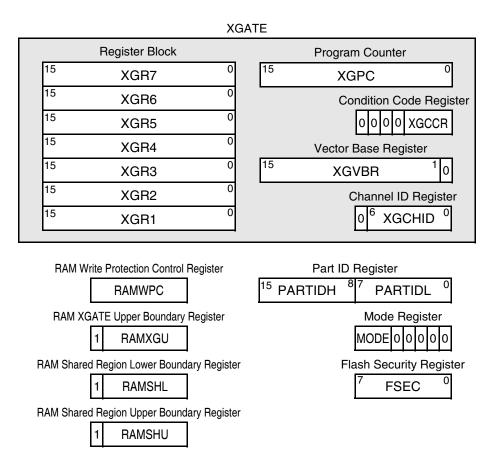

Information required for debugging XGATE Software Errors on S12X devices can be derived from the 18 registers shown in Figure 3.

Figure 3. Sources of Information for Debugging S12X Devices

These registers are:

- The XGATE's status and debug registers (XGCHID, XGVBR, CGPC, XGCCR, XGR7..XGR1) They provide information about the state of the XGATE's RISC core and the current instruction.

- The MCU's Part ID Register (PARTIDH, PARTIDL) This register is used to determine which implementation of the XGATE is on the device

- The S12XMMC's RAM protection registers (RAMWPC, RAMXGU, RAMSHL, RAMSHU) These registers determine the protected memory ranges

- The Mode register and the Flash Security register (MODE, FSEC) These registers are necessary to find out the unmapped areas within the XGATE's memory map

As some of the registers can be used to obtain addresses of relevant memory locations, it is important that the memory content remains unchanged for the investigation of Software Errors.

## 4.2 Memory Protection

As mentioned in Section 2.1, there are two categories of Software Error Condition. The first one, "Invocation of Unsupported Features" (see Section 2.1.1), includes access to unmapped addresses in the memory map. On S12X devices there is only one scenario in which an address range inside the XGATE's memory map is unmapped. If the MCU is in expanded mode while it is secured; the Flash is disabled for security reasons. In this case, access to the Flash range would result in Software Error Conditions 2, 5, 7, 9, 10, or 15 (see Figure 2).

The other category of Software Error Conditions are "Violations of the Memory Protection Scheme" (see Section 2.1.2). In addition to the general restriction, that opcode and vector fetches from register space are forbidden, S12X devices offer a configurable RAM write protection scheme. There are three registers (RAMXGU, RAMSHL, and RAMSHU) to set the boundaries of two write protected address ranges. Write accesses to these areas trigger Software Error Conditions 12 or 17 (see Figure 2).

Figure 4 illustrates the full memory protection scheme of an S12X device.

Figure 4. XGATE Memory Protection on S12X Devices

## 4.3 **Observable Conditions**

When investigating XGATE Software Errors, there is a set of significant conditions that can be directly checked on the source registers (see Section 4.1) and the current content of the MCU's memories. For every cause of an Software Error, a certain subset of these observable conditions must be true. If one condition in this subset can be proven false, then the associated cause can be excluded from further examination.

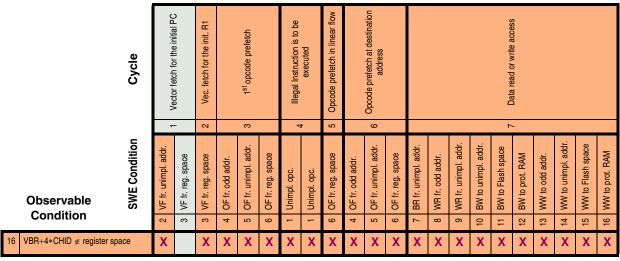

On S12X devices there are 31 observable conditions that are relevant for the investigation of Software Errors. These conditions are listed in Figure 5.

|    | Mnemonic                        | Description                                                                                          | Details                                                                                                                           |                                  |

|----|---------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1  | PC = 0xFFFE                     | The program counter is set to the value 0xFFFE                                                       | XGPC = 0xFFFE                                                                                                                     |                                  |

| 2  | PC & 1 = 1                      | The program counter contains an odd address                                                          | XGPC[0] = 1                                                                                                                       |                                  |

| 3  | PC & 1 = 0                      | The program counter contains an even address                                                         | XGPC[0] = 0                                                                                                                       |                                  |

| 4  | $PC+2 \in register space$       | The incremented program counter is located in the register space                                     | (XGPC = 0xFFFE)<br>(XGPC < 0x07FE)                                                                                                | II                               |

| 5  | PC ∉ register space             | The program counter is not located in the register space                                             | (XGPC Š≥ 0x0800)                                                                                                                  |                                  |

| 6  | $PC+2 \in flash space$          | The incremented program counter is located in the flash space                                        | (XGPC ≥ 0x07FE)<br>(XGPC Š≤ 0xFFFD-RAM size)                                                                                      | &&                               |

| 7  | $PC \notin secured flash space$ | The program counter is not located in the secured flash space                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                              |                                  |

| 8  | PC+2 = [VBR+4*CHID]             | The 1 <sup>st</sup> word of the channel vector contains the value of the incremented program counter | XGPC = [XGVBR+4*XGCHID] - 2                                                                                                       |                                  |

| 9  | CCR = 0x0                       | The condition code register is cleared                                                               | XGCCR = 0x00                                                                                                                      |                                  |

| 10 | R1 = 0x0000                     | General purpose register R1 is cleared                                                               | XGR1 = 0x0000                                                                                                                     |                                  |

| 11 | R1 = [VBR+4*CHID+2]             | The 2 <sup>nd</sup> word of the channel vector contains the content of general purpose register R1   | XGR1 = [XGVBR+4*XGCHID+2]                                                                                                         |                                  |

| 12 | R2R7 = 0x0000                   | General Purpose Registers<br>R2 to R7 are cleared                                                    | (XGR2 = 0x0000)<br>(XGR3 = 0x0000)<br>(XGR4 = 0x0000)<br>(XGR5 = 0x0000)<br>(XGR6 = 0x0000)<br>(XGR6 = 0x0000)<br>(XGR7 = 0x0000) | &&<br>&&<br>&&<br>&&<br>&&<br>&& |

| 13 | VBR+4*CHID = 0xFFFE             | The location of the channel vector is 0xFFFE                                                         | XGVBR+4*XGCHID = 0xFFFE                                                                                                           |                                  |

| 14 | VBR+4*CHID ≠ 0xFFFE             | The location of the channel vector is not 0xFFFE                                                     | XGVBR+4*XGCHID ≠ 0xFFFE                                                                                                           |                                  |

Figure 5. Observable Conditions for Investigating Software Errors on S12X Devices (Sheet 1 of 3)

\_\_\_\_\_

|    | Mnemonic                           | Description                                                              | Details                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |  |  |  |

|----|------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 15 | $VBR+4^*CHID \in register \ space$ | The location of the channel vector is inside the register space          | XGVBR+4*XGCHID < 0x0800                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |  |  |  |

| 16 | VBR+4*CHID ∉ register space        | The location of the channel vector is not inside the register space      | XGVBR+4*XGCHID ≥ 0x0800                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |  |  |  |

| 17 | $VBR+4^*CHID \in flash \ space$    | The location of the channel vector is inside the flash space             | (XGVBR+4*XGCHID ≥ 0x0800)<br>(XGVBR+4*XGCHID ≤ 0xFFFF-RAM size)                                                                                                                                                                                                                                                                                                                        | && |  |  |  |  |  |  |  |  |

| 18 | VBR+4*CHID ∉ secured flash space   | The location of the channel vector is not inside the secured flash space | (MODE&0xC0 = 0x00)<br>(FSEC&0x03 = 0x02)<br>(XGVBR+4*XGCHID < 0x0800)<br>(XGVBR+4*XGCHID Š> 0xFFFF-RAM size)                                                                                                                                                                                                                                                                           |    |  |  |  |  |  |  |  |  |

| 19 | [PC] ∈ legal opcodes               | The program counter points to a legal opcode                             | (([XGPC]&0xF880 ≠ 0x0000)    ([XGPC]&0x07F = 0x0000))<br>(([XGPC]&0xF880 ≠ 0x0080)    ([XGPC]&0xF8FF ≠ 0x00FB)<br>((XGPC]&0xF8FF ≠ 0x00FB)<br>((XGPC]&0xF8FC ≠ 0x00FC)<br>([XGPC]&0xF8F1 ≠ 0x0400)<br>([XGPC]&0xF818 ≠ 0x0800)<br>([XGPC]&0xF818 ≠ 0x0808)<br>([XGPC]&0xF803 ≠ 0x1001)                                                                                                 |    |  |  |  |  |  |  |  |  |

| 20 | [PC] ∉ legal opcodes               | The program counter points to an illegal opcode                          | (([XGPC]&0xF880 = 0x0000) && ([XGPC]&0x007F ≠ 0x0000))<br>(([XGPC]&0xF880 = 0x0080) && ([XGPC]&0x0070 ≠ 0x0070))<br>([XGPC]&0xF8FF = 0x00FB)<br>([XGPC]&0xF8FC = 0x00FC)<br>([XGPC]&0xF8FF = 0x0400)<br>([XGPC]&0xF818 = 0x0800)<br>([XGPC]&0xF818 = 0x0808)<br>([XGPC]&0xF803 = 0x1001)                                                                                               |    |  |  |  |  |  |  |  |  |

| 21 | [PC] ∈ STB                         | The program counter points to a STB instruction                          | ([XGPC]&0xF800 = 0x5000)<br>(([XGPC]&0xF800 = 0x7000) && ([XGPC]&0x0003 ≠ 0x0003))                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |

| 22 | [PC] ∈ STW                         | The program counter points to a STW instruction                          | ([XGPC]&0xF800 = 0x5800)<br>(([XGPC]&0xF800 = 0x7800) && ([XGPC]&0x0003 ≠ 0x0003))                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |

| 23 | [PC] ∈ LDB                         | The program counter points to LDB instruction                            | ([XGPC]&0xF800 = 0x4000)<br>(([XGPC]&0xF800 = 0x6000) && ([XGPC]&0x0003 ≠ 0x0003))                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |

| 24 | [PC] ∈ LDW                         | The program counter points to a LDW <sup>1</sup> instruction             | ([XGPC]&0xF800 = 0x4800)<br>(([XGPC]&0xF800 = 0x6800) && ([XGPC]&0x0003 ≠ 0x0003))                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |  |  |  |

| 25 | [PC+2] ∉ legal opcodes             | The incremented program<br>counter points to an illegal<br>opcode        | <pre>(([XGPC+2]&amp;0xF880 = 0x0000) &amp;&amp; ([XGPC+2]&amp;0x007F ≠ 0x0000))<br/>(([XGPC+2]&amp;0xF880 = 0x0080) &amp;&amp; ([XGPC+2]&amp;0x0070 ≠ 0x0070))<br/>([XGPC+2]&amp;0xF8FF = 0x00FB)<br/>([XGPC+2]&amp;0xF8FF = 0x00FC)<br/>([XGPC+2]&amp;0xF8FF = 0x0400)<br/>([XGPC+2]&amp;0xF818 = 0x0800)<br/>([XGPC+2]&amp;0xF818 = 0x0808)<br/>([XGPC+2]&amp;0xF803 = 0x1001)</pre> |    |  |  |  |  |  |  |  |  |

| 26 | data address & 1 = 1               | The address of the data access is odd                                    | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                  |    |  |  |  |  |  |  |  |  |

| 27 | data address $\in$ protected RAM   | The address of the data<br>access is within a protected<br>RAM area      | if ([XGPC]&0x2000 = 0x0000)<br>data_address ← XGRb + offs5<br>if ([XGPC]&0x2002 = 0x2000)<br>data_address ← XGRb + XGRi<br>(RAMWPC&0x01 = 0x01)<br>(((data_address > (RAMXGU<<8)+0x<br>(data_address > (RAMSHL<8))<br>(data_address > (RAMSHU<8)+0x                                                                                                                                    |    |  |  |  |  |  |  |  |  |

| 28 | data address $\in$ flash space     | The address of the data access is within the flash space                 | if ([XGPC] &0x2802 = 0x2002)<br>data_address $\leftarrow$ XGRb + XGRi + 1<br>if ([XGPC] &0x2802 = 0x2802)<br>data_address $\leftarrow$ XGRb + XGRi + 2                                                                                                                                                                                                                                 | && |  |  |  |  |  |  |  |  |

Figure 5. Observable Conditions for Investigating Software Errors on S12X Devices (Sheet 2 of 3)

|    | Mnemonic      | Description                                                                    | Details                                   |    |  |  |  |  |  |

|----|---------------|--------------------------------------------------------------------------------|-------------------------------------------|----|--|--|--|--|--|

| 29 | Secured flash | The flash has been removed<br>from the XGATE's memory<br>map (due to security) | (MODE&0xC0 ≠ 0x00)<br>(FSEC&0x03 ≠ 0x02)  | && |  |  |  |  |  |

| 30 | L15Y          | Device mask set ends with<br>"L15Y"                                            | (PARTIDH = 0xC4)<br>(PARTIDL&0xF0 = 0x10) | && |  |  |  |  |  |

| 31 | L15Y          | Device i mask set does not<br>end with "L15Y"                                  | (PARTIDH ≠ 0xC4)<br>(PARTIDL&0xF0 ≠ 0x10) | 1  |  |  |  |  |  |

Figure 5. Observable Conditions for Investigating Software Errors on S12X Devices (Sheet 3 of 3) <sup>1</sup> Excluding LDW RD, #IMM16

## 4.4 Software Error Scenarios

The number of scenarios leading to a XGATE Software Error is limited. They can be broken down into 22 cases. The following sections describe all of these scenarios and show how they can be identified. These descriptions refer to the cycle notation of the XGATE's RISC core (see Figure 6).

v — Vector fetch: always an aligned word read, lasts for at least one RISC core cycle P — Program word fetch: always an aligned word read, lasts for at least one RISC core cycle r — 8 bit data read: lasts for at least one RISC core cycle R — 16 bit data read: lasts for at least one RISC core cycle w — 8 bit data write: lasts for at least one RISC core cycle W — 16 bit data write: lasts for at least one RISC core cycle A — Alignment cycle: no read or write, lasts for zero or one RISC core cycle f — Free cycle: no read or write, lasts for one RISC core cycle PP/P — Branch: PP if branch taken, P if not

Figure 6. Access Detail Notation

#### 4.4.1 Vector Fetches

The vector fetch sequence of the XGATE consists of three memory accesses: A fetch of the starting address of the thread, a fetch of the data segment pointer, and a prefetch of the first instruction. There are four Software Error scenarios that could occur during the vector fetch sequence. They are listed in Figure 7. Observable conditions in this table printed in grey are redundant.

| Cycle |   | Description                             | s | oftware Error Condition                       | 0  | bserservable Condition                              | Relevant De                       | bug Information          |

|-------|---|-----------------------------------------|---|-----------------------------------------------|----|-----------------------------------------------------|-----------------------------------|--------------------------|

| V     | 1 | Vector fetch for the initial PC         | 2 | Vector fetch from an<br>unimplemented address | 1  | PC = 0xFFFE                                         | XGATE Channel:<br>Vector Address: | XGCHID<br>XGVBR+4*XGCHID |

|       |   |                                         |   | unimplemented address                         | 3  | PC & 1 = 0                                          | vector Address.                   |                          |

|       |   |                                         |   |                                               | 4  | $PC+2 \in register \ space$                         |                                   |                          |

|       |   |                                         |   |                                               | 5  | PC ∉ register space                                 |                                   |                          |

|       |   |                                         |   |                                               | 7  | $PC \notin secured flash space$                     |                                   |                          |

|       |   |                                         |   |                                               | 9  | CCR = 0x0                                           |                                   |                          |

|       |   |                                         |   |                                               | 10 | R1 = 0x0000                                         |                                   |                          |

|       |   |                                         |   |                                               | 12 | R2R7 = 0x0000                                       |                                   |                          |

|       |   |                                         |   |                                               | 14 | $VBR+4*CHID \neq 0xFFFE$                            |                                   |                          |

|       |   |                                         |   |                                               | 16 | VBR+4*CHID ∉ register space                         |                                   |                          |

|       |   |                                         |   |                                               | 17 | $VBR{+}4{*}CHID \in flash \ space$                  |                                   |                          |

|       |   |                                         |   |                                               | 29 | Secured flash                                       |                                   |                          |

|       |   |                                         | 3 | Vector fetch from register space              | 1  | PC = 0xFFFE                                         |                                   |                          |

|       |   |                                         |   |                                               | 3  | PC & 1 = 0                                          |                                   |                          |

|       |   |                                         |   |                                               | 4  | $PC+2 \in register space$                           |                                   |                          |

|       |   |                                         |   |                                               | 5  | PC ∉ register space                                 |                                   |                          |

|       |   |                                         |   |                                               | 7  | PC ∉ secured flash space                            |                                   |                          |

|       |   |                                         |   |                                               | 9  | CCR = 0x0                                           |                                   |                          |

|       |   |                                         |   |                                               | 10 | R1 = 0x0000                                         |                                   |                          |

|       |   |                                         |   |                                               | 12 | R2R7 = 0x0000                                       |                                   |                          |

|       |   |                                         |   |                                               | 14 | $VBR+4*CHID \neq 0xFFFE$                            |                                   |                          |

|       |   |                                         |   |                                               | 15 | $VBR{+}4{*}CHID \in register \ space$               |                                   |                          |

|       |   |                                         |   |                                               | 18 | $VBR{+}4{*}CHID \not\in \text{secured flash space}$ |                                   |                          |

| V     | 2 | Vector fetch for the initial R1 content | 3 | Vector fetch from register space              | 8  | PC+2 = [VBR+4*CHID]                                 | XGATE Channel:<br>Vector Address: | XGCHID<br>0xFFFE         |

|       |   | content                                 |   |                                               | 9  | CCR = 0x0                                           | vector Address:                   | UXFFFE                   |

|       |   |                                         |   |                                               | 10 | R1 = 0x0000                                         | 1                                 |                          |

|       |   |                                         |   |                                               | 12 | R2R7 = 0x0000                                       |                                   |                          |

|       |   |                                         | 1 |                                               | 13 | VBR+4*CHID = 0xFFFE                                 | -                                 |                          |

|       |   |                                         | 1 |                                               | 16 | VBR+4*CHID ∉ register space                         |                                   |                          |

|       |   |                                         | 1 |                                               | 18 | VBR+4*CHID ∉ secured flash space                    |                                   |                          |

Figure 7. Potential Software Errors During the Vector Fetch Sequence (Sheet 1 of 2)

| Cycle | Description                       | S | oftware Error Condition          | 0  | bserservable Condition           | Relevant Debug Information                              |

|-------|-----------------------------------|---|----------------------------------|----|----------------------------------|---------------------------------------------------------|

| Р     | 3 1 <sup>st</sup> opcode prefetch | 4 | Opcode fetch from an odd address | 2  | PC & 1 = 1                       | XGATE Channel: XGCHID<br>Vector Address: XGVBR+4*XGCHID |

|       |                                   |   | address                          | 8  | PC+2 = [VBR+4*CHID]              | Initial Program Counter: XGPC+2                         |

|       |                                   |   |                                  | 9  | CCR = 0x0                        | = [XGVBR+4*XGCHID]                                      |

|       |                                   |   |                                  | 11 | R1 = [VBR+4*CHID+2]              |                                                         |

|       |                                   |   |                                  | 12 | R2R7 = 0x0000                    |                                                         |

|       |                                   |   |                                  | 14 | $VBR+4*CHID \neq 0xFFFE$         |                                                         |

|       |                                   |   |                                  | 16 | VBR+4*CHID ∉ register space      |                                                         |

|       |                                   |   |                                  | 18 | VBR+4*CHID ∉ secured flash space |                                                         |

|       |                                   | 5 |                                  | 6  | $PC+2 \in flash space$           |                                                         |

|       |                                   |   | unimplemented address            | 8  | PC+2 = [VBR+4*CHID]              |                                                         |

|       |                                   |   |                                  | 9  | CCR = 0x0                        |                                                         |

|       |                                   |   |                                  | 11 | R1 = [VBR+4*CHID+2]              |                                                         |

|       |                                   |   |                                  | 12 | R2R7 = 0x0000                    |                                                         |

|       |                                   |   |                                  | 14 | VBR+4*CHID ≠ 0xFFFE              |                                                         |

|       |                                   |   |                                  | 16 | VBR+4∗CHID ∉ register space      |                                                         |

|       |                                   |   |                                  | 18 | VBR+4*CHID ∉ secured flash space |                                                         |

|       |                                   |   |                                  | 29 | Secured flash                    |                                                         |

|       |                                   | 6 | 1 5                              | 4  | $PC+2 \in register space$        |                                                         |

|       |                                   |   | space                            | 7  | PC ∉ secured flash space         |                                                         |

|       |                                   |   |                                  | 8  | PC+2 = [VBR+4*CHID]              |                                                         |

|       |                                   |   |                                  | 9  | CCR = 0x0                        |                                                         |

|       |                                   |   |                                  | 11 | R1 = [VBR+4*CHID+2]              |                                                         |

|       |                                   |   |                                  | 12 | R2R7 = 0x0000                    |                                                         |

|       |                                   |   |                                  | 14 | VBR+4*CHID ≠ 0xFFFE              |                                                         |

|       |                                   |   |                                  | 16 | VBR+4*CHID ∉ register space      |                                                         |

|       |                                   |   |                                  | 18 | VBR+4*CHID ∉ secured flash space |                                                         |

Figure 7. Potential Software Errors During the Vector Fetch Sequence (Sheet 2 of 2)

#### 4.4.2 Illegal Instructions

On S12X devices, the XGATEV2 has actually been shipped in two revisions. Both revisions differ slightly in the way they execute illegal instructions. Figure 8 shows the behavior for both these versions. The mask set number and the PARTID register value can be used to distinguish devices. MCUs with mask sets ending with "L15Y" (PARTIDH register reads 0xC4) contain one revision. The other XGATE revision can be found on all remaining S12X MCUs.

| Cycle | Description                             | Software Error Condition                | Obserservable Condition             | Relevant Debug<br>Information                    |  |  |

|-------|-----------------------------------------|-----------------------------------------|-------------------------------------|--------------------------------------------------|--|--|

| f     | 4 Illegal Instruction is to be executed | 1 Execution of an unimplemented opcode  | 3 PC & 1 = 0                        | XGATE Channel: XGCHID<br>Program Counter: XGPC+2 |  |  |

|       | executed                                | (Device mask set ends with<br>"L15Y")   | 14 VBR+4*CHID ≠ 0xFFFE              | Instruction: [XGPC+2]                            |  |  |

|       |                                         |                                         | 16 VBR+4*CHID ∉ register space      |                                                  |  |  |

|       |                                         |                                         | 18 VBR+4*CHID ∉ secured flash space |                                                  |  |  |

|       |                                         |                                         | 25 [PC+2] ∉ legal opcodes           |                                                  |  |  |

|       |                                         |                                         | 30 L15Y                             |                                                  |  |  |

|       |                                         | opcode<br>(Device mask set does not end | 3 PC & 1 = 0                        | XGATE Channel: XGCHID<br>Program Counter: XGPC   |  |  |

|       |                                         |                                         | 5 PC ∉ register space               | Program Counter: XGPC<br>Instruction: [XGPC]     |  |  |

|       |                                         | with "L15Y")                            | 7 PC ∉ secured flash space          |                                                  |  |  |

|       |                                         |                                         | 14 VBR+4*CHID ≠ 0xFFFE              |                                                  |  |  |

|       |                                         |                                         | 16 VBR+4*CHID ∉ register space      |                                                  |  |  |

|       |                                         |                                         | 18 VBR+4*CHID ∉ secured flash space |                                                  |  |  |

|       |                                         |                                         | 20 [PC] ∉ legal opcodes             |                                                  |  |  |

|       |                                         |                                         | 31 L15Y                             |                                                  |  |  |

Figure 8. Software Errors Caused by Illegal Instructions

#### 4.4.3 Opcode Prefetches in a Linear Flow

The term Single Cycle Instructions includes all instructions that execute in one XGATE cycle, like logic or arithmetic operations. All these instructions execute one opcode prefetch, which could occur from register space if the instruction is located at address 0xFFFE. Figure 9 gives a description of this scenario.

| Cycle |                                  | Description | s  | oftware Error Condition     | 0                   | bserservable Condition           |                                                                                    | ant Debug<br>rmation   |

|-------|----------------------------------|-------------|----|-----------------------------|---------------------|----------------------------------|------------------------------------------------------------------------------------|------------------------|

| Р     | 5 Opcode prefetch in linear flow |             | 7  |                             | 1                   | PC = 0xFFFE                      | XGATE Channel:                                                                     | XGCHID                 |

|       |                                  |             |    | space 2                     | 3                   | PC & 1 = 0                       | <ul> <li>Program Counter:<br/>Instruction:</li> <li>CCR:</li> <li>R1R7:</li> </ul> | 0xFFFE<br>[0xFFFE]     |

|       |                                  |             |    |                             | 4                   | $PC+2 \in register \ space$      |                                                                                    | unchanged<br>unchanged |

|       |                                  |             |    | 5                           | PC ∉ register space |                                  |                                                                                    |                        |

|       |                                  |             |    |                             | 7                   | $PC \notin secured flash space$  |                                                                                    |                        |

|       |                                  |             |    |                             | 14                  | $VBR+4*CHID \neq 0xFFFE$         |                                                                                    |                        |

|       |                                  | 1           | 16 | VBR+4*CHID ∉ register space | 1                   |                                  |                                                                                    |                        |

|       |                                  |             |    |                             | 18                  | VBR+4*CHID ∉ secured flash space | 1                                                                                  |                        |

|       |                                  |             |    |                             | 19                  | $[PC] \in \text{legal opcodes}$  | 1                                                                                  |                        |

Figure 9. Software Errors Caused by Opcode Prefetches in a Linear Program Flow

There are three special instructions that require an alignment cycle (optional cycle) after their opcode prefetch: SIF, SSEM, and CSEM. As alignment cycles cannot trigger Software Errors, these operations may be treated as single cycle instructions.

Software Errors caused by single cycle instructions can not be clearly distinguished from Software Errors caused by jumps or branches to address 0x0000 (Section 4.4.4). An exact determination of the error cause can only be made based on the context of the application.

### 4.4.4 Branch and Jump Instructions

Branches and jumps require two XGATE bus cycles. They execute two opcode fetches to fill the RISC core's instruction queue after they have set the program counter to the new address location.

Conditional branches behave as single cycle instructions if the branch condition is false. In this case only the first opcode fetch cycle is executed, the second one is skipped.

The Software Error Conditions that might occur during these cycles are listed in Figure 10. Observable conditions in this table printed in grey are redundant.

| Cycle          |   | Description                            | s | Software Error Condition                      |    | bserservable Condition                   | Relevant Debug<br>Information                                              |                                                                              |  |  |  |

|----------------|---|----------------------------------------|---|-----------------------------------------------|----|------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| Р              |   | see Section 4.4.3                      |   |                                               |    |                                          |                                                                            |                                                                              |  |  |  |

| P <sup>1</sup> | 6 | Opcode prefetch at destination address | 5 | Opcode fetch from an odd address <sup>2</sup> | 2  | PC & 1 = 1                               | XGATE Channel:<br>Program Counter:                                         | XGCHID<br>see Section 4.4.4                                                  |  |  |  |

|                |   | autress                                |   | auuress                                       | 14 | $VBR+4*CHID \neq 0xFFFE$                 | Instruction:     Destination address:                                      | JAL R? (see Section 4.4.4)<br>XGPC+2                                         |  |  |  |

|                |   |                                        |   |                                               | 16 | VBR+4*CHID ∉ register space              | Rd:                                                                        | return address                                                               |  |  |  |

|                |   |                                        |   |                                               | 18 | $VBR+4*CHID \not\in secured flash space$ | XGATE Channel:<br>Program Counter:<br>Instruction:<br>Destination address: |                                                                              |  |  |  |

|                |   |                                        | 6 | Opcode fetch from an<br>unimplemented address | 6  | $PC+2 \in flash space$                   |                                                                            | XGCHID<br>see Section 4.4.4<br>see Section 4.4.4<br>XGPC+2<br>return address |  |  |  |

|                |   |                                        |   | unimplemented address                         | 14 | VBR+4*CHID ≠ 0xFFFE                      |                                                                            |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 16 | VBR+4*CHID ∉ register space              | Rd: <sup>2</sup>                                                           |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 18 | VBR+4*CHID ∉ secured flash space         |                                                                            |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 29 | Secured flash                            |                                                                            |                                                                              |  |  |  |

|                |   |                                        | 7 | Opcode fetch from register                    | 4  | $PC+2 \in register space$                | 1                                                                          |                                                                              |  |  |  |

|                |   |                                        |   | space                                         | 7  | PC ∉ secured flash space                 |                                                                            |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 14 | VBR+4*CHID ≠ 0xFFFE                      | 1                                                                          |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 16 | VBR+4*CHID ∉ register space              |                                                                            |                                                                              |  |  |  |

|                |   |                                        |   |                                               | 18 | VBR+4*CHID ∉ secured flash space         | <u> </u>                                                                   |                                                                              |  |  |  |

Figure 10. Potential Software Errors Caused by Jump or Branch Instructions

<sup>1</sup> Omitted for conditional branches if the branch condition is false

<sup>2</sup> JAL instructions only

Branches to odd addresses are not possible, as the branch offset is always given in word entities. Only the JAL instruction is able to trigger this Software Error Condition.

Debugging of branch and jump instructions can be a tricky if the Software Error is detected in the second program fetch cycle.

Right before execution of the second P-cycle, the program counter is updated to the instruction preceeding the destination address, which causes two problems for the investigation of Software Errors:

- The address of the current instruction is lost. The XGATE doesn't provide a direct way to determine which branch or jump instruction has caused the Software Error.

- Branches or jumps to address 0x0000 leave exactly the same register signature as instructions executed from address 0xFFFE. These two scenarios cannot be clearly distinguished.

This change of the program counter in the middle of the instruction actually makes it easier to determine the Software Error Condition as the critical address of the opcode fetch can be checked directly (XGPC+2). Finding the exact instruction that caused the problem, however requires some deeper investigation. In general actions can be taken:

- All branch instructions that could have caused the Problem can be found through code linting. Any branch instruction that directs the program flow to the address XGPC+2 is a candidate for causing the problem. To ease this step all branch instructions that point into the register space must be eliminated. However, this is not always possible as these opcodes might by chance also appear in data structures.

- Assuming that the Software Error was caused by a JAL instruction, then the return address (the address following the JAL instruction) is stored in one of the General Purpose Registers (XGR1..XGR7).

A list of jump instructions that potentially triggered the Software Error can be obtained by iterating through the General Purpose Registers. If all of the following conditions are fulfilled...

$- XGRn \& 1 \equiv 0$

- XGRn > 0x0800

-  $[XGRn-2] \equiv 0x00F6 | (256*n)^{-1}$

... then the JAL Rn instruction located at address XGR*n*-2 is a candidate for causing the Software Error.

Any further investigation depends on the context of the application code.

#### 4.4.5 Load and Store Instructions

All load and store instructions perform two bus accesses: an opcode prefetech and a data access. The Software Error Conditions which can be triggered by these instructions are shown in Figure 11.

<sup>1.</sup> Opcode of the JAL Rn instruction

| Cycle | Description                | Software Error Conditio                      | n Obserservable Condition           | Relevant Debug<br>Information                          |  |  |

|-------|----------------------------|----------------------------------------------|-------------------------------------|--------------------------------------------------------|--|--|

| Р     |                            | S                                            | ee Section 4.4.3                    |                                                        |  |  |

| r     | 7 Data read or write acces | s 7 Byte read from an unimplemented address  | 3 PC & 1 = 0                        | XGATE Channel: XGCHID<br>Program Counter: XGPC         |  |  |

|       |                            |                                              | 5 PC ∉ register space               | Instruction: [XGPC]<br>Data address: see Section 4.4.5 |  |  |

|       |                            |                                              | 7 PC ∉ secured flash space          | R1R7: unchanged                                        |  |  |

|       |                            |                                              | 14 VBR+4*CHID $\neq$ 0xFFFE         |                                                        |  |  |

|       |                            |                                              | 16 VBR+4*CHID ∉ register space      |                                                        |  |  |

|       |                            |                                              | 18 VBR+4*CHID ∉ secured flash space |                                                        |  |  |

|       |                            |                                              | 19 $[PC] \in legal opcodes$         |                                                        |  |  |

|       |                            |                                              | 23 $[PC] \in LDB$                   |                                                        |  |  |

|       |                            |                                              | 28 data address $\in$ flash space   |                                                        |  |  |

|       |                            |                                              | 29 Secured flash                    |                                                        |  |  |

| R     |                            | 8 Word read from an odd addre                | ss 3 PC & 1 = 0                     |                                                        |  |  |

|       |                            |                                              | 5 PC ∉ register space               |                                                        |  |  |

|       |                            |                                              | 7 PC ∉ secured flash space          |                                                        |  |  |

|       |                            |                                              | 14 VBR+4*CHID ≠ 0xFFFE              |                                                        |  |  |

|       |                            |                                              | 16 VBR+4*CHID ∉ register space      |                                                        |  |  |

|       |                            |                                              | 18 VBR+4*CHID ∉ secured flash space |                                                        |  |  |

|       |                            |                                              | 19 $[PC] \in legal opcodes$         |                                                        |  |  |

|       |                            |                                              | 24 [PC] ∈ LDW                       |                                                        |  |  |

|       |                            |                                              | 26 data address & 1 = 1             |                                                        |  |  |

|       |                            | 9 Word read from an<br>unimplemented address | 3 PC & 1 = 0                        |                                                        |  |  |

|       |                            | unimplemented address                        | 5 PC ∉ register space               |                                                        |  |  |

|       |                            |                                              | 7 PC ∉ secured flash space          |                                                        |  |  |

|       |                            |                                              | 14 VBR+4*CHID ≠ 0xFFFE              |                                                        |  |  |

|       |                            |                                              | 16 VBR+4*CHID ∉ register space      |                                                        |  |  |

|       |                            |                                              | 18 VBR+4*CHID ∉ secured flash space |                                                        |  |  |

|       |                            |                                              | 19 [PC] ∈ legal opcodes             |                                                        |  |  |

|       |                            |                                              | 24 [PC] ∈ LDW                       |                                                        |  |  |

|       |                            |                                              | 28 data address ∈ flash space       |                                                        |  |  |

|       |                            |                                              | 29 Secured flash                    | 1                                                      |  |  |

Figure 11. Potential Software Errors Caused by Load or Store Instructions (Sheet 1 of 4)

| Cycle |   | Description               | So | oftware Error Condition                | 0  | bserservable Condition           |                                                   | ant Debug<br>rmation        |

|-------|---|---------------------------|----|----------------------------------------|----|----------------------------------|---------------------------------------------------|-----------------------------|

| w     | 7 | Data read or write access | 10 | Byte write to an unimplemented address | 3  | PC & 1 = 0                       | XGATE Channel:                                    | XGCHID<br>XGPC              |

|       |   |                           |    | address                                | 5  | PC ∉ register space              | Program Counter:<br>Instruction:<br>Data address: | [XGPC]<br>see Section 4.4.5 |

|       |   |                           |    |                                        | 7  | PC ∉ secured flash space         | R1R7:                                             | unchanged                   |

|       |   |                           |    |                                        | 14 | VBR+4*CHID ≠ 0xFFFE              |                                                   |                             |

|       |   |                           |    |                                        | 16 | VBR+4*CHID ∉ register space      |                                                   |                             |

|       |   |                           |    |                                        | 18 | VBR+4*CHID ∉ secured flash space |                                                   |                             |

|       |   |                           |    |                                        | 19 | $[PC] \in legal \ opcodes$       |                                                   |                             |

|       |   |                           |    |                                        | 21 | $[PC] \in STB$                   |                                                   |                             |

|       |   |                           |    |                                        | 28 | data address $\in$ flash space   |                                                   |                             |

|       |   |                           |    |                                        | 29 | Secured flash                    |                                                   |                             |

|       |   |                           | 11 | Byte write to flash space              | 3  | PC & 1 = 0                       |                                                   |                             |

|       |   |                           |    |                                        | 5  | PC ∉ register space              |                                                   |                             |

|       |   |                           |    |                                        | 7  | PC ∉ secured flash space         |                                                   |                             |

|       |   |                           |    |                                        | 14 | $VBR+4*CHID \neq 0xFFFE$         |                                                   |                             |

|       |   |                           |    |                                        | 16 | VBR+4*CHID ∉ register space      |                                                   |                             |

|       |   |                           |    |                                        | 18 | VBR+4*CHID ∉ secured flash space |                                                   |                             |

|       |   |                           |    |                                        | 19 | $[PC] \in \text{legal opcodes}$  |                                                   |                             |

|       |   |                           |    |                                        | 21 | $[PC] \in STB$                   |                                                   |                             |

|       |   |                           |    |                                        | 28 | data address $\in$ flash space   |                                                   |                             |

|       |   |                           | 12 | Byte write to protected RAM            | 3  | PC & 1 = 0                       |                                                   |                             |

|       |   |                           |    |                                        | 5  | PC ∉ register space              |                                                   |                             |

|       |   |                           |    |                                        | 7  | PC ∉ secured flash space         |                                                   |                             |

|       |   |                           |    |                                        | 14 | VBR+4*CHID ≠ 0xFFFE              |                                                   |                             |

|       |   |                           |    |                                        | 16 | VBR+4*CHID ∉ register space      |                                                   |                             |

|       |   |                           |    |                                        | 18 | VBR+4*CHID ∉ secured flash space |                                                   |                             |

|       |   |                           |    |                                        | 19 | $[PC] \in \text{legal opcodes}$  |                                                   |                             |

|       |   |                           |    |                                        | 21 | $[PC] \in STB$                   |                                                   |                             |

|       |   |                           |    |                                        | 27 | data address $\in$ protected RAM |                                                   |                             |

Figure 11. Potential Software Errors Caused by Load or Store Instructions (Sheet 2 of 4)

\_\_\_\_\_

| Cycle |   | Description               | So | oftware Error Condition      | 0  | bserservable Condition                |                                    | ant Debug<br>rmation        |

|-------|---|---------------------------|----|------------------------------|----|---------------------------------------|------------------------------------|-----------------------------|

| W     | 7 | Data read or write access | 13 | Word write to an odd address | 3  | PC & 1 = 0                            | XGATE Channel:<br>Program Counter: | XGCHID<br>XGPC              |

|       |   |                           |    |                              | 5  | PC ∉ register space                   | Instruction:<br>Data address:      | [XGPC]<br>see Section 4.4.5 |

|       |   |                           |    |                              | 7  | PC ∉ secured flash space              | R1R7:                              | unchanged                   |

|       |   |                           |    |                              | 14 | $VBR+4*CHID \neq 0xFFFE$              |                                    |                             |

|       |   |                           |    |                              | 16 | $VBR+4*CHID \not\in register \ space$ |                                    |                             |

|       |   |                           |    |                              | 18 | VBR+4*CHID ∉ secured flash space      |                                    |                             |

|       |   |                           |    |                              | 19 | $[PC] \in \text{legal opcodes}$       |                                    |                             |

|       |   |                           |    |                              | 22 | $[PC] \in STW$                        |                                    |                             |