# Freescale Semiconductor Application Note

Document Number: AN3802 Rev. 1, 2/2009

# Interfacing an LCD with the MC9S08LG32

by: Saurabh Jhamb

Reference Design and Applications Engineering

Microcontroller Solutions Group

### 1 Introduction

The MC9S08LG32 is a member of the Freescale HCS08 family. It uses the HCS08 core and integrated peripherals such as LCD, ADC, IIC, SPI, TPM, and RTC. This application note:

- Describes how the LCD module works for the MC9S08LG32

- Provides an example that illustrates the hardware connections and software driver for the LCD

- Explains configuration of the LCD module

- Describes use of the LCD glass with the MC9S08LG32

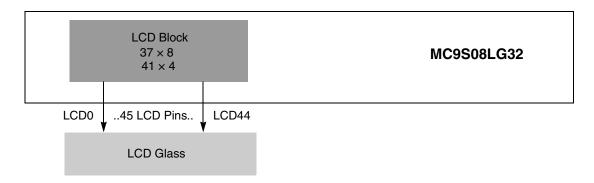

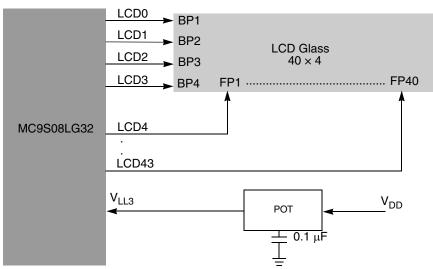

Figure 1 shows the block diagram for the LCD. The MC9S08LG32 contains 45 pins for LCD frontplane and backplane operation that are totally configurable. This means any pin can be configured for use with either the frontplane or the backplane.

#### **Contents**

| 1 | Intro | oducti  | on                                         |

|---|-------|---------|--------------------------------------------|

| 2 | Har   | dware   | e Interface Description                    |

|   | 2.1   |         | ntplane and Backplane Pin Connections 2    |

|   | 2.2   |         | age Pin Connections                        |

|   | 2.3   | Har     | dware Abstraction Layer                    |

|   | 2.    | .3.1    | Frontplane and Backplane Configuration 3   |

|   | 2.    | .3.2    | Control and Voltage Supply Configuration 5 |

|   | 2.    | .3.3    | Data Waveform Registers                    |

|   | 2.4   | LCD     | Operating Modes                            |

|   | 2.    | .4.1    | Resistor Bias (R-Bias) Mode 8              |

|   | 2.    | .4.2    | Charge Pump Mode                           |

| 3 | Sof   | tware   | Interface Description                      |

|   | 3.1   | Inte    | rfacing LCD Glass with MC9S08LG32 10       |

|   | 3.2   | Reg     | ister Configuration11                      |

| 4 | Initi | alizati | on Procedure                               |

|   | 4.1   |         | rating Modes Summary13                     |

| 5 | Opt   | ions f  | or V <sub>LL3</sub>                        |

| 6 | Ref   | erenc   | es                                         |

#### **Hardware Interface Description**

Figure 1. LCD Block Diagram

# 2 Hardware Interface Description

Table 1 describes the LCD pins and their directions.

**Pins** Direction Description LCD[0:44] LCD data pins Output You can configure these pins as frontplane or backplane.  $\rm V_{\rm LL1}$ Output LCD bias voltage  $V_{LL2}$ Output LCD bias voltage Input LCD bias voltage  $V_{LL3}$ See Section 5, "Options for V<sub>LL3</sub>," for more details.  $V_{LL3_2}$ Provides current enhancement at VII3 Input Note: This PIN must be shorted with V<sub>LL3</sub>.  $V_{CAP1}$ N/A Provides storage capacitance for LCD operation on internal charge pump mode N/A  $V_{CAP2}$

**Table 1. LCD Pin Description**

### 2.1 Frontplane and Backplane Pin Connections

These pin connections identify the number of backplanes and frontplanes supported in the LCD glass and connect each LCD glass pin to the corresponding LCD pin at MC9S08LG32 SoC.

#### NOTE

In the LCD software driver configuration, you must configure as backplane the SoC LCD block pins that connect to the backplane of the LCD glass.

#### 2.2 Voltage Pin Connections

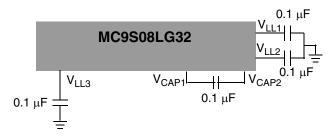

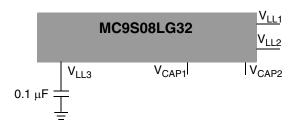

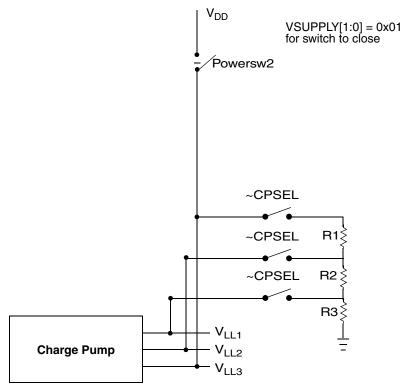

Figure 2 and Figure 3 show the recommended connections for the voltage supply pins of the SoC LCD block. Add a capacitor on the  $V_{LL3}$  pin to filter noise from the  $V_{DD}$  input and on  $V_{LL1}$ ,  $V_{LL2}$ ,  $V_{CAP1}$ , and

$V_{CAP2}$  pins for LCD operation in charge pump mode. No capacitor is required for LCD operation in resistor bias mode on  $V_{LL1}$ ,  $V_{LL2}$ ,  $V_{CAP1}$ , and  $V_{CAP2}$  pins.

Figure 2. LCD Voltage PIN Connections for Charge Pump Mode

Figure 3. LCD Voltage PIN Connections for Resistor Bias Mode

### 2.3 Hardware Abstraction Layer

This section contains the LCD registers. These registers configure:

- Pins used for the LCD display

- Pins used as backplane or frontplane

- Pins for transferring display data to the LCD glass

- Voltage and current specifications

#### 2.3.1 Frontplane and Backplane Configuration

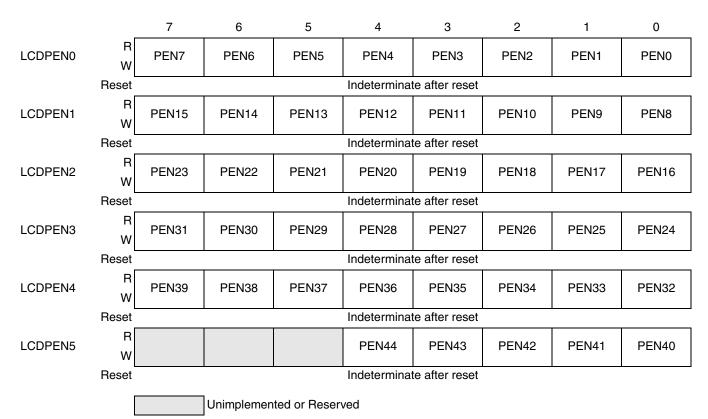

#### 2.3.1.1 LCD Pin Enable Registers

These registers specify the number of pins used for the LCD display.

#### **Hardware Interface Description**

Figure 4. LCDPEN Registers

Table 2. LCDPEN[0:5] Field Descriptions

| Field        | Description                                                       |

|--------------|-------------------------------------------------------------------|

| LCDPEN[44:0] | LCD Pin Enable  0 LCD operation disabled  1 LCD operation enabled |

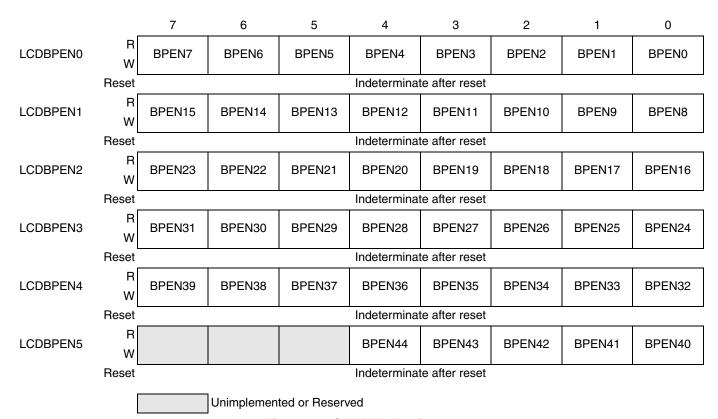

#### 2.3.1.2 Backplane Enable Registers

These registers specify the number of pins used as backplane. If the BPEN bits are cleared for a corresponding pin, then it acts as a frontplane pin.

Figure 5. LCDBPEN Registers

Table 3. LCDBPEN[0:5] Field Descriptions

| Field         | Description                                                                   |

|---------------|-------------------------------------------------------------------------------|

| LCDBPEN[44:0] | Backplane Enable 0 Frontplane operation enabled 1 Backplane operation enabled |

### 2.3.2 Control and Voltage Supply Configuration

This section describes the registers that configure the voltage and control specifications of the LCD block.

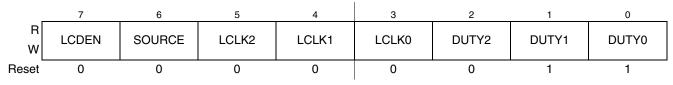

#### 2.3.2.1 LCD Control Register 0 (LCDC0)

Figure 6. LCD Control Register 0 (LCDC0)

#### **Hardware Interface Description**

#### **Table 4. LCDC0 Field Descriptions**

| Field            | Description                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LCDEN       | LCD Driver Enable 0 LCD disabled 1 LCD enabled                                                                                                           |

| 6<br>SOURCE      | CD Clock Source Select     Selects the OSCOUT (external clock reference) as the LCD clock source     Selects the alternate clock as the LCD clock source |

| 5:3<br>LCLK[2:0] | LCD Clock Prescaler — Used as a clock divider to generate the LCD module frame frequency.                                                                |

| 2:0<br>DUTY[2:0] | LCD Duty Select — These bits select the duty cycle of the LCD module driver.                                                                             |

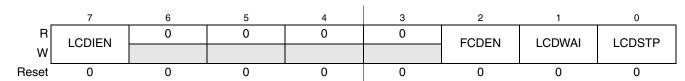

# 2.3.2.2 LCD Control Register 1 (LCDC1)

Figure 7. LCD Control Register 1 (LCDC1)

#### **Table 5. LCDC1 Field Descriptions**

| Field       | Description                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LCDIEN | LCD Module Frame Frequency Interrupt Enable  1 LCD interrupt enabled                                                                   |

| 2<br>FCDEN  | Full Complementary Drive Enable 0 Shared GPIOs are open drain 1 Shared GPIOs are full complementary                                    |

| 1<br>LCDWAI | LCD Module Driver and Charge Pump Stop When in Wait Mode  UCD is operating in WAIT mode  LCD is not operating in WAIT mode             |

| 0<br>LCDSTP | LCD Module Driver and Charge Pump Stop When in Stop2 or Stop3 Mode  UCD is operating in STOP modes  LCD is not operating in STOP modes |

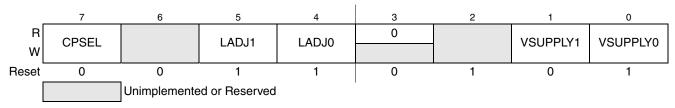

# 2.3.2.3 LCD Voltage Supply Register (LCDSUPPLY)

Figure 8. LCD Voltage Supply Register (LCDSUPPLY)

Interfacing an LCD with the MC9S08LG32, Rev. 1

**Table 6. LCDSUPPLY Field Descriptions**

| Field               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CPSEL          | Charge Pump or Resistor Bias Select  0 Resister bias selected  1 Charge pump selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5:4<br>LADJ[1: 0]   | LCD Module Load Adjust For CPSEL = 1 Adjust the clock source for the charge pump 00 — Fastest clock source for charge pump (LCD glass capacitance 8000 pF or lower) 01 — Intermediate clock source for charge pump (LCD glass capacitance 6000 pF or lower)) 10 — Intermediate clock source for charge pump (LCD glass capacitance 4000 pF or lower) 11 — Slowest clock source for charge pump (LCD glass capacitance 2000 pF or lower)  For CPSEL = 0 Adjust the resistor bias network for different LCD glass capacitance 00 — Low load (LCD glass capacitance 2000 pf or lower) 01 — Low load (LCD glass capacitance 2000 pf or lower) 10 — High load (LCD glass capacitance 8000 pf or lower) 11 — High load (LCD glass capacitance 8000 pf or lower) |

| 1:0<br>VSUPPLY[1:0] | Voltage Supply Control 01 — Drive V <sub>LL3</sub> internally 11 — Drive V <sub>LL3</sub> externally Others — Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### 2.3.3 Data Waveform Registers

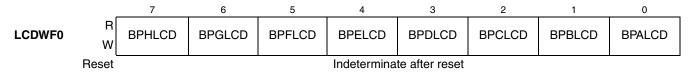

### 2.3.3.1 LCD Waveform Registers (LCDWF[63:0])

Figure 9. LCDWF Registers

**Table 7. LCDWF Field Descriptions**

| Field                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BP[x]LCD[y]<br>x — A:H<br>y — 0:44 | Segment on frontplane operation — If the LCD[y] pin is enabled and configured to operate as a frontplane pin, these bits control the on or off state for the LCD segment connected between LCD[y] and BP[x].  0 LCD segment off 1 LCD segment on Segment on backplane operation — If the LCD[y] pin is enabled and configured to operate as a backplane pin, these bits control the phase (A-H) in which the LCD[y] pin is active.  0 LCD BP[x] inactive for LCD[y] 1 LCD BP[x] active for LCD[y] |

#### 2.4 LCD Operating Modes

Figure 10 shows the internal circuitry for controlling the modes of operation for LCD block. The switches shown control all modes of bias voltage generation.

Figure 10. Generation of Bias Voltage in Different Modes

Table 8 describes all possible configurations for charge pump/resistor network mode selection.

| VSUPPLY[1:0] | CPSEL | Configuration                                                                                |

|--------------|-------|----------------------------------------------------------------------------------------------|

| 01           | 0     | Drive $V_{LL3}$ internally from $V_{DD}$ and $V_{LL1}$ . Drive $V_{LL2}$ from resistor bias. |

| 11           | 0     | Drive $V_{LL3}$ externally from $V_{DD}$ and $V_{LL1}$ . Drive $V_{LL2}$ from resistor bias. |

| 01           | 1     | Drive $V_{LL3}$ internally from $V_{DD}$ and $V_{LL1}$ . Drive $V_{LL2}$ from charge pump.   |

| 11           | 1     | Drive $V_{LL3}$ externally from $V_{DD}$ and $V_{LL1}$ . Drive $V_{LL2}$ from charge pump.   |

**Table 8. LCD Operating Modes**

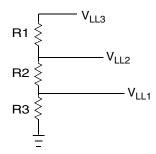

#### 2.4.1 Resistor Bias (R-Bias) Mode

In this mode, the bias voltages,  $V_{LL1}$  and  $V_{LL2}$ , are generated by an internal resistor bias circuit. In this mode, you can provide  $V_{LL3}$  or drive it internally from  $V_{DD}$ . The internal bias network has multiple drive variants (see Table 9). See Table 10 to configure register bias mode.

Figure 11. Bias Voltage in Resistor Bias Mode (R1 = R2 = R3)

**Table 9. Drive Variants in Internal Register Bias**

|            | LADJ[1:0] | Description                                           |

|------------|-----------|-------------------------------------------------------|

| Low Drive  |           | Up to 992 kW resistor ladder (three 992 kW resistors) |

| High Drive | 1X        | Up to 92 kW resistor ladder (three 92 kW resistors)   |

**Table 10. Resistor Bias Mode Configuration**

|                        | Va                          | lue                         |

|------------------------|-----------------------------|-----------------------------|

| Register Bit(s)        | V <sub>LL3</sub> Internally | V <sub>LL3</sub> Externally |

| LCDSUPPLY_CPSEL        | 0                           | 0                           |

| LCDSUPPLY_VSUPPLY[1:0] | 01                          | 11                          |

#### 2.4.2 Charge Pump Mode

In this mode, the bias voltages  $V_{LL1}$  and  $V_{LL2}$  are generated using an internal charge pump. For the charge pump to work properly, storage capacitors (0.1  $\mu$ F) are required on  $V_{LL1}$ ,  $V_{LL2}$ ,  $V_{CAP1}$ , and  $V_{CAP2}$  external pins. See Section 2.2, "Voltage Pin Connections," for details. In this mode, you can provide  $V_{LL3}$  externally or derive it internally from  $V_{DD}$  based on the configuration.

Figure 12. Bias Voltages in Charge Pump Mode

**Table 11. Charge Pump Mode Register Configuration**

|                        | Va                          | lue                         |

|------------------------|-----------------------------|-----------------------------|

| Register Bit(s)        | V <sub>LL3</sub> Internally | V <sub>LL3</sub> Externally |

| LCDSUPPLY_CPSEL        | 1                           | 1                           |

| LCDSUPPLY_VSUPPLY[1:0] | 01                          | 11                          |

Interfacing an LCD with the MC9S08LG32, Rev. 1

**Software Interface Description**

# **3 Software Interface Description**

This section describes the external APIs available. These APIs use the LCD block functionality in the software driver.

**Table 12. Software Interfaces**

| Interface            | Description                                                                                                                                                                   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lcd_Init             | Provides LCD initial configuration based on flags that you define.                                                                                                            |

| lcd_PrintString      | Takes a string as input and displays it on the alphanumeric character space on the LCD, starting from first alphanumeric character.                                           |

| lcd_PrintStringPos   | Takes a string as input and displays it on the alphanumeric character space on the LCD, starting from alphanumeric character as per the argument passed as pos.               |

| lcd_SlideString      | Takes a string as input and displays it on the alphanumeric character space on the LCD, sliding the string from right-most digit to the left-most digit.                      |

| lcd_DispHexVal       | Takes a number as input and displays it in hexadecimal format on the alphanumeric character space on the LCD, starting from alphanumeric character passed as startloc.        |

| lcd_DispDecVal       | Takes a float number as input and displays it in decimal base format on the alphanumeric character space on the LCD, starting from alphanumeric character passed as startloc. |

| lcd_DispVal          | Takes an integer number as input and displays it in decimal base format on the alphanumeric character space on the LCD, starting from alphanumeric digit passed as startloc.  |

| lcd_StopBlinking     | Turns off the blinking feature of the LCD on the current display.                                                                                                             |

| lcd_SetAltDisplay    | Turns on the alternate blinking mode with the display switching between the two strings that were passed as arguments.                                                        |

| lcd_Clear            | Clears all the LCD segments.                                                                                                                                                  |

| lcd_ActivateBlink    | Activates LCD blink functionality for the current LCD display.                                                                                                                |

| lcd_TestSpecialChars | A test routine for all the special characters supported in LCD.                                                                                                               |

# 3.1 Interfacing LCD Glass with MC9S08LG32

This section describes an example of interfacing the LCD glass ( $40 \times 4$ ) with the MC9S08LG32 in auto applications. The LCD block of the SoC is configured in resistor bias mode, and uses the external voltage supply on the  $V_{LL3}$  pin for LCD supply as well as external contrast control. Figure 13 shows the hardware connections for this example.

Figure 13. Example of Hardware Connections for Interfacing LCD Glass with MC9S08LG32

# 3.2 Register Configuration

Table 13 shows the control, voltage supply pins, and waveform data register configurations for operating the LCD glass in  $40 \times 4$  mode:

| Register   | Value | Configuration Description                                                                                         |

|------------|-------|-------------------------------------------------------------------------------------------------------------------|

| LCDC0      | 0x83  | Source clock from external oscillator<br>LCLK — Clock divider is 0<br>DUTY — Duty cycle is 3 (because mode is 4×) |

| LCDC1      | 0x00  | LCD Interrupt — Off<br>LCD interrupt — On in wait and stop modes                                                  |

| LCDVSUPPLY | 0x33  | CPSEL — Charge pump off LADJ[1:0] — 0x3 high drive (see Table 9) VSUPPLY — V <sub>LL3</sub> externally supplied   |

| LCDPEN0    | 0xFF  | Use 44 SoC pins for LCD operation.                                                                                |

| LCDPEN1    | 0xFF  |                                                                                                                   |

| LCDPEN2    | 0xFF  |                                                                                                                   |

| LCDPEN3    | 0xFF  |                                                                                                                   |

| LCDPEN4    | 0xFF  |                                                                                                                   |

| LCDPEN5    | 0x0F  |                                                                                                                   |

Table 13. LCD Register Configurations for 40  $\times$  4 Mode

#### **Initialization Procedure**

Table 13. LCD Register Configurations for 40 × 4 Mode (continued)

| Register    | Value | Configuration Description                                                                |  |

|-------------|-------|------------------------------------------------------------------------------------------|--|

| LCDBPEN0    | 0x0F  | Use LCD[0:3] as backplane and all other LCD                                              |  |

| LCDBPEN1    | 0x00  | pins (LCD[4:43]) as frontplane.                                                          |  |

| LCDBPEN2    | 0x00  |                                                                                          |  |

| LCDBPEN3    | 0x00  |                                                                                          |  |

| LCDBPEN4    | 0x00  |                                                                                          |  |

| LCDBPEN5    | 0x00  |                                                                                          |  |

| LCDWF[0:43] | 0x00  | Initialize the waveform registers. These registers contain the data for the LCD display. |  |

#### NOTE

You must configure all registers as described in Table 13 before enabling LCD (setting the LCDC0 LCDEN bit).

#### 4 Initialization Procedure

Obey the instructions below to configure the LCD block of the SoC to operate with an LCD glass, and to operate in resistor bias mode with external voltage supply on the  $V_{\rm LL3}$  pin and external contrast control.

1. Disable clock gating for the LCD module.

$$SCGC2_LCD = 1$$

2. Write LCDC0 register bits to configure the LCD module to use the clock from an external oscillator and to use clock divider and the duty cycle (number of backplanes – 1).

$$LCDC0 = 0x03$$

3. Write LCDC1 register bits to configure LCD interrupt as off and to make LCD functional in wait and stop low-power modes.

$$LCDC1 = 0x00$$

4. Write in LCD supply register (LCDCSUPPLY) to configure resistor bias mode operation and external voltage application on V<sub>LL3</sub> pin.

$$LCDSUPPLY = 0x33$$

- 5. Configure the number of pins to be used for LCD operation (44 SOC pins in LCDPEN register).

- 6. Configure the backplane pins LCD[0:3] as backplane and all other LCD pins as frontplane in LCDBPEN register.

$$LCDBPEN = 0x0F$$

- 7. Clear the LCDWF register to avoid the display of unwanted data on the LCD.

- 8. Enable the LCD module in the SoC by setting the LCDC0\_LCDEN bit.

$$LCDC0 = 0x83$$

# 4.1 Operating Modes Summary

Table 14 summarizes the operating modes, associated hardware connections, and register configurations for the LCD block of MC9S08LG32:

**Table 14. LCD Operating Modes Summary**

| Operating<br>Temperature<br>Range | Current<br>Consumption<br>(mA)      | Operating Mode | Hardware Connections                                                                         | Register Configurations                     | Applications                                                          |

|-----------------------------------|-------------------------------------|----------------|----------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------|

| –40 °C to 85 °C                   | X<br>(Lower current<br>consumption) | Charge Pump    | Supply $0.1\mu F$ capacitor for charge storage on $V_{LL1},V_{LL2},V_{CAP1},$ and $V_{CAP2}$ | _                                           | Consumer<br>appliances like<br>washing<br>machine,<br>microwave, etc. |

| −40 °C to 105 °C                  | Χ + (20 μΑ)                         | Register Bias  | No capacitor needed                                                                          | LCDSUPPLY_CPSEL = 0<br>LCDSUPPLY_LADJ = 0x3 | Automotive<br>applications like<br>auto cluster,<br>HVAC, etc.        |

# 5 Options for V<sub>LL3</sub>

Table 15 describes the configurations for  $V_{LL3}$  in MC9S08LG32.

#### NOTE

$V_{LL3} \mbox{ and } V_{DD} \mbox{ if different at power ramp, will cause current leakage.}$

Table 15. V<sub>LL3</sub> Configurations for LCD

| Configuration                                                                              | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>LL3</sub> connected to external supply                                              | This configuration applies if you:  • Use any of the 45 LCD pins as a full complementary digital GPIO.  • Vary V <sub>DD</sub> through board regulator to enable> the LCD contrast control feature.  • Select register bias mode or charge pump operating mode.                                                                                                                                                                                                                                                                                                          |

| V <sub>LL3</sub> connected to V <sub>DD</sub> internally                                   | <ul> <li>This configuration applies if you:</li> <li>Use any of the 45 LCD pins as a full complementary digital GPIO. GPIOs toggling as outputs must be configured as open drain. You can use digital input functions for these GPIOs.</li> <li>Vary V<sub>DD</sub> through board regulator to enable the LCD contrast control feature.</li> <li>Select register bias mode or charge pump operating mode.</li> </ul>                                                                                                                                                     |

| V <sub>LL3</sub> connected to an external independent source through potentiometer network | <ul> <li>This configuration applies if you:</li> <li>Use all 45 pins as LCD pins. You can also use digital input functions for GPIOs.</li> <li>Vary V<sub>DD</sub> through the external potentiometer to control the LCD contrast.</li> <li>Charge pump mode is preferred in this scenario. If using register bias mode, you must ensure that the potentiometer resistance is less than the register bias network values selected by setting LCDSUPPLY_LADJ bits. This is required to avoid a drop in V<sub>LL3</sub> if internal register bias is activated.</li> </ul> |

# 6 References

See S08LG Product Summary Page for more information and the documents released for MC9S08LG32.

Interfacing an LCD with the MC9S08LG32, Rev. 1

#### How to Reach Us:

**Home Page:**

www.freescale.com

Web Support:

http://www.freescale.com/support

USA/Europe or Locations Not Listed: Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130

www.freescale.com/support

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH

Technical Information Center

Schatzbogen 7

81829 Muenchen, Germany

+44 1296 380 456 (English)

+46 8 5220080 (English)

+49 89 92103 559 (German)

+33 1 69 35 48 48 (French)

www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: AN3802 Rev. 1 2/2009 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2009. All rights reserved.