Freescale Semiconductor Application Note Document Number: AN3832 Rev. 0, 04/2009

# Sensorless BLDC Motor Control Using MC9S08AC16

by: Petr Frgal

Freescale Czech System Laboratories Roznov pod Radhostem, Czech Republic

# 1 Introduction

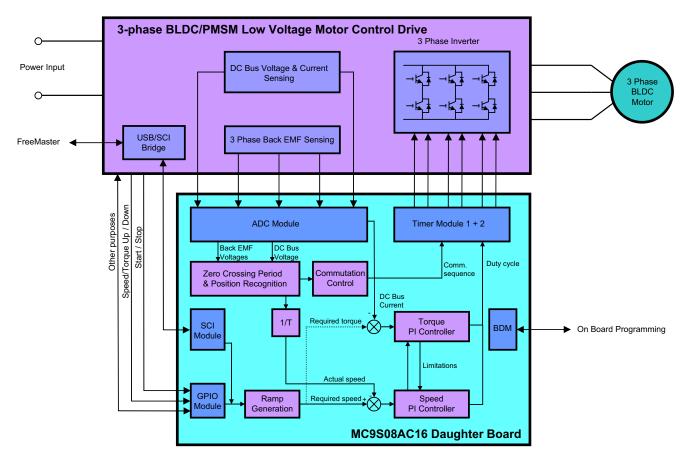

This application note describes the design of a 3-phase sensorless BLDC motor drive with Back-EMF zero crossing. It is based on Freescale's MC9S08AC16 that can be effectively used for motor-control applications.

The concept of the application is that of a speed-closed loop drive using Back-EMF zero crossing technique for positional detection. It serves as an example of a sensorless BLDC motor control system using Freescale's MCU and 3-Phase BLDC/PMSM Low-Voltage Motor Control Drive. It also illustrates the usage of general on-chip peripherals for motor-control applications.

This application note includes a description of the controller features, basic BLDC motor theory, system design concept, hardware implementation, software design including the FreeMaster software visualization tool, application setup, and demo operation.

#### Contents

| 1 | Intr               | oduction                          |  |

|---|--------------------|-----------------------------------|--|

| 2 | HC                 | S08 Advantages and Features       |  |

| 3 | BLD                | DC Motor Control Theory 4         |  |

| 4 |                    | tem Design Concept                |  |

|   | 4.1                | System Specification              |  |

|   | 4.2                | Sensorless Drive Concept7         |  |

| 5 | Har                | dware                             |  |

|   | 5.1                | Hardware Outline                  |  |

|   | 5.2                | Component Description             |  |

| 6 | Software Design 11 |                                   |  |

|   | 6.1                | MOSFET Driver Configuration       |  |

|   | 6.2                | PWM Generation & Timers           |  |

|   | 6.3                | Fault Handling 13                 |  |

|   | 6.4                | Manual User's Interface           |  |

|   | 6.5                | FreeMASTER Communication          |  |

|   | 6.6                | Others                            |  |

|   | 6.7                | Controller Usage 13               |  |

| 7 | Der                | no Setup and Operation14          |  |

|   | 7.1                | Hardware Setup 14                 |  |

|   | 7.2                | Software Setup 15                 |  |

|   | 7.3                | Sensorless BLDC Demo Operation 16 |  |

| 8 | Ref                | erences                           |  |

© Freescale Semiconductor, Inc., 2009. All rights reserved.

**HCS08 Advantages and Features**

# 2 HCS08 Advantages and Features

The MC9S08ACxx is a family of devices based on the high-performance HCS08 core, supporting 5-volt applications. It is a highly integrated, high-performance family packed with valuable features:

- 8-128 K flash memory.

- 3/4K-8 K RAM.

- A flexible internal clock generator that eliminates the need for external components, low voltage detection, high-performance, analog-to-digital converter (ADC), serial communication modules, and so on.

The MC9S08ACxx family performs well in a variety of environments, and is qualified for automotive applications. This family is suitable for appliance (white goods) and industrial applications.

The HCS08 family incorporates these standard features:

- 40 MHz HCS08 CPU.

- HC08 instruction set with BGND instruction.

- Internal background debugging system.

- Breakpoint capability to allow single-breakpoint setting during in-circuit debugging (plus two more breakpoints in the on-chip debug module).

- Debug module:

- Contains two comparators, nine trigger modules, and eight deep FIFO for storing change-of-flow addresses and event-only data.

- Supports tag and force breakpoints.

- Support for up to 32 interrupt/reset sources.

- System protection features:

- Optional computer operation properly (COP) reset.

- Low voltage detection with reset or interrupt.

- Illegal opcode detection with reset.

- Illegal address detection with reset (some devices don't have illegal addresses).

The MC9S08AC16 incorporates these features:

- 16 KB of on-chip, in-circuit programmable flash memory with block protection and security options.

- 1 KB of on-chip RAM.

- 6/8-channel, 10-bit analog-to-digital converter (ADC).

- Two serial communication interface (SCI) modules.

- Serial peripheral interface (SPI) module.

- External voltage monitor (EVM) allowing input level monitoring with selectable trigger point and interrupt generation.

- Clock source options including crystal, resonator, external clock, or an internally-generated clock with precise NVM trimming.

- Inter-integrated circuit (IIC) bus module to operate at up to 100 kbps.

- Two 2-channel and one 2/4-channel, 16-bit timer/pulse width modulator (TPM) modules.

- Selectable input-capture, output-compare, and edge-aligned pulse width modulation (PWM) capability on each channel.

- Each timer module may be configured for buffered, centered PWM (CPWM) on all channels.

- 4/6/7-pin keyboard interrupt (KBI) module.

- Software-selectable pullups on ports when used as input (selection is on an individual port-bit basis; during output mode, pullups are disengaged).

- Software-selectable slew rate control is on-port when used as inputs.

- Master  $\overline{\text{RESET}}$  pin and power-on reset (POR).

- Internal pullup on  $\overline{\text{RESET}}$  and IRQ pins to reduce customer system cost.

- 22/34/38 general-purpose input/output (I/O) pins.

- 32-pin low-profile quad flat package (LQFP), 44-pin low-profile quad flat package (LQFP), and 48-pin quad flat no-lead package (QFN).

Table 1 shows peripheral availability according to package type.

|          | Package Option |           |           |  |

|----------|----------------|-----------|-----------|--|

| Feature  | 32-pin         | 44-pin    | 48-pin    |  |

| ADC      | 6-channel      | 6-channel | 8-channel |  |

| IIC      | yes            |           |           |  |

| IRQ      | yes            |           |           |  |

| KBI1     | 4              | 6         | 7         |  |

| SCI1     | yes            |           |           |  |

| SCI2     | no             | yes       | yes       |  |

| SPI1     | yes            |           |           |  |

| TPM1     | 2-channel      | 4-channel | 4-channel |  |

| TPM2     | 2-channel      | 2-channel | 2-channel |  |

| ТРМЗ     | 2-channel      | 2-channel | 2-channel |  |

| I/O pins | 22             | 34        | 38        |  |

#### Table 1. Peripheral Availability per Package Type

The key peripherals for 3-phase BLDC motor control are the TPM/PWM module and an analog-to-digital converter (ADC). The MC9S08AC16 includes a 4-channel TPM1 and a separate 2-channel TPM2 and TPM3. The TPM1 and TPM2 modules, set in buffered center-aligned mode, are used for generating a PWM pattern for 3-phase BLDC motor control. TMP3 module channel zero and channel one work in software-output compare-only mode. The interrupt from TMP3 channel zero is used for updating the commutation sector and channel one for a periodic interrupt every 5 ms.

#### **BLDC Motor Control Theory**

The TPM module features include:

- Eight channels:

- Each channel may be input-capture, output-compare, or buffered, edge-aligned PWM.

- Rising-edge, falling-edge, or any-edge input-capture trigger.

- Set, clear, or toggle output-compare action.

- Selectable polarity on PWM outputs.

- Each TPM may be configured for buffered, center-aligned PWM (CPWM) on all channels.

- Clock source to the prescaler for each TPM is independently selectable as the bus clock, fixed system clock, or an external pin:

- Pre-scale taps for division by 1, 2, 4, 8, 16, 32, 64, or 128.

- 16-bit free-running or up/down (CPWM) count operation.

- 16-bit modulus register to control the counter range.

- Timer system enable.

- One interrupt per channel and a terminal-count interrupt for each TPM module.

The ADC evaluates Back EMF zero-crossing detection without any external comparators, and senses other analog quantities necessary for BLDC motor control. ADC is set for single, 10-bit conversion.

The ADC has the following features:

- Linear successive approximation algorithm with 10-bit resolution.

- Up to eight analog inputs.

- Output formatted as 10- or 8-bit right-justified.

- Single or continuous conversion (automatic return to idle after single conversion).

- Configurable sample time and conversion speed/power.

- Conversion-complete flag and interrupt.

- Input clock selectable from up to four sources.

- Operation in *wait* or *stop3* modes for lower-noise operation.

- Selectable asynchronous hardware-conversion trigger.

- Automatic comparison with interrupt for a less-than, greater-than, or equal-to programmable value.

# 3 BLDC Motor Control Theory

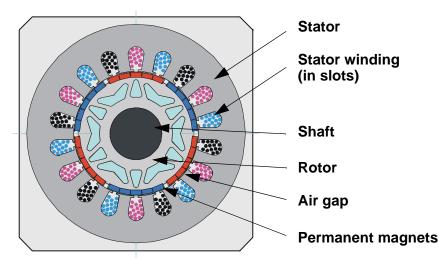

The Brushless DC Motor (BLDC Motor) is a rotating electric machine with a classic 3-phase stator like that of an induction motor; the rotor has surface-mounted permanent magnets. It is also referred to as an electronically-commuted motor. There are no brushes on the rotor and the commutation is performed electronically at certain rotor positions. The stator is usually made from magnetic steel sheets. A typical cross section of a BLDC Motor is shown in Figure 1. The stator-phase windings are inserted in the slots (distributed winding) or they can be wound as one coil onto the magnetic pole. Because the air-gap magnetic field is produced by permanent magnets, the rotor magnetic field is constant.

#### **BLDC Motor Control Theory**

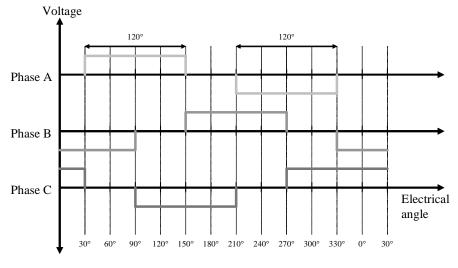

The magnetisation of the permanent magnets and their displacement on the rotor is chosen so that the Back-EMF (the voltage induced on the stator winding due to rotor movement) shape is trapezoidal. This allows the DC voltage (see Figure 2) with a rectangular shape to be used to create a rotational field with low-torque ripples.

Figure 1. BLDC Motor / Cross Section

The motor can have more than just one pole-pair per phase. The pole-pair per phase defines the ratio between the electrical revolution and the mechanical revolution. For example, the shown BLDC motor has three pole-pairs per phase that represent the three electrical revolutions per one mechanical revolution.

The rectangular, easy to create shape of the applied voltage ensures the simplicity of control and drive. However, the rotor position must be known at certain angles in order to align the applied voltage with the Back-EMF. The alignment between Back-EMF and commutation events is very important. Under this condition the motor behaves as a DC motor and runs at the best working point. Thus, simplicity of control and performance makes the BLDC motor the best choice for low-cost and high-efficiency applications.

Figure 2. 3-Phase Voltage System of BLDC Motor

#### **BLDC Motor Control Theory**

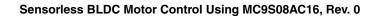

Figure 3 shows the number of waveforms, the magnetic-flux linkage, the phase Back-EMF voltage, and the phase-to-phase Back-EMF voltage. The magnetic-flux linkage was measured by calculating the integration-phase Back-EMF voltage, which was measured on the non-fed motor terminals of the BLDC motor. As can be seen, the shape of the Back-EMF is approximately trapezoidal and the amplitude is a function of the actual speed. During the speed reversal the amplitude is changed, and its sign and phase sequence change too.

The filled areas in the tops of the phase Back-EMF voltage waveforms indicate the intervals, where the particular phase power stage commutations are conducted. As can be seen, the power switches are cyclically commutated through the six steps. The crossing points of the phase Back-EMF voltages represent the natural commutation points. In a normal operation, the commutation is performed here. Some control techniques lead the commutation by a defined angle in order to control the drive above the PWM voltage control.

Figure 3. BLDC Motor / Back-EMF

# 4 System Design Concept

### 4.1 System Specification

The motor-control system is designed to drive a 3-phase, brushless-DC (BLDC) motor in a speed and torque-closed loop. The application meets these performance specifications:

- It has a sensorless brushless DC motor control using Back-EMF zero-crossing sensing.

- It is targeted at the MC6S08AC16 controller.

- The application is running on a 3-Phase BLDC/PMSM Low-Voltage Motor Control Drive.

- Control technique incorporates:

- Sensorless control with speed and torque-closed loop.

- ADC converter for zero-crossing sensing.

- Rotation in both directions.

- Full 4-quadrant operation.

- Start from any motor position with rotor alignment.

- Manual interface (direction toggle switch, up/down push-button control).

- FreeMASTER software-control interface (motor START/STOP, speed/torque setup).

- FreeMASTER software remote monitor.

### 4.2 Sensorless Drive Concept

The concept shown in Figure 4 was chosen. The sensorless rotor position technique developed detects the zero-crossing points of Back-EMF induced in the motor windings. The phase Back-EMF zero-crossing points are sensed while one of the three phase windings is not powered. The obtained information is processed in order to commutate the energized phase pair and control the phase voltage, using Pulse Width Modulation.

#### System Design Concept

Figure 4. System Configuration

The Back-EMF zero-crossing detection enables positional recognition. The resistor network is used to divide sensed voltages down to a 0–3.3 V voltage level. Zero-crossing detection is synchronized with the center of the center-aligned PWM signal by the software, in order to filter high-voltage spikes produced by the switching of the MOSFETs. This signal is transferred to the controller on the daughter board. Scaled Back-EMF signal selection is done through software, which corresponds to the current commutation step.

A current shunt is used to measure the DC-bus current. The obtained signal is rectified and amplified (0–3.3 V with 1.65 V offset). The controller's AD converter, as well as zero-crossing detection, is synchronized with the PWM signal. This synchronization avoids spikes when the MOSFETs are switching, and simplifies the electric circuit.

The AD converter is also used to sense the DC-bus voltage. The DC-bus voltage is divided down to a 3.3 V level by a resistor network.

The six MOSFETs and gate drivers create a compact power stage. The drivers provide the level shifting that is required to drive the high-side bridge circuits commonly used in motor drives. The PWM technique is applied to control motor-phase voltage.

# 5 Hardware

### 5.1 Hardware Outline

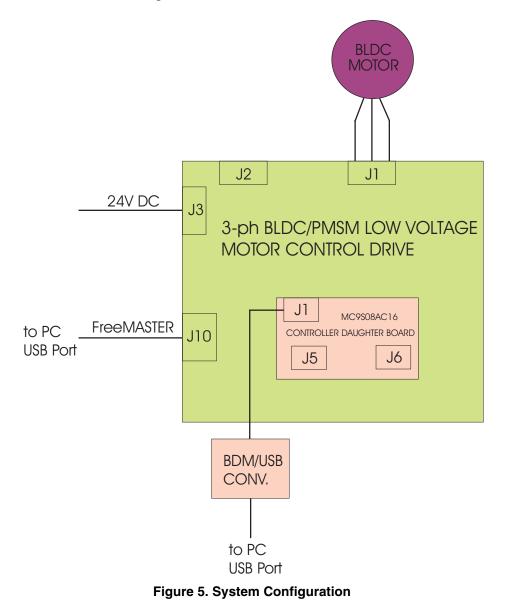

The BLDC sensorless application runs on Freescale's 3-phase BLDC/PMSM Low-Voltage Motor Control Drive, MC9S08AC16 Controller Daughter Board and 45ZWN24-40 motor.

Hardware

### 5.2 Component Description

### 5.2.1 3-Phase BLDC/PMSM Low-Voltage Motor Control Drive

Freescale's 3-phase BLDC/PMSM Low Voltage Motor Control Drive is a 12–24 V (50 V optional) DC, 4 A, off-line power stage that, as a main board together with a daughter board, creates a single unit for developing BLDC/PMSM motor-control applications.

With one of the available daughter boards, accommodating a selected microcontroller, it provides a ready-made, software-development platform for 3-phase motors. Feedback signals that allow a variety of algorithms to control 3-phase PMSM and BLDC motors are provided.

A detailed description, including the hardware specification of the 3-phase BLDC/PMSM Low-Voltage Motor Control Drive board, is located in the user's manual under LVMCDBLDCPMSMUG. The user's guide contains the schematic of the board, description of individual function blocks, and a bill of materials.

The board doesn't need any hardware modification or jumper setting before first usage. Before first usage, the user should pay attention to a correct driver USB/SCI installation. All about the driver installation is also included in the board user's manual.

### 5.2.2 MC9S08AC16 Controller Daughter Board

A detailed description of the MC9S08AC16 Controller Daughter Board can be found in user's manual CDBBLDCPMSMUG. The user's guide contains the schematic of the board, a brief description, and a bill of materials.

Headers J2, J3, and J4 must be shorted by jumpers between pins two and three to connect the Back-EMF signal to the controller inputs.

### 5.2.3 Motor 45ZWN24-40 (Produced by Linix)

The following motor is used for the BLDC sensorless application. Of course, other motors can also be adapted to the application, just by defining and changing the motor-related parameters. A detailed motor specification is shown in Table 2.

#### Software Design

| Characteristic            | Symbol          | Min | Тур | Max  | Units   |

|---------------------------|-----------------|-----|-----|------|---------|

| Reference Winding Voltage | Vt              | —   |     | 24   | V       |

| Speed @ V <sub>t</sub>    |                 | —   | —   | 4000 | RPM     |

| Torque Constant           | K <sub>t</sub>  | —   |     | _    | Nm/A    |

|                           |                 |     | _   | _    | oz-in/A |

| Voltage Constant          | K <sub>e</sub>  | —   | _   | —    | V/kRPM  |

| Terminal Resistance       | Rt              | —   | _   | —    | W       |

| Winding Inductance        | L               |     |     |      | mH      |

| Continuous Current        | I <sub>cs</sub> | —   | —   | —    | A       |

| Number of Pole Pairs      | J <sub>m</sub>  | —   | _   | —    | —       |

| Temperature Rating        |                 | —   |     | _    | °C      |

|                           |                 | —   | —   | —    | °F      |

#### Table 2. Electrical Characteristics of Linix 45ZWN24-40 Motor

# 6 Software Design

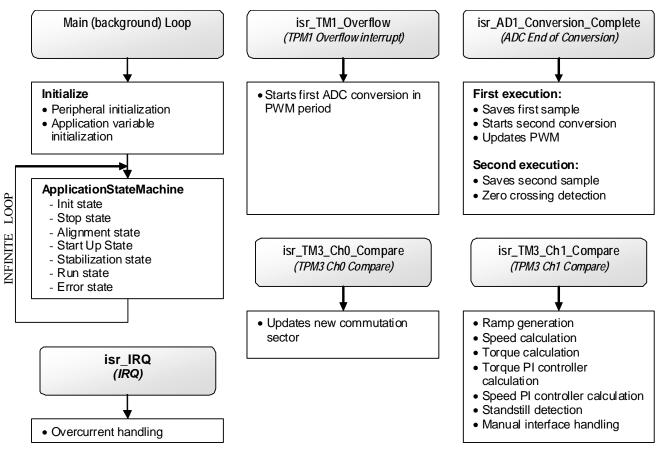

As earlier mentioned, the whole application comes out of reference design DRM086 — see • Sensorless BLDC Motor Control Using MC9S08AW60, DRM086, Freescale 2007. This concerns the software too. A detailed software description is in the DRM086. Therefore, there will be a description of the differences only. The main software structure is shown in Figure 6.

#### Software Design

Figure 6. Main Software Flow Chart

The software was ported from the HCS9S08AW60 to the HCS9S08AC16. These parts are pin-compatible but each has a different number of pins. The HCS9S08AW60 has 64 pins, the HCS9S08AC16 has 44 pins.

Due to the different hardware topology of the MOSFET driver, the generation of PWM signals is different. PWM dead time is generated by means of hardware using the MC33927 driver instead of software generation in the reference design.

### 6.1 MOSFET Driver Configuration

For correct operation of the MC33927, the driver should be configured. This driver is able to configure only via SPI communication. There are two more files, providing SPI communication between the MCU and the driver, and for configuring the MOSFET driver. In the *spi\_comm.h* header file, there are configuration and status constants defined for the MC33927 driver. In the *spi\_comm.c* file there are SPI communication functions and configuration function for the MC33927 driver. The SPI communication isn't used only for driver configuration, but also for diagnosing this driver. A spicom driver is used.

### 6.2 **PWM Generation & Timers**

Because the HCS9S08AC16 has only four timers in the TIMER1 module, the TIMER2 module is configured to operate in the same mode, center-aligned mode, as TIMER1 and its two channels together with four channels of TIMER1 are used to generate the PWM signal for the 3-phase bridge. Both timers are running synchronously.

Both channels of TIMER3 are operating in output-compare mode and substitute the TIMER2 function from reference design DRM086 — see • Sensorless BLDC Motor Control Using MC9S08AW60, DRM086, Freescale 2007.

### 6.3 Fault Handling

An IRQ event interrupt is called in the case of over-current detection and in the case of DC-bus under-voltage, driver over-temperature, and other cases. Over-current detection is a hardware interrupt source of the MC33927 driver. All others are software-interrupt sources and can be configured in this driver. The over-current pin OC and the INT pin, representing software interrupts, are linked to an OR gate before being connected to the IRQ pin, and can call out an interrupt independently of each other. The OR gate is located on the MC9S08AC16 Controller Daughter Board.

In the IRQ interrupt service routine all PWM signals are disabled, and the source or sources that cause the interrupt are stored in *fault\_reg* and an infinite loop is executed.

### 6.4 Manual User's Interface

A toggle-switch with three selectable positions was used for the start/stop function. The left edge position is used to start spinning the motor in a clockwise direction, and the right edge position is used for spinning in a counter-clockwise direction. The middle position is used to stop the motor spinning.

### 6.5 FreeMASTER Communication

Serial communication using the SCI module was implemented for remote control using FreeMASTER. The host computer is connected to the controller via a USB cable. The computer USB port works as a virtual COM port. Signal conversion from USB form to SCI form, and vice versa, is done by the USB/SCI bridge. More information can be found in the 3-Phase BLDC/PMSM Low-Voltage Motor Control Drive user's manual — LVMCDBLDCPMSMUG.

### 6.6 Others

Finally, motor parameters, alignment, and starting constants are stored in the *main.h* file. The motor used in this application is different from that used in the reference design, so the motor parameters are logically different.

### 6.7 Controller Usage

Table 3 shows how much memory is used to run the BLDC motor drive with Back-EMF zero crossing in a speed-closed loop. A part of the device's memory is still available for other tasks.

**Demo Setup and Operation**

| Memory        | Available | Used        |

|---------------|-----------|-------------|

| Program FLASH | 16 kB     | 6 085 Bytes |

| Data RAM      | 1 kB      | 593 Bytes*  |

Table 3. RAM and FLASH Memory Usage

\* including stack

# 7 Demo Setup and Operation

For demonstrating the operation, this demo was built and is available for customers.

### 7.1 Hardware Setup

The sensorless BLDC demo includes the BLDC motor and the 3-Phase BLDC/PMSM Motor Control Drive together with the MC9S08AC16 Daughter Board (see Figure 7).

Figure 7. Sensorless BLDC Demo

Steps needed to operate the sensorless BLDC demo:

- 1. Plug the power supply jack connector to the 3-Phase BLDC/PMSM Motor Control Drive connector J2.

- 2. Connect the USB cable to the PC and to the BLDC drive board.

- 3. Check the jumper settings of J2–J4 on the MC9S08AC16 Daughter Board. BEMF\_A, BEMF\_B, and BEMF\_C (shorted pins two and three) must be in position.

- 4. Plug the power supply into an outlet. LED D19 on the 3-phase BLDC Drive lights up.

The demo setup is shown in Figure 8.

Figure 8. Sensorless BLDC Demo Setup

### 7.2 Software Setup

Source code is a part of this application note. Source code is written in CodeWarrior ver. 6.3. There is a FreeMASTER project file and a FreeMASTER control page also available.

USB/SCI driver installation is required prior to first usage of FreeMASTER. Driver installation is described in the MS Word file "Installation USB/SCI Bridge manual". After succesfully installing the driver, select a virtual COM port attached to the USB port (HC9S08JMxx CDC (COMx)), and then FreeMASTER is ready to use.

References

# 7.3 Sensorless BLDC Demo Operation

The BLDC motor control application can be controlled through the manual interface, consisting of the toggle-switch and UP/DOWN buttons on the 3-Phase BLDC/PMSM Low-Voltage Motor Control Drive board, or remotely using PC. The BLDC drive can operate in speed or torque operational mode.

### 7.3.1 Speed Operational Mode

If the application is set to the speed operational mode, the user can set the required speed manually, or using the PC. The DC-bus current (torque) is automatically set to the maximal value of x A. In this case, the BLDC drive maintains the required speed until the maximum DC-bus current (torque) is exceeded.

### 7.3.2 Torque Operational Mode

Similarly, in torque operational mode the user can set the DC-bus current (torque) of the BLDC motor. The required value can be set by the UP/DOWN buttons, or remotely using the PC. The speed limit is set to a maximal speed of 4000 rpm. In this case, the BLDC drive maintains the required DC-bus current (torque) until the maximum BLDC motor speed is achieved.

The operational mode can be changed only when the motor is stopped (toggle-switch is in the middle position). The default setting is speed-operational mode.

## 8 References

- Sensorless BLDC Motor Control Using MC9S08AW60, DRM086, Freescale 2007.

- 3-phase BLDC/PMSM Low Voltage Motor Control Drive User's Manual, LVMCDBLDCPMSMUG, Freescale 2008

- MC9S08AC16 Controller Daughter Board User's Manual, CDBBLDCPMSMUG, Freescale 2008.

- MC9S08AC16: Technical Data Sheet for MC9S08AC8/AC16/AW8A/AW16A MCUs, Freescale 2008.

- 3-Phase BLDC Motor Control with Sensorless Back EMF Zero Crossing Detection Using 56F80x, AN1914, Freescale 2005

- FreeMaster for Embedded Applications User Manual, Freescale 2004.

- Freescale web page: http://www.freescale.com.

References

#### How to Reach Us:

Home Page: www.freescale.com

Web Support:

http://www.freescale.com/support

#### USA/Europe or Locations Not Listed:

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Rescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China China +86 10 5879 8000 support.asia@freescale.com

For Literature Requests Only: Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Document Number: AN3832 Rev. 0 04/2009

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2009. All rights reserved.