# Freescale Semiconductor

**Application Note**

Document Number: AN4236 Rev. 0, 11/2010

# MC9S12XHY-Family Demonstration Lab Training

by: José Cisneros Luis Hernandez Hugo Osornio Microcontroller Solutions Group, Mexico

## 1 Introduction

This publication serves to document demonstration lab software examples. The examples show how to configure and use the modules to users getting started with the MC9S12XHY family of MCUs.

The examples included here illustrate a basic configuration of the modules that allow users to quickly start developing applications.

The complete code is available for all examples. This can be downloaded onto an MC9S12XHY256 target such as the DEMO9S12XHY256 demo board, which this demonstration lab is based on.

Each module of the MC9S12XHY family has its own stand alone software and is discussed within its own section of this document.

#### Contents

| 1 | Intro | duction                         |

|---|-------|---------------------------------|

| 2 | Setu  | ıp2                             |

| 3 | Dem   | onstration Lab Examples         |

|   | 3.1   | Clocks and reset generator      |

|   | 3.2   | Flash programming example       |

|   | 3.3   | Emulated EEPROM driver          |

|   | 3.4   | MSCAN Module                    |

|   | 3.5   | PWM module                      |

|   | 3.6   | Low Power Modes                 |

|   | 3.7   | MMC program flash paging window |

|   | 3.8   | ADC module                      |

|   | 3.9   | Timer module                    |

|   | 3.10  | SCI communications              |

|   | 3.11  | SPI Communications              |

|   | 3.12  | Motor Control Module            |

|   | 3.13  | LCD module                      |

|   | 3.14  | Stepper stall detect module     |

| 4 | Con   | clusion                         |

| 5 | Use   | ful Reference Material          |

|   |       |                                 |

© Freescale Semiconductor, Inc., 2010. All rights reserved.

# 2 Setup

### 2.1 Tools setup

#### NOTE

Before starting any of the module examples in this document, it is important to install CodeWarrior<sup>TM</sup> Development Studio and CodeWarrior for Micro-controllers as described in the *DEMO9S12XHY256 Quick Start Guide* which accompanies the demonstration board.

### 2.2 Board setup

The steps listed below provide a basic configuration for each of the module examples in this document. Any deviation from this basic configuration or any specific requirements for a module will be outlined in the relevant module chapter.

- 1. The DEMO9S12XHY256 board must be configured with the default jumper settings as shown in the *DEMO9S12XHY256 Quick Start Guide* that accompanies the demonstration board.

- 2. Connect an A/B USB cable to an open USB port on the host PC and the USB connector on the DEMO9S12XHY256 demonstration board. Follow the on-screen instructions to install the necessary USB drivers if required.

- 3. Move the ON/OFF switch (SW5) to the ON position.

- 4. The green +5 V LED above the ON/OFF switch will illuminate.

# 3 Demonstration Lab Examples

### 3.1 Clocks and reset generator

This lab example shows how to produce PLL based bus clocks using the CRG module in its different modes of operation. The example software initializes the PLL to run in RUN Mode at 4 MHz bus, Run Mode 40 MHz bus, Pseudo Stop 8 MHz bus, and Stop Mode 16 MHz bus clock. The changes in the bus clock can be observed via the pulse rate of LED1 and the frequency can be measured by monitoring the ECLK signal (bus clock) on an oscilloscope.

### 3.1.1 Setup

The following steps must be followed before running the lab example.

- 1. Start CodeWarrior by selecting it in the Windows Start menu.

- 2. From the CodeWarrior main menu, choose File > Open and choose the S12XHY\_CRG\_Demo.mcp file.

- 3. Click Open. The project window then opens.

- 4. C code of this demonstration is contained within the main.c file. Double click on the file to open it.

- 5. From the main menu choose Project > Debug. This compiles the source code, generates an executable file, and downloads it to the demo board.

- 6. A new debugger environment opens. After the download process is finished, close the debugger environment.

- 7. The PLL configuration is sent through the serial communications port on the DEMO9S12XHY256 board (baud rate = 9600, data bits = 8, parity = N, stop bits = 1, flow control = none). Open a terminal window on the PC with this configuration.

- 8. The bus clock speed is represented on pin 59 PH2/ECLK (to accomplish this demonstration code clear the ECLKCTL register and see the MCU reference manual for further information). The ECLK signal is equivalent to the MCU bus speed and can be monitored by attaching an oscilloscope probe to pin 23 of the DS1 header. This signal is not available in J1 header because it is part of the LCD bus.

#### 3.1.2 Instructions

Follow these instructions to run the lab example.

#### Run 4 MHz test

- 1. Press RESET, the MCU is now in run mode with a bus clock frequency of 4 MHz.

- 2. Monitor the ECLK signal on the oscilloscope. The ECLK matches the bus clock frequency, observe the LED pulse rate, and examine the PLL configuration on the terminal window.

#### Run 40 MHz test

- 3. Press RESET while pressing down SW1, make sure to release the RESET switch first. The MCU is now in run mode with a bus clock frequency of 40 MHz.

- 4. Monitor the ECLK signal on the oscilloscope. The ECLK will match the bus clock frequency, observe the LED pulse rate, and examine the PLL configuration on the terminal window.

#### Pseudo stop mode test

- 5. Press RESET while pressing down SW2, make sure to release the RESET switch first. The MCU is now running in Pseudo Stop with a bus clock frequency of 8MHz.

- 6. Monitor the ECLK signal on the oscilloscope. The ECLK will match the bus clock frequency, observe the LED pulse rate, and examine the PLL configuration on the terminal window.

- 7. Press the SW4 button, clock pulses will disappear, and the MCU will restart after WD expires with its default clock configuration (4 MHz bus clock).

#### Stop mode test

- 8. Press RESET while pressing down SW3, make sure to release RESET switch first. The MCU is now running and prepared for stop mode with a bus clock frequency of 16 MHz.

- 9. Monitor the ECLK signal on the oscilloscope. ECLK will match the bus clock frequency. Observe the LED pulse rate and examine the PLL configuration on the terminal window.

- 10. Press the SW4 button, the clock pulses disappear, the MCU enters STOP mode, the bus clock will stop, and the MCU will stay in STOP mode until the RESET switch is pressed.

MC9S12XHY-Family Demonstration Lab Training, Rev. 0

### 3.1.3 Summary

The CRG PLL has four operation modes, self-clock mode (which is a fail soft action when the MCU looses the main CLK, see the MCU manual for further information regarding this mode), run mode, pseudo stop, and full stop mode.

For further information on the CRG module, refer to the following documentation available at www.freescale.com.

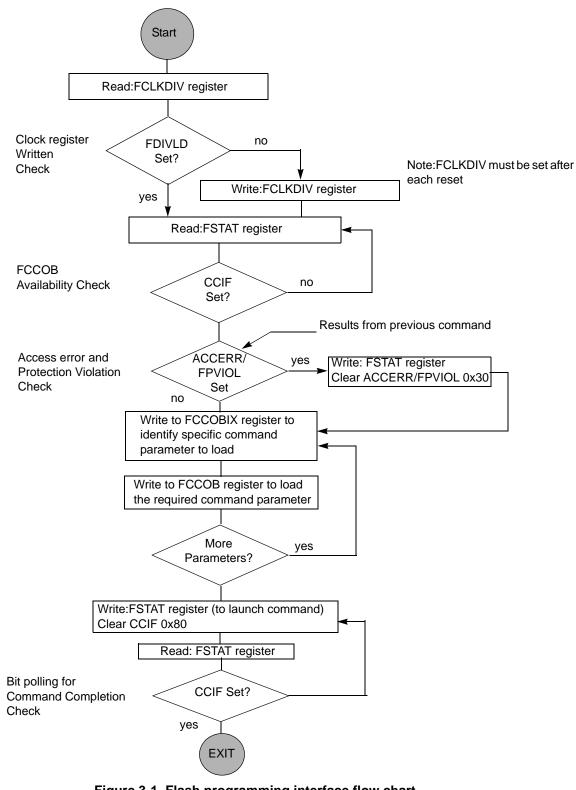

### 3.2 Flash programming example

The flash technology module contains program flash (P-flash) and data flash (D-flash). P-Flash is intended primarily for non-volatile code storage. D-Flash is used as basic flash memory for non-volatile data storage or non-volatile storage to support emulated EEPROM or a combination of both. The user interfaces with this module via the following steps.

- 1. Set the flash clock divider (FCLKDIV)

- 2. Check the status of the Flash status register (FSTAT)

- 3. Make sure the command complete interrupt flag is set (CCIF=1)

- 4. Launch the appropriate flash commands (program, erase, verify, and so on) via FCCOBIX and FCCOB registers.

- 5. Check flash status register and the CCIF=1.

A flow chart of these steps is shown below Figure 3-1.

Figure 3-1. Flash programming interface flow chart

#### 3.2.1 Setup

- 1. Start CodeWarrior by selecting it in the Windows Start menu.

- 2. From the CodeWarrior main menu, choose File > Open and choose the S12XHY\_Flash\_Demo.mcp file.

- 3. Click Open. The project window opens.

- 4. The C code of this demonstration is contained within the main.c file. Double click on the file to open it.

- 5. From the main menu choose Project > Debug. This compiles the source code, generates an executable file, and downloads it to the demo board.

- 6. A new debugger environment will open.

#### 3.2.2 Instructions

Notice that this program is compiled and runs from RAM because sections of the flash will be erased in this example. The security information (0x7F\_FF0F) in the flash configuration field is not erased.

#### NOTE

If this is accidently erased the part will be secured and cannot be re-programmed until it is unsecured. For more information on how to unsecure go to the P&E Micro website.

The file of interest is main.c. The purpose of this demonstration is to:

- Launch a flash command

- Demonstrate programming and erasing of flash

This example has been written with a series of user software breakpoint. Therefore, the only thing that has to be done is to press the Run button .

On start-up, the debugger should begin the program in main.

#### 3.2.2.1 Breakpoint 1— Launch flash command—filling P-flash

The importance at this breakpoint is the LaunchFlashCommand function. This function is responsible for exercising the flash block depending upon the flash command given. The flash commands are briefly described in the flash.h header file and within the *S12XHY Reference Manual*.

Stepping through will take the user to the function below Figure 3-2.

| /*************************************                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------|

| Function Name : LaunchFlashCommand                                                                                         |

| Engineer : b06320<br>Date : 08/06/09                                                                                       |

| Arguments :                                                                                                                |

| Return :<br>Notes : This function does not check if the Flash is erased.                                                   |

| This function does not explicitly verify that the data has been                                                            |

| sucessfully programmed                                                                                                     |

| This function must be located in RAM or a flash block not<br>being programmed.                                             |

| ***************************************                                                                                    |

|                                                                                                                            |

| tU08 LaunchFlashCommand(char params, tU08 command, tU08 ccob0, tU16 ccob1, tU16 ccob2, tU16 ccob3, tU16 ccob4, tU16 ccob5) |

| if(FSTAT_CCIF == 1) {                                                                                                      |

| /* Clear any error flags*/<br>FSTAT = (FPVIOL_MASK   ACCERR_MASK);                                                         |

| /* Write the command id / ccob0 */<br>FCCOBIX = 0;<br>FCCOBII = command;                                                   |

| FCCOBLO = ccob0;                                                                                                           |

| if(++FCCOBIX != params) {     FCCOB = ccob1:                                                                               |

| if(++FCCOBIX != params) {                                                                                                  |

| FCCOB = ccob2; /* Write next data word to CCOB buffer. */<br>if(++FCCOBIX != params) {                                     |

| FCCOB = ccob3; /* Write next data word to CCOB buffer. */                                                                  |

| if(++FCCOBIX != params) { FCCOB = ccob4: /* Write next data word to CCOB buffer. */                                        |

| if(++FCCOBIX != params)                                                                                                    |

| FCCOB = ccob5; /* Write next data word to CCOB buffer. */                                                                  |

| }                                                                                                                          |

|                                                                                                                            |

| FCCOBIX = parame-1:                                                                                                        |

| /* Clear command buffer empty flag by writing a 1 to it $*/$                                                               |

| /* Liear command buffer empty flag by Writing a 1 to 1t */<br>FSTAT = CCLF_MASK;                                           |

| <pre>while (!FSTAT_CCIF) {</pre>                                                                                           |

| <pre>} return(FSTAT); /* command completed */ }</pre>                                                                      |

| <pre>return(FLASH_BUSY); /* state machine busy */ }</pre>                                                                  |

Figure 3-2. (Code Snippet) Launch flash command function

#### 3.2.2.2 Breakpoint 2 — Launched program commands — known data

On entry of the second breakpoint, the memory maps have been set up to show the P-flash being erased (0xFFFF state) then programmed with known parameters (0xAAAA). P-Flash pages from F0 to FB have been filled with 0XAAAA. Consider that the store process, particularly in sectors as big as the P-Flash, may take ~20s to be completed Figure 3-3.

| D-flash                          | P-flash                                           |

|----------------------------------|---------------------------------------------------|

| 📟 Memory: 1                      | Memory: 2                                         |

| Auto Logical                     | Auto Logical                                      |

| 000800'L FF FF FF FF FF FF FF FF | 008000'L AA AA AA AA AA AA AA AA AA               |

| 000808'L FF FF FF FF FF FF FF FF | 008008'L AA AA AA AA AA AA AA AA AA               |

| 000818'L FF FF FF FF FF FF FF FF | 008010'L AA AA AA AA AA AA AA AA AA               |

| 000820'L FF FF FF FF FF FF FF FF | 008020'L AA AA AA AA AA AA AA AA AA               |

| 000828'L FF FF FF FF FF FF FF    | 008028'L AA AA AA AA AA AA AA AA AA               |

| 000830'L FF FF FF FF FF FF FF FF | 008030'L AA AA AA AA AA AA AA AA                  |

| 000838'L FF FF FF FF FF FF FF FF | 008038'L AA AA AA AA AA AA AA AA AA               |

| 000840'L FF FF FF FF FF FF FF FF | 008040'L AA AA AA AA AA AA AA AA AA               |

| 000848'L FF FF FF FF FF FF FF FF | 008048'L AA AA AA AA AA AA AA AA                  |

| 000850'L FF FF FF FF FF FF FF FF | 008050'L AA AA AA AA AA AA AA AA AA               |

| 000858'L FF FF FF FF FF FF FF FF | 008058'L AA AA AA AA AA AA AA AA                  |

| 000860'L FF FF FF FF FF FF FF FF | 008060'L AA AA AA AA AA AA AA AA                  |

| 000868'L FF FF FF FF FF FF FF FF | 008068'L AA AA AA AA AA AA AA AA AA               |

| 000870'L FF FF FF FF FF FF FF FF | 008070'L AA AA AA AA AA AA AA AA AA               |

| 000878'L FF FF FF FF FF FF FF FF | 008078'L AA AA AA AA AA AA AA AA AA               |

| 000880'L FF FF FF FF FF FF FF FF | 008080'L AA AA AA AA AA AA AA AA AA               |

| 000888'L FF FF FF FF FF FF FF FF | 008088'L AA AA AA AA AA AA AA AA AA               |

| 000898'L FF FF FF FF FF FF FF FF | 008090'L AA AA AA AA AA AA AA AA AA               |

| 0008A0'L FF FF FF FF FF FF FF FF | 0080A0'L AA AA AA AA AA AA AA AA AA               |

| 0008A8'L FF FF FF FF FF FF FF FF | 0080A8'L AA AA AA AA AA AA AA AA AA               |

| 0008B0'L FF FF FF FF FF FF FF FF | 0080BO'L AA AA AA AA AA AA AA AA AA               |

| 0008B8'L FF FF FF FF FF FF FF    | 0080B8'L AA AA AA AA AA AA AA AA                  |

| 0008C0'L FF FF FF FF FF FF FF    | 0080CO'L AA AA AA AA AA AA AA AA                  |

| 0008C8'L FF FF FF FF FF FF FF FF | 0080C8'L AA AA AA AA AA AA AA AA AA               |

| 0008D0'L FF FF FF FF FF FF FF FF | 0080DO'L AA AA AA AA AA AA AA AA                  |

| 0008D8'L FF FF FF FF FF FF FF FF | 0080D8'L AA AA AA AA AA AA AA AA                  |

| 0008E0'L FF FF FF FF FF FF FF FF | 0080EO'L AA AA AA AA AA AA AA AA                  |

| 지지 지지 지지 지지 지지 지지 지지 NR NNNN     | א גע גע גע גע גע גע די איז א און אין 🗹            |

| 📰 Register                       |                                                   |

| HC12                             | Auto                                              |

| D O A O B                        | 0                                                 |

|                                  | 1.0                                               |

|                                  |                                                   |

| IP 3115 PC 3115 PPA(             |                                                   |

|                                  | SXHINZVC                                          |

| EPAGE   0 GPAGE   F DIRI         | ECT   0 RPAGE   FD                                |

|                                  | na and meansmine. D Flack filled with 0x44444 usi |

Figure 3-3. The memory maps real time erasing and programming, P-Flash filled with 0xAAAA values

The P-flash window (0x8000 to 0xBFFF) shows 16 K of the P-Flash content, to navigate through all programmed pages change the PPAGE index. Programmed pages in this example are F0 to FB.

The D-flash window (0x0800 to 0x0BFF) shows 1 K of the D-Flash, navigation through the D-Flash's 8 K space is possible by changing EPAGE index from 0 to 7 (8 1K pages) (Figure 3-4).

| 🔳 Register |         |                   |

|------------|---------|-------------------|

| HC12       |         | Auto              |

| D 0        | A 0     | в 0               |

| IX CO      | IY 2    |                   |

| IP 3312    | PC 3312 | PPAGE FO          |

| SP 20FB    | IPL 0   | CCR SXHINZVC      |

| EPAGE 0    | GPAGE F | DIRECT O RPAGE FD |

|            |         |                   |

|            |         |                   |

|            |         |                   |

Figure 3-4. Changing P and D flash page indexes

### 3.2.2.3 Breakpoint 3 — Launched program commands — address data

The store procedure is the same as in previous step, except the data being written to the P-flash is different. The data written is the actual addresses of the P-flash (Figure 3-5).

| D-flash                                                              |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P-fla                      | ash                   |          |       |

|----------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|----------|-------|

| Memory: 1                                                            |           | Memory: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |                       | -        |       |

| Auto                                                                 | Logical   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       | Auto Lo  | gical |

| 000800'L FF FF FF FF FF FF FF FF                                     | 🔺         | 008000'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00 00 02 00                | 04 00 06              |          | ~     |

| 000808'L FF FF FF FF FF FF FF FF                                     |           | 1. No. 2. 2. 2. 2. 2. 2. 2. 2. 2. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                       |          |       |

| 000810'L FF FF FF FF FF FF FF FF                                     |           | 008010'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10 00 12 00                | 14 00 16              |          |       |

| 000818'L FF FF FF FF FF FF FF FF                                     |           | 008018'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 <mark>00</mark> 1A 00   | 1C <mark>00</mark> 1E |          |       |

| 000820'L FF FF FF FF FF FF FF FF                                     |           | 008020'L <mark>00</mark>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 00 22 00                | 24 00 26              | ".\$.&   |       |

| 000828'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       | . (.*.,  |       |

| 000830'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 00 32 00                |                       | .0.2.4.6 |       |

| 000838'L FF FF FF FF FF FF FF FF                                     |           | 7.57.787.787.87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       | .8.:.<.> |       |

| 000840'L FF FF FF FF FF FF FF FF                                     |           | C. M. C. S. C. Starting and Street                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 00 42 00                |                       | .@.B.D.F |       |

| 000848'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48 00 4A 00                |                       | .H.J.L.N |       |

| 000850'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50 00 52 00                |                       | .P.R.T.V |       |

| 000858'L FF FF FF FF FF FF FF FF                                     |           | A CONTRACTOR OF A CONTRACTOR OF A CONTRACTOR OF A CONTRACTOR OF A CONTRACTOR A CONTRACTOR A CONTRACTOR A CONTRA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58 00 5A 00                |                       | .X.Z.\.^ |       |

| 000860'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60 00 62 00                |                       | . b.d.f  |       |

| 000868'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68 00 6A 00                |                       | .h.j.l.n |       |

| 000870'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | 74 00 76              | .p.r.t.v |       |

| 000878'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78 00 7A 00<br>80 00 82 00 |                       | .x.z. .~ |       |

| 000880'L FF FF FF FF FF FF FF FF<br>000888'L FF FF FF FF FF FF FF FF |           | 1. No. 2. State (1996) ***********************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88 00 8A 00                |                       | *******  |       |

| 000880°L FF FF FF FF FF FF FF FF FF                                  |           | Contraction of the second second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90 00 92 00                |                       |          |       |

| 000898'L FF FF FF FF FF FF FF FF                                     |           | Contraction of the state of the state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98 00 92 00<br>98 00 9A 00 |                       |          |       |

| 0008A0'L FF FF FF FF FF FF FF FF                                     |           | A CONTRACTOR OF A CONTRACTOR A CONTRA | A0 00 A2 00                |                       |          |       |

| 0008A8'L FF FF FF FF FF FF FF FF                                     |           | Constant and an an an an an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A8 00 AA 00                |                       |          |       |

| 0008B0'L FF FF FF FF FF FF FF FF                                     |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | B0 00 B2 00                |                       |          |       |

| 0008B8'L FF FF FF FF FF FF FF                                        |           | [14] 20 19 20 20 20 20 20 20 20 20 20 20 20 20 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | B8 00 BA 00                |                       |          |       |

| 0008CO'L FF FF FF FF FF FF FF FF                                     |           | 12.13.24.26.25.26.26.7 State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CO 00 C2 00                |                       |          |       |

| 0008C8'L FF FF FF FF FF FF FF FF                                     |           | 1 1 1 1 2 2 2 2 2 2 1 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | C8 00 CA 00                |                       |          |       |

| 0008D0'L FF FF FF FF FF FF FF FF                                     |           | 0080D0'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DO 00 D2 00                | D4 <mark>00</mark> D6 |          |       |

| 0008D8'L FF FF FF FF FF FF FF FF                                     |           | 0080D8'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D8 00 DA 00                | DC <mark>OO</mark> DE |          |       |

| 0008E0'L FF FF FF FF FF FF FF FF                                     |           | 0080E0'L 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | E0 00 E2 00                | E4 <mark>00</mark> E6 |          |       |

| वन वन वन वन वन वन वन ता 18780000                                     | <u> </u>  | ດດຂດສຸຊານ. ດດ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F8 00 FA 00                | नन <mark>00</mark> 1न |          | ×     |

| I Re                                                                 | gister    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       |          |       |

| HC12                                                                 | 2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | Auto                  |          |       |

|                                                                      |           | D P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                          | , ion o               |          |       |

| D                                                                    | 0 A       | 0 B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U U                        |                       |          |       |

| IX                                                                   | CO IY     | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                       |          |       |

|                                                                      | 3312 PC : | 3312 PPAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FO                         |                       |          |       |

| SP                                                                   | 20FB IPL  | 0 CCR S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SXHINZVC                   |                       |          |       |

| EPAG                                                                 | E O GPAGE | F DIRECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | T O RPAGE                  | FD                    |          |       |

|                                                                      | 111       | 1//                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            | 9-24                  |          |       |

|                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       |          |       |

|                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       |          |       |

|                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       |          |       |

|                                                                      |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                       |          |       |

Figure 3-5. Address values stored in P-flash

### 3.2.2.4 Breakpoint 4 — D-flash — launched program commands

The same functions are used but now they perform activity on the D-flash. The only differences to the flash command function are the memory addresses issued and flash commands, that is D-flash instead of P-flash.

The end of the demonstration is indicated by the LEDs on the evaluation board (EVB) being toggled.

This example does not re-program the device to default, this happens on the next re-load of a program by allowing NVM erasing.

#### 3.2.3 Summary

The demonstration software has shown how to initialize the flash command to perform programming, erasing, and erase verify on both the P-flash and D-flash. It is vital that the flow diagram is followed for correct operation. Deviation from this could cause errors when working with the P/D-flash. Although this demonstration did not include it, it is good practice to verify that the correct data has been programmed to the flash.

### 3.3 Emulated EEPROM driver

The electrically erasable programmable read only memory (EEPROM), which can be byte or word programmed and erased is often used in automotive electronic control units. This flexibility for program and erase operations make it suitable for data storage of application variables that must be maintained when power is removed, and needs to be updated individually during run-time. For the devices without EEPROM memory, the page-erasable flash memory can be used to emulate for EEPROM through EEPROM emulation software.

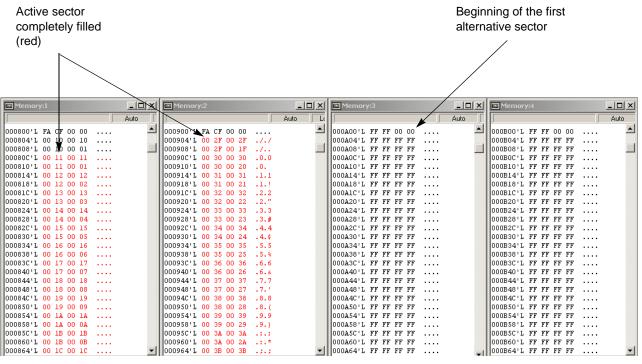

The EEPROM emulation driver for the S12XHY implements the fixed-length data record scheme emulation on a split gate flash. The emulated EEPROM functionalities are organizing data records, initializing and de-initializing EEPROM, and reporting EEPROM status reading and writing data records.

Four or more sectors will be involved in emulation with a round robin scheduling scheme.

#### 3.3.1 Setup

- 1. Start CodeWarrior by selecting it in the Windows Start menu.

- 2. From the CodeWarrior main menu, choose File > Open and choose the S12XHY\_EEE\_Demo.mcp file.

- 3. Click Open. The project window opens.

- 4. The C code of this demonstration is contained within the NormalDemo.c file. Double click on the file to open it.

- 5. From the main menu choose Project > Debug. This compiles the source code, generates an executable file, and downloads it to the demo board.

- 6. A new debugger environment opens.

### 3.3.2 Instructions

The file of interest is NormalDemo.c where the main function resides. The purpose of this demonstration is to show how:

- The D-flash is initialized for EEE

- The active and alternative sectors are assigned

- The active sector is filled and swapped (and erased) with an alternative sector

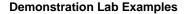

In an application, only the last point above is of relevance — the D-flash is continually read and written to, sectors would be copied, and swapped and erased. This example has been written with a series of user software breakpoint, therefore the only thing that has to be done is to press the Run button .

On start-up, the debugger should begin the program in main as shown in Figure 3-6.

```

void main(void)

{

UINT16 returnCode;

UINT16 readAddr;

UINT16 erasingCycles;

UINT16 temp[EED_DATA_VALUE_SIZE/EED_MIN_PROG_SIZE] = { > 0,0,0 < };

UINT18 i,j;</pre>

```

#### Figure 3-6. Main function

#### 3.3.2.1 Breakpoint 1 — Erase the D-flash

```

/* This erases the D-Flash sectors used for EED. The entire emulated EEPROM

from EED_FLASH_START_ADDRESS to EED_FLASH_END_ADDRESS is erased. */

asm_BGND;

/* User breakpoint1 - the function below will erase the D-flash */

returnCode = FSL_DeinitEeprom();

if (EED_OK != returnCode)

{

[...]

/* Wait until DeinitEeprom is done */

while(BUSY_== EE_Status)

...]

```

#### Figure 3-7. Breakpoint 1

When selecting the run button, the first software breakpoint is reached. Breakpoint 1 stops at the function responsible for initializing the D-flash. This function erases and assigns the physical D-flash which is used for EEE. Notice that the selected D-flash (0x800, 0x900, 0xA00, 0xB00) is in the erased state.

# NP

#### 3.3.2.2 Breakpoint 2 — Initialize the active and alternative sectors

```

returnCode = FSL_InitEeprom();  /* initilise EEPROM */

/* Hit run to the next software breakpoint, where first record will be written */

if (EED_OK != returnCode)

{

ErrorTrap();

FrorTrap();

while (BUSY == EE_Status)

{

FSL_Main();

FSL_Main();

}

```

#### Figure 3-8. Breakpoint 2

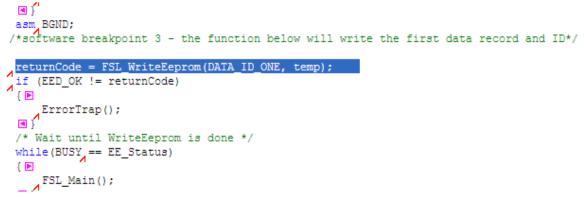

The D-flash has now been erased and has to be arranged as active and alternative sectors. This software driver requires that at least 2 alternative sectors be available. This deals with any brownout or dead sector situations. The FSL\_InitEeprom function initializes the two sectors at location 0x100000 and 0x100100 to *active* and the remaining sectors 0x100200, 0x100300, and 0x100400 to *alternative*. On completion, the active sectors are defined by 0xFACF0000 and the alternative sectors are defined by 0xFFFF0000.

The active sectors are displayed on the memory windows as follows (Table 3-1).

| Window   | EPAGE | Local Map | Global Address |

|----------|-------|-----------|----------------|

| Memory:1 | 0     | 0x800     | 0x100000       |

| Memory:2 | 0     | 0x900     | 0x100100       |

| Memory:3 | 0     | 0xA00     | 0x100200       |

| Memory:4 | 0     | 0xB00     | 0x100300       |

| Memory:1 | 1     | 0x800     | 0x100400       |

#### Table 3-1. Active sectors on memory windows

#### NOTE

For being able to see the content of the 0x100400 alternative record change the EPAGE register on the Register window as indicated on Figure 3-9.

| Memory:1                                     | Memory:2              |          | Memory:3                                     | <u>_   ×</u> | Memory:4                                     |       |

|----------------------------------------------|-----------------------|----------|----------------------------------------------|--------------|----------------------------------------------|-------|

| Auto                                         |                       | Auto Lo  |                                              | Auto         |                                              | Auto  |

| 000800'L FA CF 00 00                         | 000900'L FA CF 00 00  | <b>_</b> | 000A00'L FF FF 00 00                         | <b></b>      | 000B00'L FF FF 00 00                         |       |

| 000804'L FF FF FF FF                         | 000904'L FF FF FF FF  |          | 000A04'L FF FF FF FF                         |              | 000B04'L FF FF FF FF                         |       |

| 000808'L FF FF FF FF                         | 000908'L FF FF FF FF  |          | 000A08'L FF FF FF FF                         |              | 000B08'L FF FF FF FF                         |       |

| 00080C'L FF FF FF FF                         | 00090C'L FF FF FF FF  |          | 000A0C'L FF FF FF FF                         |              | 000B0C'L FF FF FF FF                         | .     |

| 000810'L FF FF FF FF                         | 000910'L FF FF FF FF  |          | 000A10'L FF FF FF FF                         |              | 000B10'L FF FF FF FF                         |       |

| 000814'L FF FF FF FF                         | 000914'L FF FF FF FF  |          | 000A14'L FF FF FF FF                         |              | 000B14'L FF FF FF FF                         | ·     |

| 000818'L FF FF FF FF                         | 000918'L FF FF FF FF  |          | 000A18'L FF FF FF FF                         |              | 000B18'L FF FF FF FF                         | ·     |

| 00081C'L FF FF FF FF                         | 00091C'L FF FF FF FF  |          | 000A1C'L FF FF FF FF                         |              | 000B1C'L FF FF FF FF                         | ·     |

| 000820'L FF FF FF FF                         | 000920'L FF FF FF FF  |          | 000A20'L FF FF FF FF                         |              | 000B20'L FF FF FF FF                         |       |

| 000824'L FF FF FF FF                         | 000924'L FF FF FF FF  |          | 000A24'L FF FF FF FF                         |              | 000B24'L FF FF FF FF                         | -     |

| 000828'L FF FF FF FF<br>00082C'L FF FF FF FF | 000928'L FF FF FF FF  |          | 000A28'L FF FF FF FF<br>000A2C'L FF FF FF FF |              | 000B28'L FF FF FF FF<br>000B2C'L FF FF FF FF |       |

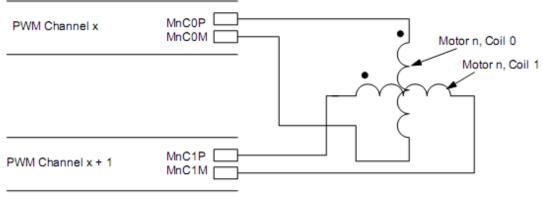

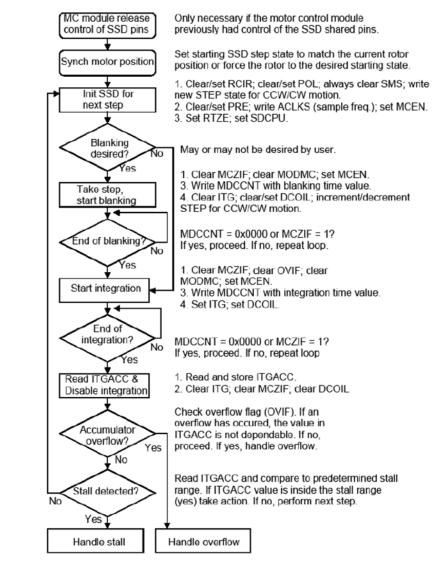

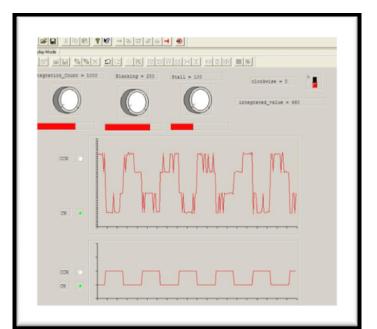

|                                              | 00092C'L FF FF FF FF  |          | 000A2C'L FF FF FF FF                         |              |                                              |       |