Freescale Semiconductor Design Checklist Document Number: AN4403 Rev. 0, 04/2014

# P3041 QorlQ Integrated Processor Design Checklist

## About this document

This document provides recommendations for new designs based on the P3041. It may also be useful in debugging newly-designed systems by highlighting those aspects of a design that merit special attention during initial system start-up.

Each section has a pin termination checklist or a system-level checklist, or sometimes both.

## Before you begin

Ensure you are familiar with the following Freescale documents before proceeding:

- P3041 QorIQ Integrated Processor Hardware Specifications (P3041EC)

- P3041 QorIQ Integrated Processor Reference Manual (P3041RM)

- P3041 Chip Errata (P3041CE)

- QorIQ Data Path Acceleration Architecture (DPAA) Reference Manual (DPAARM)

#### Contents

| 1.  | Simplifying the first phase of design | . 2 |

|-----|---------------------------------------|-----|

| 2.  | Power design recommendations          | . 6 |

| 3.  | Power-on reset recommendations        | 11  |

| 4.  | DDR recommendations                   | 12  |

| 5.  | SerDes recommendations                | 15  |

| 6.  | eLBC recommendations                  | 16  |

| 7.  | DMA recommendations                   | 17  |

| 8.  | PIC recommendations                   | 18  |

| 9.  | IEEE 1588 recommendations             | 18  |

| 10. | Ethernet management recommendations   | 19  |

| 11. | TSEC recommendations                  | 20  |

| 12. | UART recommendations                  | 21  |

| 13. | I2C recommendations                   | 22  |

| 14. | eSDHC recommendations                 | 22  |

| 15. | eSPI recommendations                  | 24  |

| 16. | USB recommendations                   | 24  |

| 17. | GPIO recommendations                  | 26  |

| 18. | DFT recommendations                   | 28  |

| 19. | Power management recommendations      | 28  |

| 20. | Trust recommendations                 | 29  |

| 21. | Clock recommendations                 | 29  |

| 22. | System control recommendations        | 30  |

| 23. | Debug recommendations                 | 31  |

| 24. | JTAG recommendations                  | 33  |

| 25. | No connect recommendations            | 38  |

| 26. | Thermal recommendations               | 38  |

| 27. | Revision history                      | 42  |

|     |                                       |     |

### **1** Simplifying the first phase of design

This section outlines recommendations to simplify the first phase of design. Before designing a system with the chip, it is recommended that the designer be familiar with the available documentation, software, models, and tools.

This figure shows the major functional units within the chip.

Figure 1. Chip Block Diagram

### 1.1 Recommended resources

This table lists helpful tools, training resources, and documentation, some of which may be available only under a non-disclosure agreement (NDA). Contact your local field applications engineer or sales representative to obtain a copy.

| ID         | Name                                                                                                                                                                                                                              | Location                              |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

|            | Related documentation                                                                                                                                                                                                             |                                       |  |  |  |

| P3041CE    | <i>P3041 Chip Errata</i><br><b>Note:</b> This document describes the latest fixes and work-arounds for the chip. It is strongly recommended that this document be thoroughly researched prior to starting a design with the chip. | Contact your Freescale representative |  |  |  |

| P3041EC    | P3041 QorIQ Integrated Processor Hardware Specifications                                                                                                                                                                          | Contact your Freescale representative |  |  |  |

| P3041FS    | P3041 Fact Sheet                                                                                                                                                                                                                  | www.freescale.com                     |  |  |  |

| P3041RM    | P3041 QorlQ Integrated Processor Reference Manual                                                                                                                                                                                 | www.freescale.com                     |  |  |  |

| P3041RMAD  | Errata to P3041 QorlQ Integrated Processor Reference Manual                                                                                                                                                                       | Contact your Freescale representative |  |  |  |

| DPAARM     | QorIQ Data Path Acceleration Architecture (DPAA) Reference Manual                                                                                                                                                                 | Contact your Freescale representative |  |  |  |

| P3041SECRM | P3041 Security (SEC 4.2) Reference Manual                                                                                                                                                                                         | Contact your Freescale representative |  |  |  |

| E500CORERM | PowerPC e500 Core Complex Reference Manual                                                                                                                                                                                        | www.freescale.com                     |  |  |  |

| AN4326     | Verification of the IEEE 1588 Interface                                                                                                                                                                                           | www.freescale.com                     |  |  |  |

| AN4311     | SerDes Reference Clock Interfacing and HSSI measurements Recommendations                                                                                                                                                          | www.freescale.com                     |  |  |  |

| AN4309     | PowerQUICC DDR3 SDRAM Controller Register Setting Considerations                                                                                                                                                                  | www.freescale.com                     |  |  |  |

| AN4290     | Configuring the Data Path Acceleration Architecture (DPAA)                                                                                                                                                                        | www.freescale.com                     |  |  |  |

| AN3939     | DDR Interleaving for PowerQUICC and QorIQ Processors                                                                                                                                                                              | www.freescale.com                     |  |  |  |

| AN3940     | Hardware and Layout Design Considerations for DDR3 SDRAM Memory Interfaces                                                                                                                                                        | www.freescale.com                     |  |  |  |

| AN3645     | SEC 2/3x Descriptor Programmer's Guide                                                                                                                                                                                            | www.freescale.com                     |  |  |  |

| AN2919     | Determining the I2C Frequency Divider Ratio for SCL                                                                                                                                                                               | www.freescale.com                     |  |  |  |

#### Table 1. Helpful tools and references

#### Table 1. Helpful tools and references (continued)

| ID                   | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Location                              |  |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|--|

|                      | Software tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |  |  |

| I2CBOOTSEQ           | Boot sequencer generator tool allows configuration of any memory-mapped register before the completion of power-on reset (POR). The register data to be changed is stored in an I2C EEPROM. The chip requires a particular data format for register changes as outlined in the P3041RM. The boot sequencer tool (I2CBOOTSEQ) is a C-code file. When compiled and given a sample data file, it will generate the appropriate raw data format as outlined in the P3041RM. The file that is generated is an s-record file that can be used to program the EEPROM. | Contact your Freescale representative |  |  |  |

| LBCUPMIBCG           | UPM Programming tool features a GUI for a user-friendly programming interface. It allows programming of all three of the chip's user-programmable machines. The GUI consists of a wave editor, a table editor, and a report generator. The user can edit the waveform directly or the RAM array directly. At the end of programming, the report generator will print out the UPM RAM array that can be used in a C-program.                                                                                                                                    | Contact your Freescale representative |  |  |  |

| NetComm<br>Software  | <ul> <li>The NetComm device driver software package is available for download. It includes the following:</li> <li>Device drivers for DPAA and other commonly used modules</li> <li>Use cases to test the functionality of DPAA and other commonly used modules</li> </ul>                                                                                                                                                                                                                                                                                     | www.freescale.com/netcommsw           |  |  |  |

| QorlQ DPAA<br>SDK    | Mentor Embedded Linux Essentials for QorIQ Processors with Data Path Acceleration                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | www.freescale.com                     |  |  |  |

|                      | Hardware tools                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |  |  |  |

| P3041DS <sup>1</sup> | Development system, including schematics, bill of materials, board errata list, user's Guide, and configuration guide                                                                                                                                                                                                                                                                                                                                                                                                                                          | Contact your Freescale representative |  |  |  |

|                      | Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |  |  |  |

| IBIS                 | To ensure first path success, Freescale strongly recommends using the IBIS models for board level simulations, especially for SerDes and DDR characteristics.                                                                                                                                                                                                                                                                                                                                                                                                  | www.freescale.com                     |  |  |  |

| BSDL                 | Use the BSDL files in board verification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | www.freescale.com                     |  |  |  |

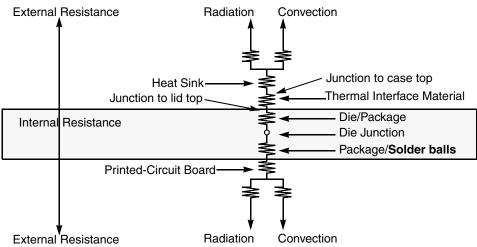

| Flotherm             | Use the Flotherm model for thermal simulation. Especially without forced cooling or constant airflow, a thermal simulation should not be skipped.                                                                                                                                                                                                                                                                                                                                                                                                              | www.freescale.com                     |  |  |  |

#### Table 1. Helpful tools and references (continued)

| ID | Name                                                                                                                                                                                                              | Location                    |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|

|    | Available training                                                                                                                                                                                                |                             |  |  |  |

| _  | Our third-party partners are part of an extensive alliance network. More information can be found at www.freescale.com/alliances.                                                                                 | www.freescale.com/alliances |  |  |  |

| _  | Training materials from past Smart Network Developer's Forums and Freescale Technology Forums (FTF) are also available at our website. These training modules are a valuable resource for understanding the chip. | www.freescale.com/alliances |  |  |  |

<sup>1</sup> Design requirements in the device hardware specification and design checklist supersede the design/implementation of the DS system.

### 1.2 **Product revisions**

This table lists the processor version register (PVR) and system version register (SVR) values for the various chip silicon derivatives.

| Device<br>number | Device<br>revision | Core<br>revision | Processor version<br>register value | System version register value | With         |

|------------------|--------------------|------------------|-------------------------------------|-------------------------------|--------------|

| P3041E           | 1.0                | V2.2             | 0x8023_0121                         | 0x8219_0310                   | DPAA SEC 4.2 |

| P3041            |                    |                  |                                     | 0x8211_0310                   | DPAA only    |

| P3041E           | 1.1                |                  |                                     | 0x8219_0311                   | DPAA SEC 4.2 |

| P3041            |                    |                  |                                     | 0x8211_0311                   | DPAA only    |

Table 2. Chip product revisions

## 2 Power design recommendations

### 2.1 Power pin recommendations

#### Table 3. Power and ground pin termination checklist

| Signal name              | Signal<br>type | Used                                                                                             | Not used          | Remarks (for customer use) | Completed |

|--------------------------|----------------|--------------------------------------------------------------------------------------------------|-------------------|----------------------------|-----------|

| AV <sub>DD</sub> _CC1    |                | Power supply for Core cluster PLL1 (1.0 V through a filter).                                     | Tie to GND        |                            |           |

| AV <sub>DD</sub> _CC2    |                | Power supply for Core cluster PLL2 (1.0 V through a filter).                                     | Tie to GND        |                            |           |

| AV <sub>DD</sub> _DDR    |                | Power supply for the DDR PLL (1.0 V through a filter).                                           | Tie to GND        |                            |           |

| AV <sub>DD</sub> _PLAT   |                | Power supply for the Platform PLL (1.0 V through a filter).                                      | Tie to GND        |                            |           |

| AV <sub>DD</sub> _SRDS1  |                | Power supply for the SerDes PLL1 (1.0 V through a filter).                                       | Tie to GND        |                            |           |

| AV <sub>DD</sub> _SRDS2  |                | Power supply for the SerDes PLL2 (1.0 V through a filter).                                       | Tie to GND        |                            |           |

| AV <sub>DD</sub> _SRDS3  |                | Power supply for the SerDes PLL3 (1.0 V through a filter).                                       | Tie to GND        |                            |           |

| SV <sub>DD</sub>         |                | Power supply for the SerDes core logic (1.0 V).                                                  | Tie to GND        |                            |           |

| BV <sub>DD</sub>         |                | Power supply for the local bus and GPIO (1.8 V/2.5 V/3.3 V).                                     | Tie to GND        |                            |           |

| CV <sub>DD</sub>         |                | Power supply for eSPI and& eSDHC.                                                                | Tie to GND        |                            |           |

| GV <sub>DD</sub>         |                | Power supply for the DDR (1.5 V/1.35V).                                                          | Tie to GND        |                            |           |

| LV <sub>DD</sub>         | _              | Power supply for the TSEC (2.5 V/3.3 V).                                                         | Tie to GND        |                            |           |

| OV <sub>DD</sub>         |                | Power supply for the general I/O (3.3 V).                                                        | Tie to GND        |                            |           |

| V <sub>DD_CA_CB_PL</sub> |                | Power supply for core 0-3 and platform (1.0 V).                                                  | Tie to GND        |                            |           |

| V <sub>DD_LP</sub>       |                | Low power security monitor supply (1.0V)                                                         | Tie to GND        |                            |           |

| SENSEVDD_CA_PL           | _              | For Rev 1.1 and Rev 2.0, the better solution is to use the SENSEVDD_CB and SENSEGND_CB pair. The | Leave unconnected |                            |           |

| SENSEVDD_CB              |                | SENSEVDD_CA_PL and SENSEGND_CA_PL pair can be left as unconnected.                               |                   |                            |           |

| XV <sub>DD</sub>         |                | Power supply for the SerDes transceiver (1.5 V/1.8 V).                                           | Tie to GND        |                            |           |

| POVDD                    | _              | Fuse programming override supply (1.5V).                                                         | Tie to GND        |                            |           |

| Signal name    | Signal<br>type | Used                                | Not used                        | Remarks (for customer use) | Completed |

|----------------|----------------|-------------------------------------|---------------------------------|----------------------------|-----------|

| USB1_VDD_3P3   | —              | USB1 PHY PLL 3.3V Supply.           | Tie to GND or leave unconnected |                            |           |

| USB2_VDD_3P3   | —              | USB2 PHY Transceiver 3.3V Supply.   | Tie to GND or leave unconnected |                            |           |

| USB1_VDD_1P0   | —              | USB1 PHY PLL 1.0V Supply.           | Tie to 1.0V                     |                            |           |

| USB2_VDD_1P0   | —              | USB2 PHY PLL 1.0V Supply            | Tie to 1.0V                     |                            |           |

| SGND           | —              | SerDes core logic GND               |                                 |                            |           |

| XGND           | —              | SerDes transceiver GND              | SerDes transceiver GND          |                            |           |

| GND            | —              | Ground                              |                                 |                            |           |

| AGND_SRDS1     | —              | SerDes PLL 1 GND                    |                                 |                            |           |

| AGND_SRDS2     | —              | SerDes PLL 2 GND                    |                                 |                            |           |

| AGND_SRDS3     | —              | SerDes PLL 3 GND                    |                                 |                            |           |

| SENSEGND_CA_PL | —              | Core group A and Platform GND sense |                                 |                            |           |

| SENSEGND_CB    | —              | Core group B GND sense              |                                 |                            |           |

| USB1_AGND      | —              | USB1 PHY Transceiver GND            |                                 |                            |           |

| USB2_AGND      | —              | USB2 PHY Transceiver GND            |                                 |                            |           |

#### Table 3. Power and ground pin termination checklist (continued)

### 2.2 Power system-level recommendations

#### Table 4. Power design system-level checklist

| Item                                                                                                               | Remarks (for customer use) | Completed |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| General                                                                                                            |                            |           |

| 1. Ensure that all power supplies have a voltage tolerance no greater than 5% from the nominal value. <sup>1</sup> |                            |           |

| 2. Ensure the power supply is selected based on MAXIMUM power dissipation. <sup>1</sup>                            |                            |           |

| 3. Ensure the thermal design is based on THERMAL power dissipation. <sup>1</sup>                                   |                            |           |

#### Table 4. Power design system-level checklist (continued)

| Item                                                                                                                                                                                                                                                          | Remarks (for customer use) | Completed |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| 4. Ensure the power-up sequence is within 75 ms. <sup>1</sup>                                                                                                                                                                                                 |                            |           |

| 5. Use large power planes to the extent possible.                                                                                                                                                                                                             |                            |           |

| 6. Ensure the PLL filter circuit is applied to AV <sub>DD-CA_PL</sub> , AV <sub>DD-CB</sub> , AV <sub>DD-DDR</sub> .                                                                                                                                          |                            |           |

| 7. If SerDes is enabled, ensure the PLL filter circuit is applied to the respective AV <sub>DD</sub> _SRDS. Otherwise, a filter is not required.                                                                                                              |                            |           |

| 8. Ensure the PLL filter circuits are placed as close to the respective AV <sub>DD</sub> pin as possible.                                                                                                                                                     |                            |           |

| 9. Ensure the decoupling capacitors of 0.1 $\mu$ F are placed at each V <sub>DD</sub> , AV <sub>DD</sub> , B/C/G/L/X/S/OV <sub>DD</sub> pin.                                                                                                                  |                            |           |

| Power supply decoupling                                                                                                                                                                                                                                       |                            |           |

| 10. Provide large power planes, because immediate charge requirements by the device are always serviced from the power planes first.                                                                                                                          |                            |           |

| 11.Place at least one decoupling capacitor at each V <sub>DD</sub> , AV <sub>DD</sub> , BV <sub>DD</sub> , CV <sub>DD</sub> , OV <sub>DD</sub> , GV <sub>DD</sub> , and LV <sub>DD</sub> pins of the device.                                                  |                            |           |

| 12. Ensure these decoupling capacitors receive their power from separate $V_{DD}$ , $AV_{DD}$ , $BV_{DD}$ , $CV_{DD}$ , $OV_{DD}$ , $GV_{DD}$ , and $LV_{DD}$ , and GND planes in the PCB, utilizing short traces to minimize inductance.                     |                            |           |

| 13.Capacitors may be placed directly under the device using a standard escape pattern, and others may surround the part.                                                                                                                                      |                            |           |

| <ul> <li>14.Ensure these capacitors have a value of 0.01 or 0.1 μF.</li> <li>15.Only use ceramic surface mount technology (SMT) capacitors to minimize lead inductance, preferably 0402 or 0603.</li> </ul>                                                   |                            |           |

| 16.Distribute several bulk storage capacitors around the PCB, feeding the $V_{DD}$ , $AV_{DD}$ , $BV_{DD}$ , $CV_{DD}$ , $OV_{DD}$ , $GV_{DD}$ , and $LV_{DD}$ planes to enable quick recharging of the smaller chip capacitors.                              |                            |           |

| 17. Ensure the bulk capacitors have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary.                                                                                                                              |                            |           |

| 18. Ensure the bulk capacitors are connected to the power and ground planes through two vias to minimize inductance.                                                                                                                                          |                            |           |

| 19. Ensure you work directly with your power regulator vendor for best values and types of bulk capacitors. The capacitors need to be selected to work well with the power supply so as to be able to handle the chip dynamic load requirements. <sup>2</sup> |                            |           |

| Item                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Remarks (for customer use) | Completed |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| SerDes power supply decoupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |           |

| 20. Use only SMT capacitors to minimize inductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |           |

| 21. Connections from all capacitors to power and ground must be done with multiple vias to further reduce inductance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |           |

| <ul> <li>22. Ensure the board has at least one 10 × 10-nF SMT ceramic chip capacitor as close as possible for each supply ball of the chip.</li> <li>23. Where the board has blind vias, ensure these capacitors are placed directly below the chip supply and ground connections.</li> <li>24. Where the board does not have blind vias, ensure these capacitors are placed in a ring around the chip as close to the supply and ground connections as possible.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |           |

| 25. For all SerDes supplies: Ensure there is a 1-μF ceramic chip capacitor on each side of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |           |

| 26. For all SerDes supplies: Ensure there is a 10-μF, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100-μF, low ESR SMT tantalum chip capacitor between the device and any SerDes voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |           |

| PLL power supply filtering <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |           |

| 27. Provide independent filter circuits per PLL power supply, as illustrated in this figure <sup>4</sup> .<br>$V_{DD}$ _@A_PL $V_{DD}$ _@A_PL $V_{DD}$ |                            |           |

| 28. Ensure it is built with surface mount capacitors with minimum effective series inductance (ESL). <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |           |

| 29. Place each circuit as close as possible to the specific AV <sub>DD</sub> pin being supplied to minimize noise coupled from nearby circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |           |

| 30. Ensure each of the PLLs is provided with power through independent power supply pins (AV <sub>DD-CA-PLAT</sub> , AV <sub>DD-CB</sub> , AV <sub>DD-DDR</sub> , AV <sub>DD-SRDS</sub> , respectively).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |           |

| 31. Ensure the AV <sub>DD</sub> level is always equivalent to V <sub>DD</sub> , and preferably these voltages are derived directly from V <sub>DD</sub> through a low frequency filter scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |           |

#### Table 4. Power design system-level checklist (continued)

r design recommendations

| Item                                                                                                                                                                                                                                         | Remarks (for customer use) | Completed |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| 32.For maximum effectiveness, ensure the filter circuit is placed as close as possible to the AV <sub>DD-SRDS</sub> ball to ensure it filters out as much noise as possible.                                                                 |                            |           |

| 33. Ensure the ground connection is near the AV <sub>DD_SRDS</sub> ball. The 0.003- $\mu$ F capacitor is closest to the ball, followed by the two 2.2- $\mu$ F capacitors, and finally the 1.0- $\Omega$ resistor to the board supply plane. |                            |           |

| 34. To ensure stability of the internal clock, ensure the power supplied to the PLL is filtered using a circuit similar to the one shown in this figure.                                                                                     |                            |           |

| $SV_{DD} \circ \qquad 1.0 \Omega$<br>$\downarrow 2.2 \mu F^1 \qquad \downarrow 2.2 \mu F^1 \qquad \downarrow 0.003 \mu F$<br>$\downarrow GND$                                                                                                |                            |           |

| Caution: These filters are a necessary extension of the PLL circuitry and are compliant with the device specifications. Any deviation from the recommended filters is done at the user's risk.                                               |                            |           |

| 35.Ensure the capacitors are connected from AV <sub>DD_SRDS</sub> to the ground plane.                                                                                                                                                       |                            |           |

| 36.Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces should be kept short, wide, and direct.                                                                                                         |                            |           |

| 37.Ensure AV <sub>DD-SRDS</sub> is a filtered version of SVDD.                                                                                                                                                                               |                            |           |

| 38.Ensure that signals on the SerDes interface are fed from the XV <sub>DD</sub> power plane.                                                                                                                                                |                            |           |

| See the P30/1EC for more details                                                                                                                                                                                                             |                            | <b>I</b>  |

#### Table 4. Power design system-level checklist (continued)

See the P3041EC for more details.

<sup>2</sup> Suggested bulk capacitors are 100–330 μF (AVX TPS tantalum or Sanyo OSCON).

<sup>3</sup> The PLL power supply filter circuit filters noise in the PLLs' resonant frequency range from 500 kHz–10 MHz.

<sup>4</sup> A higher capacitance value for C2 can be used to improve the filter as long as the other C2 parameters do not change (0402 body, X5R, ESL <= 0.5 nH).

<sup>5</sup> Consistent with the recommendations of Dr. Howard Johnson in High Speed Digital Design: A Handbook of Black Magic (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

### **3** Power-on reset recommendations

Various device functions are initialized by sampling certain signals during the assertion of PORESET. These power-on reset (POR) inputs are pulled either high or low during this period. While these pins are generally output pins during normal operation, they are treated as inputs while PORESET is asserted. When PORESET de-asserts, the configuration pins are sampled and latched into registers, and the pins then take on their normal output circuit characteristics.

#### Table 5. Power-on reset system-level checklist

| Item                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Remarks (for customer use) | Completed |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------|

| Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |           |

| 1. Ensure PORESET is asserted for a minimum of 1ms. Ensure HRESET is asserted for a minimum of 32 SYSCLK cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |           |

| 2. Use a 4.7 k $\Omega$ pull-down resistor to pull the configuration pin to a valid logic-low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |           |

| <ol> <li>Optional: An alternative to using pull-up and pull-down resistors to configure the POR pins is to use a PLD or similar device that drives the configuration signals to the chip when PORESET is asserted. The PLD must begin to drive these signals at least four SYSCLK cycles prior to the de-assertion of PORESET, hold their values for at least 2 SYSCLK cycles after the de-assertion of PORESET, and then release the pins to high impedance afterward for normal device operation.</li> <li>Note: See the P3041EC for details about reset initialization timing specifications.</li> </ol> |                            |           |

| I/O supply voltage encodings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |           |

| <ul> <li>4. Ensure IO_VSEL[0:4] encodings are selected properly for each I/O supply. The external pull-up resistor on IO_VSEL[0:4] must be less than 1K.</li> <li>Warning: Incorrect voltage-select settings can lead to irreversible device damage.</li> <li>Note: See the P3041EC for details about I/O voltage selection.</li> </ul>                                                                                                                                                                                                                                                                     |                            |           |

This table lists all the reset configuration pins. See the chip reference manual, section 4.6.3 for more information.

#### Table 6. Reset configuration pins

| Reset configuration name | Function signal name | Configuration                                          | Default value       | Remarks (for customer use) | Completed |

|--------------------------|----------------------|--------------------------------------------------------|---------------------|----------------------------|-----------|

| cfg_gpinput[0:15]        | LAD[0:15]            | This is for an application-specific purpose.           | 1111 1111 1111 1111 |                            |           |

| cfg_xvdd_sel             | LAD[26]              | 0: XVDD 1.8V<br>1: XVDD 1.5V                           | 1                   |                            |           |

| cfg_elbc_ecc             | LAD[23]              | 0: NAND flash ECM disable<br>1: NAND flash ECC enable  | 1                   |                            |           |

| cfg_dram_type            | LAD[24]              | 0: DDR3 technology(1.5V)<br>1: DDR3L technology(1.35V) | 1                   |                            |           |

| cfg_rcw_src[0]           | LGPL0/LFCLE          | Source of the reset configuration                      | 1                   |                            |           |

| cfg_rcw_src[1]           | LGPL1/LFALE          | word                                                   | 1                   |                            |           |

| cfg_rcw_src[2]           | LGPL2/LOE/LFRE       |                                                        | 1                   |                            |           |

| cfg_rcw_src[3]           | LGPL3/LFWP           |                                                        | 1                   |                            |           |

| cfg_rcw_src[4]           | LGPL5                |                                                        | 1                   |                            |           |

| cfg_svr[0:1]             | LAD[16:17]           | LAD[16:17] = 2'b11;                                    | 11                  |                            |           |

### 4 DDR recommendations

#### Table 7. DDR pin termination checklist

| Signal name            | I/О Туре | Used                                | Not used                                                                                | Remarks (for customer use) | Completed |

|------------------------|----------|-------------------------------------|-----------------------------------------------------------------------------------------|----------------------------|-----------|

| MA[0:15]               | 0        | Must be properly terminated to VTT. | May be left unconnected.                                                                |                            |           |

| MBA[0:2]               | 0        | Must be properly terminated to VTT. | May be left unconnected.                                                                |                            |           |

| MCK[0:3] /<br>MCK[0:3] | 0        | Must be properly terminated.        | May be left unconnected. However, the MCK pin should be disabled via DDRCLKDR register. |                            |           |

| MCKE[0:3]              | 0        | Must be properly terminated to VTT. | May be left unconnected.                                                                |                            |           |

| Signal name              | I/О Туре | Used                                                                                                                                                                                                                                                         | Not used                                             | Remarks (for customer use) | Completed |

|--------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------|-----------|

| MCS[0:3]                 | 0        | Must be properly terminated to VTT.                                                                                                                                                                                                                          | May be left unconnected.                             |                            |           |

| MDIC[0:1]                | I/O      | These pins are used for automatic calibration<br>of the DDR IOs. The calibration resistor value<br>for DDR3 should be $20-\Omega$ (full-strength<br>mode) or $40.2-\Omega$ (half-strength mode).                                                             | May be left unconnected.                             |                            |           |

| MDM[0:8]                 | 0        | —                                                                                                                                                                                                                                                            | May be left unconnected.                             |                            |           |

| MDQ[0:63]                | I/O      | —                                                                                                                                                                                                                                                            | May be left unconnected.                             |                            |           |

| MDQS[0:8] /<br>MDQS[0:8] | I/O      | _                                                                                                                                                                                                                                                            | May be left unconnected.                             |                            |           |

| MECC[0:7]                | I/O      | _                                                                                                                                                                                                                                                            | May be left unconnected.                             |                            |           |

| MAPAR_ERR                | I        | This pin is an open drain output from registered DIMMs. Ensure that a 4.7K pull-up to GVDD is present on this pin.                                                                                                                                           | This pin is should be pulled up whether used or not. |                            |           |

| MAPAR_OUT                | 0        | If the controller supports the optional<br>MAPAR_OUT and MAPAR_ERR signals,<br>ensure that they are hooked up as follows:<br>• MAPAR_OUT (from the controller) =><br>PAR_IN (at the RDIMM)<br>• ERR_OUT (from the RDIMM) =><br>MAPAR_ERR (at the controller) | May be left unconnected.                             |                            |           |

#### Table 7. DDR pin termination checklist (continued)

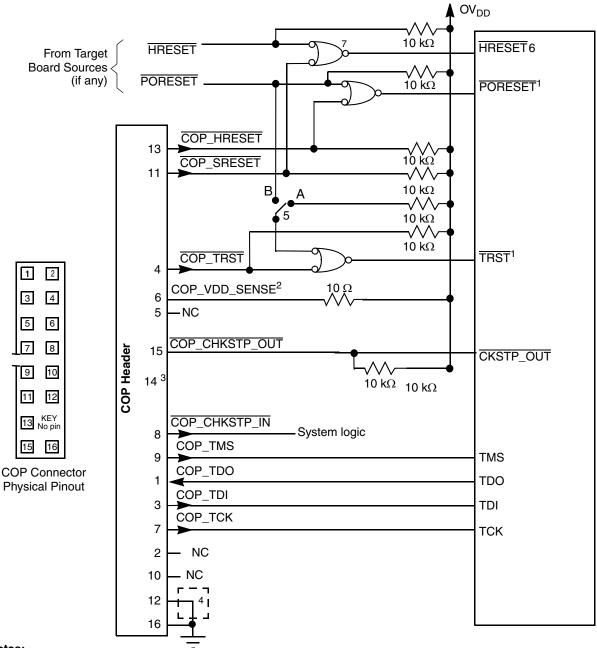

| Signal name | I/O Type | Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Not used                  | Remarks (for customer use) | Completed |